Data Hazards

Data Hazards

Uploaded by

PetreMaziluCopyright:

Available Formats

Data Hazards

Data Hazards

Uploaded by

PetreMaziluOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Data Hazards

Data Hazards

Uploaded by

PetreMaziluCopyright:

Available Formats

CS 2160

Spring, 2011

Data Hazards

Spring, 2011

CS 2160 - Pipeline Data Hazards

Overview

Today well

we ll discuss the following topics:

Data hazards and what causes them

Techniques for avoiding hazards

Pipeline Data Hazards

Software

Edge-Triggered Clocking

Forwarding unit

Hazard detection unit

Additionally, well trace execution of

instructions with data dependencies resulting

in data hazards.

Page 1

CS 2160

Spring, 2011

Data Hazard

A Definition

The situation where an instruction depends on the

result of a previous instruction.

and

the previous instruction hasnt produced the result yet

sub $2, $1, $3

and $12, $2, $5

or $13, $6, $2

add $14, $2, $2

sw $15, 100($2)

Identify the dependencies in the code sequence.

Data Hazards

Identifying Data Hazards in the Pipeline

The dependencies and

resulting hazards are easier

to see in the multi-cycle

representation.

Assume: $t1=10, $t2=10, $t3=-20

CC1

Time

Value of $t2:

sub $2, $1, $3

Program

Execution

Order

and $12, $2, $5

or $13, $6, $2

add $14, $2, $2

sw $15, 100($2)

Data Hazard

Dependency on result of

first instruction and need

that result before its ready.

CC2

CC3

CC4

CC5

CC6

-20

20

CC7

10

10

10

10

10/ 20

10/-20

-20

20

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

WB

WB

Why isnt this a data

hazard in the MIPS

pipeline?

Identify the data hazards in the code sequence.

Pipeline Data Hazards

Page 2

CS 2160

Spring, 2011

Data Hazards

Avoiding Data Hazards: Edge-Triggered Clocking

Writes only occur on the clock edge (first)

Reads occur next

dependencies occurring in the same cycle

as the result is generated are safe

sub $2, $1, $3

IF

and $12, $2, $5

or $13, $6, $2

add $14, $2, $2

ID

EX

MEM

WB

IF

ID

EX

MEM

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

WB

WB

Data Hazards

Avoiding Data Hazards: Software Solutions

Make data hazards illegal. That is, correct code cant

contain dependencies that cause data hazards.

Makes the software (compiler) responsible for

generating correct code.

Compiler either inserts non-dependent code or nops

between the result and the dependent instructions.

sub $2, $1, $3

nop

and $12, $2, $5

nop

or $13, $6, $2

and

add $12,

$14, $2, $5

$2

or

$2

sw $13,

$15, $6,

100($2)

add $14, $2, $2

sw $15, 100($2)

Is this approach realistic? Why or why not?

Pipeline Data Hazards

Page 3

CS 2160

Spring, 2011

Data Hazards

Avoiding Data Hazards: Forwarding

Observation: Instr 1 has the result ready after the EX

stage.

Question:

Since were already storing each Instr 1 result in the EX/MEM

pipeline register, why not hardwire a path and some control to

forward the result to Instr 2 at that point to avoid the hazard?

Answer: O.K.!!!

Instr 1: sub $2, $1, $3

IF

Instr 2: and $12, $2, $5

ID

EX

MEM

WB

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

Instr 3: or $13, $6, $2

Instr 4: add $14, $2, $2

WB

Well address the data hazards caused by memory reads later.

Forwarding & the Forwarding Unit

Detecting Data Hazards in the Pipeline

Notice that data hazards of this type (R-type instructions) occur

when one of the following four conditions is met:

Those where one of the two ALU arguments is currently in the

EX/MEM register

i t (dependency

(d

d

on previous

i

instruction)

i t ti )

EX/MEM.RegisterRd = ID/EX.RegisterRs,

EX/MEM.RegisterRd = ID/EX.RegisterRt

Those where one of the two ALU arguments is currently in the

MEM/WB register (dependency on instruction two ahead in pipeline).

MEM/WB.RegisterRd = ID/EX.RegisterRs

MEM/WB.RegisterRd = ID/EX.RegisterRt

Instr 1: sub $2

$2, $1

$1, $3

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

EX/MEM.RegisterRd = ID/EX.RegisterRs

Instr 2: and $12, $2, $5

MEM/WB.RegisterRd = ID/EX.RegisterRt

Instr 3: or $13, $6, $2

WB

We can use these conditions to detect data hazards and develop our

forwarding unit. When dont these conditions hold?

Pipeline Data Hazards

Page 4

CS 2160

Spring, 2011

Forwarding & the Forwarding Unit

Adding the Forwarding Unit to the Datapath

Add datapath to hold the

ALU results of the previous

two instructions.

PCSrc

0

M

RegDst, ALUOp, ALUSrc

+

4

Shft

Lft

2

Read Data #1

Read Reg #1

Read Reg #2

Instruction

Address

ALUSrc

E

X

M

u

x

Address

ALU

A

ALUOp

Instr[15-0]

Sign

Extend 32

16

IF/ID.RegisterRs

0

M

u

x

1

M

u

x

6

RegDst

Rs

Rt

IF/ID.RegisterRt

IF/ID.RegisterRt

Rt

IF/ID.RegisterRd

Rd

ALU

Cntrl

ForwardA

ForwardB

0

M

u

x

1

W

B

Data

Memory

zero

Registers

Write Reg

Read Data #2

Write Data

Read

Data

branch

RegWrite

IF/ID

P

C

between

EX/Mem

W

B

Branch MemRead

Branch,

MemRead, MemWrite

MemtoReg

Control

Instr

Memory

Add mux to choose

read reg #1,

EX/MEM

EX/MEM.RegisterRs,

RegisterRs or

W

Mem/WB

B

MEM/WB.RegisterRs.

ID/EX

RegWrite, MemToReg

MemWrite

M

1u

x

2

Read

Data

Write

Data

0

M

u

x

1

Add mux to choose

between MemRead

read reg #2,

EX/MEM.RegisterRt, or

MEM/WB.RegisterRt.

EX/MEM.RegisterRd

Forwarding

Unit

MEM/WB.RegisterRd

Forwarding & the Forwarding Unit

Inputs and Outputs -- Abstract

PCSrc

Output: controls which candidate

0

M the ALU.

Rs is used by

1u

ID/EX

Instruction

Instr

Memory

Input:

the Rd register number of

P

Address

C two previous instructions.

the

IInput: Rs

R and

dR

Rt off the

h

instruction about to

enter the EX stage

RegWrite

Shft

Lft

2

Read Data #1

Read Reg #1

Read Reg #2

M

u

x

zero

Registers

ALU

Write Reg

Read Data #2

Write Data

Instr[15-0]

Sign

Extend 32

16

IF/ID.RegisterRs

IF/ID.RegisterRt

M

u

x

0

M

u

x

1

6

RegDst

Rs

Rt

IF/ID.RegisterRt

Rt

IF/ID.RegisterRd

Rd

ALU

Cntrl

ForwardA

ForwardB

0

M

u

x

1

W

B

Data

Memory

Address

Read

Data

Write

Data

0

M

u

x

1

MemRead

EX/MEM.RegisterRd

Forwarding

Unit

Pipeline Data Hazards

Mem/WB

A

ALUOp

Read

Data

W

B

ALUSrc

E

X

branch

IF/ID

Input: the RegWrite

value for

+

the two

previous instructions.

4

EX/Mem

MemtoReg

RegDst, ALUOp, ALUSrc

W

B

MemWrite

x

2

Output: controls which candidateRegWrite, MemToReg

Branch MemRead

Branch,

MemRead, MemWrite

Rt is used by the ALU

ALU.

Control

MEM/WB.RegisterRd

Page 5

CS 2160

Spring, 2011

Forwarding & the Forwarding Unit

Inputs and Outputs -- Detail

Mux Control

ForwardA=00

Source

ID/EX

Explanation

The first ALU operand comes from the register file.

ForwardA=10

EX/MEM

The first ALU operand is forwarded from the prior ALU

result.

ForwardA=01

MEM/WB

The first ALU operand is forwarded from data memory

or an earlier ALU result.

ForwardB=00

ID/EX

The second ALU operand comes from the register file.

ForwardB=10

EX/MEM

The second ALU operand is forwarded from the prior

ALU result.

ForwardB=01

MEM/WB

The first ALU operand is forwarded from data memory

or an earlier ALU result.

Forwarding & the Forwarding Unit

Mapping Inputs to Outputs

Question: How does the forwarding unit determine

which outputs to produce?

A

Answer:

B

Based

d on th

the iinputs,

t off course!!

!!

Check for data hazard on A operand:

-- check the previous instruction

if EX/MEM.RegWrite and

(EX/MEM.RegisterRd0) and

-- will the register be written

-- is the register writable?

(NOT $0)

(EX/MEM.RegisterRd = ID/EX.RegisterRs) then is operand rs = to rd of prev?

ForwardA = 10

-- check the instruction one cycle ahead of the previous instruction

elsif MEM/WB.RegWrite and

-- will the register be written

(MEM/WB.RegisterRd 0) and

-- is the register writable?

(NOT $0)

(MEM/WB.RegisterRd= ID/EX.RegisterRs) then - is operand rs = rd or prevprev?

ForwardA = 01

else -- just use the read data #2

ForwardA = 00

end if

Pipeline Data Hazards

How would this if statement change for the B operand?

Page 6

CS 2160

Spring, 2011

Tracing Execution

Lets execute the following sequence of instructions:

sub $2, $1, $3

and $4, $2, $5

or $4, $4, $2

add $9, $4, $2

What data dependencies would result in a data hazard

without the forwarding

g unit?

Tracing Execution

Clock Cycle 3

IF:

or $4, $4, $2

ID:

and $4, $2, $5

EX:

sub $2, $1, $3

MEM:

before <1>

WB:

before <2>

PCSrc

0

Branch MemRead

Branch,

MemRead, MemWrite

M

ALUSrc

RegDst, ALUOp, ALUSrc

Address

Read Data #1

Read Reg #1

Read Reg #2

$2

M

u

x

zero

Registers

ALU

Write Reg

$5

Read Data #2

Write Data

$3

Instr[15-0]

Sign

Extend 32

16

2

IF/ID.RegisterRs

IF/ID.RegisterRt

0

M

u

x

1

ALU

Cntrl

RegDst

5

IF/ID.RegisterRt

IF/ID.RegisterRd

M

u

x

Rt

4

ForwardA

ForwardB

1

3

0

M

u

x

1

Data

Memory

Address

The write reg is also

forwarded Read

to the next

Data

stage. Write

Data

0

M

u

x

1

MemRead

EX/MEM.RegisterRd

Forwarding

Unit

Pipeline Data Hazards

W

B

The result of $1-$3 is

computed

Shft

Lft

2

$1

A

ALUOp

Read

Data

Instruction

P

C

branch

+

4

Mem/WB

E

X

RegWrite

IF/ID

10

W

B

MemtoReg

Control

Instr

Memory

Data hazard! This

instruction is dependent on

the result of sub $2, $1, $3

EX/Mem

because $2 is an operand

operand.

W

ID/EX

RegWrite, MemToReg = 10

MemWrite

M

1u

x

2

MEM/WB.RegisterRd

Page 7

CS 2160

Spring, 2011

Tracing Execution

This instruction needs $2!

But $2 hasnt been

updated with the most

recent value.

MEM:

WB:

Clock Cycle 4

IF:

and $9, $4, $2

ID:

or $4, $4, $2

EX:

and $4, $2, $5

sub $2, $1, $3

before <1>

PCSrc

0

M

1u

x

ID/EX

Instruction

P

C

Address

EX/Mem

10

ALUSrc

RegDst, ALUOp, ALUSrc

E

X

RegWrite

Read Data #1

Read Reg #1

Read Reg #2

$4

Shft

Lft

2

$2

M

u

x

Address

ALU

$5

A

ALUOp

Instr[15-0]

Sign

Extend 32

16

4

IF/ID.RegisterRs

0

M

u

x

1

M

u

x

Read

Data

Write

Data

ALU

Cntrl

RegDst

IF/ID.RegisterRt

Rt

4

0

M

u

x

1

0

M

u

x

1

MemRead

ForwardA

ForwardB

W

B

Data

Memory

zero

Registers

IF/ID.RegisterRt

selects the value of $2

currently in the EX/MEM

IF/ID.RegisterRd

pipeline register.

Mem/WB

Write Reg

$2

Read Data #2

Write Data

Read

Data

The forwarding unit

detects this and.

W

B

Instr

Memory

10

W

B

Branch MemRead

Branch,

MemRead, MemWrite

branch

Data Hazard! Notice that

both operands are

IF/ID

registers that have

new

+

values4 that have yet to be

written.

Control

MemtoReg

RegWrite, MemToReg = 10

MemWrite

EX/MEM.RegisterRd

Forwarding

Unit

MEM/WB.RegisterRd

Tracing Execution

Clock Cycle 5

ID:

and $9, $4, $2

0

M

1u

x

EX:

or $4, $4, $2

RegWrite, MemToReg = 10

Control

Instruction

EX/Mem

10

W

B

ALUSrc

RegWrite

E

X

Read Data #1

Read Reg #1

Read Reg #2

Shft

Lft

2

$4

M

u

x

It forwards

IF/ID.RegisterRt

pipeline register

copy of $2

IF/ID.RegisterRt

to the B operand.

IF/ID.RegisterRd

M

u

x

A

ALUOp

Instr[15-0]

Sign

Extend 32

16

4

IF/ID.RegisterRs

the MEM/WB

0

M

u

x

1

Read

Data

Write

Data

ALU

Cntrl

RegDst

2

4

2

Rt

0

M

u

x

1

0

M

u

x

1

MemRead

ForwardA

ForwardB

EX/MEM.RegisterRd

2

Forwarding

Unit

Pipeline Data Hazards

Address

ALU

Write Reg

$2

Read Data #2

Write Data

W

B

Data

Memory

zero

Registers

Mem/WB

1

branch

+

The forwarding

unit again

4

detects

that both operands

depend on values4not yet

Instr

2

written.

Memory

Read

Data

WB:

sub $2, $1, $3

10

IF/ID

Address

W

B

Branch MemRead

Branch,

MemRead, MemWrite

RegDst, ALUOp, ALUSrc

P

C

MEM:

and $4, $2, $5

It forwards the EX/MEM

pipeline register copy of $4

to the A operand.

ID/EX

MemtoReg

PCSrc

MemWrite

IF:

after<1>

MEM/WB.RegisterRd

Page 8

CS 2160

Spring, 2011

Tracing Execution

Clock Cycle 6

IF:

after<2>

ID:

after<1>

EX:

and $9, $4, $2

MEM:

or $4, $4, $2

WB:

and $4, $2, $5

PCSrc

0

RegDst, ALUOp, ALUSrc

Instruction

W

B

ALUSrc

E

X

Read Data #1

Read Reg #1

Read Reg #2

Shft

Lft

2

$4

M

u

x

Address

ALU

Write Reg

Read Data #2

Write Data

$2

A

ALUOp

M

u

x

Instr[15-0]

Sign

Extend 32

16

IF/ID.RegisterRs

IF/ID.RegisterRt

IF/ID.RegisterRt

Rt

IF/ID.RegisterRd

0

M

u

x

1

Read

Data

Write

Data

ALU

Cntrl

RegDst

0

M

u

x

1

MemRead

ForwardA

ForwardB

0

M

u

x

1

W

B

Data

Memory

zero

Registers

Mem/WB

1

branch

Read

Data

EX/Mem

10

The forwarding

unit picks

Instr

Memory

the most

recent version

(the

P one in the EX/MEM

Address

C

pipeline

register)

10

MemtoReg

but theres two versions of

$4 in the pipelineIF/ID

registers.

W

B

Branch MemRead

Branch,

MemRead, MemWrite

MemWrite

Control

ID/EX

RegWrite, MemToReg = 10

RegWrite

$2 is safe1 Munow, but $4 is still

x

2 (not written)...

a problem

EX/MEM.RegisterRd

Forwarding

Unit

MEM/WB.RegisterRd

Data Hazards: A Second Look

Data Hazards caused by Memory Reads

Up to this point, weve only looked at data hazards

related to r-type instructions.

Data hazards can also occur when there

theres

sa

dependency between a load instruction and another

instruction.

For example:

lw $2, 20($1)

and $4, $2, $5

or $8, $2, $6

add $9, $4, $2

slt $1, $6, $7

Pipeline Data Hazards

Identify the dependencies in this code sequence.

Page 9

CS 2160

Spring, 2011

Data Hazards: A Second Look

A graphical view

Note that the value for $1 isnt available from instr 1

until after the MEM stage.

A a result,

As

lt we mustt stall

t ll th

the pipeline

i li 1 cycle

l

CC1

CC2

CC3

CC4

CC5

CC6

CC7

Time

Instr 1: lw $2, 20($1)

Instr 2: and $4, $2, $5

Instr 3: or $8, $2, $6

Instr 4: add $9, $4, $2

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

Instr 5: slt $1, $6, $7

WB

Detecting Memory Read Hazards

Testing for a Memory Read Data Hazard

Requires the addition of a hazard detection unit.

Heres the test for a memory read data hazard:

-- check

h k the

h previous

i

i

instruction

i

if ID/EX.MemRead and

((ID/EX.RegisterRt = IF/ID.RegisterRs) or

(ID/EX.RegisterRt=IF/ID.RegisterRt

stall the pipeline

end if

Pipeline Data Hazards

Why are we interested in comparing the

IF/ID.RegisterRs & Rt to the ID/EX.RegisterRt instead

of ID/EX.RegistserRd?

Page 10

CS 2160

Spring, 2011

Fixing Memory Read Hazards

Stalling the pipeline

Keep the PC unchanged to load the re-load instruction currently in

the IF stage.

Keep the IF/ID pipeline register unchanged to re-execute the

instruction in the ID stage.

Insert a nop instruction in the EX stage.

CC1

CC2

CC3

CC4

CC5

CC6

Time

IF/ID register is kept the

same.

IF

lw $2, 20($1)

CC7

ID

EX

WB

MEM

PC is kept the same.

IF

and $4, $2, $5

or $8, $2, $6

ID

ID

EX

MEM

WB

IF

IF

ID

EX

MEM

WB

ID

EX

MEM

WB

IF

ID

EX

MEM

The instructions in the IF

IF

add $9,

$2

and$4,

ID stages

re-execute in

those stages, and a nop is

inserted in the EX stage

slt $1, $6, $7

WB

Hazard Detection Unit

Adding the Hazard Detection Unit to the Datapath

PCWrite

PCSrc

ID/EX

W

B

IF/ID

P

C

Address

RegWrite

Shft

Lft

2

Read Data #1

Read Reg #1

Read Reg #2

M

u

x

Registers

Instr[15-0]

Sign

Extend 32

16

IF/ID.RegisterRs

M

u

x

IF/ID.RegisterRt

RegDst

Rs

Rt

IF/ID.RegisterRt

Rt

IF/ID.RegisterRd

Rd

0

M

u

x

1

0

M

u

x

1

Address

Read

Input: The current instruction.

Data

Write

Data

ALU

Output:

Will prevent an overwrite of

6

Cntrl

the IF/ID pipeline registerMemRead

when a

ForwardA

memory read data hazard occurs.

0

M

u

x

1

ForwardB

Output: Will prevent EX/MEM.RegisterRd

an update of

the PC.

Forwarding

Unit

Pipeline Data Hazards

Output: Forwards the nop if

theres a memory read data

hazard or the instruction

Data

information toMemory

the next stage.

zero

ALU

Write Reg

Read Data #2

Write Data

A

ALUOp

Read

Data

Instruction

4

Instr

Memory

ALUSrc

E

X

branch

EX/Mem

IInput:

t WDoes

D

th

the previous

i Mem/WB

B

instruction

read from memory.

W

MemtoReg

Control

M

u

x

MemWrite

IF/ID

D Write

M

1u

x

2

ID/EX.MemRead

Hazard

Detection

Unit

MEM/WB.RegisterRd

Page 11

CS 2160

Spring, 2011

Hazard Detection Unit

We join our pipeline in progress -- Clock Cycle 2

IF:

and $4, $2, $5

PCWrite

ID:

lw $2, 20($1)

EX:

before <1>

MEM:

before <2>

WB:

before <3>

PCSrc

ID/EX

11 W

M

u

x

ALUSrc

E

X

IF/ID

RegWrite

Instruction

Instr

Memory

Address

Read Data #1

Read Reg #1

Read Reg #2

Shft

Lft

2

$1

M

u

x

0

M

u

x

1

M

u

x

A

ALUOp

Instr[15-0]

Sign

Extend 32

16

IF/ID.RegisterRs

6

RegDst

Rs

Rt

1

X

2

IF/ID.RegisterRt

IF/ID.RegisterRt

Address

ALU

$X

Rt

IF/ID.RegisterRd

Read

Data

Write

Data

ALU

Cntrl

ID/EX.RegisterRt

0

M

u

x

1

MemRead

ForwardA

ForwardB

0

M

u

x

1

Rd

W

B

Data

Memory

zero

Registers

Write Reg

Read Data #2

Write Data

Read

Data

Mem/WB

branch

W

B

MemtoReg

P

C

EX/Mem

Control

MemWrite

1

X

IF/ID

D Write

M

1u

x

2

ID/EX.MemRead

Hazard

Detection

Unit

EX/MEM.RegisterRd

Forwarding

Unit

MEM/WB.RegisterRd

Hazard Detection Unit

Clock Cycle 3

ID:

and $4, $2, $5

EX:

lw $2, 20($1)

MEM:

before <1>

PCSrc

ID/EX

00

C t l

Control

IF/ID

Address

Read Data #1

Read Reg #1

Read Reg #2

ALUSrc

E

X

$2

$1

M

u

x

$5

$X

Sign

Extend 32

16

IF/ID.RegisterRs

IF/ID.RegisterRt

IF/ID.RegisterRt

IF/ID.RegisterRd

ID/EX.RegisterRt

M

u

x

0

M

u

x

1

6

2

5

4

ALU

Cntrl

RegDst

ForwardA

ForwardB

1

X

2

Rd

W

B

The HDU detects this and takes

the necessary actions:

1. PCWrite is not asserted.

Data

2. IF/ID WriteMemory

is

not asserted.

zero3. nop instruction is inserted in

Address

ALU pipeline..

Shft

Lft

2

Registers

Write Reg

Read Data #2

Write Data

Mem/WB

Instr[15-0]

Pipeline Data Hazards

W

B

A

ALUOp

Read

Data

Instruction

P

C

11

W

B

0

M

u

x

1

branch

+

4

Instr

Memory

M

u

x

RegWrite

Data hazard! The and

instruction needs the $2 that

has yet to be read from

memory.

EX/Mem

ID/EX.MemRead

Hazard

Detection

Unit

2

IF/ID

D Write

M

1u

x

2

MemtoReg

WB:

before <2>

MemWrite

IF:

or $4, $4, $2

PCWrite

Read

Data

Write

Data

0

M

u

x

1

MemRead

EX/MEM.RegisterRd

Forwarding

Unit

MEM/WB.RegisterRd

Page 12

CS 2160

Spring, 2011

Hazard Detection Unit

Clock Cycle 4 Pipeline Stall

IF:

or $4, $4, $2

PCWrite

ID:

and $4, $2, $5

EX:

nop (bubble)

MEM:

lw $2, 20($1)

WB:

before <1>

PCSrc

ID/EX.MemRead

Hazard

Detection

Unit

ID/EX

10

C t l

Control

IF/ID

4

P

C

Instruction

Instr

Memory

Address

$2

Shft

Lft

2

$2

$5

$5

A

ALUOp

Sign

Extend 32

16

IF/ID.RegisterRs

IF/ID.RegisterRt

6

RegDst

2

5

IF/ID.RegisterRt

Rt

4

Read

Data

Write

Data

ALU

Cntrl

ID/EX.RegisterRt

0

M

u

x

1

MemRead

ForwardA

ForwardB

0

M

u

x

1

Address

0

M

u

x

1

M

u

x

W

B

Data

Memory

u instructions stall

The and and or

x

zero

for one clock cycle in the ID and

ALU

IF stages, respectively.

Instr[15-0]

IF/ID.RegisterRd

Mem/WB

Registers

Write Reg

Read Data #2

Write Data

Read

Data

The

lw reads $2 from Data B

ALUSrc

Memory. $2 is now available

M in

the EX/MEM pipeline register

E

X

Read Data #1

Read Reg #1

Read Reg #2

EX/Mem

00

branch

00

W

B

M

RegWrite

M

u

x

MemtoReg

2

5

IF/ID

D Write

M

1u

x

2

MemWrite

EX/MEM.RegisterRd

Forwarding

Unit

MEM/WB.RegisterRd

Hazard Detection Unit

Clock Cycle 5

IF:

add $9, $4, $2

PCWrite

ID:

or $4, $4, $2

EX:

and $4, $2, $5

MEM:

nop (bubble)

WB:

lw $2, 20($1)

PCSrc

ID/EX.MemRead

Hazard

Detection

Unit

ID/EX

10

C t l

Control

Address

$4

Shft

Lft

2

$2

M

u

x

zero

Registers

Write Reg

Read Data #2

Write Data

ALU

$2

$5

Sign

Extend 32

16

IF/ID.RegisterRs

IF/ID.RegisterRt

ID/EX.RegisterRt

M

u

x

0

M

u

x

1

IF/ID.RegisterRt

IF/ID.RegisterRd

ALU

Cntrl

RegDst

Rt

4

Mem/WB

Instr[15-0]

Pipeline Data Hazards

W

B

ALUSrc

E

X

A

ALUOp

Read

Data

Instruction

P

C

EX/Mem

0

branch

IF/ID

The Forwarding

Unit can now

+

handle the data hazard caused by

4

the lw. It does so by forwarding

4

Read Data #1

the

Instr$2 in the Mem/WB pipeline

Read Reg #1

Memory

2 instruction.

register to the and

Read Reg #2

10

W

B

M

RegWrite

M

u

x

ForwardA

ForwardB

0

M

u

x

1

W

B

11

MemtoReg

4

2

IF/ID

D Write

M

1u

x

2

MemWrite

Data

Memory

Address

Read

Data

Write

Data

0

M

u

x

1

MemRead

EX/MEM.RegisterRd

2

Forwarding

Unit

MEM/WB.RegisterRd

Page 13

CS 2160

Spring, 2011

Hazard Detection Unit

Clock Cycle 6

IF:

after <1>

PCWrite

ID:

add $9, $4, $2

EX:

or $4, $4, $2

MEM:

and $4, $2, $5

WB:

nop (bubble)

PCSrc

ID/EX.MemRead

Hazard

Detection

Unit

ID/EX

10

C t l

Control

IF/ID

4

P

C

Instruction

Instr

Memory

Address

$4

Shft

Lft

2

$4

M

u

x

$2

Instr[15-0]

Sign

Extend 32

16

IF/ID.RegisterRs

IF/ID.RegisterRt

Read

Data

Write

Data

ALU

Cntrl

RegDst

IF/ID.RegisterRt

0

M

u

x

1

ID/EX.RegisterRt

0

M

u

x

1

MemRead

ForwardA

ForwardB

Rt

9

IF/ID.RegisterRd

Address

0

M

u

x

1

M

u

x

W

B

Data

Memory

zero

ALU

$2

A

ALUOp

Write Reg

Read Data #2

Write Data

Mem/WB

Registers

Read

Data

W

B

ALUSrc

E

X

Read Data #1

Read Reg #1

Read Reg #2

EX/Mem

10

branch

10

W

B

M

RegWrite

M

u

x

MemtoReg

4

2

IF/ID

D Write

M

1u

x

2

MemWrite

EX/MEM.RegisterRd

Forwarding

Unit

MEM/WB.RegisterRd

Hazard Detection Unit

Clock Cycle 7

IF:

after <2>

PCWrite

ID:

after <1>

EX:

add $9, $4, $2

MEM:

or $4, $4, $2

WB:

and $4, $2, $5

PCSrc

ID/EX

C t l

Control

IF/ID

Instr

Memory

P

C

Address

W

B

ALUSrc

E

X

Read Data #1

Read Reg #1

Read Reg #2

Shft

Lft

2

$4

M

u

x

$2

Sign

Extend 32

16

IF/ID.RegisterRs

IF/ID.RegisterRt

IF/ID.RegisterRt

Rt

IF/ID.RegisterRd

ID/EX.RegisterRt

M

u

x

0

M

u

x

1

Read

Data

Write

Data

ALU

Cntrl

RegDst

0

M

u

x

1

MemRead

ForwardA

ForwardB

0

M

u

x

1

Address

ALU

Write Reg

Read Data #2

Write Data

W

B

Data

Memory

zero

Registers

Mem/WB

Instr[15-0]

Pipeline Data Hazards

EX/Mem

10

A

ALUOp

Read

Data

Instruction

10

W

B

branch

RegWrite

M

u

x

MemtoReg

10

MemWrite

IF/ID

D Write

M

1u

x

2

ID/EX.MemRead

Hazard

Detection

Unit

EX/MEM.RegisterRd

Forwarding

Unit

MEM/WB.RegisterRd

Page 14

CS 2160

Spring, 2011

End of Slide Show

Spring, 2011

CS 2160 - Pipeline Data Hazards

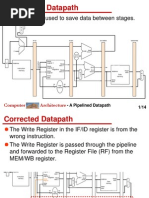

The MIPS Pipelined Datapath

Branch

IF.Flush

Hazard

Detection Unit

+

Shift

Left 2

Address

Registers

Sign

16 Extend

0

M

u

x

1

Except

PC

ALUSrc

0

W

B

Mem/WB

Data

Memory

M

1u

x

2

ALU

0

M

1u

x

2

0

M

u

x

1

ALU

ALUOp Cntrl

32

Instr[25-21]

Instr[[20-16]

Instr[20-16]

Instr[15-11]

EX/Mem

Write Reg

Read Data #2

Write Data

Read

Data

Cause

E

X

Read Data #1

Read Reg #1

Read Reg #2

Instruction

RegWrite

0

IF/ID

W

B

0

M

u

x

1

Control

Instr

Memory

0

M

u

x

1

ID/EX

W

B

MemtoReg

M

1u

x

2

MemWrite

P

C

EX.Flushc

ID.Flush

40000040

29

Address

Read

Data

Write

Data

0

M

u

x

1

MemRead

RegDst

0

M

u

x

1

Forwarding

Unit

Pipeline Data Hazards

Page 15

You might also like

- Write A Random Number Generator That Generates Random Numbers Between 1 and 6 (Simulates A Dice)Document6 pagesWrite A Random Number Generator That Generates Random Numbers Between 1 and 6 (Simulates A Dice)Kartik Rawal100% (2)

- Translating VCD and Ev CD To AteDocument13 pagesTranslating VCD and Ev CD To Atecristian_chitu100% (1)

- Data Hazards in ALU Instructions: Consider This SequenceDocument14 pagesData Hazards in ALU Instructions: Consider This Sequencesivakumarb92No ratings yet

- Lecture9 Cda3101Document62 pagesLecture9 Cda3101MD Manan RainNo ratings yet

- Lecture 11 COMP2611 Processor Part3Document41 pagesLecture 11 COMP2611 Processor Part3jnfzNo ratings yet

- A Pipelined Datapath: Resisters Are Used To Save Data Between StagesDocument14 pagesA Pipelined Datapath: Resisters Are Used To Save Data Between StagesJohnDaGRTNo ratings yet

- Chapter 3 Homework (Take 2)Document7 pagesChapter 3 Homework (Take 2)Jaime Andres Chica PNo ratings yet

- Assignment 3Document3 pagesAssignment 3bugyourselfNo ratings yet

- Anomie's SPC700Document11 pagesAnomie's SPC700picolo789No ratings yet

- Chapter Six: 2004 Morgan Kaufmann PublishersDocument25 pagesChapter Six: 2004 Morgan Kaufmann PublisherssamquicklyNo ratings yet

- FemtoRV32 Piplined Processor ReportDocument25 pagesFemtoRV32 Piplined Processor ReportRatnakarVarunNo ratings yet

- PST1 Solutions For StudentsDocument10 pagesPST1 Solutions For StudentsDirty Rajan100% (1)

- 2022HI400070G NiveditaDocument27 pages2022HI400070G NiveditaNivedita Acharyya 2035No ratings yet

- CS 4200/5200 Computer Architecture I: MIPS Instruction Set ArchitectureDocument12 pagesCS 4200/5200 Computer Architecture I: MIPS Instruction Set ArchitectureIndrit QokuNo ratings yet

- Computer Architecture Test 2Document5 pagesComputer Architecture Test 2gbland100% (1)

- FunwiththecatDocument3 pagesFunwiththecatchrizhexxNo ratings yet

- Ele 404 Super Lab ReportDocument13 pagesEle 404 Super Lab Reportapi-245385341No ratings yet

- CPS 104 Computer Organization and Programming Lecture-9: The MIPS Instruction Set ArchitectureDocument29 pagesCPS 104 Computer Organization and Programming Lecture-9: The MIPS Instruction Set ArchitectureprachesNo ratings yet

- Controlling A Pipelined DatapathDocument17 pagesControlling A Pipelined DatapathAlexander TaylorNo ratings yet

- Chapter4 Pipelining END FA11Document84 pagesChapter4 Pipelining END FA11Aditya GadgilNo ratings yet

- Modbus RTUDocument15 pagesModbus RTUHans MortenNo ratings yet

- Exam2 Practice SolDocument6 pagesExam2 Practice SolIshanNo ratings yet

- Array Processors: SIMD Computer OrganizationDocument45 pagesArray Processors: SIMD Computer OrganizationArshad Matin100% (1)

- Lecture # 12Document31 pagesLecture # 12Noman Ajaz KørãíNo ratings yet

- Kien-Truc-May-Tinh - David-Brooks - cs146-hw2 - (Cuuduongthancong - Com)Document5 pagesKien-Truc-May-Tinh - David-Brooks - cs146-hw2 - (Cuuduongthancong - Com)Ann HerbstNo ratings yet

- Talk Gatech DSP Compilation 2000Document29 pagesTalk Gatech DSP Compilation 2000larryshiNo ratings yet

- Chapter 4B: The Processor, Part B: Mary Jane IrwinDocument56 pagesChapter 4B: The Processor, Part B: Mary Jane IrwinAdip ChyNo ratings yet

- Insert, Update Ordering in InformaticaDocument6 pagesInsert, Update Ordering in InformaticaUr's GopinathNo ratings yet

- M116C 1 EE116C-Midterm2-w15 SolutionDocument8 pagesM116C 1 EE116C-Midterm2-w15 Solutiontinhtrilac100% (1)

- Ca Assignment: Syeda Haima Batool Naqvi CS-18022Document11 pagesCa Assignment: Syeda Haima Batool Naqvi CS-18022Haima NaqviNo ratings yet

- COE301 Lab 13 Pipelined CPU Design With Data ForwardingDocument8 pagesCOE301 Lab 13 Pipelined CPU Design With Data ForwardingItz Sami UddinNo ratings yet

- EE3404 MPMC ALL UNITS NOTES EduEngg-2Document189 pagesEE3404 MPMC ALL UNITS NOTES EduEngg-2lokeskece121No ratings yet

- CS M151B / EE M116C: Computer Systems ArchitectureDocument50 pagesCS M151B / EE M116C: Computer Systems ArchitecturetinhtrilacNo ratings yet

- CCNP Ccie 300 410 Enarsi DigitalTUT New-Q PDFDocument14 pagesCCNP Ccie 300 410 Enarsi DigitalTUT New-Q PDFCristihan RenteriaNo ratings yet

- Computer Science 37 Lecture 22Document14 pagesComputer Science 37 Lecture 22Alexander TaylorNo ratings yet

- Lecture8 Cda3101Document75 pagesLecture8 Cda3101pinkgirl2519No ratings yet

- Moshell Commands BeginnerDocument8 pagesMoshell Commands BeginnerAgbemor Klu88% (8)

- AN0308 Setting Up Cyclic Links With CTNet Using SyPT ProDocument8 pagesAN0308 Setting Up Cyclic Links With CTNet Using SyPT ProSamir TahaNo ratings yet

- Known Issues On Cisco 7600 Router ESDocument18 pagesKnown Issues On Cisco 7600 Router ESirozaNo ratings yet

- Using Excel 97 As A Low Cost HMIDocument9 pagesUsing Excel 97 As A Low Cost HMIhelajeNo ratings yet

- Mainframe Notes1Document8 pagesMainframe Notes1balasubramanian MSNo ratings yet

- MIPS Instruction Set Architecture: ECE4680 Computer Organization & ArchitectureDocument4 pagesMIPS Instruction Set Architecture: ECE4680 Computer Organization & ArchitectureNarender KumarNo ratings yet

- 新建 DOCX 文档Document38 pages新建 DOCX 文档刘嘉琦No ratings yet

- Tuesday, October 31, 2023 10:53 PM: Discuss, The Schemes For Dealing With The Pipeline Stalls Caused by Branch HazardsDocument7 pagesTuesday, October 31, 2023 10:53 PM: Discuss, The Schemes For Dealing With The Pipeline Stalls Caused by Branch Hazardskrahul74714No ratings yet

- Obd-Ii: RS-232 Serial CableDocument5 pagesObd-Ii: RS-232 Serial CableAmir EmraniNo ratings yet

- Ping and Traceroute UnderstandingDocument22 pagesPing and Traceroute Understandingdavekrunal46No ratings yet

- SOP 10. LabView Data Acquisition ProgramDocument7 pagesSOP 10. LabView Data Acquisition ProgramMaqsood AhmedNo ratings yet

- Enhancing Performance With PipeliningDocument71 pagesEnhancing Performance With Pipeliningapi-26072581No ratings yet

- BC420 - 46C - 013special MethodsDocument26 pagesBC420 - 46C - 013special MethodsmkumarshahiNo ratings yet

- Lecture 9: Case Study - MIPS R4000 and Introduction To Advanced PipeliningDocument23 pagesLecture 9: Case Study - MIPS R4000 and Introduction To Advanced PipeliningNithin KumarNo ratings yet

- CA-Easytrieve Frequently Asked QuestionsDocument12 pagesCA-Easytrieve Frequently Asked Questionsapi-3853979No ratings yet

- Computer Science Homework WorksheetDocument5 pagesComputer Science Homework WorksheetEe JianNo ratings yet

- Hard MemoriesDocument14 pagesHard MemoriesYouness RabahNo ratings yet

- Vario v1Document13 pagesVario v1andrade.odontomedNo ratings yet

- Presentation 5296 1523892575 PDFDocument58 pagesPresentation 5296 1523892575 PDFswapnil PanditNo ratings yet

- Lab 2B: Directional Overcurrent Relay Model: ... /FLL145.cfgDocument13 pagesLab 2B: Directional Overcurrent Relay Model: ... /FLL145.cfgAlen JefryNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsFrom EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsNo ratings yet

- WAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksFrom EverandWAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksNo ratings yet

- MM17 ToolaDocument5 pagesMM17 ToolaAchudakumar ThillaichidambaramNo ratings yet

- Unit I Notes Full1 1Document50 pagesUnit I Notes Full1 1Ganesh KumarNo ratings yet

- Seg2Mat: SEG-2 To MATLAB File ConverterDocument5 pagesSeg2Mat: SEG-2 To MATLAB File ConverterAnand BesraNo ratings yet

- Writing Audio Applications Using GStreamerDocument6 pagesWriting Audio Applications Using GStreamerralphosssNo ratings yet

- Industrial Training Report: Python Developer BootcampDocument18 pagesIndustrial Training Report: Python Developer BootcampMohit GoyalNo ratings yet

- CUDNN Library UserGuide PDFDocument149 pagesCUDNN Library UserGuide PDFalibakh62No ratings yet

- ch06 BasicSQLDocument21 pagesch06 BasicSQLcmpatel.chemNo ratings yet

- Easy PRO80 BDocument3 pagesEasy PRO80 BAngga PebriantNo ratings yet

- ABAP Programming EVENTS in SAPDocument4 pagesABAP Programming EVENTS in SAPNikhil MalpeNo ratings yet

- Contact App Android: Project DescriptionDocument16 pagesContact App Android: Project DescriptionSwaragyam PalakuraNo ratings yet

- S.Y.B.C.a 2019 Pattern NewDocument31 pagesS.Y.B.C.a 2019 Pattern NewajinkyasandipshelkeNo ratings yet

- Instant Access to Java Programming Joyce Farrell ebook Full ChaptersDocument55 pagesInstant Access to Java Programming Joyce Farrell ebook Full Chaptersgobinsmarz51100% (2)

- React Front End Developer ResumeDocument2 pagesReact Front End Developer ResumeAakash BathlaNo ratings yet

- Lab 11 - Priority SchedulingDocument5 pagesLab 11 - Priority SchedulingGurruNo ratings yet

- LogDocument12 pagesLogVô Danh KháchNo ratings yet

- Industrial Training Report On Python NewDocument32 pagesIndustrial Training Report On Python NewUTKARSH MAURYANo ratings yet

- Python Microprojec 22616Document13 pagesPython Microprojec 22616nakshtra ahireNo ratings yet

- EEM 486 Computer Architecture Homework VI 1. Consider The Following Code SequenceDocument2 pagesEEM 486 Computer Architecture Homework VI 1. Consider The Following Code SequenceHalim KorogluNo ratings yet

- 15 Java OperatorsDocument8 pages15 Java OperatorsIAN GAMING PH2009No ratings yet

- Extracted Datasheet Pic16f8xa Part2Document7 pagesExtracted Datasheet Pic16f8xa Part2hajarelbekaryNo ratings yet

- NIS Study PlanDocument1 pageNIS Study PlanRayanNo ratings yet

- Page Replacement AlgorithmsDocument4 pagesPage Replacement AlgorithmsKavita RahaneNo ratings yet

- FYITWeb ProgrammingDocument6 pagesFYITWeb Programminganandhisenthilkumar2005No ratings yet

- DSA Project ReportDocument53 pagesDSA Project ReportPritamsingh SolankiNo ratings yet

- Project-Quiz 3Document3 pagesProject-Quiz 3Ayesha ZafarNo ratings yet

- DBMSMCQFINALDocument118 pagesDBMSMCQFINALAkhilesh SinghNo ratings yet

- Comms Protocols CPPDocument189 pagesComms Protocols CPPtimeking00No ratings yet

- Sub Contract Inbound Delivery User ExitDocument3 pagesSub Contract Inbound Delivery User ExitravisamplaNo ratings yet

- CH2-MCQ-12 CompDocument4 pagesCH2-MCQ-12 Comptom7954jNo ratings yet