Dspic® DSC DSP Library: Features

Dspic® DSC DSP Library: Features

Uploaded by

ricardocristi70Copyright:

Available Formats

Dspic® DSC DSP Library: Features

Dspic® DSC DSP Library: Features

Uploaded by

ricardocristi70Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Dspic® DSC DSP Library: Features

Dspic® DSC DSP Library: Features

Uploaded by

ricardocristi70Copyright:

Available Formats

dsPIC® DSC

DSP Library

Summary Features

The dsPIC Digital Signal Controller (DSC) DSP Library Key features of the dsPIC DSC DSP Library include:

provides a set of speed optimized functions for the most • 49 total functions

common digital signal processing applications. The dsPIC • Full compliance with the Microchip MPLAB®C30 C

DSC DSP Library provides significant performance savings compiler, assembler and linker

over equivalent functions coded in C and allows developers

• Simple user interface – only one library file and one

to dramatically shorten their development time. The dsPIC

header file

DSC DSP library may be used with any dsPIC DSC variant.

• Functions are both C and assembly callable

The dsPIC DSC DSP Library is written predominantly in • FIR filtering functions include support for lattice,

Assembly language and makes extensive use of the dsPIC decimating, interpolating and LMS filters

DSC DSP instruction set and hardware resources, including

• IIR filtering functions include support for canonic,

X and Y memory addressing, modulo addressing, bit-

transposed canonic and lattice filters

reversed addressing, 9.31 saturation and REPEAT and DO

loops. • FIR and IIR functions may be used with the filter files

generated by the dsPIC® DSC Digital Filter Design Tool

The dsPIC DSC DSP Library provides functions for the • Transform functions include support for in-place and

following: out-of-place DCT, FFT and IFFT transforms

• Vector operations • Window functions include support for Bartlett,

• Matrix operations Blackman, Hamming, Hanning and Kaiser windows

• Filtering operations • Support for program space visibility

• Transform operations • Complete function profile information including

• Window® operations register usage, cycle count and function size

information

Function Execution Times

Cycle Count Number Execution Time

Function

Equation

Conditions*

of Cycles @40 MIPS

Devices Supported

Complex FFT** — N=64 3739 93.5 μs • All processors in the dsPIC DSC families

Complex FFT** — N=128 8485 212.1 μs

Complex FFT** — N=256 19055 476.4 μs

Single Tap FIR — — 1 25 ns

Block FIR 53+N(4+M) N=32, M=32 1205 30.2 μs

Block FIR Lattice 41+N(4+7M) N=32, M=32 7337 183.5 μs

Block IIR Canonic 36+N(8+7S) N=32, S=4 1188 29.7 μs

Block IIR Lattice 46+N(16+7M) N=32, M=8 2350 58.7 μs

Matrix Add 20+3(C*R) C=8, R=8 212 5.3 μs

Matrix Transpose 16+C(6+3(R-1)) C=8, R=8 232 5.8 μs

Vector Dot

17+3N N=32 113 2.9 μs

Product

Vector Max 19+7(N-2) N=32 229 5.7 μs

Vector Multiply 17+4N N=32 145 3.6 μs

Vector Power 16+2N N=32 80 2.0 μs

*C= #columns, N=# samples, M=#taps, S=#sections, R=#rows

**Complex FFT routine inherently prevents overflow.

1 cycle = 25 nanoseconds @ 40 MIPS

DS01033B-28 www.microchip.com

You might also like

- UNIT 5 (DSP Processor)Document51 pagesUNIT 5 (DSP Processor)gravitarse78% (9)

- Advanced Processors: Overview of DSP Unit-5 Unit-6Document58 pagesAdvanced Processors: Overview of DSP Unit-5 Unit-6isha rajNo ratings yet

- Ac164301 DM300022 DM300017 DM300004-1Document26 pagesAc164301 DM300022 DM300017 DM300004-1Sin NombreNo ratings yet

- Eecs 318 Cad Computer Aided DesignDocument36 pagesEecs 318 Cad Computer Aided Designshilpaa11No ratings yet

- 5.dsp UNIT 5 With 8XDocument69 pages5.dsp UNIT 5 With 8XpraveenNo ratings yet

- Using Dspic30F A/D Converters and The DSP Library For Signal FilteringDocument4 pagesUsing Dspic30F A/D Converters and The DSP Library For Signal FilteringManoj kumarNo ratings yet

- DSP ProcessorsDocument24 pagesDSP ProcessorsHerald Rufus100% (1)

- Ece699 Lecture1Document106 pagesEce699 Lecture1Maninder SinghNo ratings yet

- Unit 5 DSP SystemDocument30 pagesUnit 5 DSP SystemSiddhasen Patil100% (2)

- DSA0039087Document2 pagesDSA0039087AnjuNo ratings yet

- DS-70095K DSPicDocument24 pagesDS-70095K DSPicSandi DladlaNo ratings yet

- 1_2_3DSPDocument7 pages1_2_3DSPns5446742No ratings yet

- 633888485056270520Document115 pages633888485056270520rafeshNo ratings yet

- Xilinx DSP PrimeDocument94 pagesXilinx DSP PrimeQuốc Việt TạNo ratings yet

- Xtremedsp Solutions: Selection GuideDocument38 pagesXtremedsp Solutions: Selection GuideNithishkumar VenkatachalamNo ratings yet

- Evolution of DSP ProcessorsDocument23 pagesEvolution of DSP ProcessorsMuhamed ShereefNo ratings yet

- Unit 51Document191 pagesUnit 51Arvind VishnubhatlaNo ratings yet

- Full NotesDocument367 pagesFull Notesshubhuannu25No ratings yet

- Architectural Analysis of A DSP Device, The Instruction Set and The Addressing ModesDocument50 pagesArchitectural Analysis of A DSP Device, The Instruction Set and The Addressing ModesAnonymous ho5zU20cNo ratings yet

- The Evolution of DSP ProcessorsDocument35 pagesThe Evolution of DSP ProcessorsvivekpaliNo ratings yet

- PDSP ArchitectureDocument95 pagesPDSP ArchitecturekrajasekarantutiNo ratings yet

- BITS Pilani: Digital Signal ProcessingDocument14 pagesBITS Pilani: Digital Signal ProcessingNirneya GuptaNo ratings yet

- Finish Faster With Xilinx DSP Design Solutions: Corporate Headquarters European Headquarters Japan Asia PacificDocument2 pagesFinish Faster With Xilinx DSP Design Solutions: Corporate Headquarters European Headquarters Japan Asia PacificdcesentherNo ratings yet

- DSP ArchitectureDocument71 pagesDSP ArchitectureAnishKumar100% (1)

- Sap - 2Document135 pagesSap - 2Muh Nur FaiziNo ratings yet

- Labview DSP Module For Ni Speedy-33 and Ti DsksDocument4 pagesLabview DSP Module For Ni Speedy-33 and Ti DsksJorge MartinezNo ratings yet

- 5.1. Unit V - DSP ProcessorDocument83 pages5.1. Unit V - DSP ProcessorJayaram ThamizhmaniNo ratings yet

- DsPIC Filter Design Sell Sheet - 51438bDocument2 pagesDsPIC Filter Design Sell Sheet - 51438beinkatzeNo ratings yet

- DSK 6713Document15 pagesDSK 6713sachin_bhingareNo ratings yet

- Lec08 DSPDocument42 pagesLec08 DSPSantosh BanNo ratings yet

- Spirit GSM Amr NB DatasheetDocument1 pageSpirit GSM Amr NB Datasheetsem_sergeNo ratings yet

- Design and Implementation of Digital IIR & FIR Filters On DSK6713 Using CC STUDIOV6.1 PlatformDocument6 pagesDesign and Implementation of Digital IIR & FIR Filters On DSK6713 Using CC STUDIOV6.1 PlatformIheb HamedNo ratings yet

- DSP Lab ManualDocument57 pagesDSP Lab ManualJaronNo ratings yet

- pn0010676 2Document2 pagespn0010676 2Elangovan SekarNo ratings yet

- Digital Signal Processing Unit V: DSP ProcessorDocument20 pagesDigital Signal Processing Unit V: DSP ProcessorKumar ManiNo ratings yet

- Xtremedsp Slice Delivers Maximum Performance and EfficiencyDocument4 pagesXtremedsp Slice Delivers Maximum Performance and EfficiencydcesentherNo ratings yet

- CSC 520 Chapter 1Document56 pagesCSC 520 Chapter 1Le Song LamNo ratings yet

- DSP - Module 5Document16 pagesDSP - Module 5mithunloorNo ratings yet

- DR Tahir Zaidi: Targets For AlgorithmsDocument37 pagesDR Tahir Zaidi: Targets For AlgorithmsBilal AwanNo ratings yet

- DSP Unit-5 FinalDocument97 pagesDSP Unit-5 FinalreventhhuntNo ratings yet

- VLSI Design of Radix-4 Signed-Digit Encoding Based Pre-Encoded MultipliersDocument20 pagesVLSI Design of Radix-4 Signed-Digit Encoding Based Pre-Encoded Multiplierssurya pratapNo ratings yet

- Experiements (Using DSP Kit) Introduction To DSP Processors: MicroprocessorDocument9 pagesExperiements (Using DSP Kit) Introduction To DSP Processors: Microprocessorshiksha singhNo ratings yet

- Digital Signal Processing (DSP)Document45 pagesDigital Signal Processing (DSP)forfreeNo ratings yet

- E5-01 - DSP Lab Version 2Document2 pagesE5-01 - DSP Lab Version 2waleed.murad@gmail.comNo ratings yet

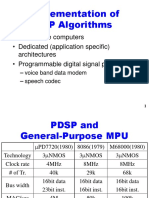

- Implementation of DSP AlgorithmsDocument20 pagesImplementation of DSP Algorithmss tharunNo ratings yet

- DSP Lab Manual DSK Technical Programming With C, MATLAB Programs 2008 B.Tech ECE IV-I JNTU Hyd V1.9Document52 pagesDSP Lab Manual DSK Technical Programming With C, MATLAB Programs 2008 B.Tech ECE IV-I JNTU Hyd V1.9Chanukya Krishna Chama80% (5)

- DDCA_Ch6_Ravi_annotated_v2(2)-mergedDocument176 pagesDDCA_Ch6_Ravi_annotated_v2(2)-mergedRimsha pervaizNo ratings yet

- Introduction to Digital Signal Processors (DSPs)_studentDocument24 pagesIntroduction to Digital Signal Processors (DSPs)_studentharshucaresNo ratings yet

- EE6304 Lecture13 ProcessorsDocument69 pagesEE6304 Lecture13 ProcessorsAshish SoniNo ratings yet

- DSP ArchitecturesDocument71 pagesDSP ArchitecturesTripuresh JoshiNo ratings yet

- 2 Arch Mips IDocument16 pages2 Arch Mips Ijack.johnson.jj1234No ratings yet

- Digital Signal ProcessingDocument14 pagesDigital Signal ProcessingsalonihonaleNo ratings yet

- M. Sc. 4sem Phy-404 A U1 2L Dr. Ratna AgrawalDocument5 pagesM. Sc. 4sem Phy-404 A U1 2L Dr. Ratna AgrawalRohit sahuNo ratings yet

- TDCI ArchDocument77 pagesTDCI ArchCristian Garcia AlarcònNo ratings yet

- INTRODUCTION TO DSP PROCESSORS Unit-5Document43 pagesINTRODUCTION TO DSP PROCESSORS Unit-5Nayab Rasool SKNo ratings yet

- Embedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesFrom EverandEmbedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Architecture-Aware Optimization Strategies in Real-time Image ProcessingFrom EverandArchitecture-Aware Optimization Strategies in Real-time Image ProcessingNo ratings yet

- Markov Analysis DetailsDocument6 pagesMarkov Analysis DetailsAshutoshNo ratings yet

- HTML 101Document2 pagesHTML 101Isam el-laymounyNo ratings yet

- Harel 10Document9 pagesHarel 10Nilesh GopnarayanNo ratings yet

- LG4 - Conditional and Loop StatementsDocument26 pagesLG4 - Conditional and Loop Statementskiddie angelsNo ratings yet

- Costing ProfitssDocument9 pagesCosting Profitssapi-542433757No ratings yet

- Proceedings Second International Conference On Critical Digital PDFDocument243 pagesProceedings Second International Conference On Critical Digital PDFHatem HadiaNo ratings yet

- 231337-TracesDocument164 pages231337-TracesBinibining Acel SustentoNo ratings yet

- Curriculum Vitae: Navneet ThakurDocument4 pagesCurriculum Vitae: Navneet ThakurNavneet ThakurNo ratings yet

- Amateur Photographer - 15 August 2015Document84 pagesAmateur Photographer - 15 August 2015lasgpoaNo ratings yet

- Submission Letter2006Document1 pageSubmission Letter2006Diyantoro NyoNo ratings yet

- 2022 Global Software Outsourcing Trends and Rates GuideDocument47 pages2022 Global Software Outsourcing Trends and Rates GuideMukeshLagadhirNo ratings yet

- Wireless and Mobile NetworksDocument70 pagesWireless and Mobile NetworksDurga KNo ratings yet

- Call of Duty 2 Read MeDocument11 pagesCall of Duty 2 Read MeMauroNo ratings yet

- Schneider Electric Logic Controller Modicon M251 TM251MESEDocument11 pagesSchneider Electric Logic Controller Modicon M251 TM251MESEmanhtienvuNo ratings yet

- First Semester Examinations 2012/13: COMP213Document9 pagesFirst Semester Examinations 2012/13: COMP213Soo Lian KeiNo ratings yet

- Ommic: Short Form Catalog 2014Document32 pagesOmmic: Short Form Catalog 2014Mara RouaNo ratings yet

- Management and Development Process of Learning Resources - SIMDocument76 pagesManagement and Development Process of Learning Resources - SIMGlezelBayubayNo ratings yet

- A Performance Evaluation of WebRTC Over LTEDocument6 pagesA Performance Evaluation of WebRTC Over LTEedinson cortes cabezasNo ratings yet

- October 2016 Fundamental IT Engineer Examination (Afternoon)Document36 pagesOctober 2016 Fundamental IT Engineer Examination (Afternoon)Phyo PyaeNo ratings yet

- Assignment No. 1 Transcription and Speed Building 1. How Do You Transcribe Laughter? Answer: HR A - F 2. How Do You Past A Transcription Test? AnswerDocument2 pagesAssignment No. 1 Transcription and Speed Building 1. How Do You Transcribe Laughter? Answer: HR A - F 2. How Do You Past A Transcription Test? AnswerJona BustamanteNo ratings yet

- Sharp - 32n-s350 - Chassis - sn-002 - Control UnitDocument8 pagesSharp - 32n-s350 - Chassis - sn-002 - Control UnitMohamad Hafiz Md TahirNo ratings yet

- Strategic Asset Management Plan 2016-2020 PDFDocument64 pagesStrategic Asset Management Plan 2016-2020 PDFghoyarbide100% (1)

- CSS 11 - Week 5Document4 pagesCSS 11 - Week 5GREGORIO ALVAREZNo ratings yet

- Ao1 2024 Qcu Student Application Form For AdmissionDocument3 pagesAo1 2024 Qcu Student Application Form For AdmissionalayonneljohnnNo ratings yet

- Master Pro VOA DjouiniDocument68 pagesMaster Pro VOA DjouinitoufikNo ratings yet

- VoLTE KPI ReportDocument29 pagesVoLTE KPI ReportDee Oye100% (2)

- Bentley MXROAD V8i Fundamental ASTASOFT Com PDFDocument2 pagesBentley MXROAD V8i Fundamental ASTASOFT Com PDFUmesh KumarNo ratings yet

- PDH User GuideDocument526 pagesPDH User GuidePrasad KaleNo ratings yet

- PilotRiv AM AlphaPilot MF User Manual 5-6-2020Document19 pagesPilotRiv AM AlphaPilot MF User Manual 5-6-2020valentin mocanuNo ratings yet

- Veritas Cluster Cheat SheetDocument9 pagesVeritas Cluster Cheat SheetarvindNo ratings yet