PID Report

Uploaded by

Nishiya VijayanCopyright:

Available Formats

PID Report

Uploaded by

Nishiya VijayanCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

PID Report

Uploaded by

Nishiya VijayanCopyright:

Available Formats

PID CONTROLLER

CHAPTER 1 INTRODUCTION

Since the Years 60, the law of Moore predicts that the complexity in terms of builtin circuit transistors doubles every two years, remain verified. The programmable FPGA circuits (Field Programmable Gate Array) didn't escape to this law. Since the first FPGA, developed like an evolution natural of the CPLD (Complex Programmable Logic Devices), these circuits didn't stop winning in complexity and integrated henceforth until one billion of transistors for the most recent generations. This increase of the integration level resulted in a similar growth of the power of calculation of these circuits. The FPGAs have been used then to make the fast samples of ASICs (Application Specific Integrated Circuits) and find since some years their place in many domains of applications. However, the order of the processes industrial requires more and more elements of powerful calculations. This type of order is in the same way in perpetual evolution with the development of the numeric circuits of calculation. Thus, the PID controllers represent the majority of the controllers used in the industrial systems control. Of this fact, it will be necessary to digitalize the PID algorithm. The modern digital control systems require more and more strong and fastest calculation components. This type of elements becomes yet indispensable with the utilization of some new control algorithms like the fuzzy control, the adaptive control, the sliding mode control Although the PID controllers are the oldest they represent the most used controllers in the industrial control systems.

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

PID CONTROLLER

The PID controllers to be implemented in FPGA systems, first needs to digitized. The digital PID controller equations are modeled using Verilog HDL. Several other HDLs like VHDL are also available, the Verilog HDL is selected for its popularity and simplicity. The Verilog HDL supports three distinct modeling methods like dataflow, structural and behavioral. In this design a mixed level modeling of PID controller is proposed.

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

PID CONTROLLER

Chapter 2

PROPOSED MECHANISM

The main objective of our mini project is to develop an efficient and low cost PID controller using Verilog hdl. Our controller may be used to control any parameter of a vehicle such as speed, rear mirror control. Here we take speed, the most sensitive parameter to be controlled using our PID controller. Available controllers are high cost and less effective. Such controllers may not be affordable by small scale industries. Need for a low cost and highly efficient reconfigurable controller arise in the market. The implementation using Verilog

HDL further reduces its complexity by reducing number of programming lines and decreasing the area used thus resulting in high area effectiveness. Our project mainly focuses on: 1. PID Controller 2. Verilog HDL

2.1PID (PROPORTIONAL INTEGTRAL DERIVATIVE) CONTROLLER In the control of dynamic systems, no controller has enjoyed both the success and the failure of the PID control. Of all control design techniques, the PID controller is the most widely used. Over 85% of all dynamic controllers are of the PID variety. There is actually a great variety of types and design methods for the PID

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

PID CONTROLLER

controller. What is a PID controller? The acronym PID stands for Proportional-IntegralDifferential control. Each of these, the P, the I and the D are terms in a control algorithm and each has a special purpose. Sometimes certain of the terms are left out because they are not needed in the control design. This is possible to have a PI, PD or just a P control. It is very rare to have a ID control

2.2VERILOG HDL Verilog digital logic simulator tools allow you to perform the following tasks in the design process without building a hardware prototype: - Determine the feasibility of new design ideas - Try more than one approach to a design problem - Verify functionality - Identify design problems. Coupling HDL Compiler with logic synthesis tools, you can automatically convert an HDL description to a gate-level implementation in a target technology. - HDL descriptions provide technology independent documentation of a design and its functionality. Since the initial HDL design description is technologyindependent, you can use it again to generate the design in a different technology, without having to translate from the original technology.

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

PID CONTROLLER

Chapter 3 Digital PID Controller 3.1 PID CONTROLLER WORKING:

A proportionalintegralderivative controller (PID controller) is a generic control loop feedback mechanism (controller) widely used in industrial control systems a PID is the most commonly used feedback controller. A PID controller calculates an "error" value as the difference between a measured process variable and a desired set point. The controller attempts to minimize the error by adjusting the process control inputs.

The PID controller calculation (algorithm) involves three separate constant parameters, and is accordingly sometimes called three-term control: the proportional, the integral and derivative values, denoted P, I, and D. Heuristically, these values can be interpreted in terms of time: P depends on the present error, I on the accumulation of past errors, and D is a prediction of future errors, based on current rate of change.[1] The weighted sum of these three actions is used to adjust the process via a control element such as the position of a control valve, or the power supplied to a heating element.

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

PID CONTROLLER

In the absence of knowledge of the underlying process, a PID controller has historically been considered to be the best controller.[2] By tuning the three parameters in the PID controller algorithm, the controller can provide control action designed for specific process requirements. The response of the controller can be described in terms of the responsiveness of the controller to an error, the degree to which the controller overshoots the set point and the degree of system oscillation. Note that the use of the PID algorithm for control does not guarantee optimal control of the system or system stability.

Some applications may require using only one or two actions to provide the appropriate system control. This is achieved by setting the other parameters to zero. A PID controller will be called a PI, PD, P or I controller in the absence of the respective control actions. PI controllers are fairly common, since derivative action is sensitive to measurement noise, whereas the absence of an integral term may prevent the system from reaching its target value due to the control action. To improve the speed and minimize the cost while offering clearly good performances, the adopted architecture used includes essentially three

combinational logic multiplier, one subtractor three adders and three registers.

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

PID CONTROLLER

BLOCK DIAGRAM

3.1.1 P controller P controller can eliminate forced oscillations caused by use of on-off controller. However, a second problem arises. There exists now a steady state error. For a properly designed control system steady state error should be zero. With P controller that is possible if: a) K = b) u (t) = u0 The first alternative (K = ) cannot be physically realized in any proportional

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE 7

PID CONTROLLER

band (PB) excerpt for PB = 0 [%] which leads back to on-off controller and forced oscillations. The second alternative (u(t) = u0) implies that it is possible to find u0 at every moment and that it is possible to satisfy condition u(t) = u0 for every given reference value r(t). This can be achieved if integral mode is added to P controller. In general it can be said that P controller cannot stabilize higher order processes. For the 1st order processes, meaning the processes with one energy storage, a large increase in gain can be tolerated. Proportional controller can stabilize only 1st Order unstable process. Changing controller gain K can change closed loop dynamics. A large controller gain will result in control system with: a) Smaller steady state error, i.e. better reference following b) Faster dynamics, i.e. broader signal frequency band of the closed loop system and larger sensitivity with respect to measuring noise c) Smaller amplitude and phase margin The proportional term (P) gives a system control input proportional with the error. Using only P control gives a stationary error in all cases except when the system control input is zero and the system process value equals the desired value. In Figure the stationary error in the system process value appears after a change in the desired value (ref). Using a too large P term gives an unstable system.

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

PID CONTROLLER

3.1.2 PI controller The name comes from the term "manual reset" which marks a manual change of operating point or of "bias" u0 in order to eliminate error. PI controller performs this function automatically. The fact that u0 is replaced with an integral allows PI controller to eliminate steady state error. On the other hand, P controller cannot eliminate steady state error since it does not have any algorithm that would allow for the controller to increase control signal u(t) in order to increase controlled variable y(t) (assuming positive process gain) if in some moment t1 error e(t1) = const. > 0. Proportional control law stays constant in this case and it will not try to change a controlled variable in such manner that control error is diminished. Integral action can occur in the controller only on purpose, by design. Integral action can be noted on the other parts of the control system (actuators, plant etc.). These components may help in diminishing steady state error, but control system designer generally cannot tune this components.

The integral term (I) gives an addition from the sum of the previous errors to the system control input. The summing of the error will continue until the system

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE 9

PID CONTROLLER

process value equals the desired value and this result in no stationary error when the reference is stable. The most common use of the I term is normally together with the P term, called a PI controller. Using only the I term gives slow response and often an oscillating system. Figure shows the step responses to a I and PI controller. As seen the PI controller response have no stationary error and the I controller response is very slow.

3.1.3 PD controller

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

10

PID CONTROLLER

D mode is used when prediction of the error can improve control or when it necessary to stabilize the system. From the frequency characteristic of D element it can be seen that it has phase lead of 90 Thus, D element will move frequency . characteristic of the open loop Go(j further away from the critical point (-1,j0). ) Often derivative is not taken from the error signal but from the system output variable. This is done to avoid effects of the sudden change of the reference input that will cause sudden change in the value of error signal. Sudden change in error signal will cause sudden change in control output. To avoid that it is suitable to design D mode to be proportional to the change of the output variable y (t). If there is a measuring noise present in y(t) will amplify this noise. Noise is usually higher frequency signal, so good remedy for the noise problem is use of low-pass filter in derivative channel that will insure derivative action only in the frequency band of interest and diminish negative effect of D mode on signal noise. The derivative term (D) gives an addition from the rate of change in the error to the system control input. A rapid change in the error will give an addition to the system control input. This improves the response to a sudden change in the system state or reference value. The D term is typically used with the P or PI as a PD or PID controller. A to large D term usually gives an unstable system. Figure shows D and PD controller responses. The response of the PD controller gives a faster rising system process value than the P controller. Note that the D term essentially behaves as a high pass filter on the error signal and thus easily introduces instability in a system and make it more sensitive to noise.

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

11

PID CONTROLLER

3.1.4 PID controller The PID controller performs especially well when the system has first order dynamics (a single pole). Actually, in this case, the P controller is a state-feedback control! In general, for the system with first-order dynamics the PI control is sufficient, and the D is not needed. For the system with essentially second-order dynamics, the PD control corresponds to state feedback. The PID control generally works well for these systems. The PID controller can also work for some systems of higher order. Generally speaking, the derivative term is beneficial when the time constants of the system differ by orders of magnitude. It is sometimes helpful when tight control of higher-order dynamics is required. This is because the higher order dynamics prevent the use of high proportional gain. The D provides damping and speeds up the transient response.

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE 12

PID CONTROLLER

The PID controller, of course, is not the end-all of controllers. Sometimes the controller just wont work very well. The following are cases when the PID control doesnt perform well. In general, these require the use of more sophisticated methods of control. Tight control of higher order process Systems with long delay times. In this case, the derivative term is not helpful. A Smith predictor is often used in this case. Systems with lightly damped oscillatory modes Systems with large uncertainties or variations. Systems with harmonic disturbances Highly coupled multi-input, coordination is important. multi-output systemsespecially where

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

13

PID CONTROLLER

3.1.5 Choice of the controller type

3.1.5.1P controller When P controller is used, large gain is needed to improve steady state error table system do not have a problems when large gain is used. Such systems are systems with one energy storage (1st order capacitive systems). If constant steady state error can be accepted with such processes, than P controller can be used. Small steady state errors can be accepted if sensor will give measured value with error or if importance of measured value is not too great anyway. Example of such system is liquid level control in tanks when exact approximate level of liquid sufficient for the proper plant operation. Also, in cascade control sometime it is not important if there is an error inside inner loop, so P controller can a good solution in such cases. Derivative mode is not required if the process itself is fast or if the control system as whole does not have to be fast in response. Processes of 1st order react immediately on the reference signal change, so it is not necessary to predict error (introduce D mode) or compensate for the steady state error (introduce I mode) if it is possible to achieve satisfactory steady state error using only P controller. 3.1.5.2 PD controller It is well known that thermal processes with good thermal insulation act almost as integrators. Since insulation is good and thermal losses are small, the most significant part of the energy that is led to the system is used temperature rise.

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

14

PID CONTROLLER

Those processes allow for large gains so that integral mode in the controller is not needed. These processes can be described as different connections of thermal energy storages. Thermal energy is shifted from one storage into another. In general, with such processes there is present a process dynamics with large inertia. Since dynamics is slow, derivative mode is required for control of such processes. Integral mode would only already slow dynamics make more slowly. The other reason for using PD controllers in such systems is that is possible to measure temperature with low level of noise in the measured signal. PD controller is often used in control of moving objects such are flying and underwater vehicles, ships, rockets etc. One of the reasons is in stabilizing effect of PD controller on sudden changes in heading variable y(t). Often a "rate gyro" for velocity measurement is used as sensor of heading change of moving object. 3.1.5.3 PI controller PI controllers are the most often type used today in industry. A control without D mode is used when: a) Fast response of the system is not required b) Large disturbances and noise are present during operation of the process c) There is only one energy storage in process (capacitive or inductive) d) There are large transport delays in the system If there are large transport delays present in the controlled process, error prediction is required. However, D mode cannot be used for prediction because every information is delayed till the moment when a change in controlled variable is

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE 15

PID CONTROLLER

recorded. In such cases it is better to predict the output signal using mathematical model of the process in broader sense (process + actuator).

3.1.5.4 PID controller Derivative mode improves stability of the system and enables increase in gain K and decrease in integral time constant Ti, which increases speed of the controller response. PID controller is used when dealing with higher order capacitive processes (processes with more than one energy storage) when their dynamic is not similar to the dynamics of an integrator (like in many thermal processes). PID controller is often used in industry, but also in the control of mobile objects (course and trajectory following included) when stability and precise reference following are required. Conventional autopilots are for the most part PID type controllers.

3.1.6 PID controller parameter and topology identification

Problem of identification of PID controller arises when parameters of an existing controller have to be tuned. Manufacturers usually dont give data about controller structure (serial or parallel), so its structure also has to be determined. Controller parameters have to be manually tuned if they are changed with time (that is often with hydraulic and pneumatic controllers) or because process parameters have changed so the controller does not perform satisfactory anymore. Not knowing the exact structure of the controller is not critical if manual parameter tuning can be done in controlled environment using trial and error method and if rules given in table are observed:

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

16

PID CONTROLLER

CL RESPONSE Kp Ki Kd

RISE TIME Decrease Decrease Small Change

OVERSHOOT Increase Increase Decrease

SETTLING TIME Small Change Increase Decrease

S-S ERROR Decrease Eliminate Small Change

3.2 PID CONTROLLER THEORY:

This section describes the parallel or non-interacting form of the PID controller. For other forms please see the section Alternative nomenclature and PID forms. The PID control scheme is named after its three correcting terms, whose sum constitutes the manipulated variable (MV). The proportional, integral, and derivative terms are summed to calculate the output of the PID controller. Defining as the controller output, the final form of the PID algorithm is:

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

17

PID CONTROLLER

Where, Kp: Proportional gain, a tuning parameter Ki: Integral gain, a tuning parameter Kd: Derivative gain, a tuning parameter e (t): Error t: Time or instantaneous time (the present)

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

18

PID CONTROLLER

Chapter 4 MODELLING OF PID CONTROLLER 4.1 VLSI implementation

Industrial familiarized technology.

Globally used logic.

Original standard IEEE 1364-1995 was approved.

Simple to design (VHDL circuits).

4.2 HISTORY 4.2.1 BEGINNING Verilog was the first modern hardware description language to be invented. It was created by [[Phil Moorby]] and [[Prabhu Goel]] during the winter of 1983/1984. The wording for this process was "Automated Integrated Design Systems" (later renamed to [[Gateway Design Automation]] in 1985) as a hardware modeling language. Gateway Design Automation was purchased by [[Cadence Design Systems]] in 1990. Cadence now has full proprietary rights to Gateway's Verilog and the Verilog-XL, the HDL-simulator that would become the de-facto standard (of Verilog [[logic simulator]]s) for the next decade. Originally,

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE 19

PID CONTROLLER

Verilog was intended to describe and allow simulation; only afterwards was support for synthesis added. Verilog-95 With the increasing success of [[VHDL]] at the time, Cadence decided to make the language available for open [[standardization]]. Cadence transferred Verilog into the public domain under the [http://www.ovi.org/ Open Verilog International] (OVI) (now known as [[Accellera]]) organization. Verilog was later submitted to [[IEEE]] and became IEEE Standard 1364-1995, commonly referred to as Verilog95.

In the same time frame Cadence initiated the creation of [[Verilog-A]] to put standards support behind its analog simulator [[Spectre Circuit Simulator|Spectre]]. Verilog-A was never intended to be a standalone language and is a subset of [[Verilog-AMS]] which encompassed Verilog-95. Verilog 2001 Extensions to Verilog-95 were submitted back to IEEE to cover the deficiencies that users had found in the original Verilog standard. These extensions became [[IEEE]] Standard 1364-2001 known as Verilog-2001.

Verilog-2001 is a significant upgrade from Verilog-95. First, it adds explicit support for (2's complement) signed nets and variables. Previously, code authors had to perform signed operations using awkward bit-level manipulations (for

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE 20

PID CONTROLLER

example, the carry-out bit of a simple 8-bit addition required an explicit description of the Boolean algebra to determine its correct value). The same function under Verilog-2001 can be more succinctly described by one of the built-in operators: +, -, /, *, >>>. A generate/endgenerate normal decision construct operators (similar to VHDL's Using generate/endgenerate) allows Verilog-2001 to control instance and statement instantiation through (case/if/else). generate/endgenerate, Verilog-2001 can instantiate an array of instances, with control over the connectivity of the individual instances. File I/O has been improved by several new system tasks. And finally, a few syntax additions were introduced to improve code readability (e.g. always @*, named parameter override, C-style function/task/module header declaration).

Verilog-2001 is the dominant flavor of Verilog supported by the majority of commercial [[Electronic design automation|EDA]] software packages. Verilog 2005 Not to be confused with [[SystemVerilog]], ''Verilog 2005'' ([[IEEE]] Standard 1364-2005) consists of minor corrections, spec clarifications, and a few new language features (such as the uwire keyword).'''A separate part of the Verilog standard, [[Verilog-AMS]], attempts to integrate analog and mixed signal modeling with traditional Verilog.

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

21

PID CONTROLLER

4.3 DESIGN PROCESSING

Design process consists of four main steps,

Analysis Elaboration Simulation Synthesis

4.3.1 ANALYSIS

Check for syntax and semantic errors Syntax: grammar of the language. semantics: the meaning of the model

Analyze each design unit separately entity declaration architecture body best if each design unit is in a separate file Analyzed design units are placed in a library in an implementation dependent internal form current library is called work

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

22

PID CONTROLLER

4.3.2 ELABORATION

Flattening the design hierarchy create ports create signals and processes within architecture body for each component instance, copy instantiated entity and architecture body repeat recursively bottom out at purely behavioral architecture bodies

Final result of elaboration flat collection of signal nets and processes

4.3.3 SIMULATION

Execution of the processes in the elaborated model Discrete event simulation time advances in discrete steps

when signal values changeevents

A processes is sensitive to events on input signals specified in wait statements resumes and schedules new values on output signals

schedules transactions

event on a signal if new value different from old value

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

23

PID CONTROLLER

4.3.3.1 SIMULATION ALGORITHM

Simulation cycle advance simulation time to time of next transaction for each transaction at this time update signal value event if new value is different from old value for each process sensitive to any of these events, or whose wait for time-out has expired resume execute until a wait statement, then suspend Simulation finishes when there are no further scheduled transactions

4.3.4 SYNTHESIS

Translates register-transfer-level (RTL) design into gate-level netlist Restrictions on coding style for RTL model Tool dependent

4.4 STRUCTURAL MODELING

Logic is described in terms of Verilog gate primitives.

Structural architecture

port maps implements the module as a composition of subsystems

contains

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

24

PID CONTROLLER

signal declarations, for internal interconnections the entity ports are also treated as signals component instances instances of previously declared entity/architecture pairs in component instances connect signals to component ports

4.5 BEHAVIOURAL MODELING

Algorithmically specify the behavior of the design. Architecture body describes an implementation of an entity may be several per entity

Behavioral architecture describes the algorithm performed by the module contains

process statements, each containing

sequential statements, including

signal assignment statements and

wait statements.

4.6 MIXED BEHAVIORAL AND STRUCTURAL MODELING

An architecture can contain both behavioral and structural parts process statements and component instances

collectively called concurrent statements

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

25

PID CONTROLLER

processes can read and assign to signals Example: register-transfer-level (RTL) Model data path described structurally control section described behaviorally

4.7OPERATORS

Operator type ~ & Bitwise | ^

Operator symbols

Operation performed Bitwise NOT (1's complement) Bitwise AND Bitwise OR Bitwise XOR Bitwise XNOR NOT AND OR Reduction AND Reduction NAND Reduction OR Reduction NOR Reduction XOR

26

~^ or ^~ ! Logical && || Reduction & ~& | ~| ^

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

PID CONTROLLER

~^ or ^~ + Arithmetic * / ** > < >= <= ==

Reduction XNOR Addition Subtraction 2's complement Multiplication Division Exponentiation (*Verilog-2001) Greater than Less than Greater than or equal to Less than or equal to Logical equality (bit-value 1'bX is removed from comparison) Logical inequality (bit-value 1'bX is removed from comparison) 4-state logical equality (bit-value 1'bX is taken as literal)

Relational

!=

===

!==

4-state logical inequality (bit-value 1'bX is taken as literal)

Shift

>>

Logical right shift

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

27

PID CONTROLLER

<< >>> <<< Concatenation { , } Replication {n{m}}

Logical left shift Arithmetic right shift (*Verilog-2001) Arithmetic left shift (*Verilog-2001) Concatenation Replicate value m for n times Conditional

Conditional

?:

4.8 Discrete PID

There are three controllers acting in concert. The three controllers are: A proportional (top), An Integral (center), A Derivative (bottom). The proportional, integral and derivative outputs are added together. The PID controller can be thought of as having a transfer function. The PID controller transfer function can be obtained by adding the three terms. PID(s) = Kp + Ki/s+ sKd The transfer function can be combined into a pole-zero form. PID(s) = [sKp + Ki+ s2Kd]/s

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

28

PID CONTROLLER

Since there is a quadratic in the numerator, there are two zeroes in this transfer function as well as the obvious pole at the origin, s = 0. Now, here's a good way to think about the effect of using a PID controller. The PID controller transfer function really adds a pole at the origin, and two zeroes that can be anywhere in the s-plane that the designer wants, depending upon the designer's choice of the three gains. PID(s) = [sKp + Ki+ s2Kd]/s This gives the designer an incredibly large number of possibilities. A standard textbook equation of PID controller is

Which then converted back to discrete equation as

- a form suitable for implementation.

4.9 Verilog Model:

module PID // bit width ? 1 (output signed [15:0] u_out, // input signed [15:0] e_in, //

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE 29

PID CONTROLLER

input clk, input reset); parameter k1=107; // change these values to suit your system parameter k2 = 104; parameter k3 = 2; //reg signed [15:0] u_out; reg signed [15:0] u_prev; reg signed [15:0] e_prev[1:2]; always @ (posedge clk) begin if (reset == 1) begin u_prev <= 0; e_prev[1] <= 0; e_prev[2] <= 0; end else begin e_prev[2] <= e_prev[1]; e_prev[1] <= e_in;

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE 30

PID CONTROLLER

u_prev <= u_out; end end assign u_out = u_prev + k1*e_in - k2*e_prev[1] + k3*e_prev[2]; endmodule module PID_TST; reg clk, reset; reg[15:0] e_in; wire[15:0] u_out; initial begin clk=1'b0; reset = 1'b1; end always #5 clk =~clk; initial begin //#10 reset = 1'b1; //#25 reset = 1'b0;

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE 31

PID CONTROLLER

#15 e_in=16'b0000000000001000; #25 e_in=16'b0000000000000110; end PID p1 (.u_out(u_out), .e_in(e_in), .clk(clk), .reset(reset)); endmodule

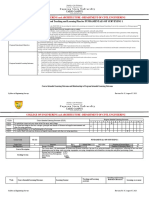

4.10 SPARTAN 3E

The design is targeted to Spartan 3E board and synthesized.

After synthesis, the design summary is obtained. The RTL Schematic is also obtained from synthesis.

The device summary for our code is given below:

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

32

PID CONTROLLER

The device utilization summary of our program in FPGA board comparing to its total memory available is:

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

33

PID CONTROLLER

Chapter 5 RESULTS AND WAVEFORMS

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

34

PID CONTROLLER

Chapter 6 CONCLUSION AND FUTURE WORKS 6.1ADVANTAGES

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE 35

PID CONTROLLER

It is far easier to tune a digital PID controller, than an analog controller. To tune analog controller, requires multi-turn potentiometers and a lot of actual "tweaking" of those pots. Occasionally you need to change out capacitors in an analog controller, too. Once pot values have been fixed, and permanent resistors have been soldered in place, there is amplifier, resistor, and capacitor drift to contend with. Analog systems sometimes require precision-valued components, which are expensive. Its major advantages are: The Verilog code is developed with complex routines and in depth operators to make it simpler. The developed code is proved to area effective when it is synthesized with Xilinx ISE.

The design uses a single global clock. The total gate count is only 1,832 and it uses only 83 memory slices in FPGA out of 2844.

6.2CONCLUSION: A digital PID controller implemented in Verilog HDL is a configurable controller in terms of bit-width and parallelism.

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE 36

PID CONTROLLER

Implementing PID controllers on FPGAs features speed, accuracy, power, compactness, and cost improvement over other digital implementation techniques. The Verilog code is developed with complex routines and in depth operators to make it simpler. The developed code is proved to area effective when it is synthesized with Xilinx ISE. The design uses a single global clock. The total gate count is only 1,832 and it uses only 83 memory slices in FPGA out of 2844. We developed a Verilog code which is more simpler and consumes less area which in turn consumes less power*.

6.3FUTURE WORKS:

In Future work we have planned to identify suitable plant to control and tune the gains accordingly. Also we like to implement interfacing modules along with this.

Chapter 7 REFERENCE

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

37

PID CONTROLLER

1.R. Gao, D. Xu,J. P. Bentley, Recongurable hardware implementation of an improved parallel architecture for MPEG-4 motion estimation in mobile applications,IEEE Transactions on Consumer Electronics, V49, N4,Nov 08. 2. Verilog HDL-Samir Palnitkar 3. www.asic-world.com

SREE NARAYANA GURUKULAM COLLEGE OF ENGINEERING DEPARTMENT OF ECE

38

You might also like

- Boiler Flow Control Using PID and Fuzzy Logic ControllerNo ratings yetBoiler Flow Control Using PID and Fuzzy Logic Controller5 pages

- The Working Principle of A PID Controller For BeginnersNo ratings yetThe Working Principle of A PID Controller For Beginners15 pages

- PID Controller Working Principle Explained For BeginnersNo ratings yetPID Controller Working Principle Explained For Beginners6 pages

- PID Controller Design: Itce470: Control Sysytem Experiment No. 4No ratings yetPID Controller Design: Itce470: Control Sysytem Experiment No. 45 pages

- Design and Simulation of PID Controller Using FPGANo ratings yetDesign and Simulation of PID Controller Using FPGA5 pages

- Comparison of Control System Using PLC & PIDNo ratings yetComparison of Control System Using PLC & PID6 pages

- GAIN SCHEDULING CONTROLLER DESIGN FOR AN ELECTRIC DRIVE Final PDFNo ratings yetGAIN SCHEDULING CONTROLLER DESIGN FOR AN ELECTRIC DRIVE Final PDF6 pages

- 27.ijaest Vol No 8 Issue No 2 DC Motor Control Using Fuzzy Logic Controller 291 296No ratings yet27.ijaest Vol No 8 Issue No 2 DC Motor Control Using Fuzzy Logic Controller 291 2966 pages

- Design and Simulation of DA Based PID Controller Using Verilog CodingNo ratings yetDesign and Simulation of DA Based PID Controller Using Verilog Coding6 pages

- Pseudo-PID Controller: Design, Tuning and ApplicationsNo ratings yetPseudo-PID Controller: Design, Tuning and Applications6 pages

- How Does A PID Controller Work - Structure & Tuning MethodsNo ratings yetHow Does A PID Controller Work - Structure & Tuning Methods12 pages

- A Design of A PID Self-Tuning Controller Using PDFNo ratings yetA Design of A PID Self-Tuning Controller Using PDF11 pages

- Universidad Politécnica Salesiana: Sistema de Control en Tiempo ContinuoNo ratings yetUniversidad Politécnica Salesiana: Sistema de Control en Tiempo Continuo6 pages

- PID Controllers and Algorithms: Selection and Design Techniques Applied in Mechatronics Systems Design - Part IINo ratings yetPID Controllers and Algorithms: Selection and Design Techniques Applied in Mechatronics Systems Design - Part II13 pages

- Temperature Monitoring System Based On PLCNo ratings yetTemperature Monitoring System Based On PLC8 pages

- Instruction Manual: Pid Based Pressure Loop TrainerNo ratings yetInstruction Manual: Pid Based Pressure Loop Trainer28 pages

- GUI Based Control System Analysis Using PID Controller For EducationNo ratings yetGUI Based Control System Analysis Using PID Controller For Education11 pages

- A Design of A PID Self-Tuning Controller Using Labview: Mohammad A. K. Alia, Tariq M. Younes, Shebel A. AlsabbahNo ratings yetA Design of A PID Self-Tuning Controller Using Labview: Mohammad A. K. Alia, Tariq M. Younes, Shebel A. Alsabbah11 pages

- Design of Pid Controller For PLC: J. Paulusová, L. KörösiNo ratings yetDesign of Pid Controller For PLC: J. Paulusová, L. Körösi8 pages

- Thermal Characteristics of Pid Controller Water HeaterNo ratings yetThermal Characteristics of Pid Controller Water Heater10 pages

- Analysis of Speed Control of DC Motor - A Review StudyNo ratings yetAnalysis of Speed Control of DC Motor - A Review Study6 pages

- A Comprehensive Analysis of PID Control ApplicatioNo ratings yetA Comprehensive Analysis of PID Control Applicatio7 pages

- International Journal of Engineering Research and Development (IJERD)No ratings yetInternational Journal of Engineering Research and Development (IJERD)7 pages

- Real Time Speed Control of DC Motor With Unknown Transfer Function Through PIDNo ratings yetReal Time Speed Control of DC Motor With Unknown Transfer Function Through PID6 pages

- Tuning of An Optimal PID Controller With Iterative Feedback Tuning Method For DC MotorNo ratings yetTuning of An Optimal PID Controller With Iterative Feedback Tuning Method For DC Motor5 pages

- DC Motor Position Control Using Fuzzy Proportional-Derivative Controllers With Different Defuzzification MethodsNo ratings yetDC Motor Position Control Using Fuzzy Proportional-Derivative Controllers With Different Defuzzification Methods11 pages

- Class Test 2 Time: 50 Minute Max - Marks:20 Marks: Part ANo ratings yetClass Test 2 Time: 50 Minute Max - Marks:20 Marks: Part A1 page

- Programming Experiments Using 8051 SimulatorNo ratings yetProgramming Experiments Using 8051 Simulator4 pages

- Fifth Semester Branch: Electronics and Communication Engineering Ec010 502-Control Systems Time: 1.5 HoursNo ratings yetFifth Semester Branch: Electronics and Communication Engineering Ec010 502-Control Systems Time: 1.5 Hours2 pages

- Presented by Nishiya Vijayan S1 Mtech SngceNo ratings yetPresented by Nishiya Vijayan S1 Mtech Sngce22 pages

- GUIDEBOOK FOR ALL NTA INST New 2023 - 2024 - CompressedNo ratings yetGUIDEBOOK FOR ALL NTA INST New 2023 - 2024 - Compressed160 pages

- Created Unique Architectural Designs According To Clients DemandNo ratings yetCreated Unique Architectural Designs According To Clients Demand3 pages

- Investigation To Failure Analysis of Rolling Element Bearing With Various Defects (Bearing)No ratings yetInvestigation To Failure Analysis of Rolling Element Bearing With Various Defects (Bearing)12 pages

- Statement of Purpose: Heramb Sakpal Master's in Civil EngineeringNo ratings yetStatement of Purpose: Heramb Sakpal Master's in Civil Engineering1 page

- INSWAREB Develops: No-Aggregate Concrete (NAC)No ratings yetINSWAREB Develops: No-Aggregate Concrete (NAC)4 pages

- Akhtar Mahmood: Linguistic Profile: Urdu Excellent - Arabic and English FunctionalNo ratings yetAkhtar Mahmood: Linguistic Profile: Urdu Excellent - Arabic and English Functional2 pages

- Building Services Engineering Dissertation Examples100% (1)Building Services Engineering Dissertation Examples6 pages

- Job Order # 12-18 (Air Tank For Aramco Pre-Aduti)No ratings yetJob Order # 12-18 (Air Tank For Aramco Pre-Aduti)3 pages

- Monolithic Structure Formwork System (For Submittal)No ratings yetMonolithic Structure Formwork System (For Submittal)19 pages

- W1 - The Scope of Software Engineering PDFNo ratings yetW1 - The Scope of Software Engineering PDF11 pages

- ECM 366 Basic Civil Engineering QuantitiesNo ratings yetECM 366 Basic Civil Engineering Quantities65 pages

- Fundamentals in Surveying 1 August 2023 Revised SyllabiNo ratings yetFundamentals in Surveying 1 August 2023 Revised Syllabi8 pages

- Engineers Australia Stage 2 Competency StandardNo ratings yetEngineers Australia Stage 2 Competency Standard7 pages

- [FREE PDF sample] Essential Architecture and Principles of Systems Engineering 1st Edition C.E. Dickerson ebooksNo ratings yet[FREE PDF sample] Essential Architecture and Principles of Systems Engineering 1st Edition C.E. Dickerson ebooks50 pages

- Mechanical Properties of Polypropylene Reinforced Paver BlockNo ratings yetMechanical Properties of Polypropylene Reinforced Paver Block30 pages

- CUSA Technical Report 12 12 12 - 201212131618551955 PDFNo ratings yetCUSA Technical Report 12 12 12 - 201212131618551955 PDF55 pages

- Boiler Flow Control Using PID and Fuzzy Logic ControllerBoiler Flow Control Using PID and Fuzzy Logic Controller

- The Working Principle of A PID Controller For BeginnersThe Working Principle of A PID Controller For Beginners

- PID Controller Working Principle Explained For BeginnersPID Controller Working Principle Explained For Beginners

- PID Controller Design: Itce470: Control Sysytem Experiment No. 4PID Controller Design: Itce470: Control Sysytem Experiment No. 4

- Design and Simulation of PID Controller Using FPGADesign and Simulation of PID Controller Using FPGA

- GAIN SCHEDULING CONTROLLER DESIGN FOR AN ELECTRIC DRIVE Final PDFGAIN SCHEDULING CONTROLLER DESIGN FOR AN ELECTRIC DRIVE Final PDF

- 27.ijaest Vol No 8 Issue No 2 DC Motor Control Using Fuzzy Logic Controller 291 29627.ijaest Vol No 8 Issue No 2 DC Motor Control Using Fuzzy Logic Controller 291 296

- Design and Simulation of DA Based PID Controller Using Verilog CodingDesign and Simulation of DA Based PID Controller Using Verilog Coding

- Pseudo-PID Controller: Design, Tuning and ApplicationsPseudo-PID Controller: Design, Tuning and Applications

- How Does A PID Controller Work - Structure & Tuning MethodsHow Does A PID Controller Work - Structure & Tuning Methods

- A Design of A PID Self-Tuning Controller Using PDFA Design of A PID Self-Tuning Controller Using PDF

- Universidad Politécnica Salesiana: Sistema de Control en Tiempo ContinuoUniversidad Politécnica Salesiana: Sistema de Control en Tiempo Continuo

- PID Controllers and Algorithms: Selection and Design Techniques Applied in Mechatronics Systems Design - Part IIPID Controllers and Algorithms: Selection and Design Techniques Applied in Mechatronics Systems Design - Part II

- Instruction Manual: Pid Based Pressure Loop TrainerInstruction Manual: Pid Based Pressure Loop Trainer

- GUI Based Control System Analysis Using PID Controller For EducationGUI Based Control System Analysis Using PID Controller For Education

- A Design of A PID Self-Tuning Controller Using Labview: Mohammad A. K. Alia, Tariq M. Younes, Shebel A. AlsabbahA Design of A PID Self-Tuning Controller Using Labview: Mohammad A. K. Alia, Tariq M. Younes, Shebel A. Alsabbah

- Design of Pid Controller For PLC: J. Paulusová, L. KörösiDesign of Pid Controller For PLC: J. Paulusová, L. Körösi

- Thermal Characteristics of Pid Controller Water HeaterThermal Characteristics of Pid Controller Water Heater

- Analysis of Speed Control of DC Motor - A Review StudyAnalysis of Speed Control of DC Motor - A Review Study

- A Comprehensive Analysis of PID Control ApplicatioA Comprehensive Analysis of PID Control Applicatio

- International Journal of Engineering Research and Development (IJERD)International Journal of Engineering Research and Development (IJERD)

- Real Time Speed Control of DC Motor With Unknown Transfer Function Through PIDReal Time Speed Control of DC Motor With Unknown Transfer Function Through PID

- Tuning of An Optimal PID Controller With Iterative Feedback Tuning Method For DC MotorTuning of An Optimal PID Controller With Iterative Feedback Tuning Method For DC Motor

- DC Motor Position Control Using Fuzzy Proportional-Derivative Controllers With Different Defuzzification MethodsDC Motor Position Control Using Fuzzy Proportional-Derivative Controllers With Different Defuzzification Methods

- Control System: Fundamentals and ApplicationsFrom EverandControl System: Fundamentals and Applications

- The Essential Guide to Internet of Things (IoT)From EverandThe Essential Guide to Internet of Things (IoT)

- Class Test 2 Time: 50 Minute Max - Marks:20 Marks: Part AClass Test 2 Time: 50 Minute Max - Marks:20 Marks: Part A

- Fifth Semester Branch: Electronics and Communication Engineering Ec010 502-Control Systems Time: 1.5 HoursFifth Semester Branch: Electronics and Communication Engineering Ec010 502-Control Systems Time: 1.5 Hours

- GUIDEBOOK FOR ALL NTA INST New 2023 - 2024 - CompressedGUIDEBOOK FOR ALL NTA INST New 2023 - 2024 - Compressed

- Created Unique Architectural Designs According To Clients DemandCreated Unique Architectural Designs According To Clients Demand

- Investigation To Failure Analysis of Rolling Element Bearing With Various Defects (Bearing)Investigation To Failure Analysis of Rolling Element Bearing With Various Defects (Bearing)

- Statement of Purpose: Heramb Sakpal Master's in Civil EngineeringStatement of Purpose: Heramb Sakpal Master's in Civil Engineering

- Akhtar Mahmood: Linguistic Profile: Urdu Excellent - Arabic and English FunctionalAkhtar Mahmood: Linguistic Profile: Urdu Excellent - Arabic and English Functional

- Building Services Engineering Dissertation ExamplesBuilding Services Engineering Dissertation Examples

- Monolithic Structure Formwork System (For Submittal)Monolithic Structure Formwork System (For Submittal)

- Fundamentals in Surveying 1 August 2023 Revised SyllabiFundamentals in Surveying 1 August 2023 Revised Syllabi

- [FREE PDF sample] Essential Architecture and Principles of Systems Engineering 1st Edition C.E. Dickerson ebooks[FREE PDF sample] Essential Architecture and Principles of Systems Engineering 1st Edition C.E. Dickerson ebooks

- Mechanical Properties of Polypropylene Reinforced Paver BlockMechanical Properties of Polypropylene Reinforced Paver Block

- CUSA Technical Report 12 12 12 - 201212131618551955 PDFCUSA Technical Report 12 12 12 - 201212131618551955 PDF