Datasheet 555

Datasheet 555

Uploaded by

Roy Alejandro Vega MendozaCopyright:

Available Formats

Datasheet 555

Datasheet 555

Uploaded by

Roy Alejandro Vega MendozaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Datasheet 555

Datasheet 555

Uploaded by

Roy Alejandro Vega MendozaCopyright:

Available Formats

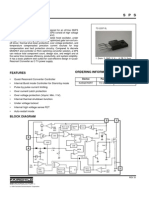

ADVANCED LINEAR DEVICES, INC.

ALD555 HIGH SPEED CMOS TIMER

GENERAL DESCRIPTION The ALD555 timer is a high performance monolithic timing circuit built with advanced silicon gate CMOS technology. It offers the benefits of high input impedance, thereby allowing smaller timing capacitors and longer timing cycle; high speed, with typical cycle time of 500ns; low power dissipation for battery operated environment; reduced supply current spikes, allowing smaller and lower cost decoupling capacitors. It is capable of producing accurate time delays and oscillations in both monostable and astable operation. It operates in the one-shot (monostable) mode or 50% duty cycle free running oscillation mode with a single resistor and one capacitor. The inputs and outputs are fully compatible with CMOS, NMOS or TTL logic. There are three matched internal resistors (approximately 200K each) that set the threshold and trigger levels at two-thirds and one-third respectively of V +. These levels can be adjusted by using the control terminal (pin 5). When the trigger input is below the trigger level, the output is in the high state and sourcing 2mA. When threshold input is above the threshold level at the same time the trigger input is above the trigger level, the internal flip-flop is reset, the output goes to the low state and sinks up to 10mA. The reset input overrides all other inputs and when it is active (reset voltage less than 1V), the output is in the low state. FEATURES Functional equivalent to NE555 with greatly expanded high and low frequency ranges High speed, low power, monolithic CMOS technology Low supply current 100A typical Extremely low trigger, threshold and reset currents -- 1pA typical High speed operation -- 2MHz oscillation Low operating supply voltage 2 to 12V Operates in both monostable and astable modes Fixed 50% duty cycle or adjustable duty cycle CMOS, NMOS and TTL compatible input/output High discharge sinking current (80mA) Low supply current spikes ORDERING INFORMATION

Operating Temperature Range * -55C to +125C 0C to +70C 0C to +70C 8-Pin CERDIP Package ALD555 DA 8-Pin Small Outline Package (SOIC) ALD555 SA 8-Pin Plastic Dip Package ALD555 PA

APPLICATIONS

High speed one-shot (monostable)

pulse generation Precision timing Sequential timing Long delay timer Pulse width and pulse position modulation Missing pulse detector Frequency divider

PIN CONFIGURATION

GROUND TRIGGER OUTPUT RESET

1 2 3 4

8 7 6 5

V+ DISCHARGE THRESHOLD CONTROL

TOP VIEW DA, PA, SA PACKAGE

BLOCK DIAGRAM

V+ (8)

RESET (4)

THRESHOLD (6) CONTROL (5) R R S DISCHARGE (7) R OUTPUT (3)

TRIGGER (2) R

GND (1)

* Contact factory for industrial temperature range

1998 Advanced Linear Devices, Inc. 415 Tasman Drive, Sunnyvale, California 94089 -1706 Tel: (408) 747-1155 Fax: (408) 747-1286 http://www.aldinc.com

ABSOLUTE MAXIMUM RATINGS

Supply voltage, V+ Input voltage range Power dissipation Operating temperature range Storage temperature range Lead temperature, 10 seconds 13.2V -0.3V to V+ +0.3V 600 mW 0C to +70C -55C to +125C -65C to +150C +260C

PA,SA package DA package

OPERATING ELECTRICAL CHARACTERISTICS TA = 25 oC V + = +5V unless otherwise specified

Parameter Supply Voltage Supply Current Timing error / Astable mode Initial Accuracy Drift with Temperature 1 Drift with Supply Voltage 1 Threshold Voltage Trigger Voltage Trigger Current 2 Reset Voltage Reset Current 2 Threshold Current 2 Control Voltage Level Output Voltage Drop (Low) Output Voltage Drop (High) Rise Time of Output 1 Fall Time of Output 1 Discharge Transistor Leakage Current Discharge Voltage Drop

Symbol

V+ IS

Min

2

Typ

Max

12

Unit

V A

Test Conditions

100

180

Outputs Unloaded

terr t/T t/V+ VTH VTRIG ITRIG VRST IRST ITH VCONT VOL VOH tr tf IDL 3.273 0.4 3.273 1.607

1.0 10.0 0.1 3.333 1.667 .001 0.7 .001 .001 3.333 0.2

2.2

% ppm/C %/V

C = 0.1F RA = 1K RB = 1K

3.393 1.737 0.2 1.0 0.2 0.2 3.393 0.4 4.2

V V nA V nA nA V V V ns ns nA ISINK = 10mA ISOURCE = -2mA RL = 10M CL = 10pF

15 10 .01

30 20

VDISC

0.5 0.2

1.0 0.4

V V

I DISCHARGE = 80mA I DISCHARGE = 30mA RA = 470 RB = 200 CT = 200pF

Maximum Frequency Astable Mode

1 2

fMAX

1.4

MHz

Notes:

Sample tested parameters. Consists of junction leakage currents with strong temperature dependence.

ALD555

Advanced Linear Devices

9-2

TYPICAL PERFORMANCE CHARACTERISTICS

DISCHARGE OUTPUT SINK CURRENT AS A FUNCTION OF DISCHARGE LOW VOLTAGE

DISCHARGE SINK CURRENT (mA)

100

MINIMUM PULSE WIDTH REQUIRED FOR TRIGGERING

800

MINIMUM PULSE WIDTH (ns)

50 20 10 5.0 2.0 1.0 0.5 0.2 0.1 0.01

TA = 25C

V+ = 12V

V+ = 5V V+ = 2V

700 600 500 400 300 200 100 0 0

TA = 25C

V+ = 2V V+ = 5V V+= 12V

0.02

0.05

0.1

0.2

0.5

1.0

DISCHARGE LOW VOLTAGE (V)

10

20

30

40

LOWEST VOLTAGE LEVEL OF TRIGGER PULSE ( % V+)

FREE RUNNING FREQUENCY AS A FUNCTION OF RA, RB AND C

10 mF

FREQUENCY CHANGE IN THE ASTABLE MODE AS A FUNCTION OF SUPPLY VOLTAGE

+4

100 F

( RA - 2RB )

FREQUENCY CHANGE (%)

1 mF

TA = 25C

+3 +2 +1 0 -1 -2 -3 -4

CAPACITANCE

10 F 1 F 100 nF 10 nF 1 nF 100 pF 0.1 1.0 10 100 1K 10K 100K 1M 10M 100M FREQUENCY (Hz)

10

10

0M

1M

10

10

0K

1K

10

12

SUPPLY VOLTAGE (V)

TIME DELAY IN THE MONOSTABLE MODE AS A FUNCTION OF RA AND C

10 mF 1 mF 100 F

SUPPLY CURRENT AS A FUNCTION OF SUPPLY VOLTAGE

200 180

TA = 25C

RA

SUPPLY CURRENT (uA)

160 140 120 100 80 60 40 20 0

CAPACITANCE

1K K 0K

10 F 1 F 100 nF 10 nF 1 nF 100 pF

TA = - 40C TA = + 20C TA = + 85C

10

10

M 0M

1G

1M

10

10

100ns 1s 10s 100s 1ms 10ms 100ms 1s

10s

100s

10

12

TIME DELAY

SUPPLY VOLTAGE (V)

ALD555

Advanced Linear Devices

9-3

TYPICAL PERFORMANCE CHARACTERISTICS

OUTPUT SINK CURRENT AS A FUNCTION OF OUTPUT VOLTAGE

50 20 10 5.0 2.0 1.0 0.5 0.2 0.1 0.01 0.02 0.05 0.1 0.2 0.5 1.0 OUTPUT VOLTAGE (V) V+ = 2V TA = 25C V+ = 12V

OUTPUT SOURCE CURRENT (mA)

OUTPUT SOURCE CURRENT AS A FUNCTION OF OUTPUT VOLTAGE

-0.1 -0.2 -0.5 -1.0 -2.0 -5.0 -10 -20 -50 -100 -1.0 -0.5 -0.2 -0.1 -0.05 -0.02 -0.01 V+ = 2V V+ = 5V V+ = 12V

100

OUTPUT SINK CURRENT (mA)

V+ = 5V

OUTPUT VOLTAGE (V) (REFERENCED TO V+)

TYPICAL APPLICATIONS

ASTABLE MODE OPERATION 50% DUTY CYCLE

V+

ASTABLE MODE OPERATION (FREE RUNNING OSCILLATOR)

V+

1 2 R 3 V+ 4

8 0.1F 7 6 C 5

1 2 3 V+ 4

8 RA 7 RB 6 C 5 0.1F

Frequency f = 1/ (1.4 RC)

Frequency f = 1.46 / (RA + 2RB)C Duty Cycle DC = RB / (RA + 2RB)

MONOSTABLE MODE OPERATION (ONE SHOT PULSE) Pulse Delay td = 1.1 RC

V+

1 TRIGGER INPUT DELAYED PULSE OUTPUT RESET 2 3 4

8 R 7 6 C 5

0.1F

ALD555

Advanced Linear Devices

9-4

You might also like

- STR W6735Document14 pagesSTR W6735proctepNo ratings yet

- Document - SG3525A DDocument10 pagesDocument - SG3525A Donlinerahul823405No ratings yet

- 7555 CNDocument9 pages7555 CNdsdsds4No ratings yet

- LTC 1625Document24 pagesLTC 1625Sakura KunNo ratings yet

- Regulating Pulse Width Modulators: Features DescriptionDocument7 pagesRegulating Pulse Width Modulators: Features DescriptionkkaytugNo ratings yet

- SFA350 :: ROAL Living EnergyDocument6 pagesSFA350 :: ROAL Living EnergyroalscribdNo ratings yet

- NE/SE5560 Switched-Mode Power Supply Control Circuit: Description Pin ConfigurationDocument16 pagesNE/SE5560 Switched-Mode Power Supply Control Circuit: Description Pin ConfigurationkokiskoNo ratings yet

- SG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorDocument10 pagesSG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorJayesh SuryavanshiNo ratings yet

- Sg3525a DDocument10 pagesSg3525a DRiz WanNo ratings yet

- Fan 7530Document20 pagesFan 7530aldo_suviNo ratings yet

- SG2525A SG3525A: Regulating Pulse Width ModulatorsDocument12 pagesSG2525A SG3525A: Regulating Pulse Width ModulatorsMagelicanNo ratings yet

- High Speed-10 Mbit/S Logic Gate Optocouplers: Single-Channel Dual-Channel 6N137 Hcpl-2630 Hcpl-2601 Hcpl-2631 Hcpl-2611Document11 pagesHigh Speed-10 Mbit/S Logic Gate Optocouplers: Single-Channel Dual-Channel 6N137 Hcpl-2630 Hcpl-2601 Hcpl-2631 Hcpl-2611Filip SavicNo ratings yet

- 0.5 Amp Output Current IGBT Gate Drive Optocoupler: HCPL-3150Document16 pages0.5 Amp Output Current IGBT Gate Drive Optocoupler: HCPL-3150dhaka0001d2451No ratings yet

- L9230Document25 pagesL9230Juan LouroNo ratings yet

- Photo SCR Optocouplers: Description 4N39 4N40Document9 pagesPhoto SCR Optocouplers: Description 4N39 4N40ramiro_vicente_6No ratings yet

- NTE955MC Integrated Circuit CMOS Timing Circuit: DescriptionDocument7 pagesNTE955MC Integrated Circuit CMOS Timing Circuit: DescriptionManuel ReynosoNo ratings yet

- OL2068LFDocument9 pagesOL2068LFdieselroarmt875bNo ratings yet

- Datasheet STR 6757Document11 pagesDatasheet STR 6757Walter CarreroNo ratings yet

- Ka 5q0765rt (Sps Fairchild)Document10 pagesKa 5q0765rt (Sps Fairchild)Cristian Steven RuizNo ratings yet

- STR W6735 DatasheetDocument13 pagesSTR W6735 DatasheetloagerNo ratings yet

- 5 M 0965 QT UDocument12 pages5 M 0965 QT UcesarlcaNo ratings yet

- SSC2001S Application NoteDocument18 pagesSSC2001S Application NoteGerardo Mendez CamarilloNo ratings yet

- LM5020 100V Current Mode PWM Controller: General Description FeaturesDocument13 pagesLM5020 100V Current Mode PWM Controller: General Description FeaturesAlonso CoradoNo ratings yet

- Off-Line Quasi-Resonant Switching Regulators: STR-X6759NDocument9 pagesOff-Line Quasi-Resonant Switching Regulators: STR-X6759Nch3o10836266No ratings yet

- 4N39 40Document8 pages4N39 40cagh21No ratings yet

- RCB1200 :: ROAL Living EnergyDocument10 pagesRCB1200 :: ROAL Living EnergyroalscribdNo ratings yet

- MC 34152Document12 pagesMC 34152dcastrelos2000No ratings yet

- Transition-Mode PFC Controller: 1 FeaturesDocument17 pagesTransition-Mode PFC Controller: 1 Featuresadriancho66No ratings yet

- S Feature D Escriptio: LTC1255 Dual 24V High-Side MOSFET DriverDocument16 pagesS Feature D Escriptio: LTC1255 Dual 24V High-Side MOSFET DriverMuhammed AsimNo ratings yet

- UC3842Document8 pagesUC3842miguelarielfrancoNo ratings yet

- CS2841BD14Document10 pagesCS2841BD14giapy0000No ratings yet

- Synchronous Presettable 4-Bit Counter: M B Order CodesDocument12 pagesSynchronous Presettable 4-Bit Counter: M B Order CodesMarimuthu RajNo ratings yet

- Inverter For Air Conditioner IGBT/Power MOS FET Gate Drive Industrial InverterDocument9 pagesInverter For Air Conditioner IGBT/Power MOS FET Gate Drive Industrial InverterFurqan MemonNo ratings yet

- DC/DC C 28 V I: Onverters OLT NputDocument21 pagesDC/DC C 28 V I: Onverters OLT Nputnpadma_6No ratings yet

- Dap006 Dap6a DataDocument15 pagesDap006 Dap6a DataluisfeipezzNo ratings yet

- NCP1337 PWM Current Mode Controller For Free Running Quasi Resonant OperationDocument14 pagesNCP1337 PWM Current Mode Controller For Free Running Quasi Resonant Operationcorrales_86No ratings yet

- RCB600 :: ROAL Living EnergyDocument10 pagesRCB600 :: ROAL Living EnergyroalscribdNo ratings yet

- Uc 3525 ADocument17 pagesUc 3525 AespaguetesNo ratings yet

- Quasi-Resonant Topology Primary Switching Regulators: STR-W6735Document13 pagesQuasi-Resonant Topology Primary Switching Regulators: STR-W6735perro sNo ratings yet

- MC34067 PDFDocument16 pagesMC34067 PDFwj18868908No ratings yet

- LM350 DatasheetDocument12 pagesLM350 DatasheetOmarVelasquezC.No ratings yet

- DatasheetDocument13 pagesDatasheetebertecnicoNo ratings yet

- Iramx 16 Up 60 ADocument17 pagesIramx 16 Up 60 AJandfor Tansfg ErrottNo ratings yet

- Lm301 Alta PerformanceDocument8 pagesLm301 Alta PerformanceJohn PachecoNo ratings yet

- DDP400 Sealed :: ROAL Living EnergyDocument8 pagesDDP400 Sealed :: ROAL Living EnergyroalscribdNo ratings yet

- P1027P65 (SMPS)Document30 pagesP1027P65 (SMPS)Jesus Silva67% (3)

- 7 M 0880Document18 pages7 M 0880Mahmoued YasinNo ratings yet

- MFA350 :: ROAL Living EnergyDocument6 pagesMFA350 :: ROAL Living EnergyroalscribdNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Analog Dialogue Volume 46, Number 1: Analog Dialogue, #5From EverandAnalog Dialogue Volume 46, Number 1: Analog Dialogue, #5Rating: 5 out of 5 stars5/5 (1)

- Boat Maintenance Companions: Electrics & Diesel Companions at SeaFrom EverandBoat Maintenance Companions: Electrics & Diesel Companions at SeaNo ratings yet

- Analog Dialogue, Volume 48, Number 1: Analog Dialogue, #13From EverandAnalog Dialogue, Volume 48, Number 1: Analog Dialogue, #13Rating: 4 out of 5 stars4/5 (1)

- Some Power Electronics Case Studies Using Matlab Simpowersystem BlocksetFrom EverandSome Power Electronics Case Studies Using Matlab Simpowersystem BlocksetNo ratings yet

- A Highly-Efficient Multi-Band Multi-Mode Digital Quadrature Transmitter With 2D Pre-DistortionDocument4 pagesA Highly-Efficient Multi-Band Multi-Mode Digital Quadrature Transmitter With 2D Pre-DistortionSMBNo ratings yet

- VN/VP13 Series Application Note: Circuit Description/Design ConsiderationsDocument4 pagesVN/VP13 Series Application Note: Circuit Description/Design ConsiderationsGerardo TexisNo ratings yet

- 300-GHz CMOS QPSK Transmitter For 30-Gbps Dielectric Waveguide CommunicationDocument4 pages300-GHz CMOS QPSK Transmitter For 30-Gbps Dielectric Waveguide CommunicationMarcoNo ratings yet

- 17 A - Nano-Watt - MOS-Only - Voltage - Reference - With - High-Slope - PTAT - Voltage - GeneratorsDocument5 pages17 A - Nano-Watt - MOS-Only - Voltage - Reference - With - High-Slope - PTAT - Voltage - GeneratorsBalaramamurty SannidhiNo ratings yet

- Design of A Low Power Dynamic Comparator in 180nm CMOS TechnologyDocument6 pagesDesign of A Low Power Dynamic Comparator in 180nm CMOS TechnologyVishnu VardhanNo ratings yet

- Infineon IRS218!4!44 and IR218 4 44 Comparison An v01 00 enDocument6 pagesInfineon IRS218!4!44 and IR218 4 44 Comparison An v01 00 enNini FarribasNo ratings yet

- Class17 18 IBIS Io Buffer ClassDocument66 pagesClass17 18 IBIS Io Buffer ClassdeepakNo ratings yet

- A Cmos Low Noise Amplifier Design For 433mhz ReceiverDocument4 pagesA Cmos Low Noise Amplifier Design For 433mhz ReceiverDuc DucNo ratings yet

- Tle5205 2Document23 pagesTle5205 2Richard MachadoNo ratings yet

- 65-nm CMOS TECHNOLOGYDocument32 pages65-nm CMOS TECHNOLOGYsumithmhNo ratings yet

- SI4d SubstrateDocument23 pagesSI4d Substratekeynote76No ratings yet

- FG 7002 CDocument28 pagesFG 7002 CAlejandro Alfredo Fernandez AntezanaNo ratings yet

- Logic Design Styles: Dinesh SharmaDocument22 pagesLogic Design Styles: Dinesh SharmasunilsheelavantNo ratings yet

- Speed Compact Priority EncoderDocument4 pagesSpeed Compact Priority EncoderNeha TripathiNo ratings yet

- Analog Digital Bicmos RealizationDocument63 pagesAnalog Digital Bicmos RealizationSravana JyothiNo ratings yet

- CMOS Processing TechnologyDocument35 pagesCMOS Processing Technologysneha rNo ratings yet

- 15 A - Cryo-CMOS - Voltage - Reference - in - 28-nm - FDSOIDocument4 pages15 A - Cryo-CMOS - Voltage - Reference - in - 28-nm - FDSOIBalaramamurty SannidhiNo ratings yet

- Dheeraj ReportDocument15 pagesDheeraj ReportGirdhar Gopal GautamNo ratings yet

- VLSI Design REC702Document2 pagesVLSI Design REC702Abhimanyu YadavNo ratings yet

- 74HCT14 Hex Schmitt Trigger Inverter With LSTTL Compatible InputsDocument8 pages74HCT14 Hex Schmitt Trigger Inverter With LSTTL Compatible InputsEloyNo ratings yet

- Module3 - SPICE and CMOS VTCDocument23 pagesModule3 - SPICE and CMOS VTCdilshan singhNo ratings yet

- Electrolyte-Gated Transistors For Neuromorphic ApplicationsDocument14 pagesElectrolyte-Gated Transistors For Neuromorphic Applicationskamrul.malNo ratings yet

- Digital VLSI Design (ECE314/ ECE514) : Lecture-4Document29 pagesDigital VLSI Design (ECE314/ ECE514) : Lecture-4Roshan SoniNo ratings yet

- 99 Process Integration PDFDocument53 pages99 Process Integration PDFJayamurugan MookkanNo ratings yet

- CMOS IntroDocument39 pagesCMOS IntrovenkateshNo ratings yet

- Emi Emc 07 11 2023 22mia004Document18 pagesEmi Emc 07 11 2023 22mia004Shivam GaunsNo ratings yet

- NikonovBeyondCMOS 1 ScalingDocument30 pagesNikonovBeyondCMOS 1 Scalingsasi kiran sNo ratings yet

- Digital ElectronicsDocument125 pagesDigital ElectronicsAditya SharmaNo ratings yet

- A Study and Analysis of Two Stage Single Ended CMOS OP-AMPDocument9 pagesA Study and Analysis of Two Stage Single Ended CMOS OP-AMPsanjeevsoni64No ratings yet