0 ratings0% found this document useful (0 votes)

vi điều khiển

Uploaded by

DAO THANH MAIThis document summarizes a proposed method for synthesizing the data path and control path of a CPU. The method uses a graphical representation called a Register Transfer Graph (RTG) to represent the data transfer operations and processing operations between components. It proposes using synthesis parameters like resource sharing, multiport memory, multicycled operations, and pipelined operations to transform the architecture represented by the RTG. The RTG is scheduled at the micro-operation level to optimize performance under the selected parameters. Data transfer paths are also reduced by replacing paths with bypass routes to reduce the connection cost.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

vi điều khiển

Uploaded by

DAO THANH MAI0 ratings0% found this document useful (0 votes)

This document summarizes a proposed method for synthesizing the data path and control path of a CPU. The method uses a graphical representation called a Register Transfer Graph (RTG) to represent the data transfer operations and processing operations between components. It proposes using synthesis parameters like resource sharing, multiport memory, multicycled operations, and pipelined operations to transform the architecture represented by the RTG. The RTG is scheduled at the micro-operation level to optimize performance under the selected parameters. Data transfer paths are also reduced by replacing paths with bypass routes to reduce the connection cost.

Original Description:

vi dieu khien

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

This document summarizes a proposed method for synthesizing the data path and control path of a CPU. The method uses a graphical representation called a Register Transfer Graph (RTG) to represent the data transfer operations and processing operations between components. It proposes using synthesis parameters like resource sharing, multiport memory, multicycled operations, and pipelined operations to transform the architecture represented by the RTG. The RTG is scheduled at the micro-operation level to optimize performance under the selected parameters. Data transfer paths are also reduced by replacing paths with bypass routes to reduce the connection cost.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

vi điều khiển

Uploaded by

DAO THANH MAIThis document summarizes a proposed method for synthesizing the data path and control path of a CPU. The method uses a graphical representation called a Register Transfer Graph (RTG) to represent the data transfer operations and processing operations between components. It proposes using synthesis parameters like resource sharing, multiport memory, multicycled operations, and pipelined operations to transform the architecture represented by the RTG. The RTG is scheduled at the micro-operation level to optimize performance under the selected parameters. Data transfer paths are also reduced by replacing paths with bypass routes to reduce the connection cost.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1/ 4

E Asia Pacific Cmference 011 Civnrits and Systems '96

member 28- 21, 1996,

are-Software C

Dept. of Electrical and Electronic Engineering

Abstract

ropose a systematic method which syn-

thesizes the data path and control path of CPU

We use a graphical representation

re design space more broadly,

change the architecture of data path. The num-

ber of data transfer paths is reduced by replacing

NTRODUCTI ON

One of the fast time-to-market design solutions for

he embedded system. While the software

part is used for providing the behav

ibility of system, the hardware par

Application Specific

as been studied pop- lnstruction Processor

I P is a processor

CPU core of ASIP.

other is to synthesize the micro-architecture opti-

mized the given application which is described with

instructions. They have used the initial architectures

which have data path with an almost fixed connec-

tion topology In those cases, since architectural flex-

ibility is limited by the initial topology, it is not easy

to explore design space widely.

Hiroaki Kunieda

Dept. of Electrical and Elec tronic Engin

Tokyo Institute of Techn

2-12-1, Ookayama, Meguro-ku,

el: i-81-3-5734-257

: +81-3-5734-2842

unieda@ss.titech.ac.jp

Compared with the previous works, our approach

is more aggressive to achieve the high performance

of ASIP. Instruction sequence is decomposed into

micro-operations(M0P's). They are scheduled in

MOP level in order to achieve higher performance

with optimized micro-architecture. To explo

sign space broadly, we try to transform the

tecture by the selection of synthesis parameters. We

assumed a virtual machine as the initial architectural

template, in which there is no limit in th

of control path on the se1

time.

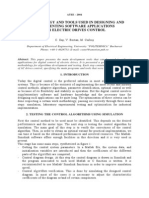

ed microprocessor. The

part and hardware part is done

quence. In the hardware synthesis part, th

bly codes are translated into a graphical form, callcd

ical representation of dat

ing between RTL compon

and the topology synthesis process begin, the combi-

nations of synthesis parameters is applied selectively

to enhance the performance or to reduce the area.

This results in the transformation of data path topol-

ogy. The scheduling is performed in MOP-level un-

ansfer Graph(RTG) wh

306 T4-OB4. 0-7803-3702-6/96/$5.00@1996 IEEE

eI .TL n.ni.r

Fig. 1. : Synthesis Flow

der the selected synthesis parameters. Additionally,

to reduce the connection area cost, the data transfer

paths are reduced by replacing a path with its bypass

route.

3. REGISTER TRANSFER GRAPH

Since instruction is composed of a series of MOPs

which are data transfer operation or data processing

operations between RTL components, it is possible

to consider an instruction as the ordered execution

of such RTL operations. In order to represent oper-

ations in RTL, weintroduce a new RTL-level graph

RTG(V,A), in which V is the set of RTL compo-

nents and A is the set of MOPs. Compared with

CDFG, RTG is more useful to predict the usages of

RTL components, and the connection topology be-

tween them. The easiness of prediction is important

to evaluate the usages of RTL components before the

resource allocation is performed. The multiple exe-

cutions of operation are denoted by execution order

set Oz3, simply called as order set. The elements of

the order set are control step numbers at which the

operation have to be executed.

Initially, the propagation delays of all operations

are assumed to have unit time delay. The numbering

of registers are subject to its assignment table. The

functional operation is represented by two incoming

arcs with the same execution order to a vertex. All

functional operation is numbered by a unique num-

ber. The RTG for LOAD instruction and its MOP

definition are shown in Fig.2. The order sets are as

fOllOWS: 01, 3 ={I}, 01,1 ={2}, 0 2 , s ={4}, 0 3 , 4 =

MAR <- PC

MBRo <- mem[MARl. PC <- PC + 1

IR <- MBR

MAR <- 1R.addr

MBRo <- mem[UARI

Rd <- MBR

Fig. 2. : RTG of LOAD Instruction

Fig. 3. : RTG for Sample Instruction Sequence

{2,5), 0 4 , 2 =(3)~ 04, Bn =( 6) .

According to the execution sequence of the given

instruction sequence, each RTG for instruction is in-

tegrated into a representative RTG. When the dif-

ferent kind of instruction is integrated, a new vertex

or a new arc may be added as well as the change of

order sets. The order of arcs is updated sequentially

according to its execution sequence. Fig.3 shows the

representative RTG of the example instruction se-

quence for x =(w +x) - y.

4. SELECTION OF SYNTHESIS PARAMETER

Depending on the selected synthesis parameters,

RTG is modified to accommodate the parameters,

and in turn, the result architecture will be changed.

Each parameter or the combination of them is ap-

plied to the initial RTG in which all MOPs are

assumed to be executed sequentially without any

execution overlap or component sharing. We are

using four synthesis parameters: Resource Sharing

(Cl ), Multiport Memory (C2), Multicycled Opera-

tion (C3), Pipelined Operation (C4).

In this paper, these synthesis parameters are ap-

plied additively shown in Table.1. Multicycled func-

tional operation and functional pipelining are se-

lectable alternatively according to the application

or the objective function. Fig.4 shows the modified

RTG by each case. The elements of order sets and

the connection topology are changed. In (b), there

are two pair of MBR and MAR. One is for instruction

fetch (3,4), the other is for data fetch (3*,4*). In (c),

two operand registers (pl,p2) are included for mul-

ticycled functional operation (Case-111) or pipelined

function operation (Case-IV).

5. LIST SCHEDULI NG WI TH I NSTRUCTI ON ORDER

In order to schedule MOPs to guarantee correct

execution of instructions, the dependencies between

T4-OB4.2 307

( C )

Fig 4. Modified RTG under (a) Case-I (b) Case-I1 (c)

Case-II1,IV

TABLE I COMBINATIONS OF SYNTHESIS PARAMETERS

Fi

IT1 c1+ c2 +c3

I V c1+ c 2 +c4

instructions or MOPS must be kept. There are two

kinds of dependencies in instruction sequence : inter-

instruction and intra-instruction.

ion dependency is the dependency be-

ons. Since the concurrent execution

of multiple instructions such as super-scalar is not

allowed at the current syste tion can be ex-

ecuted only after all instruct re the instruc-

tion are executed. Hence,

struction implies the depe

ral dependency between them, called as inter-MOP

dency. The operation code field of an instruc-

has the information w h kind of operation

to be executed Therefore, only after the in-

tion is decoded properly, the type of execution

wn. The MOPs of exec

uled before the MOPs o

cle We call this constraint as cycle boundary. We

use list scheduling to sch

tion into a control step order is used

as the priority function which resolves resource con-

tention.

Fig. 5. . Refined RTGs by Transfer Path Reduction

6. TRANSFER PATH REDUCTION

For the scheduled RTG, we apply a heuristic tech-

nique to reduce the number of data transfer paths

without increasing the number of control steps. Data

transfer operations means register-to-register opera-

tion which directly transfers data without modifica-

tion. If we can find out an alternative path for a data

transfer path in RTG, the data t can be

results in the reduction of connection cost. The

rect connections between registers and the functional

units with bypass operation are used as the bypass

resources.

placement is performed in three st

replaced with alternative path (b , wh

nement and selection.

s to find out the candi

s to refine the cur-

path replacement.

The selection step is to select only candidates with

total number of control steps after

RTGs for each case are refined like sho

In (a), a4,60, a4, 61 are removed and

a4*,60, a4*, 61 are removed.

7. DATA/CONTROL PATH GENERATION

After the scheduling and the transfer path reduc-

tion are completed, the vertices of RTG are mapped

into RTL components and the arc

mapped into connection resources

can be implemented in bus-oriented

ed. Since the connection geomet

itly in connectivity graph, multiplexer-type

When buses are used as the connection resources,

the occupancies of connection resources have to be

carefully investigated. When more than one MOP

ath is derived straight-forw

308 T4-OB4.3

are executed simultaneously, all resources required

to execute those concurrent MOPs should be re-

served so as to avoid resource conflict and data colli-

sion. Also, the operand paths and the result path of

functional unit should be reserved during operation

time. In case of memory access, both data path and

address path must be reserved together in order to

ensure the correct memory access.

Control path consists of condition register, state

register, decoder and micro-instructions stored in

PLA, ROM or wired logic. Micro-instructions are

generated from the scheduled time table. The dif-

ferent combination of MOPs is executed at every

control steps. We define the combination of MOPs

as M-set. Among M-sets, there are common M-sets

which are executed more than one times. Common

M-set is unique for all control steps and has unique

micro-instruction. Decoder associates the current

control step with the micro-instruction which has to

be executed. In order to reduce the hardware, new

instruction set tuned to the derived topology must

be generated. Currently, our system does not include

such a procedure.

8. EXPERIMENTAL RESULT

To verify the feasibility of the proposed method,

the basic block of dzfleq, the differential equation

benchmark are chosen as the example. Table.11

shows the result component utilization of five cases.

wegenerate data path and control path under 4 com-

binations of synthesis parameters. We assume the

delay of multiplier is three times of that of addition.

Mark t means the multicycled multiplier with the

propagation delay of 3 control cycles and means

the 4-stage pipelined multiplier, respectively. Cur-

rently, the number of pipeline stages is fixed to 4

and the propagation delay of multicycled operator is

3 control steps. As the advanced work, the optimal

number of pipeline stages and the propagation delay

of multicycled operator will be determined so that

the given design goal can be satisfied. re, which is

the product of the number of control steps and the

maximum register-to-register delay, is calculated un-

der the assumption that the control cycle time of the

initial RTG is the nominal cycle time s, n, , w, are

the number of control steps, the number of M-set

and the width of micro-instruction.

Note that even if the number of functional com-

ponents and the number of storage components are

same, the usages of connection resources are differ-

ent according to its connection topologies and im-

plementation methods. This result indicates that

the connection geometry as well as the utilization

of storage unit and functional unit has to be consid-

ered at the design evaluation step. Also, the width

of micro-instruction is vaned with the different im-

plementation methods even in the same case. So, in

order to select more practical solution, the effect of

control path has to be considered together with the

data path.

9. CONCLUSI ON

We proposed a systematic method which synthe-

sizes the data path and control path of CPU Core for

hardware-software codesign. We firstly proposed a

graphical representation method to describe instruc-

tions in register transfer level. By using RTG, we can

derive the topology of data path directly. In order

to transform the architecture of data path, we ap-

plied synthesis parameters selectively. As the result,

we can explore design space more efficiently. The

optimization of data path topology as well as the

maximization of resource utilization is considered si-

multaneously. By reducing the number of data trans-

fel paths by replacing the rarely used path with its

bypass route, the connection cost is minimized. To

select the best among the candidate CPU core, the

data path cost and control path cost are considered

together.

10. ACKNOWLEDGEMENT

This work has been engaged as a project in CAD21

Research Body of Tokyo I nstitute of Technology. We

wish to thank all the members of CAD21 for their

suggestions and cooperations.

T4-OB4.4 309

You might also like

- Very High-Level Synthesis of Datapath and Control Structures For Reconfigurable Logic DevicesNo ratings yetVery High-Level Synthesis of Datapath and Control Structures For Reconfigurable Logic Devices5 pages

- Area-Efficient Architecture For Fast Fourier TransformNo ratings yetArea-Efficient Architecture For Fast Fourier Transform7 pages

- A Simple Self-Timed Implementation of A Priority Queue For Dictionary Search ProblemsNo ratings yetA Simple Self-Timed Implementation of A Priority Queue For Dictionary Search Problems6 pages

- SJB Institute of Technology: CO & ARM Microcontrollers (21EC52)No ratings yetSJB Institute of Technology: CO & ARM Microcontrollers (21EC52)61 pages

- IJAMM 2023 000015 For+conversion (1) Zhijun+Liu LNo ratings yetIJAMM 2023 000015 For+conversion (1) Zhijun+Liu L11 pages

- Basic Processing Unit:: Fundamental ConceptsNo ratings yetBasic Processing Unit:: Fundamental Concepts35 pages

- 4.2 5-Stage Pipeline ARM Organization: Memory Bottle NeckNo ratings yet4.2 5-Stage Pipeline ARM Organization: Memory Bottle Neck6 pages

- Final Report: Delft University of Technology, EWI IN4342 Embedded Systems LaboratoryNo ratings yetFinal Report: Delft University of Technology, EWI IN4342 Embedded Systems Laboratory24 pages

- ECSE 548 - Electronic Design and Implementation of The Sine Function On 8-Bit MIPS Processor - Report100% (1)ECSE 548 - Electronic Design and Implementation of The Sine Function On 8-Bit MIPS Processor - Report4 pages

- IJECE - Design and Implementation of An On CHIP JournalNo ratings yetIJECE - Design and Implementation of An On CHIP Journal8 pages

- First Steps Towards An Open Control Architecture For A PUMA 560No ratings yetFirst Steps Towards An Open Control Architecture For A PUMA 5606 pages

- Implementation and Evaluation of A Labscale Synchrophasor Model and ApplicationsNo ratings yetImplementation and Evaluation of A Labscale Synchrophasor Model and Applications6 pages

- Lecture 14 Building a Datapath ExtendedNo ratings yetLecture 14 Building a Datapath Extended40 pages

- Formal Verification of Logical Link Control and Adaptation ProtocolNo ratings yetFormal Verification of Logical Link Control and Adaptation Protocol4 pages

- Unit - V: Pipeline & Vector Processing and Multi Processors Pipeline and Vector Processing: MultiprocessorsNo ratings yetUnit - V: Pipeline & Vector Processing and Multi Processors Pipeline and Vector Processing: Multiprocessors20 pages

- Design of Roba Multiplier For High-Speed Yet Energy-Efficient Digital Signal Processing Using Verilog HDLNo ratings yetDesign of Roba Multiplier For High-Speed Yet Energy-Efficient Digital Signal Processing Using Verilog HDL16 pages

- Netiq Using Chariot For Switch and Router Performance TestingNo ratings yetNetiq Using Chariot For Switch and Router Performance Testing9 pages

- Synthesis of High-Speed Finite State Machines in Fpgas by State SplittingNo ratings yetSynthesis of High-Speed Finite State Machines in Fpgas by State Splitting7 pages

- Simple Technique For Root Locus PlottingNo ratings yetSimple Technique For Root Locus Plotting9 pages

- Performance Comparison of Adaptive Modulation and Coding in OFDM Systems Using Signalling and Automatic Modulation ClassificationNo ratings yetPerformance Comparison of Adaptive Modulation and Coding in OFDM Systems Using Signalling and Automatic Modulation Classification8 pages

- TAU - DLR Deutsh Software Flow Aero SolverNo ratings yetTAU - DLR Deutsh Software Flow Aero Solver7 pages

- Radar MTI-MTD Implemetation & Performance (JNL Article) (2000) WWNo ratings yetRadar MTI-MTD Implemetation & Performance (JNL Article) (2000) WW5 pages

- Quality-Of-Service Class Specific Traffic Matrices in IP/MPLS NetworksNo ratings yetQuality-Of-Service Class Specific Traffic Matrices in IP/MPLS Networks6 pages

- A One Cycle FIFO Buffer For Memory Management Units in Manycore SystemsNo ratings yetA One Cycle FIFO Buffer For Memory Management Units in Manycore Systems6 pages

- Ijert Ijert: Implementation of Interleaving Switch Based Architecture For System On ChipNo ratings yetIjert Ijert: Implementation of Interleaving Switch Based Architecture For System On Chip7 pages

- Micro DECSSAO New Microsoft Word DocumentNo ratings yetMicro DECSSAO New Microsoft Word Document4 pages

- Distributed Traffic Management Framework by Network Parameters PDFNo ratings yetDistributed Traffic Management Framework by Network Parameters PDF5 pages

- Module-2: Microcontroller and Embedded SystemsNo ratings yetModule-2: Microcontroller and Embedded Systems74 pages

- Simulation of Dynamic Grid Replication Strategies in OptorsimNo ratings yetSimulation of Dynamic Grid Replication Strategies in Optorsim8 pages

- SAP interface programming with RFC and VBA: Edit SAP data with MS AccessFrom EverandSAP interface programming with RFC and VBA: Edit SAP data with MS AccessNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Programming Guide For Linux Usb Device DriversNo ratings yetProgramming Guide For Linux Usb Device Drivers109 pages

- NguyenLyHeDieuHanh 14-15 HeDieuHanhLinuxNo ratings yetNguyenLyHeDieuHanh 14-15 HeDieuHanhLinux10 pages

- A Course in Mathematical Statistics 0125993153100% (10)A Course in Mathematical Statistics 0125993153593 pages

- Business Vocabulary in Use - Advanced Mascull Cambridge - Nguyen Tan TienNo ratings yetBusiness Vocabulary in Use - Advanced Mascull Cambridge - Nguyen Tan Tien42 pages

- Chapter 17 FB-7SG 7-Segment LED Display ModuleNo ratings yetChapter 17 FB-7SG 7-Segment LED Display Module13 pages

- Bcs Higher Education Qualifications BCS Level 4 Certificate in ITNo ratings yetBcs Higher Education Qualifications BCS Level 4 Certificate in IT4 pages

- Difference Between Enhancement Type and Depletion Type MOSFETNo ratings yetDifference Between Enhancement Type and Depletion Type MOSFET3 pages

- DP83822 Robust, Low Power 10/100 Mbps Ethernet Physical Layer TransceiverNo ratings yetDP83822 Robust, Low Power 10/100 Mbps Ethernet Physical Layer Transceiver110 pages

- FEPL Xilinx Application Module (FE-XAM) Installation GuideNo ratings yetFEPL Xilinx Application Module (FE-XAM) Installation Guide3 pages

- MES MODULE 3 ARM Cortex M3 Instruction Sets and ProgrammingNo ratings yetMES MODULE 3 ARM Cortex M3 Instruction Sets and Programming60 pages

- Very High-Level Synthesis of Datapath and Control Structures For Reconfigurable Logic DevicesVery High-Level Synthesis of Datapath and Control Structures For Reconfigurable Logic Devices

- Area-Efficient Architecture For Fast Fourier TransformArea-Efficient Architecture For Fast Fourier Transform

- A Simple Self-Timed Implementation of A Priority Queue For Dictionary Search ProblemsA Simple Self-Timed Implementation of A Priority Queue For Dictionary Search Problems

- SJB Institute of Technology: CO & ARM Microcontrollers (21EC52)SJB Institute of Technology: CO & ARM Microcontrollers (21EC52)

- 4.2 5-Stage Pipeline ARM Organization: Memory Bottle Neck4.2 5-Stage Pipeline ARM Organization: Memory Bottle Neck

- Final Report: Delft University of Technology, EWI IN4342 Embedded Systems LaboratoryFinal Report: Delft University of Technology, EWI IN4342 Embedded Systems Laboratory

- ECSE 548 - Electronic Design and Implementation of The Sine Function On 8-Bit MIPS Processor - ReportECSE 548 - Electronic Design and Implementation of The Sine Function On 8-Bit MIPS Processor - Report

- IJECE - Design and Implementation of An On CHIP JournalIJECE - Design and Implementation of An On CHIP Journal

- First Steps Towards An Open Control Architecture For A PUMA 560First Steps Towards An Open Control Architecture For A PUMA 560

- Implementation and Evaluation of A Labscale Synchrophasor Model and ApplicationsImplementation and Evaluation of A Labscale Synchrophasor Model and Applications

- Formal Verification of Logical Link Control and Adaptation ProtocolFormal Verification of Logical Link Control and Adaptation Protocol

- Unit - V: Pipeline & Vector Processing and Multi Processors Pipeline and Vector Processing: MultiprocessorsUnit - V: Pipeline & Vector Processing and Multi Processors Pipeline and Vector Processing: Multiprocessors

- Design of Roba Multiplier For High-Speed Yet Energy-Efficient Digital Signal Processing Using Verilog HDLDesign of Roba Multiplier For High-Speed Yet Energy-Efficient Digital Signal Processing Using Verilog HDL

- Netiq Using Chariot For Switch and Router Performance TestingNetiq Using Chariot For Switch and Router Performance Testing

- Synthesis of High-Speed Finite State Machines in Fpgas by State SplittingSynthesis of High-Speed Finite State Machines in Fpgas by State Splitting

- Performance Comparison of Adaptive Modulation and Coding in OFDM Systems Using Signalling and Automatic Modulation ClassificationPerformance Comparison of Adaptive Modulation and Coding in OFDM Systems Using Signalling and Automatic Modulation Classification

- Radar MTI-MTD Implemetation & Performance (JNL Article) (2000) WWRadar MTI-MTD Implemetation & Performance (JNL Article) (2000) WW

- Quality-Of-Service Class Specific Traffic Matrices in IP/MPLS NetworksQuality-Of-Service Class Specific Traffic Matrices in IP/MPLS Networks

- A One Cycle FIFO Buffer For Memory Management Units in Manycore SystemsA One Cycle FIFO Buffer For Memory Management Units in Manycore Systems

- Ijert Ijert: Implementation of Interleaving Switch Based Architecture For System On ChipIjert Ijert: Implementation of Interleaving Switch Based Architecture For System On Chip

- Distributed Traffic Management Framework by Network Parameters PDFDistributed Traffic Management Framework by Network Parameters PDF

- Simulation of Dynamic Grid Replication Strategies in OptorsimSimulation of Dynamic Grid Replication Strategies in Optorsim

- SAP interface programming with RFC and VBA: Edit SAP data with MS AccessFrom EverandSAP interface programming with RFC and VBA: Edit SAP data with MS Access

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960

- Business Vocabulary in Use - Advanced Mascull Cambridge - Nguyen Tan TienBusiness Vocabulary in Use - Advanced Mascull Cambridge - Nguyen Tan Tien

- Bcs Higher Education Qualifications BCS Level 4 Certificate in ITBcs Higher Education Qualifications BCS Level 4 Certificate in IT

- Difference Between Enhancement Type and Depletion Type MOSFETDifference Between Enhancement Type and Depletion Type MOSFET

- DP83822 Robust, Low Power 10/100 Mbps Ethernet Physical Layer TransceiverDP83822 Robust, Low Power 10/100 Mbps Ethernet Physical Layer Transceiver

- FEPL Xilinx Application Module (FE-XAM) Installation GuideFEPL Xilinx Application Module (FE-XAM) Installation Guide

- MES MODULE 3 ARM Cortex M3 Instruction Sets and ProgrammingMES MODULE 3 ARM Cortex M3 Instruction Sets and Programming