Reconfigurable High Frequency Class S Power Amplifier Demonstrator

Reconfigurable High Frequency Class S Power Amplifier Demonstrator

Uploaded by

Vitor HugoCopyright:

Available Formats

Reconfigurable High Frequency Class S Power Amplifier Demonstrator

Reconfigurable High Frequency Class S Power Amplifier Demonstrator

Uploaded by

Vitor HugoOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Reconfigurable High Frequency Class S Power Amplifier Demonstrator

Reconfigurable High Frequency Class S Power Amplifier Demonstrator

Uploaded by

Vitor HugoCopyright:

Available Formats

Reconfigurable High Frequency Class S Power Amplifier Demonstrator

John Dooley, Gerry Corley, Tomasz Podsiadlik and Ronan Farrell

CTVR - The Telecommunications Research Centre, Callan Institute, National University of Ireland

Maynooth, Co. Kildare, Ireland

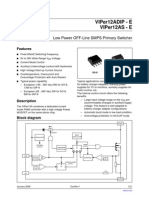

Abstract This paper presents an end-to-end high frequency

class S power amplifier. A description of the full testbench and

some important points on generation of RF outputs from FPGA

devices and current mode class D design are given.

Experimental measurements are provided for the prototype PA

consisting of a signal generator, analog to digital converter,

driver circuit, current mode class D switching stage and

bandpass filter. Theory and experimentally measured results for

this prototype are presented for a multi tone signal centred at

930 MHz and with a total output power of 24.7dBm.

Index Terms Delta-sigma modulation, power amplifiers.

I. INTRODUCTION

Switch-mode power amplifiers such as class D, E and F

have higher theoretical efficiencies than class A or AB

amplifiers. Because switch-mode PAs are nonlinear they are

not direct replacements for linear PAs, though they can be

used in architectures such as Envelope Elimination and

Restoration (EER), LInear amplification with Nonlinear

Components (LINC) or as is shown here, with based

modulators in what is known as a class S power amplifier.

The Class S architecture in this paper utilizes a current

mode class D (CMCD) switch for the high efficiency switchmode PA stage. This class of power amplifier has published

drain efficiencies of the order of 60%, 63% and 71% for

designs with high power discrete devices [1-3]. Since the

class D amplifier eliminates the envelope of the input signal,

all information in the input signal must be encoded in the

timing of the switch transitions. Maximum transistor

switching frequency remains a major barrier to high

efficiency implementation of the class-S PA architecture and

influences the maximum possible bit rate of the input signal.

The modulation strategy must therefore be optimized for both

cheap implementation on a digital circuit and compatibility as

a drive signal for the available transistor technology.

The type of encoder that can be used is limited due to the

necessity to reconstruct the amplified version of the original

input signal. A direct bandpass modulator can be used as

the encoder as it can convert the modulated carrier signal into

a binary amplitude pulse train for amplification in the class D

switchmode power amplifier stage. Typically, direct

modulation will require a system clock frequency of 4 times

the carrier frequency and circuits have been presented for

carrier frequencies of the order of 2.2 GHz [4].

978-1-4577-0649-3/11/$26.00 2011 IEEE

Although it is possible to manufacture modulators for

high frequency operation an alternative approach presented

here is to implement the at a lower frequency on an

FPGA. This implementation has several advantages including

low cost, low risk and it provides a reconfigurable hardware

implementation. Such a solution is suitable for integration in

a software defined radio as it can be accommodated on an

FPGA and requires a small fraction of total FPGA resources.

Figure 1. System view of a class S switch mode PA

In this paper we present experimentally measured results

for a class S power amplifier with a high level structure

similar to that shown in Fig 1. This platform operates at high

frequency using a mid-range FPGA development board and a

CMCD amplifier. It is shown that the clock frequency for the

modulator can be set at a fraction of the carrier frequency

of the output by adopting alternative techniques to direct

bandpass modulation. For this demonstrator we will use a

10th order modulator to convert the input signal to a pulse

density modulated output which is up-converted and used to

drive a CMCD PA. Experimentally measured results are

presented for the output of the full PA.

II. HIGH FREQUENCY DIGITAL MODULATOR

A modulator converts a high resolution digital input

signal to a pulse density modulated output. This is done by

adding an error signal whose spectral components are filtered

out from the signal band, and when added to the input in the

time domain creates a square wave. Digital modulators

are used when high dynamic range, low noise and high

linearity are required. modulators can be broadly

classified in terms of order, number of output levels of the

quantizer and noise transfer function.

For the end-to-end RF class S PA presented here we

require a modulator which can convert a low frequency

high resolution signal to a high frequency low resolution

signal. Limitations in the implementation of high frequency

direct bandpass modulators include the high clock

frequency which in turn will increase the cost of developing

and building such a solution, and the input signal in the

direct approach is an RF signal. In this way a number of

integrated circuits must be used prior to the modulator to

upconvert the signal.

A combination of both the up conversion and modulation

stages can now be realised on FPGA development boards. In

this implementation the signal is first encoded with a band

pass 10th order modulator using a relatively low clock

frequency as shown in Fig. 2. It is characterized by signal

transfer function (STF) and noise transfer function (NTF)

given by (1) and (2) respectively.

STF ( z ) = 1

(1)

1

NTF ( z ) =

1+ H (z)

(2)

The loop filter employed in the has been introduced in

[5], and it is optimized for fast operation in digital signal

processors. The loop filter shown in Fig. 3 has two adders in

a cascade in the longest computational path. It is constructed

in such a way, that the poles of H(z) move along the unit

circle as coefficients mi change. Therefore deep notches

appear in the NTF as the poles of H(z) become zeros of the

NTF. This feature is used to generate power of two

coefficients in the loop filter, and effectively replace

multiplications by a fast operation of bit shifting. This makes

the chosen structure suitable for fast FPGA operation.

Moreover, the latency does not depend on modulator order.

Here, a 10th order BP with zeros optimized around f/4

has been used, the structure of which is shown in Figures 2

and 3.

The modulated signal is subsequently multiplied by a +1

and -1 bit stream. Since a bit stream of +1,-1 clocked at a

frequency fCLK (fCLK = 20 f, where f is a sampling

frequency of , f = 98MHz) is equivalent to a frequency

multiplication by a local oscillator at fCLK/2 sampled at the

nyquist rate. The spectrums of both the direct BP approach

and the digital mixing approach are shown in Fig.4.

The purpose of this signal modulator is to drive a switch

mode RF power amplifier. As such the performance of the

power amplifier is directly dependent on the signal driving it.

Comparison of the direct approach to the digital mixing

method is performed using a number of figures of merit such

as dynamic range, signal passband or bandwidth (BW),

maximum and minimum pulse width and coding efficiency.

The dynamic range of the signal and passband of the

modulator must be large enough so that when the modulated

signal is filtered by the PA output network and filter stages

the output signal will meet spectral mask requirements. Here

we will gauge the relative difference in available signal

bandwidth for each modulator and not compare it to a

particular spectral mask requirement. Modulator output

signal pulse widths can have a large effect on the overall

performance of the class S power amplifier depending on the

types of transistors used. Short and long pulse lengths in the

modulator output bit stream will effect the overall

performance of the class S PA depending on the gate switch

on time, low frequency dispersion effects and fT for the

devices used [6]. Mean power coding efficiency, P, of a pulse

density modulator is defined as the ratio of in-band signal

power to total modulator output power [7].

P =

Pinband

Ptotal

(3)

Relative performance and signal quality for both the direct

and digitally mixed approaches can be calculated in Matlab.

Using a fixed point simulation a close approximation to the

FPGA implementation can be calculated and are found in

Table I.

TABLE I. COMPARISON OF MODULATORS

Parameter

Fc

F

BW

Dynamic Range

Figure 2.

Figure 3.

Direct

930 MHz

3.72 GHz

+ Mixing

930 MHz

98 MHz

180 MHz

57 dB

9 MHz

45 dB

structure used

Computationally efficient loop filter H(z)

It is possible to change the pulse density modulator NTF by

updating the modulator coefficients on the FPGA. To

dynamically change the transmit frequency is also possible,

however the quality of the transmit signal generated by the

modulator on the FPGA will be influenced by the reference

oscillator used on the FPGA board and the relationship

between its frequency and the required transmit frequency for

the system.

Since the clock frequency requirements for the direct

implementation are prohibitively large for the Virtex II pro

FPGA development board only experimental results for the

digital mixing approach are presented.

-20

Power/frequency (dB/Hz)

-40

-60

-80

-100

-120

-140

-160

0

0.2

0.4

0.6

0.8

1.2

1.4

1.6

1.8

Frequency (GHz)

Figure 4. Plot of direct 4th order and 10th order digitally mixed bandpass

modulators (direct approach in black, digitally mixed approach in grey).

-20

-30

Power/frequency (dB/Hz)

-40

-50

-60

of the signal using pulse-density modulation [10]. Shown in

this publication, the signal into the class S PA is a high

resolution digital signal at a fraction of the carrier frequency.

This signal is modulated and upconverted to an RF frequency

in the PA. To solve the input signal generation problem, a

differential output signal directly from the multi-gigabit

transceiver (MGT) on a Virtex II pro FPGA development

board was used. In this way the input signal for the power

amplification stage can be generated at different carrier

frequencies and most importantly uses a modulator

clocked at a fraction of the carrier frequency.

The resources required on the Virtex II pro FPGA to

implement the design constitute a very small percentage of

those available on the device. The signal source used for this

demonstrator is implemented directly on the FPGA. 4 direct

digital synthesizers are used to generate a multi tone signal

having a bandwidth of 2MHz. A 10th order bandpass

modulator is instantiated in this implementation on a Virtex

II pro FPGA board. The MGT of the FPGA board is used to

upsample the output signal from the modulator.

The MGT outputs of the FPGA development board are

connected to a prototype CMCD PCB board built on 4 layer

FR4. The board consists of a PWD06 switch-mode driver IC

from PWRF, the output of this is fed to a 3dB 180 degree

splitter from Anaren to provide the differential drive signals

for the class D stage. The CMCD bridge power amplifier

structure consists of two pHEMT ATF52189 transistors from

Avago Technologies. The differential output across the

drains of the two transistors is connected to a resonant LC

tank circuit tuned to 930 MHz. Finally a lumped element

balun was designed and implemented to convert the signal

from differential to single ended output for measurement

purposes.

-70

-80

-90

-100

-110

-120

0.85

0.9

0.95

Frequency (GHz)

Figure 5. Magnification about the carrier frequency

(direct approach in black, digitally mixed approach in grey).

III. CLASS-S PA DEMONSTRATOR DESIGN

Class D, E and F switch-mode power amplifiers have been

shown to offer linearity and high efficiency through the use of

various PA architectures, namely: Envelope Elimination and

Restoration (EER) and LInear amplification with Nonlinear

Components (LINC) [8][9]. In these cases the switch mode

PA accepts an analog signal already modulated on the RF

carrier transmit frequency. This requires a high frequency

circuit to pre-process the signal and split it into two separate

paths. The class S PA is similar as it requires pre-processing

Figure 6. Photo of CMCD amplifier PCB

IV

E XPERIMENTAL MEASUREMENTS

Experimental measurements were taken for the

reconfigurable class S power amplifier described in Section

III. Figure 6 shows a photograph of the CMCD power

amplifier board. The FPGA development board MGT output

is connected to the CMCD board by two matched semi-rigid

co-axial cables. Care is taken in the PCB layout to match the

two paths of the differential signal into the CMCD.

A first set of measurements was taken to determine the

performance of the CMCD board for a single tone at the

center frequency. An Agilent E4433B signal generator was

used to generate the signal and an off-board splitter was used

to convert the signal from single-ended to differential. In

these tests a CMCD stage drain efficiency of 65% was

recorded for a single tone at 930MHz. This result is for the

CMCD stage alone and does not represent the overall system

efficiency, which suffers from the power consumption of the

IC used to amplify the pulse density modulated signal from

the FPGA.

The second set of measurements used the output from a

pulse density modulated and upconverted signal to drive the

current mode class D switch. A screen capture from a Rohde

& Schwarz FSL spectrum analyser of the output signal from

the PCB is presented in Figure 7.

The total power contained in the output signal spectrum is

24.7dBm, 12.5dBm in the wanted signal, 24.2dBm from

noise and 10.6dBm from images and other spurious signals.

* RBW 30 kHz

Ref

30 dBm

* Att

50 dB

* VBW 2 kHz

Marker 1 [T1 ]

-3.13 dBm

SWT 6.8 s

929.038461538 MHz

components greatly reduces the efficiency of the CMCD stage

and as a result, the overall system efficiency. Further work is

required to improve the performance of this system to

increase the available signal bandwidth and improve the

dynamic range. At present it is not possible to identify the

presence of nonlinear effects from the system output. There is

also an open issue of power consumption in the amplification

of the digital pulse stream from the FPGA to drive the CMCD

stage.

ACKNOWLEDGMENTS

This material is based in part upon works supported by

Science Foundation Ireland under grant number

08/CE/I1523.

REFERENCES

[1]

[2]

[3]

30

A

20

[4]

1 AP

VIEW

10

-10

[5]

-20

3DB

-30

-40

[6]

-50

-60

[7]

-70

Center

930 MHz

50 MHz/

Span

500 MHz

Figure 7. Measured output spectrum from CMCD board

[8]

CONCLUSIONS

A class S power amplifier prototype that can accept a

modulated data stream from an FPGA and produce an output

of greater than 20dBm has been built. The modulated RF

signals from the FPGA are sufficient to test the prototype

CMCD board and demonstrate an end-to-end class S PA.

From these results it is evident that the modulation

scheme is critical for overall system efficiency. A high level

of out of band noise power and unwanted spectral

[9]

[10]

Al Tanany, A., Sayed, A., and Boeck, G. A 2.14 GHz 50 Watt

60% Power Added Efficiency GaN Current Mode Class D Power

Amplifier. Proceedings of 38th European Microwave Conference,

432-435. 27-10-2008.

Ji-Yeon, K., Dong-Hoon, H., Jong-Heon, K., and Stapleton, S. P.

A 50 W LDMOS current mode 1800 MHz class-D power

amplifier. Microwave Symposium Digest, 2005 IEEE MTT-S

International 4. 12-6-2005.

Nemati, H. M., Fager, C., and Zirath, H. High Efficiency

LDMOS Current Mode Class-D Power amplifier at 1 GHz.

Microwave Conference, 2006. 36th European 176-179. 10-92006.

Schmidt, M.; Heck, S.; Dettmann, I.; Grozing, M.; Berroth, M.;

Wiegner, D.; Templ, W.; , "Continuous-Time Bandpass DeltaSigma Modulator for a Signal Frequency of 2.2 GHz," German

Microwave Conference, 2009 , vol., no., pp.1-4, 16-18 March

2009

Choon Haw Leong; Roberts, G.W.; , "An effective

implementation of high-order bandpass sigma-delta modulators

for high speed D/A applications," Circuits and Systems, 1997.

ISCAS '97., Proceedings of 1997 IEEE International Symposium

on , vol.1, no., pp.49-52 vol.1, 9-12 Jun 1997

Samulak, A.; Fischer, G.; Weigel, R.; , "Basic Nonlinear Analysis

of Class-S Power Amplifiers based on GaN Switching

Transistors," German Microwave Conference, 2009 , vol., no.,

pp.1-4, 16-18 March 2009

Johnson, T.; Sobot, R.; Stapleton, S.; , "Manchester encoded

bandpass sigma-delta modulation for RF class D amplifiers,"

Circuits, Devices & Systems, IET , vol.1, no.1, pp.21-26,

February 2007

Milosevic, D.; van der Tang, J.; van Roermund, A.; ,

"Intermodulation products in the EER technique applied to classE amplifiers," Circuits and Systems, 2004. ISCAS '04.

Proceedings of the 2004 International Symposium on , vol.1,

no., pp. I- 637-40 Vol.1, 23-26 May 2004

H. Chireix, High power outphasing modulation, Proc. IRE, vol.

23, no. 11, pp.1370-1392, Nov. 1935

Dooley, J.; Podsiadlik, T.; Canniff, A.; Farrell, R.; ,

"Reconfigurable Class S power amplifiers at RF and microwave

frequencies," Integrated Nonlinear Microwave and MillimetreWave Circuits, 2008. INMMIC 2008. Workshop on , vol., no.,

pp.43-46, 24-25 Nov. 2008

You might also like

- Bridge EquipmentsDocument14 pagesBridge EquipmentsSandipanBiswas100% (1)

- HSC 4 1823df c750gpm @190psi - Speed 3350rpmDocument2 pagesHSC 4 1823df c750gpm @190psi - Speed 3350rpmJwardNo ratings yet

- AVR IAR C/C++ Compiler Reference GuideDocument323 pagesAVR IAR C/C++ Compiler Reference GuidethietdaucongNo ratings yet

- Using SimBiology For Pharmacokinetic and Mechanistic ModelingDocument72 pagesUsing SimBiology For Pharmacokinetic and Mechanistic Modelingjose rigoberto bedolla balderasNo ratings yet

- Mulesoft NotesDocument9 pagesMulesoft NotesJohn Constantine100% (2)

- What Is PWM and Why Is It UsefulDocument4 pagesWhat Is PWM and Why Is It UsefulBagus HarperNo ratings yet

- Pulse-Density Modulation For RF Applications: The Radio-Frequency Power Amplifier (RF PA) As A Power ConverterDocument6 pagesPulse-Density Modulation For RF Applications: The Radio-Frequency Power Amplifier (RF PA) As A Power ConverteriMiklaeNo ratings yet

- A 6.1 GS/S 52.8 MW 43 DB DR 80 MHZ Bandwidth 2.4 GHZ RF Bandpass Adc in 40 NM CmosDocument4 pagesA 6.1 GS/S 52.8 MW 43 DB DR 80 MHZ Bandwidth 2.4 GHZ RF Bandpass Adc in 40 NM Cmossohailasghar_tNo ratings yet

- Digital IF Subsampling Using The HI5702, HSP45116 and HSP43220Document6 pagesDigital IF Subsampling Using The HI5702, HSP45116 and HSP43220Farhan BabarNo ratings yet

- Digitally Controlled Envelope Tracking Power Supply For An RF Power AmplifierDocument7 pagesDigitally Controlled Envelope Tracking Power Supply For An RF Power AmplifierHamed GheidiNo ratings yet

- Implementation of Digital QPSK Modulator by Using VHDL / MatlabDocument5 pagesImplementation of Digital QPSK Modulator by Using VHDL / Matlabblesson123No ratings yet

- Multi-Channel Digital Up/Down Converter For Wimax Systems: FeaturesDocument13 pagesMulti-Channel Digital Up/Down Converter For Wimax Systems: FeaturesAmandeep GroverNo ratings yet

- Optimized Digital Filter Architectures For Multi-Standard RF TransceiversDocument15 pagesOptimized Digital Filter Architectures For Multi-Standard RF TransceiversvvigyaNo ratings yet

- FPGA-based Implementation of Efficient Sample Rate Conversion For Software Defined RadiosDocument5 pagesFPGA-based Implementation of Efficient Sample Rate Conversion For Software Defined RadiosNitin MathurNo ratings yet

- AMFM Software Radio Receiver Implementation in FPGADocument11 pagesAMFM Software Radio Receiver Implementation in FPGAphamcaodaiNo ratings yet

- Jantzi Snelgrove Sigma Delta ModulatorDocument4 pagesJantzi Snelgrove Sigma Delta ModulatorMaciej KlimkiewiczNo ratings yet

- Bandpass Continuous-Time Delta-Sigma Modulator For Wireless Receiver ICDocument4 pagesBandpass Continuous-Time Delta-Sigma Modulator For Wireless Receiver ICBalthier8745No ratings yet

- A 2GS/s 9-Bit 8-12x Time-Interleaved Pipeline-SAR ADC For A PMCW Radar in 28nm CMOSDocument4 pagesA 2GS/s 9-Bit 8-12x Time-Interleaved Pipeline-SAR ADC For A PMCW Radar in 28nm CMOSburakgonenNo ratings yet

- A 2.4GHz 2Mbs Digital PLL-Based Transmitter For 802.15.4 in 130nm CMOSDocument4 pagesA 2.4GHz 2Mbs Digital PLL-Based Transmitter For 802.15.4 in 130nm CMOSraja_ramalingam07No ratings yet

- Digital Signal - WikipediaDocument4 pagesDigital Signal - WikipediaMubashir AliNo ratings yet

- The Design and Construction of A DDS Based Waveform GeneratorDocument12 pagesThe Design and Construction of A DDS Based Waveform GeneratorWilson Fernando Rodríguez RodríguezNo ratings yet

- Design of Integer N Frequency Divider For High Performance PLL Using 180 NM CMOS TechnologyDocument8 pagesDesign of Integer N Frequency Divider For High Performance PLL Using 180 NM CMOS Technology123abhijeetNo ratings yet

- Chapter 3Document42 pagesChapter 3Cu BomNo ratings yet

- Zhao 2014Document14 pagesZhao 2014yossof tayelNo ratings yet

- 5 Ijaest Vol No.4 Issue No.2 Developoment of Programmable Demodulator Using Arm Processor 018 022Document5 pages5 Ijaest Vol No.4 Issue No.2 Developoment of Programmable Demodulator Using Arm Processor 018 022iserpNo ratings yet

- Delta ModulationDocument5 pagesDelta Modulationian.maximillianNo ratings yet

- Demodulation AlgoritmsDocument8 pagesDemodulation AlgoritmsPraveen Kumar BodireddyNo ratings yet

- Ijesat 2012 02 Si 01 02Document4 pagesIjesat 2012 02 Si 01 02Ijesat JournalNo ratings yet

- Design of 4 Watt Power AmplifierDocument3 pagesDesign of 4 Watt Power AmplifierTapas Sarkar100% (1)

- Design of A Digital Front-End Transmitter For Ofdm-Wlan Systems Using FpgaDocument4 pagesDesign of A Digital Front-End Transmitter For Ofdm-Wlan Systems Using FpgaMd.Maruf Ahamed BeddutNo ratings yet

- Digital Modulation TechDocument63 pagesDigital Modulation Techgaurav_juneja_4No ratings yet

- A New Approach To Complex Bandpass Sigma Delta Modulator Design For GPS/Galileo ReceiverDocument7 pagesA New Approach To Complex Bandpass Sigma Delta Modulator Design For GPS/Galileo ReceiverƋniïiƨ TƎinNo ratings yet

- Term Paper of EleDocument8 pagesTerm Paper of Eleshailesh singhNo ratings yet

- 50% PAE WCDMA Basestation AmplifierDocument4 pages50% PAE WCDMA Basestation AmplifiersrikandiujungNo ratings yet

- Low Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron TechnologyDocument5 pagesLow Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron Technologyeditor_ijtel100% (1)

- A Wideband Delta Sigma Digital-RF Modulator For High Data Rate TransmittersDocument13 pagesA Wideband Delta Sigma Digital-RF Modulator For High Data Rate TransmittersKarim Abd El HamidNo ratings yet

- D-Band Frequency Tripler For Passive Imaging - Final 13th JulyDocument4 pagesD-Band Frequency Tripler For Passive Imaging - Final 13th JulyTapas Sarkar100% (1)

- A Direct-Conversion CMOS Transceiver For The 802.11a/b/g WLAN Standard Utilizing A Cartesian Feedback TransmitterDocument13 pagesA Direct-Conversion CMOS Transceiver For The 802.11a/b/g WLAN Standard Utilizing A Cartesian Feedback TransmitterdeviNo ratings yet

- F0283111611-Ijsce Paper - SubirDocument5 pagesF0283111611-Ijsce Paper - SubirSubir MaityNo ratings yet

- (2000 JSSC) A_1.8-mW_CMOS_Sigma_Delta_modulator_with_integrated_mixer_for_A_D_conversion_of_IF_signalsDocument8 pages(2000 JSSC) A_1.8-mW_CMOS_Sigma_Delta_modulator_with_integrated_mixer_for_A_D_conversion_of_IF_signalsLaiken ChenNo ratings yet

- Abstmct: 0-7803-5604-7/99/$10.00 1999 Ieee 1999 IEEE Radio Frequency Integrated Circuits SymposiumDocument6 pagesAbstmct: 0-7803-5604-7/99/$10.00 1999 Ieee 1999 IEEE Radio Frequency Integrated Circuits SymposiumPramod SrinivasanNo ratings yet

- W2023Document11 pagesW2023Miki ArsovskiNo ratings yet

- Sbaa 094Document22 pagesSbaa 094Vitu VituNo ratings yet

- Software-Defined-Radio: National University of Science and TechnologyDocument19 pagesSoftware-Defined-Radio: National University of Science and TechnologyZain ShabbirNo ratings yet

- Z 87200Document55 pagesZ 87200Bảo BìnhNo ratings yet

- Peak-To-Average Power Ratio Reduction by CB-ACE and Adaptive Ace AlgorithmsDocument8 pagesPeak-To-Average Power Ratio Reduction by CB-ACE and Adaptive Ace AlgorithmsShankar GaneshNo ratings yet

- Bit Error Rate Evaluation of IEEE 802.16 in OFDM SystemDocument4 pagesBit Error Rate Evaluation of IEEE 802.16 in OFDM Systemabhi_rules08No ratings yet

- Ijesrt: A Verilog Design in FPGA Implementation of Quadrature Phase Shift Keying (QPSK) Digital ModulatorDocument6 pagesIjesrt: A Verilog Design in FPGA Implementation of Quadrature Phase Shift Keying (QPSK) Digital ModulatorRahulNo ratings yet

- A Novel FPGA-based LVDT Signal Conditioner: Kumardeb Banerjee, Bivas Dam, Kalyan MajumdarDocument6 pagesA Novel FPGA-based LVDT Signal Conditioner: Kumardeb Banerjee, Bivas Dam, Kalyan MajumdarnarayanNo ratings yet

- Herzel BCTM2015 8bit DividerDocument5 pagesHerzel BCTM2015 8bit DividerHagar IlbheryNo ratings yet

- Digital IQ DemodulatorDocument3 pagesDigital IQ DemodulatoraboashoorNo ratings yet

- Use Double Integration in Sigma Delta Modulation: 11. FeedbackDocument10 pagesUse Double Integration in Sigma Delta Modulation: 11. FeedbackAnonymous eQgC9YFNo ratings yet

- THLDL: Wright2Document2 pagesTHLDL: Wright2Dennis AtyugrasiwiNo ratings yet

- Wind Band Radar Signal Using RF2051Document8 pagesWind Band Radar Signal Using RF2051Khushal KharadeNo ratings yet

- A High Linearity FMCW Sweep GeneratorDocument10 pagesA High Linearity FMCW Sweep GeneratorDong-hun ShinNo ratings yet

- Polar IQ TXDocument5 pagesPolar IQ TXjaoudeNo ratings yet

- A Wideband Digital RF Receiver Front-End Employing A New Discrete-Time Filter For M-WimaxDocument10 pagesA Wideband Digital RF Receiver Front-End Employing A New Discrete-Time Filter For M-WimaxFarhan AliNo ratings yet

- Basics of Sigma-Delta ModulationDocument25 pagesBasics of Sigma-Delta ModulationbrufoNo ratings yet

- Basics of Sigma-Delta ModulationDocument25 pagesBasics of Sigma-Delta ModulationDuthi Dinh MitetNo ratings yet

- Modeling of Sigma Delta Modulator Non Idealities With Two Step Quantization in MATLAB SIMULINK PDFDocument6 pagesModeling of Sigma Delta Modulator Non Idealities With Two Step Quantization in MATLAB SIMULINK PDFeditor_ijcatNo ratings yet

- AMW9905 Hybrid Frequency Synthesizer Combines Octave Tuning Range and Millihertz StepsDocument7 pagesAMW9905 Hybrid Frequency Synthesizer Combines Octave Tuning Range and Millihertz StepsAnonymous 39lpTJiNo ratings yet

- Chi SNSNDocument4 pagesChi SNSNYOGESH GOWDA VNo ratings yet

- A 120 DB Dynamic Range 400 MW Class-D Speaker Driver With Fourth-Order PWM ModulatorDocument9 pagesA 120 DB Dynamic Range 400 MW Class-D Speaker Driver With Fourth-Order PWM Modulatorawais107No ratings yet

- FM DemodulationDocument4 pagesFM DemodulationRudra Pratap SinghNo ratings yet

- High-Performance D/A-Converters: Application to Digital TransceiversFrom EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNo ratings yet

- Inerting Steam For Coal Mill Fire PDFDocument12 pagesInerting Steam For Coal Mill Fire PDFparveen100% (1)

- B - HRG0W62401 - Electric SystemDocument9 pagesB - HRG0W62401 - Electric SystemArtur LiepinsNo ratings yet

- 2836 01Document6 pages2836 01rp801113717No ratings yet

- Concrete Technology: No. of TestDocument10 pagesConcrete Technology: No. of TestJayHatNo ratings yet

- Scheidegger & Schubert, 1989Document11 pagesScheidegger & Schubert, 1989DanielNo ratings yet

- Viper 12ADocument21 pagesViper 12Aahmed hussainNo ratings yet

- 1959 Cholette RTDDocument8 pages1959 Cholette RTDAuthierOlivierNo ratings yet

- Frequently Asked Questions About Flame DetectionDocument11 pagesFrequently Asked Questions About Flame DetectionRicardo Javier PlasenciaNo ratings yet

- Aurora 410 Series Horizontal Split Case PumpsDocument2 pagesAurora 410 Series Horizontal Split Case PumpsHenry SuarezNo ratings yet

- Master Mf6400 WSM 10 enDocument3 pagesMaster Mf6400 WSM 10 enporcha1No ratings yet

- Updating Progress in Primavera P6Document2 pagesUpdating Progress in Primavera P6Edin LissicaNo ratings yet

- Day 04 Design of LPG System Part 04Document14 pagesDay 04 Design of LPG System Part 04kmas1612No ratings yet

- Easa TCDSDocument53 pagesEasa TCDSAnonymous ucJM9AGdaNo ratings yet

- Valve and Actuator: An IntroductionDocument19 pagesValve and Actuator: An IntroductionZakky Ibnu FadjrieNo ratings yet

- R 390 An 95Document39 pagesR 390 An 95n8trNo ratings yet

- Kasur Tanneries Waste Mnagment Agency (KTWMA)Document45 pagesKasur Tanneries Waste Mnagment Agency (KTWMA)Engr Muhammad Imran Nawaz0% (2)

- Dynamic Modelling and Simulation of A Photovoltaic Refrigeration PlantDocument11 pagesDynamic Modelling and Simulation of A Photovoltaic Refrigeration PlantVicenteFerrazNo ratings yet

- ROLLAND ZAT540eDocument17 pagesROLLAND ZAT540egesssmNo ratings yet

- HydrogenType4 Datasheet TableDocument2 pagesHydrogenType4 Datasheet TableALEX D LOPEZ RNo ratings yet

- Looping in DatastageDocument7 pagesLooping in DatastageCsvv VardhanNo ratings yet

- Maeen Engineering Services - Geotech - Nov-2023Document29 pagesMaeen Engineering Services - Geotech - Nov-2023Mohammad HegazyNo ratings yet

- Vickers Micro-Hardness MeasurementDocument11 pagesVickers Micro-Hardness MeasurementIsha TiwariNo ratings yet

- Parker Overview BigDocument35 pagesParker Overview BigsenamotoNo ratings yet

- Aluminium 7075 SpecDocument2 pagesAluminium 7075 Specadam.el.polaco7881No ratings yet

- Maintenance, Overhaul & Repair of Aircraft SystemsDocument35 pagesMaintenance, Overhaul & Repair of Aircraft SystemsBigbearBigbearNo ratings yet