VLSI Design Question Bank

VLSI Design Question Bank

Uploaded by

books babuCopyright:

Available Formats

VLSI Design Question Bank

VLSI Design Question Bank

Uploaded by

books babuOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

VLSI Design Question Bank

VLSI Design Question Bank

Uploaded by

books babuCopyright:

Available Formats

www.alljntuworld.

in JNTU World

ld

or

W

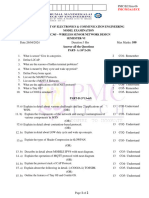

GROUP-A (SHORT ANSWER QUESTIONS)

TU

S No. Questions Bloom’s Course

Taxonomy Outcome

Level

UNIT-I

1 Define oxidation & Classify different types of oxidation Remember 1

2 Explain about Ion implantation Understand 1

3 Describe lithography Understand 1

4 List the advantages of IC Remember 1

JN

5 Discuss the four generations of Integration Circuits Understand 1

6 State the various Silicon wafer Preparations Remember 1

7 Describe BiCMOS Technology Understand 1

8 Illustrate the steps involved in twin-tub process Remember 1

9 State the different types of CMOS process Remember 1

10 Describe encapsulation Understand 1

11 Explain the basic processing steps involved in BiCMOS process Remember 1

12 State Moore’s law Remember 1

13 Describe enhancement mode and depletion mode of transistor Remember 1

14 State the advantages of CMOS process Remember 1

Downloaded From JNTU World (http://www.alljntuworld.in)

www.alljntuworld.in JNTU World

S No. Questions Bloom’s Course

Taxonomy Outcome

Level

15 Describe diffusion Remember 1

16 List the advantages of CMOS process Remember 1

UNIT – II

1 State why nMOS technology is preferred more than pMOS technology. Remember 2

2 Describe Short Channel devices. Remember 2

3 Explain a pull down device. Understand 2

ld

4 Explain pull up device. Remember 2

5 Describe the different operating regions for an MOS transistor. Remember 2

6 Define Threshold voltage. Remember 3

7 State Body effect. Remember 3

8 Describe Channel length modulation. Remember 3

or

9 Define Latch up. Remember 2

10 Demonstrate the CMOS inverter circuits. Apply 3

11 Demonstrate nMOS inverter circuit. Apply 3

12 Distinguish between linear and circular convolution of two sequences. Understand 2

13 Demonstrate BiCMOS inverter circuit. Apply 3

14 Describe figure of merit. Remember 2

15

16

W

Explain pass transistor.

Demonstrate the transfer characteristics of CMOS.

Understand

Apply

2

2

UNIT – III

1 Explain VLSI design flow. Understand 3

2 Describe Stick Diagram. Remember 3

3 List the uses of Stick diagram. Remember 4

4 List the various color coding used in stick diagram. Remember 4

TU

5 Explain different MOS layers. Understand 4

6 Sketch a stick diagram for 2 input nMOS NAND gate. Apply 4

7 Sketch a stick diagram for CMOS inverter. Apply 4

8 List the types of design rules. Remember 4

9 Sketch a Transistor related design rules (Orbit 2 μm CMOS) minimum sizes Apply 5

and overlaps

10 Sketch the aspects of λ-based design rules for contacts, including some Apply 5

factors contributing to higher yield/reliability.

11 Sketch the stick diagram for 2 i/p nMOS nor gate. Apply 4

JN

12 Describe Scaling. Remember 5

13 Explain about transistor design rules for nMOS. Understand 5

14 Describe layout diagram. Remember 4

15 Sketch stick diagram for nMOS inverter. Apply 4

UNIT – IV

1 Give the different symbols for transmission gate Remember 6

2 What is pass transistor? Understand 6

3 What is sheet resistance? Remember 6

4 Define Rise time. Understand 6

Downloaded From JNTU World (http://www.alljntuworld.in)

www.alljntuworld.in JNTU World

S No. Questions Bloom’s Course

Taxonomy Outcome

Level

5 Define Fall time. Remember 6

6 Define Delay time. Remember 6

7 What are the other forms of CMOS logic? Understand 6

8 What is meant by wiring capacitance? Remember 6

9 What is fan in? Understand 6

10 What is fan out? Understand 6

ld

11 Draw OR gate with pass transistors. Apply 6

12 Draw the circuit for inverter type super buffer. Apply 6

UNIT – V

1 What is a data path subsystem? Remember 7

2 What is a shifter? Remember 7

or

3 What is the difference between shifter and barrel shifter? Remember 7

4 Write the truth table for full adder. Remember 7

5 Draw the circuit of one detector with AND gates. Apply 7

6 Draw the circuit of zero detector with AND gates. Understand 7

7 What is comparator? Remember 7

8 Draw the circuit of comparator. Apply 7

9

10

W

What is parity generator?

What is the difference between synchronous and asynchronous counter.

Remember

Remember

7

7

UNIT – VI

1 Write categories of memory arrays Understand 8

2 What is a RAM Understand 8

3 What is ROM Understand 8

4 What is serial access memory Understand 8

TU

5 What is content Addressable memory Understand 8

6 Draw the 6-Transistor SRAM cell Apply 8

7 Draw the 1-Transistor Dram cell Apply 8

8 What are the different types of serial access memories Remember 8

9 What is flash memory Remember 8

10 What are the different types of ROMs Remember 8

11 Explain the principle of SRAM Understand 8

12 Discuss the advantages of SRAM Understand 8

JN

13 Explain the principle of DRAM Understand 8

14 Discuss the advantages of Flash memory Understand 8

UNIT – VII

1 Name the different types of ASICs. Remember 9

2 Analyze full custom ASIC design. Understand 9

3 Analyze the standard cell-based ASIC design. Understand 9

4 Differentiate between channeled & channel less gate array. Remember 9

5 Explain about FPGA. Understand 9

6 Explain about antifuse technology. Understand 9

7 Explain about Programmable Interconnects. Understand 9

Downloaded From JNTU World (http://www.alljntuworld.in)

www.alljntuworld.in JNTU World

S No. Questions Bloom’s Course

Taxonomy Outcome

Level

8 List the steps in ASIC design flow. Remember 9

9 Discuss the parameters influencing low power design. Understand 9

10 Explain about CPLD. Understand

UNIT – VIII

1 State the levels at which testing of a chip can be done. Remember 10

2 Discuss the categories of testing. Understand 10

ld

3 Explain functionality tests. Understand 10

4 Explain manufacturing tests. Understand 10

5 Discuss the defects that occur in a chip Understand 10

6 Explain about fault models Understand 10

7 Analyze stuck – at fault Understand 10

or

8 Explain fault models with examples Understand 10

9 Discuss about observability Understand 10

10 Discuss about controllability Understand 10

11 Explain various approaches in design for testability Understand 10

12 Mention the common techniques involved in ad hoc testing Remember 10

13 Analyze the scan-based test techniques Understand 10

14

15

W

Analyze the self-test techniques.

Discuss the applications of chip level test techniques.

Understand

Understand

10

10

16 Explain boundary scan Understand 10

17 Analyze test access port Understand 10

18 Explain about boundary scan register. Understand 10

GROUP-B (LONG ANSWER QUESTIONS)

TU

Bloom’s

Course

S. No. Questions Taxonomy

Outcome

Level

UNIT-I

1 Explain the operation of NMOS enhancement transistor Understand 1

2 Explain about the body effect of MOS transistors. Understand 1

3 Explain the silicon semiconductor fabrication process Understand 1

JN

4 Explain the fabrication of PMOS transistor and its substrate fabrication

Understand 1

Process

5 Explain different fabrication process of CMOS transistor Understand 1

6 Explain the silicon semiconductor fabrication process Understand 1

7 Derive the threshold voltage for NMOS enhancement transistor Apply 1

8 Derive the design equations for MOS devices Apply 1

9 Explain channel length modulation. Understand 1

10 Explain BiCMOS fabrication in an n-well process Understand 1

11 Compare between CMOS and bipolar technologies Remember 1

12 Explain the oxidation process in the IC fabrication process with sketches. Understand 1

Downloaded From JNTU World (http://www.alljntuworld.in)

www.alljntuworld.in JNTU World

Bloom’s

Course

S. No. Questions Taxonomy

Outcome

Level

UNIT – II

1 Illustrate the relationship between Ids versus Vds of MOSFET Understand 2

2 Interpret the Pull-up to pull-down ratio(Zpu-Zpd) for an nMOS inverter driven

Apply 3

by another nMOS inverter

3 Interpret the Pull-up to pull-down ratio(Zpu-Zpd) for an nMOS inverter driven

Apply 3

through One or more Pass Transistors

4 Explain the various forms of pull-ups. Understand 3

ld

5 Explain what is latch up in CMOS and BiCMOS Susceptibility. Understand 3

6 Differentiate the parameters of CMOS and Bipolar Technologies Remember 2

7 Explain BiCMOS inverter in all conditions. Understand 3

8 Explain the latch up prevention techniques. Remember 3

9 Illustrate the CMOS inverter DC characteristics and obtain the relationship

Apply 3

or

for output voltage at different region in the transfer characteristics

10 Explain the terms figure of merit of MOSFET and output conductance, using

Remember 2

necessary equations

UNIT – III

1 (a) What is a stick diagram? Sketch the stick diagram and layout for a CMOS

inverter.

(b) What are the effects of scaling on Vt. Understand 4

(c) What are design rules? Why is metal- metal spacing larger than poly –

poly spacing.

W

2 Explain clearly the nMOS Design style with neat sketches. Understand 4

3 Explain clearly the CMOS Design style with neat sketches. Understand 4

4 Sketch the stick diagram for the NMOS implemented of the Boolean

Apply 4

expression Y = AB + C.

5 (a) Sketch a Schematic and Cell Layout with neat diagrams.

Apply 5

(b) With neat diagram explain λ- based design rules for contact cuts and vias.

6 Sketch the circuit schematic and stick diagram of CMOS 2-Input NAND gate Apply 4

TU

7 sketch the transistor level diagram for the given expression and also get the

corresponding Apply 4

Stick diagram representation in CMOS logic Y = a (b + c) +d

8 Define scaling. What are the factors to be considered for transistor scaling? Remember 2

9 Remember

Define constant voltage scaling. Give necessary equations. 5

10 Explain with suitable examples how to design the layout of a gate to Remember 4

maximize performance and minimize area.

UNIT – IV

JN

1 4

Draw the CMOS implementation of 4-to-1 MUX using transmission gates. Apply

2 Explain the VLSI design flow with a neat diagram Understand 4

3 Explain the Transmission gate and the tristate inverter briefly Understand 4

4 Clearly explain the AOI implementation using cmos design style with neat

Apply 4

diagrams.

5 Design a 2-input multiplexer using CMOS transmission gates. Apply 4

6 Explain PSEUDO nMOS Logic give its advantages and disadvantages Apply 6

7 Explain dynamic CMOS logic give its advantages and disadvantages Understand 6

8 Explain CMOS domino logic give its advantages and disadvantages Understand 6

Downloaded From JNTU World (http://www.alljntuworld.in)

www.alljntuworld.in JNTU World

Bloom’s

Course

S. No. Questions Taxonomy

Outcome

Level

9 Explain clocked CMOS logic and n-p CMOS logic give its advantages and

Apply 6

disadvantages

10 Explain basic circuit concepts such as RS, area capacitances. Apply 6

11 Derive the expression for time delay Tsd in case of MOSFET Apply 6

12 Discuss the issues involved in driving large capacitive loads in VLSI circuit

Understand 6

regions.

13 Describe three sources of wiring capacitances. Discuss the wiring capacitance

ld

Understand 6

on the performance of a VLSI circuit

14 List the logical constraints of layers Remember 6

UNIT – V

1 Explain description for half adder and Full adder. Understand 7

2 Draw the logic diagram of zero/one detector and explain its operation with

Apply 7

the help of stick diagram.

or

3 Draw the schematic and explain the principle and operation of Array

Apply 7

Multiplier.

4 Explain the carry look ahead Adder Understand 7

5 Explain the design hierarchies and bring out which kind of approach is better

Apply 7

to adopt for system design.

6 Describe briefly n-bit parallel adder. Apply 7

7

8

W

Draw and explain the structure barrel shifter. Remember

Remember

7

7

Discuss the circuit design considerations in case of static adder circuits

9 How Boolean functions are performed using MUX. Discuss 1-bit CMOS Apply 7

implementation of ALU

10 Sketch the schematic serial parallel multiplier and explain its operation Apply 7

11 Discuss synchronous and asynchronous counters Remember 7

UNIT – VI

1 8

TU

Discuss in detail about classification of memory arrays. Understand

2 Explain the memory cell read and write operation of 6T SRAM with neat

Understand 8

sketches.

3 Explain the principles of SRAM and DRAM. Understand 8

4 What are the advantages of SRAM and DRAMs compare them in all

Remember 8

respects.

5 Explain the read and write operations of 1T DRAM memory cell Remember 8

6 Explain the read and write operations of 3T DRAM memory cell Remember 8

7

JN

Explain about NAND based ROM design. Remember 8

8 Explain about NOR based ROM design. Remember 8

9 Discuss about different types of ROMs Remember 8

10 Explain various types of serial access memories with sketches. Understand 8

11 What is content addressable memory and give any one application of it. Understand 8

UNIT – VII

1 Discuss the different methods of programming of PALs Understand 9

2 Distinguish PLAs, PALs, CPLDs, FPGAs, and standard cells in all respects. Remember 9

3 Explain about the principle and operation of FPGAs. What are its

Understand 9

applications?

Downloaded From JNTU World (http://www.alljntuworld.in)

www.alljntuworld.in JNTU World

Bloom’s

Course

S. No. Questions Taxonomy

Outcome

Level

4 Draw the schematic for PLA and explain the principle. What are the

Apply 9

advantages of PLAs?

5 Explain the structure and principle of PLA. Understand 9

6 Draw the schematic and examine how Full Adder can be implemented using

Apply 9

PLA's.

7 Explain about configurable FPGA based I/O blocks. Understand 9

8 Design JK Flip flop circuit using PLA. Apply 9

ld

9 Explain semicustom design approach of an IC Understand 9

10 Compare semicustom and full custom designs of an IC Remember 9

UNIT – VIII

1 Explain the various DFT techniques. Understand 10

2 Discuss about signature analysis in Testing. Explain with an example. Understand 10

or

3 Explain about memory-self test with the help of a schematic Understand 10

4 Analyze the issues to be considered while implementing BIST and explain

Remember 10

each.

5 Explain how layout design can be done for improving testability. Remember 10

6 Explain about different fault models in VLSI testing with examples. Remember 10

7 Analyze any TWO

a) DFT

b) BIST

W Remember 10

c) Boundary scan Testing

8 Explain fault models. Understand 10

9 Explain ATPG. Understand 10

10 Briefly explain

a) Fault grading & fault

Understand 10

b) simulation Delay fault testing

c) Statistical fault analysis

TU

11 Understand

Discuss scan-based test techniques. 10

12 Explain Ad-Hoc testing and chip level test techniques. Remember 10

13 Explain self-test techniques. Remember 10

14 Explain system-level test techniques Remember 10

15 Explain

a) BILBO

Understand

b) TAP controller 10

c) Observability

JN

d) Controllability

GROUP-III (ANALYTICAL QUESTIONS)

S. No. Questions Bloom’s Course

Taxonomy Outcome

Level

UNIT – I

1 Explain lithography process with sketches Understand 1

2 Explain diffusion process in IC fabrication Understand 1

Downloaded From JNTU World (http://www.alljntuworld.in)

www.alljntuworld.in JNTU World

S. No. Questions Bloom’s Course

Taxonomy Outcome

Level

3 Discuss the purpose of metallization in IC manufacturing? Explain the Understand 1

methods employed for metallization

4 How integrated passive components are fabricated in ICs? Explain Understand 1

5 Mention the properties of oxidation. Explain about thermal oxidation process Understand 1

6 Explain how a bipolar NPN transistor is included in n-well CMOS Understand 1

processing. Draw the cross section of BiCMOS transistor.

UNIT – II

ld

1 Consider an nMOS transistor in a 65 nm process with a minimum drawn Apply 2

channel length of 50 nm (λ = 25 nm). Let W/L = 4/2 λ (i.e., 0.1/0.05 µm). In

this process, the gate oxide thickness is 10.5 A. Estimate the high-field

mobility of electrons to be 80cm2/V· s at 70 o C. The threshold voltage is 0.3

V. Plot Ids vs. Vdsfor Vgs= 0, 0.2, 0.4, 0.6, 0.8, and 1.0 V using the long-

channel model.

or

2 Calculate the diffusion parasitic Cdbof the drain of a unit-sized contacted Apply 2

nMOS transistor in a 65 nm process when the drain is at 0 V and again at

VDD = 1.0 V. Assume the substrate is grounded. The diffusion region

conforms to the design rules from Figure 2.8 with λ = 25 nm. The transistor

characteristics are CJ = 1.2 fF/µm2, MJ = 0.33, CJSW = 0.1 fF/µm, CJSWG =

0.36 fF/µm, MJSW = MJSWG = 0.10, and 0 = 0.7 V at room temperature.

3 Consider the nMOS transistor in a 65 nm process with a nominal threshold Apply 2

voltage of 0.3 V and a doping level of 8 × 1017 cm–3. The body is tied to

W

ground with a substrate contact. How much does the threshold change at

room temperature if the source is at 0.6 V instead of 0?

4 What is the minimum threshold voltage for which the leakage current Apply 2

through an OFF transistor (Vgs= 0) is 103 times less than that of a transistor

that is barely ON (Vgs= Vt) at room temperature if n = 1.5. One of the

advantages of silicon-on insulator (SOI) processes is that they have smaller n.

What threshold is required for SOI if n = 1.3.

5 Consider an nMOS transistor in a 0.6 µm process with W/L = 4/2 λ (i.e., 2

1.2/0.6 µm). In this process, the gate oxide thickness is 100 A and the Apply

TU

mobility of electrons is 350 cm2/V· s. The threshold voltage is 0.7 V. Plot

Idsvs. Vdsfor Vgs= 0, 1, 2, 3, 4, and 5 V.

6 Derive an equation for Idc of an n channel process of twin well MOSFET Apply 2

operating in saturation region.

7 AN nMOS transistor is operating in saturation region with the following Apply 2

parameters. Vgs=5V, Vth=1.2V.(W/L)=10, µCox=110µ A/V2. Find

transconductance of the device.

8 For a CMOS inverter, calculate the shift in the transfer characteristic curve Apply 6

when βn/ βp ratio is varied from 1/1 to 10/1.

9 Find gm and rdsfor an n-channel transistor with Vgs=1.2V,Vth=0.8V.(W/L)=10, Apply 6

JN

µCox=92µ A/V2and VDS = Veff +0.5V. The output impedance

constant=0.0953V-1.

10 Draw the pass transistor arrangement for the logic X=ABC. Apply 6

UNIT – III

1 Sketch a stick diagram for a CMOS gate computing Y A B C ·D and Apply 4

estimate the cell width and height.

2 Design a layout diagram for the CMOS logic shown below Apply 4

Y A B .C .

Downloaded From JNTU World (http://www.alljntuworld.in)

www.alljntuworld.in JNTU World

S. No. Questions Bloom’s Course

Taxonomy Outcome

Level

3 Design a stick diagram for the CMOS logic shown below Y A Apply 4

B C

.

4 Design a stick diagram for two input pMOS NAND and NOR gates. Apply 4

5 Apply 4

Design a stick diagram for the CMOS logic for AB CD

6 Design a layout diagram for the pMOS logic Y A(B C) Apply 4

ld

7 Design a layout diagram for two input nMOS NAND gate. Apply 4

8 Design a stick diagram and layout for two input CMOS NAND gate Apply 4

indicating all the regions and layers.

9 Draw the stick diagram and mask layout for a CMOS two input NOR gate. Apply 4

or

UNIT – IV

1 Calculate the gate capacitance value of 5mm technology minimum size Apply 5

transistor with gate to channel capacitance value is 0.0004 pF/mm2.

2 What is the problem of driving large capacitive loads? Explain a method to Understand 5

drive such load.

3 Calculate the rise time and fall time of the CMOS inverter (W/L)n=6 and Apply 5

(W/L)p=8. k 'n 150A / V 2 , Vtn 0.7V, k 'p 62A / V2 ,

W

Vtp 0.85V, VDD 3.3V. Total output capacitance =150Ff

4 Realize the function f=AB+CD using pseudo-nMOS logic. Apply 5

5 Apply 5

Realize the function f A BC

6 Derive the expression for rise and fall time of CMOS inverter. Comment on Apply 5

the expression derived.

TU

7 State the problem that arises when comparatively large capacitive loads are Apply 5

driven by inverters. Explain how super buffers can solve the problem.

8 Explain 2:1 multiplexer using transmission gate and tristate inverter. Apply 5

UNIT – V

1 Draw circuit diagram of one transistor with capacitor dynamic RAM and also Apply 7

draw its layout.

2 Draw the circuit diagram for 4X4 barrel sifter using complementary Apply 7

transmission gates and explain its shifting operation.

3 Design an incrementer circuit using counter. Apply 7

JN

4 Design ripple structure for one-zero detector circuit. Apply 7

5 Design a comparator using XNOR gates. Apply 7

6 Design sum and carry expressions of carry look ahead adder using nMOS Apply 7

logic.

7 Design a 4-bit array multiplier and implement using basic gates. Apply 7

UNIT – VII

1 Implement JK flip-flop using PROM. Apply 9

2 Implement 2-bit comparator using PAL logic. Apply 9

3 Draw and explain the antifuse structure for programming the PAL device. Apply 9

4 Apply 9

Implement Y A.C AB ACD using programmable logic array (PLA).

Downloaded From JNTU World (http://www.alljntuworld.in)

www.alljntuworld.in JNTU World

S. No. Questions Bloom’s Course

Taxonomy Outcome

Level

5 Apply 9

Implement Y A.C AB ACD using programmable array logic (PAL).

6 Apply 9

Implement Y A.C AB ACD using programmable logic read only

memory (PROM).

7 Design a 1-bit full adder and implement the sum and carry expressions using Apply 9

PLA.

UNIT – VIII

ld

1 Draw the basic structure of parallel scan and explain how it reduces the long Understand 10

scan chains.

2 Explain how an improved layout can reduces faults in CMOS circuits Understand 10

3 Draw the state diagram of TAP controller and explain how it provides the Understand 10

control signals for test data and instruction register.

4 A sequential circuit with n inputs and m storage devices. To test this circuit Apply 10

how many test vectors are required?

or

5 How IDDQ testing is used to test the bridge faults? Understand 10

6 What is ATPG? Explain a method of generation of test vector. Understand 10

W

TU

JN

Downloaded From JNTU World (http://www.alljntuworld.in)

You might also like

- Geotechnical Engineering QBDocument11 pagesGeotechnical Engineering QBT Rajesh Asst. Prof. - CENo ratings yet

- Iala NP735Document25 pagesIala NP735JamieGilbert100% (5)

- Introduction To ComputersDocument97 pagesIntroduction To Computersta_1091100% (1)

- Linear and Digital Integrated Circuits Question BankDocument8 pagesLinear and Digital Integrated Circuits Question Bankdhanaram100% (1)

- MWEDocument13 pagesMWEsruthigummadiNo ratings yet

- Power Plant Engineering Question BankDocument6 pagesPower Plant Engineering Question BankSanju ReddyNo ratings yet

- Course Outcome Eds PDFDocument12 pagesCourse Outcome Eds PDFDileep VarmaNo ratings yet

- Group - A (Short Answer Questions) : S. No Blooms Taxonomy Level Course OutcomeDocument15 pagesGroup - A (Short Answer Questions) : S. No Blooms Taxonomy Level Course OutcomeIshani JhaNo ratings yet

- Computer Graphics Question BankDocument9 pagesComputer Graphics Question BankDr-Samson ChepuriNo ratings yet

- Pulse and Digital Circuits (PDC) QB PDFDocument15 pagesPulse and Digital Circuits (PDC) QB PDFlakshmanNo ratings yet

- Tutorial Bank: Unit-I The Cellular Concept-System Design FundamentalsDocument7 pagesTutorial Bank: Unit-I The Cellular Concept-System Design Fundamentalsvictor kNo ratings yet

- Computer Organization Question BankDocument8 pagesComputer Organization Question BankAyush BaiswarNo ratings yet

- STLDDocument8 pagesSTLDsasi kiran sNo ratings yet

- Objectives: Question Bank On Short Answer QuestionsDocument12 pagesObjectives: Question Bank On Short Answer QuestionsTahseen AnjumNo ratings yet

- Electrical Measurements Question BankDocument12 pagesElectrical Measurements Question BankHarish B. M.No ratings yet

- Design and Analysis of Algorithms Question BankDocument10 pagesDesign and Analysis of Algorithms Question BankPhani Prasad100% (1)

- SS Jntu HydDocument19 pagesSS Jntu HydgiribabukandeNo ratings yet

- Part - A (Short Answer Questions) : S. No. Questions Bloom's Taxonomy Level Course OutcomeDocument11 pagesPart - A (Short Answer Questions) : S. No. Questions Bloom's Taxonomy Level Course OutcomeDevendra BhavsarNo ratings yet

- CMC Question Bank PDFDocument9 pagesCMC Question Bank PDFsrinuNo ratings yet

- Electrical Machines-III Question BankDocument9 pagesElectrical Machines-III Question BanksanthiNo ratings yet

- Jntuh Chemistry Ece Me Ce ChemDocument9 pagesJntuh Chemistry Ece Me Ce ChemvarshithrajbalnackNo ratings yet

- Formal Languages and Automata Theory QB PDFDocument5 pagesFormal Languages and Automata Theory QB PDFSatish JadhaoNo ratings yet

- Compiler Design QB PDFDocument11 pagesCompiler Design QB PDFvinod3457No ratings yet

- Concrete Technology Question Bank PDFDocument7 pagesConcrete Technology Question Bank PDFAnonymous 59S2OoNo ratings yet

- Strength of Materials - II Question Bank PDFDocument11 pagesStrength of Materials - II Question Bank PDFpavanNo ratings yet

- Computer Networks Question BankDocument9 pagesComputer Networks Question BankCharyNo ratings yet

- Group - A (Short Answer Questions)Document5 pagesGroup - A (Short Answer Questions)fortyNo ratings yet

- Utilization of Electrical Energy Question Bank PDFDocument17 pagesUtilization of Electrical Energy Question Bank PDFKranthi Kumar100% (1)

- Cec365 Model Set1Document2 pagesCec365 Model Set1suryabmepco23No ratings yet

- Group - A (Short Answer Questions) : S.No Blooms Taxonomy Level Course OutcomesDocument15 pagesGroup - A (Short Answer Questions) : S.No Blooms Taxonomy Level Course OutcomesRama KrishnaNo ratings yet

- Electronic Measurements and Instrumentation QBDocument9 pagesElectronic Measurements and Instrumentation QBSridhar Koneru VenkkatNo ratings yet

- Analog CommunicationsDocument10 pagesAnalog CommunicationsmayaNo ratings yet

- Fundamentals of HVDC and FACTS Devices QBDocument24 pagesFundamentals of HVDC and FACTS Devices QBdeptai2023No ratings yet

- DAA Question BankDocument5 pagesDAA Question Bankdask84779No ratings yet

- Toaz - Info Basic Electrical Engineering Question Bank PRDocument9 pagesToaz - Info Basic Electrical Engineering Question Bank PRIts MeNo ratings yet

- Electrical Machines - III PDFDocument9 pagesElectrical Machines - III PDFAliya MahaboobNo ratings yet

- CMC Assignment (2018-19)Document3 pagesCMC Assignment (2018-19)srinuNo ratings yet

- JNTU World: Part - A (Short Answer Questions)Document6 pagesJNTU World: Part - A (Short Answer Questions)Naresh JonnaNo ratings yet

- Microprocessors and Interfacing DevicesDocument10 pagesMicroprocessors and Interfacing DevicesAbd Amaad KhanNo ratings yet

- Guru Nanak Institutions Technical Campus (Autonomous) : Question Bank With Blooms Taxonomy Level (BTL)Document3 pagesGuru Nanak Institutions Technical Campus (Autonomous) : Question Bank With Blooms Taxonomy Level (BTL)sahithikocharlakotaNo ratings yet

- pT2K6t2K6Ec80t-HADARANDNAVIGATI0N: LossesDocument12 pagespT2K6t2K6Ec80t-HADARANDNAVIGATI0N: LossesDellNo ratings yet

- VLSIDocument51 pagesVLSIPriyanka JainNo ratings yet

- Microprocessors & MicrocontrollersDocument13 pagesMicroprocessors & MicrocontrollerssatyaNo ratings yet

- Mobile Application Development Question Bank PDFDocument8 pagesMobile Application Development Question Bank PDFAlpana BorseNo ratings yet

- Electrical Machines-I Question BankDocument12 pagesElectrical Machines-I Question BankimmadiuttejNo ratings yet

- Electronic Measurements & InstrumentationDocument9 pagesElectronic Measurements & InstrumentationSumanth NaniNo ratings yet

- BPHT 701 Question Paper-Set-2Document2 pagesBPHT 701 Question Paper-Set-2deepaatharv608No ratings yet

- Aerospace Propulsion - I Question BankDocument5 pagesAerospace Propulsion - I Question BankGanesh Natarajan SNo ratings yet

- Computer Graphics Question BankDocument9 pagesComputer Graphics Question BankDr-Samson ChepuriNo ratings yet

- OOP Through Java Question BankDocument6 pagesOOP Through Java Question BankRocky AdityaNo ratings yet

- Aaa Bridge EquipmentsDocument4 pagesAaa Bridge Equipmentsdavchd888No ratings yet

- Syi Twy Sgs LTGRV NBDocument12 pagesSyi Twy Sgs LTGRV NBVineel TalluriNo ratings yet

- CMC Question Bank - 853Document13 pagesCMC Question Bank - 853amounika597No ratings yet

- DLC 22-23Document2 pagesDLC 22-23wwwe51162No ratings yet

- Vlsi Design Kec 072Document3 pagesVlsi Design Kec 072No OneNo ratings yet

- Kcs711 Mobile ComputingDocument1 pageKcs711 Mobile ComputingUnnati DwivediNo ratings yet

- QUESTION BANK-VLSI_22Document10 pagesQUESTION BANK-VLSI_22preetha asokanNo ratings yet

- Structural Analysis - I Question Bank PDFDocument16 pagesStructural Analysis - I Question Bank PDFSayed Urooj AbbasNo ratings yet

- CIVIL EngineeringDocument16 pagesCIVIL EngineeringSasala RajuNo ratings yet

- Global Positioning System (Professional Elective - Vi) B.Tech. IV Year II Sem. Course Code: EC863PE L 3 T 0 P 0 C 3Document3 pagesGlobal Positioning System (Professional Elective - Vi) B.Tech. IV Year II Sem. Course Code: EC863PE L 3 T 0 P 0 C 3books babu0% (1)

- Notes GpsDocument17 pagesNotes Gpsbooks babuNo ratings yet

- Gps-Questions: Unit-IDocument1 pageGps-Questions: Unit-Ibooks babuNo ratings yet

- Vlsi Design NotesDocument47 pagesVlsi Design Notesbooks babuNo ratings yet

- Set-A Answer Any Two Questions 2 5 10MDocument1 pageSet-A Answer Any Two Questions 2 5 10Mbooks babuNo ratings yet

- Telecommunication Switching Systems and Networks Lesson PlanDocument6 pagesTelecommunication Switching Systems and Networks Lesson Planbooks babuNo ratings yet

- TSSN Question Bank Ece IV NRCMDocument17 pagesTSSN Question Bank Ece IV NRCMbooks babu100% (1)

- Ttdec 2013Document85 pagesTtdec 2013books babuNo ratings yet

- Co QBDocument26 pagesCo QBkhananu100% (1)

- Operating System MCQsDocument19 pagesOperating System MCQsTajammul ShahNo ratings yet

- Xps-8300 Service Manual En-UsDocument116 pagesXps-8300 Service Manual En-UsReginaldo PoianiNo ratings yet

- EE2028 - S2Ay2122 - Lecture 1 Intro and ConceptsDocument55 pagesEE2028 - S2Ay2122 - Lecture 1 Intro and ConceptsAlex CarmonaNo ratings yet

- Request Letter For ComputerDocument3 pagesRequest Letter For ComputerLiza Marie NeryNo ratings yet

- BI Apps796 Perf Tech Note V5Document57 pagesBI Apps796 Perf Tech Note V5Puneet AggarwalNo ratings yet

- 2 Address DecoderDocument18 pages2 Address DecoderSyarif Koto0% (1)

- 01375013Document8 pages01375013이은지No ratings yet

- Ise Vi File Structures 10is63 NotesDocument107 pagesIse Vi File Structures 10is63 NotesBhavya shree cNo ratings yet

- Grade 7 ICT Ppt (2017 E.C Updated)Document231 pagesGrade 7 ICT Ppt (2017 E.C Updated)reshadmuzemil.etNo ratings yet

- Computer Organization Lab ManualDocument40 pagesComputer Organization Lab ManualH A MDNo ratings yet

- Guide SokkiaDocument80 pagesGuide Sokkiafaizalprbw100% (1)

- CCC Full Paper PDFDocument35 pagesCCC Full Paper PDFSatyam SharmaNo ratings yet

- Etc Lmg-Ssc12a64Document10 pagesEtc Lmg-Ssc12a64Dubis EszterNo ratings yet

- What Is A Storage Device - Definition, Types, Examples - GeeksforGeeksDocument15 pagesWhat Is A Storage Device - Definition, Types, Examples - GeeksforGeekssiyalohia8No ratings yet

- CCMCL301 Computer LiteracyDocument99 pagesCCMCL301 Computer Literacymbarushimana samuelNo ratings yet

- Aspire 1700 Service ManualDocument119 pagesAspire 1700 Service ManualtopobucciaNo ratings yet

- Embedded System and Design ReportDocument86 pagesEmbedded System and Design ReportGulati Rohit100% (1)

- Edexcel GCSE ICT Revision GuideDocument40 pagesEdexcel GCSE ICT Revision GuideMagishalini Rajendran100% (1)

- 132RGB X 162dot 262K Color With Frame Memory Single-Chip TFT Controller/DriverDocument201 pages132RGB X 162dot 262K Color With Frame Memory Single-Chip TFT Controller/Driverхаский луцковичNo ratings yet

- Chapter 2 - Introduction To Oracle DBDocument9 pagesChapter 2 - Introduction To Oracle DBAbdiwali Ibrahim SuleimanNo ratings yet

- MWANSA'S Computer Studies Scheme of Work - 2022Document20 pagesMWANSA'S Computer Studies Scheme of Work - 2022Musonda MwenyaNo ratings yet

- Lab #3: Advanced Assembly Programming & Adding SRAMDocument2 pagesLab #3: Advanced Assembly Programming & Adding SRAMRosemond FabienNo ratings yet

- S5 Ict Notes 4Document129 pagesS5 Ict Notes 4obuyasilver995No ratings yet

- "Computer Controlled" Home Appliance Control: B.Tech Project ReportDocument26 pages"Computer Controlled" Home Appliance Control: B.Tech Project ReportashishNo ratings yet

- Implementation of Digital Clock On FPGA: Industrial Training Report ONDocument26 pagesImplementation of Digital Clock On FPGA: Industrial Training Report ONAdeel HashmiNo ratings yet

- Disassembling A Computer's System UnitDocument3 pagesDisassembling A Computer's System UnitOrlando Ginson OcampoNo ratings yet

- Bannari Amman Institute of Technology: Regulation: 2018Document2 pagesBannari Amman Institute of Technology: Regulation: 2018veerakumarsNo ratings yet

- Cisco Switch Security Configuration GuideDocument86 pagesCisco Switch Security Configuration GuideBen HetrickNo ratings yet