uP9011Q DS F0000

uP9011Q DS F0000

Uploaded by

Blue StacksCopyright:

Available Formats

uP9011Q DS F0000

uP9011Q DS F0000

Uploaded by

Blue StacksOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

uP9011Q DS F0000

uP9011Q DS F0000

Uploaded by

Blue StacksCopyright:

Available Formats

uP9011Q

Complete DDR3/ DDR4 Memory Power Solution Converter

General Description Features

The uP9011Q is a high performance synchronous buck Synchronous Buck Converter (VDDQ)

converter with 1.5A source/sink LDO for memory system

Wide Input Voltage Range from 4.5V to 26V

power. It also provides a buffered low noise reference

VTTREF. The uP9011Q has wide operation range from 4.5V Fast Load Transient Response

to 26V for input voltage and 0.75V to 3.3V for memory Output Current up to 8A

output voltage.

RCOTTM Control Topology

The synchronous buck of the uP9011Q adopts uPI

Soft-Off in S4/S5 States

proprietary robust constant on-time (RCOT TM) PWM

scheme that features easy-to-use, low external component Fixed 1.5V (DDR3), 1.8V (DDR2) Output or

count, fast transient response and quasi-constant frequency Adjustable from 0.75V to 3.3V

operation over the operation range. POK, OVP, UVP and Thermal Shutdown

The 1.5A source/sink LDO for VTT has fast transient LDO (VTT)

response, requiring only two 10uF of ceramic output

capacitors. In addition, the LDO supply input is available 1.5A Source/Sink Capability

externally to significantly reduce the total power losses. Requires Only Two 10uF Ceramic Output

The uP9011Q supports all the sleep state controls, in S3 Capacitors

state (suspend to RAM) VTT is disable and in S4/S5 Disable in S3 and Soft-Off in S4/S5

(suspend to disk) VDDQ, VTT and VTTREF are soft off.

Thermal Shutdown

The uP9011Q has complete functions including under

voltage protection, over current protection, over voltage + 20mV Accuracy

protection, power-up sequencing, power OK output, and Reference Voltage (VTTREF)

thermal shutdown. The uP9011Q is available in WQFN4x4-

+ 20mV Accuracy

32L package.

Low Noise + 10mA Output

Applications

RoHS Compliant and Halogen Free

Desktop PCs, Notebooks, and Workstations

Microprocessor and Chipset Supplies

Pin Configuration

DDR3/DDR3L/DDR4 Memory Power Supplies

20 PHASE

19 PHASE

18 PHASE

17 PHASE

SSTL-2 SSTL-18 and HSTL Bus Termination

24 VIN

23 VIN

22 VIN

21 VIN

Ordering Information

PHASE 25 16 PGND

Order Number Package Type Top Marking NC 26 Exposed 15 PGND

Pad II

BOOT 27 14 PGND

uP9011QQMI WQFN4x4-32L uP9011Q (VIN)

VTTIN 28 Exposed Pad III 13 PGND

Note: VTT 29 (PHASE) 12 PGND

(1) Please check the sample/production availability with VTTGND 30 Exposed 11 PGND

uPI representatives. VTTSNS 31

Pad I

10 CS

(VTTGND)

(2) uPI products are compatible with the current IPC/

GND 32 9 VCC

JEDEC J-STD-020 requirement. They are halogen-free,

RoHS compliant and 100% matte tin (Sn) plating that are

1

2

3

4

5

6

7

8

suitable for use in SnPb or Pb-free soldering processes.

FB

VDDQ

VTTREF

VTTGND

TON

S3

S5

POK

uP9011Q-DS-F0000, Dec. 2015 1

www.upi-semi.com

uP9011Q

Typical Application Circuit

VIN

TON VIN

POK POK BOOT

PHASE VVDDQ

5V VCC

PGND

CS

S3 S3 FB

S5 S5

VTTREF VDDQ

VTTIN

GND VTT VVTT

VTTGND VTTSNS

Adjustable Output Voltage Regulator for VDDQ

VIN

TON VIN

POK POK BOOT

VVDDQ

PHASE

1.8V/1.5V

5V VCC

PGND

CS

To 5V for DDRII

S3 S3 FB

To GND for DDRIII

S5 S5

VTTREF VDDQ

VTTIN

VVTT

GND VTT

0.9V/0.75V

VTTGND VTTSNS

Fixed Output Voltage Regulator for VDDQ

2 uP9011Q-DS-F0000, Dec. 2015

www.upi-semi.com

uP9011Q

Functional Pin Description

Pin No. Pin Name Pin Function

Buffered Reference Output. Bypass this pin with a 33nF ceramic capacitor to GND. This

1 VTTREF

pin is capable of sourcing up to 10mA current for external loads.

Reference Input for VTT and VTTREF. Connect this pin to the VDDQ output. This pin is

the di scharge current si nki ng termi nal of V D D Q output i n S 4/S 5 states. When V D D Q

2 VD D Q

regulator is in fixed output configuration (FB pin is tied to VCC or GND), this pin is the output

voltage feedback input.

VD D Q Voltage Feedback Input. Thi s pi n i s the i nverti ng i nput of the error ampli fi er. A

resistor divider from output to GND is used to set the regulator output voltage. For fixed

3 FB

output voltage application, connect this pin to VCC for DDR2 power supply, or connect this

pin to GND for DDR3 power supply.

4,30 VTTGND Pow er Ground for the VTT LDO.

S 3 S ig n al In p u t. C onnect thi s pi n to the computer system's S LP _S 3 si gnal. Thi s pi n

5 S3 companied with S5 switches the IC's operating state from active (S0, S1/S2) to S3 and

S4/S5 sleep states.

S 5 S ig n al In p u t. C onnect thi s pi n to the computer system's S LP _S 5 si gnal. Thi s pi n

6 S5 companied with S3 switches the IC's operating state from active (S0, S1/S2) to S3 and

S4/S5 sleep states.

On-Time Setting Pin. Connect a resistor from this pin to VIN to set the on-time for the upper

7 TON

MOSFET.

Pow er OK Indication. POK is the open-drain architecture that indicates the output voltage

is ready or not. This pin is set to high impedance when the output voltage is within regulation

8 POK

and the soft-start ends. POK is pulled low immediately when either output is in soft-start,

standby, shutdown or fault protection.

5V Pow er Supply Input. This pin provides power for internal circuit. Bypass this pin with

9 VC C

a 1uF ceramic capacitor to GND.

Current Limit Threshold Setting. Connect this pin through the setting resistor to VCC for

10 CS

inductor current limit threshold setting.

Pow er Ground. This pin is dedicated for lower MOSFET gate driver and should be directly

11~16 PGND

connected to the source of the lower MOSFET with an isolated path.

Sw itch Node. This pin is used as the sink for the upper MOSFET gate driver. This pin is

17~20, a lso mo ni to re d b y the sho o t-thro ug h p ro te cti o n ci rcui try to d e te rmi ne whe n the up p

PHASE

25 MOSFET has turned off. Connect this pin to the source of the upper MOSFET and the drain

of the lower MOSFET.

21~24 VIN Supply Input. Input voltage that supplies current to the output voltage.

26 NC Not Internally Connected.

Bootstrap Supply for the Floating Upper MOSFET Gate Driver. The bootstrap capacitor

27 BOOT provides the charge to turn on the upper MOSFET. Connect this bootstrap capacitor between

BOOT pin and the PHASE pin to form a bootstrap circuit.

Input for the VTT LDO. This is the drain input to the power device that supplies current to

28 VTTIN

the VTT pin.

Output for the VTT LDO. This pin is the output of VTT. Typical value of two 10uF ceramic

29 VTT capacitors is recommended to reduce the effects of current transients on VOUT. A pull low

resistance exists when the device is disabled.

uP9011Q-DS-F0000, Dec. 2015 3

www.upi-semi.com

uP9011Q

Functional Pin Description

Pin No. Pin Name Pin Function

VTT LDO Output Voltage Sense. Connect this pin to the VTT LDO output capacitors for

31 VTTSNS

VTT output voltage sensing.

32 GND Signal Ground for the IC. All voltage levels are measured with respect to this pin.

Exposed Pad I

Pow er Ground for the VTT LDO.

(VTTGND)

Exposed Pad II

Supply Input. Input voltage that supplies current to the output voltage.

(VIN)

Sw itch Node. This pin is used as the sink for the upper MOSFET gate driver. This pin is

Exposed Pad III also monitored by the shoot-through protection circuitry to determine when the upper MOSFET

(PHASE) has turned off. Connect this pin to the source of the upper MOSFET and the drain of the lower

MOSFET.

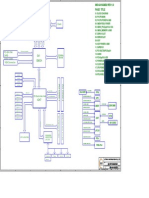

Functional Block Diagram

S3 POR VCC

Output Enable and

S5 Discharge Enable

POK

VPOK

VOV

VTTREF OV

VIN

VTTIN VUV

UV

BOOT

VTT

Control Logic PHASE

VTTGND

PGND

VTTSNS

VDDQ

Zero Cross

Detection

Current

Ramp Limit CS

Soft-Start

Generator

On-time

FB

Calculator

GND

Reference

Voltage

TON

4 uP9011Q-DS-F0000, Dec. 2015

www.upi-semi.com

uP9011Q

Functional Description

The uP9011Q is a high performance synchronous buck VIN

converter with 1.5A source/sink VTT LDO for memory VIN

system power. It also provides the buffered low noise

BOOT

reference with 10mA capability.

The buck converter adopts RCOTTM PWM scheme that PHASE VVDDQ

features easy-to-use, low external component count, fast

PGND

transient response and quasi-constant frequency operation

over the operation range.

RFB1

The 1.5A source/sink VTT LDO has fast transient response FB

that only requires two 10uF of ceramic output capacitors. RFB2

The reference voltage tracks VDDQ/2 within 1% of VDDQ.

The VTT tracks VTTREF within 20mV at no load condition VDDQ

and within 40mV over all load conditions.

Figure 1. VDDQ Output Voltage Setting

The uP9011Q supports all the sleep state controls, and

On-Time Setting

also has complete functions including over current

The uP9011Q adopts a compensated constant-on-time

protection, over voltage protection, thermal shutdown,

control scheme. A resistor RTON connected to TON pin

power-up sequencing, power OK output, and thermal

shutdown. The uP9011Q is available in space-saving programs the constant on time according to equation:

WQFN4x4-32L package. 3.8 × 10 −12 × VDDQ × R TON

TON =

Output Voltage Selection VIN − 0.5 V

As shown in Table 1, uP9011Q can support DDR2, DDR3, where RTON is in kΩ, VIN is the supply input voltage and

DDR3L, DDR4 power supply or adjustable output voltage VDDQ is the sensed output voltage.

by connecting resistor divider to the FB pin.

900

Table 1. Output Voltage Selection

800

FB VTTREF

VD D Q Application

Switching Frequency (kHz)

Connection and VTT 700

VC C 1.8 V VD D Q / 2 DDR2 600

GND 1.5 V VD D Q / 2 DDR3 500

DDR3L, DDR4

Resistor 400

Adjustable VD D Q / 2 0.75V < VVDDQ

Divider

< 3.3V

300

The uP9011Q can adjust output voltage by connecting a 200

resistive voltage divider between VDDQ and GND as shown 300 400 500 600 700 800 900 1000

in Figure 1. Choose RFB2 to be approximately 10kΩ and RTON (kohm)

solve RFB1 using the equation as below: Figure 2. Switching Frequency vs. RTON

Soft Start and POK

R FB1

VDDQ = VREF × (1 + ) The power sequence of uP9011Q is shown in Figure 3.

R FB2

After S5 is set high, VDDQ begins to ramp up after a period

where VREF is 0.75V (typ.). of delay time T1. Then the output voltage begins to soft

start to 90% of the target voltage with time interval T2 as

the end of soft start. The controller then checks the output

voltage after a period of delay time T3. If the output voltage

is in regulation, POK will be set to high impedance to

complete the power on sequence. The POK is an open-

drain output. When fault protection (OVP/UVP/thermal

shutdown) is triggered during operation, the POK will be

pulled low.

uP9011Q-DS-F0000, Dec. 2015 5

www.upi-semi.com

uP9011Q

Functional Description

will keep upper MOSFET off even the voltage loop

commands it to turn on. Converter will latch off if CS pin

VS5

is open during VCC power on or enable.

90%

The output voltage will decrease if the load continuously

VVDDQ/VVTTREF

demands more current than current limit level. Further

increase in load current higher than the current limit level

VPOK will eventually let VVDDQ decrease to trip UVP to shut down

T1 T2 T3 the uP9011Q.

The current limit threshold is set by connecting a resistor

Figure 3. VDDQ Soft Start and POK Timing from CS to VCC. The CS pin will sink a 10uA current

VDDQ Light Load Operation source and create a voltage drop across RCS as the VOCSET.

The uP9011Q automatically reduces switching frequency VOCSET = 10uA x RCS.

at light load to maintain high efficiency. As the output current

When the voltage drop across the lower MOSFET equals

decreases from heavy-load condition, the inductor current

the voltage across the setting resistor, the current limit

will also be reduced, and eventually comes to the point

will be activated.

that its valley touches zero current, which is the boundary

between continuous conduction and discontinuous The current limit level is calculated as:

conduction modes. By emulating the behavior of diodes,

VOCSET IRIPPlE

the lower MOSFET allows only partial of negative current ILIM = +

when the inductor freewheeling current reaches negative. RDS( ON) 2

As the load current is further decreased, it takes longer where IRIPPLE is the peak-to-peak inductor ripple current at

time to discharge the output capacitor to the level than steady state.

requires the next ON cycle.

Over Voltage/Under Voltage Protection

Outputs Control by S3, S5

The uP9011Q monitors FB voltage to detect overvoltage

The uP9011Q provides the output management for the sleep- and undervoltage condition of VDDQ output.

mode signals such as SLP_S3 and SLP_S5 in the

notebook PC system by monitoring S3, S5 status, the When the FB voltage becomes higher than 115% of the

output control table is as shown in Table 2 below. target voltage, the OVP is triggered. Then, upper

MOSFET is off and lower MOSFET is on. When the FB

Table 2. S0, S3 and S5 State voltage is lower than 70% of the target voltage, the UVP

VDDQSN- is triggered after 30us fault detection. Then, upper

State S3 S5 V TTR E F V TT

S MOSFET and lower MOSFET are latched off. This function

S0 High High On On On is enabled 5ms after S5 go high to ensure startup.

Off VCC UVLO

S3 Low High On On

(discharge)

The VCC has under voltage lockout protection (UVLO).

S4 Off Off Off When the VCC voltage is lower than UVLO threshold

Low Low

S5 (discharge) (discharge) (discharge) voltage, all functions are turned off. This is non-latch

protection.

Ouput Discharge Control

Thermal Protection

The uP9011Q is in non-tracking discharge mode when it

enters S4/S5 state. In this non-tracking discharge mode, The uP9011Q monitors the temperature of itself. If the

the uP9011Q discharges the VDDQ and VTT outputs temperature exceeds typical 150OC, the uP9011Q will be

through the internal MOSFETs with 15Ω RDS(on) which are turned off. This is non-latch protection.

connected from VDDQ to GND, and from VTT to VTTGND,

respectively.

Output Current Limit

The synchronous buck VDDQ monitors the inductor valley

current by lower MOSFET RDS(ON) when it turns on. The

over current limit is triggered once the sensing current level

is higher than VOCSET. When triggered, the over current limit

6 uP9011Q-DS-F0000, Dec. 2015

www.upi-semi.com

uP9011Q

Absolute Maximum Rating

(Note 1)

VCC to GND ----------------------------------------------------------------------------------------------------------- -0.3V to +6V

BOOT to PHASE ------------------------------------------------------------------------------------------------------------- -0.3V to +6V

PHASE to GND

DC ------------------------------------------------------------------------------------------------------------------------- -0.3V to +30V

<50ns ------------------------------------------------------------------------------------------------------------------------ -5V to +30V

Other Pins ----------------------------------------------------------------------------------------------------------------------- -0.3V to +6V

Storage Temperature Range ----------------------------------------------------------------------------------- -65OC to +150OC

Junction Temperature ------------------------------------------------------------------------------------------------------- 150OC

Lead Temperature Range(Soldering 10sec) ------------------------------------------------------------------------------------------- 260OC

ESD Rating (Note 2)

HBM(Human Body Mode)---------------------------------------------------------------------------------------------------------------2KV

MM(Mechine Mode)-----------------------------------------------------------------------------------------------------------------------200V

Thermal Information

Package Thermal Resistance (Note 3)

WQFN4x4-32L θJA, controller -------------------------------------------------------------------------------------------- 55OC/W

WQFN4x4-32L θJA, HS -------------------------------------------------------------------------------------------------- 45OC/W

WQFN4x4-32L θJA, LS -------------------------------------------------------------------------------------------------- 39OC/W

WQFN4x4-32L θJC, controller -------------------------------------------------------------------------------------------- 21OC/W

WQFN4x4-32L θJC, HS -------------------------------------------------------------------------------------------------- 12OC/W

WQFN4x4-32L θJC, LS -------------------------------------------------------------------------------------------------- 7OC/W

Power Dissipation, PD @ TA = 25°C

WQFN4x4-32L PD, controller ---------------------------------------------------------------------------------------------------- 1.81W

WQFN4x4-32L PD, HS -------------------------------------------------------------------------------------------------------- 2.22W

WQFN4x4-32L PD, LS -------------------------------------------------------------------------------------------------------- 2.56W

Recommended Operation Conditions

(Note 4)

Supply Input Voltage, VIN ------------------------------------------------------------------------------------------------------- 4.5V to 26V

Control Voltage, VCC ----------------------------------------------------------------------------------------------- 4.5V to 5.5V

Operating Junction Temperature Range -------------------------------------------------------------------- -40OC to +125OC

Operating Ambient Temperature Range -------------------------------------------------------------------------------- -40OC to +85OC

Note 1. Stresses listed as the above Absolute Maximum Ratings may cause permanent damage to the device.

These are for stress ratings. Functional operation of the device at these or any other conditions beyond

those indicated in the operational sections of the specifications is not implied. Exposure to absolute

maximum rating conditions for extended periods may remain possibility to affect device reliability.

Note 2. Devices are ESD sensitive. Handling precaution recommended.

Note 3. θJA is measured in the natural convection at TA = 25°C on a high effective thermal conductivity test board of

JEDEC 51-7 thermal measurement standard.

Note 4. The device is not guaranteed to function outside its operating conditions.

Note 5. Guarantee by design.

uP9011Q-DS-F0000, Dec. 2015 7

www.upi-semi.com

uP9011Q

Electrical Characteristics

(VIN = 15V, VVCC = 5V, VTTIN is connected to VDDQ output, TA = +25OC unless otherwise specified.)

Parameter Symbol Test Conditions Min Typ Max Unit

Supply Current

Supply current, VS3 = 0V, VS5 = 5V, force

-- 470 1000

VCC Current IVCC+PVCC FB above regulation level (no switching). uA

Shutdown current, VS3 = VS5 = 0V -- 1 10

Standby current, VS3 = 0V, VS5 = 5V. No

-- 0.1 10

load at VTT pin

VTTIN Current IVTTIN Shutdown current, VS3 = VS5 = 0V -- 0.1 1 uA

Bias current, VS3 = VS5 = 5V, no load at

-- 1 --

VTT pin.

Operating current, RTON = 1MΩ -- 15 --

TON Current ITON uA

Shutdown current, VS3 = VS5 = 0V -- 0.1 5

Reference Voltage

VVCC = 4.5V to 5.5V 0.742 0.75 0.758

FB Reference Voltage VREF Connect FB pin to VCC. -- 1.8 -- V

Connect FB pin to GND. -- 1.5 --

FB Input Bias Current IFB VFB = 0.75V. -1 0.1 1 uA

VTTREF Output

Connect FB pin to VCC. -- 0.9 --

VTTREF Output Voltage VVTTREF V

Connect FB pin to GND. -- 0.75 --

VTTREF Output Voltage VVDDQ = VVTTIN = 1.8V , | IVTTREF | <10mA -18 -- 18

VVTTREFTO mV

Tolerance VVDDQ = VVTTIN = 1.5V , | IVTTREF | <10mA -15 -- 15

IVTTREFOCLSR-

VTTREF Source Current Limit VVTTREF = 0V 10 -- -- mA

C

VTT Output

VVDDQ = VVTTIN = 1.2V/ 1.35V /1.5V/ 1.8V,

-20 -- 20

IVTT = 0A

VVDDQ = VVTTIN = 1.2V/ 1.35V/ 1.5V /1.8V,

VTT Output Voltage Tolerance VVTTTO -30 -- 30 mV

| IVTT | < 1A

VVDDQ = VVTTIN = 1.2V/ 1.35V, | IVTT | < 1.2A -40 -- 40

VVDDQ = VVTTIN = 1.5V/ 1.8V, | IVTT | < 1.5A -40 -- 40

VVTT = (VVDDQ/ 2) x 0.95 1.5 -- --

VTT Source Current Limit IVTTTOCLSRC A

VVTT = 0V -- 1.3 --

VVTT = (VVDDQ/ 2) x 1.05 1.5 -- --

VTT Sink Current Limit IVTTTOCLSNK A

VVTT = VVDDQ -- 1.3 --

VTTSNS Leakage Current IVTTSNSLK Sink current = 1mA -1 -- 1 uA

VTT Discharge Current IVTTDis VS3 = VS5 = 0V, VVDDQ = 0V, VVTT = 0.5V 10 30 -- mA

8 uP9011Q-DS-F0000, Dec. 2015

www.upi-semi.com

uP9011Q

Electrical Characteristics

Parameter Symbol Test Conditions Min Typ Max Unit

VD D Q

VDDQ Input Resistance RVDDQ -- 100 -- kΩ

VDDQ Discharge Resistance IVDDQDis V S 5 = 0V -- 15 -- Ω

On Time

On-Time TON RTON = 1MΩ , VVDDQ = 1.25V 267 334 401 ns

Minimum On-Time TONMIN -- 80 -- ns

Minimum Off-Time TOFFMIN 250 400 550 ns

Pow er OK

Measured at FB, with respect to

87 90 93

POK Rising Threshold VTHPOKH reference voltage. %

Hysteresis -- 5 --

From FB forced below POK falling

POK Propagation Delay TPOK -- 2.5 -- us

threshold to POK go low.

POK Leakage Current ILK_POK High state, POK = 5V -- -- 1 uA

POK Output Low Voltage VPOK_L Sink current = 1mA -- -- 0.4 V

Logic Input Threshold

High Level Input Voltage VIH S3, S5 High 2 -- -- V

Low Level Input Voltage VIL S 3, S 5 Low -- -- 0.8 V

Logic Input Leakage Current VINLEAK S3, S5 = 5V/0V -1 -- 1 uA

Internal Bootstrap Sw itch

Internal Boost Charging Switch

RBOOT VCC to BOOT, IBOOT = 5mA -- -- 80 Ω

On-Resistance

Pow er Sw itches

Upper Switch Resistance RUG,DSON -- 21.5 26 mΩ

Lower Switch Resistance RLG,DSON -- 9 11 mΩ

Protection: Current Limit

CS Sink Current ICS VCS > 4.5V 9 10 11 uA

ppm/-

CS Current Temp. Coefficient TCICS On the basis of 25OC (Note 5) -- 4700 -- O

C

OCP Comparator Offset VOCLoff GND - VPHASE, RCS = 5kΩ -15 -- 15 mV

Zero Current Threshold VZC GND - VPHASE -5 -- 10 mV

uP9011Q-DS-F0000, Dec. 2015 9

www.upi-semi.com

uP9011Q

Electrical Characteristics

Parameter Symbol Test Conditions Min Typ Max Unit

Protection: UVP & OVP

Measured at FB, with respect to

OVP Trip Threshold VOVP 110 115 120 %

reference voltage.

OVP Propagation Delay TOVPDEL Force FB above OVP trip threshold. -- 20 -- us

Measured at FB, with respect to

UVP Trip Threshold VUVP 60 70 80 %

reference voltage.

UVP Propagation Delay TUVPDEL Force FB below UVP trip threshold. -- 30 -- us

UVP Enable Delay TUVPEN From S5 signal go high -- 2 -- ms

Protection: UVLO

Rising edge 3.9 4.2 4.5

VCC UVLO Threshold VUVLO V

Hysteresis -- 0.12 --

Protection: Thermal Shutdow n

Shutdown temperature -- 150 --

O

Thermal Shutdown Threshold TSDN C

Hysteresis -- 20 --

10 uP9011Q-DS-F0000, Dec. 2015

www.upi-semi.com

uP9011Q

Typical Operation Characteristics

Power On from S3, S5 with Light Load Power On from S3, S5 with Heavy Load

S3,S5 5V/Div S3,S5 5V/Div

VDDQ 1V/Div VDDQ 1V/Div

VTT 500mV/Div VTT 500mV/Div

POK 5V/Div POK 5V/Div

Time: 100us/Div Time: 100us/Div

VIN = 6V, VDDQ = 1.35V, VTT = 0.675V, VIN = 6V, VDDQ = 1.35V, VTT = 0.675V,

VDDQ/VTT Load = no load VDDQ/VTT Load = 0.165Ω/0.5Ω

Power Off from S3, S5 with Light Load Power Off from S3, S5 with Heavy Load

Non Tracking Discharge Non Tracking Discharge

S3,S5 5V/Div S3,S5 5V/Div

VDDQ 1V/Div

VDDQ 1V/Div

VTT 500mV/Div VTT 500mV/Div

POK 5V/Div POK 5V/Div

Time: 200us/Div Time: 20us/Div

VIN = 6V, VDDQ = 1.35V, VTT = 0.675V, VIN = 6V, VDDQ = 1.35V, VTT = 0.675V,

VDDQ/VTT Load = 10Ω/4.7Ω VDDQ/VTT Load = 0.165Ω/0.5Ω

Transient Response Transient Response

(Load Applied: 0.8A to 7.2A) (Load Released: 7.2A to 0.8A)

VDDQ 50mV/Div VDDQ 50mV/Div

PHASE 5V/Div PHASE 5V/Div

IOUT 5A/Div IOUT 5A/Div

Time: 10us/Div Time: 10us/Div

VIN = 6V, VDDQ = 1.35V, L= 0.68uF, VIN = 6V, VDDQ = 1.35V, L= 0.68uF,

COUT = MLCC (22uFx5) COUT = MLCC (22uFx5)

uP9011Q-DS-F0000, Dec. 2015 11

www.upi-semi.com

uP9011Q

Typical Operation Characteristics

Transient Response Transient Response

(Load Applied: 0.8A to 7.2A) (Load Released: 7.2A to 0.8A)

VDDQ 50mV/Div VDDQ 50mV/Div

PHASE 10V/Div PHASE 10V/Div

IOUT 5A/Div IOUT 5A/Div

Time: 10us/Div Time: 10us/Div

VIN = 19V, VDDQ = 1.35V, L= 0.68uF, VIN = 19V, VDDQ = 1.35V, L= 0.68uF,

COUT = MLCC (22uFx5) COUT = MLCC (22uFx5)

OCP & UVP OVP

VDDQ 1V/Div

PHASE 5V/Div

VDDQ 500mV/Div

IL 5A/Div PHASE 5V/Div

POK 5V/Div POK 5V/Div

Time: 10us/Div Time: 20us/Div

VIN = 6V, VDDQ = 1.35V, L= 0.68uF, VIN = 6V, VDDQ = 1.35V, VDDQ Load = 1.5A

COUT = MLCC (22uFx5)

Output Control by S3, S5 VDDQ Line Regulation

1.38

1.37

S3 5V/Div

IOUT = 0A

S5 5V/Div 1.36

VDDQ(V)

VDDQ 1V/Div 1.35

IOUT = 8A

1.34

VTT 1V/Div

1.33

0 5 10 15 20 25 30

Time: 4ms/Div Vin (V)

VIN = 6V, VDDQ = 1.35V, VTT = 0.675V, VCC = 5V

VDDQ/VTT Load = 20Ω/10Ω

12 uP9011Q-DS-F0000, Dec. 2015

www.upi-semi.com

uP9011Q

Application Information

PCB Layout Considerations Place the output capacitor for VTT should close to the

pin with short and wide trace to avoid additional ESR and/

High speed switching and relatively large peak currents in

or ESL of the trace.

a synchronous-rectified buck converter make the PCB layout

a very important part of design. Fast current switching from Connect VTT to the positive of VTT output capacitors

one device to another in a synchronous-rectified buck with a separate trace.

converter causes voltage spikes across the interconnecting VDDQ can be connected separately from VTTIN.

impedances and parasitic circuit elements. The voltage Remember that this sensing potential is the reference

spikes can degrade efficiency and radiate noise that result voltage of VTTREF. Avoid any noise generative lines.

in overvoltage stress on devices. Careful component

Negative node of VTT output capacitor(s) and

placement layout and printed circuit board design minimizes

VTTREF capacitor should be tied together by avoiding

the voltage spikes induced in the converter.

common impedance to the high current path of the VTT

Follow the layout guidelines for optimal performance of source/sink current.

uP9011Q. GND (Signal GND) pin node represents the reference

Keep the PCB trace PHASE node as short and wide potential for VTTREF and VTT outputs. Connect GND to

as possible. negative nodes of VTT capacitor(s), VTTREF capacitor

Add a sunbber circuit between PHASE and PGND to and VDDQ capacitor(s) with care to avoid additional ESR

eliminate the high frequency voltage spike at PHASE node. and/or ESL. GND and PGND (power ground) should be

connected together at a single point.

Keep sensitive analog circuits such as VDDQ,

VTTSNS and CS away from high voltage switching node

such as PHASE.

Connect VDDQ output to VTTIN with short and wide

trace. If other power source is used as VTTIN, a bypass

input capacitor should be placed as close to VTTIN as

possible.

uP9011Q-DS-F0000, Dec. 2015 13

www.upi-semi.com

uP9011Q

Package Information

WQFN4x4-32L

0.00 - 0.10 0.20 - 0.35

0.96 - 1.16

0.10 - 0.20 0.20 - 0.35

0.25 - 0.35

0.20 - 0.35

2.15 - 2.25

3.90 - 4.10

3.90 - 4.10 0.25 - 0.35

0.20 - 0.35 1.01 - 1.21

0.40 BSC 0.20 - 0.35

Pin 1 mark

Bottom View - Exposed Pad

0.70 - 0.80

0.0 - 0.05 0.20 REF

Note

1.Package Outline Unit Description:

BSC: Basic. Represents theoretical exact dimension or dimension target

MIN: Minimum dimension specified.

MAX: Maximum dimension specified.

REF: Reference. Represents dimension for reference use only. This value is not a device specification.

TYP. Typical. Provided as a general value. This value is not a device specification.

2.Dimensions in Millimeters.

3.Drawing not to scale.

4.These dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm.

14 uP9011Q-DS-F0000, Dec. 2015

www.upi-semi.com

uP9011Q

Important Notice

uPI and its subsidiaries reserve the right to make corrections, modifications, enhancements, improvements, and other

changes to its products and services at any time and to discontinue any product or service without notice. Customers

should obtain the latest relevant information before placing orders and should verify that such information is current and

complete.

uPI products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment.

However, no responsibility is assumed by uPI or its subsidiaries for its use or application of any product or circuit; nor

for any infringements of patents or other rights of third parties which may result from its use or application, including but

not limited to any consequential or incidental damages. No uPI components are designed, intended or authorized for

use in military, aerospace, automotive applications nor in systems for surgical implantation or life-sustaining. No license

is granted by implication or otherwise under any patent or patent rights of uPI or its subsidiaries.

COPYRIGHT (C) 2013, UPI SEMICONDUCTOR CORP.

uPI Semiconductor Corp. uPI Semiconductor Corp.

Headquarter Sales Branch Office

9F.,No.5, Taiyuan 1st St. Zhubei City, 12F-5, No. 408, Ruiguang Rd. Neihu District,

Hsinchu Taiwan, R.O.C. Taipei Taiwan, R.O.C.

TEL : 886.3.560.1666 FAX : 886.3.560.1888 TEL : 886.2.8751.2062 FAX : 886.2.8751.5064

uP9011Q-DS-F0000, Dec. 2015 15

www.upi-semi.com

You might also like

- V320BJ6-Q01ApprovalSpec V2.0 20160712 CommonDocument33 pagesV320BJ6-Q01ApprovalSpec V2.0 20160712 CommonbosryanbroNo ratings yet

- LG Eax64905301 Led TV Power SupplyDocument2 pagesLG Eax64905301 Led TV Power Supplyies83775% (8)

- Ncp81205a DDocument28 pagesNcp81205a DBlue Stacks100% (1)

- Samsung UA32N4300AK Chassis UAV81Document55 pagesSamsung UA32N4300AK Chassis UAV81Francisco NavarroNo ratings yet

- Jeep Style Twin Bed Assembly IntructionsDocument14 pagesJeep Style Twin Bed Assembly IntructionsHumberto AndujarNo ratings yet

- NT50262MQG Nihon Dempa Kogyo Co LTD Product DetailsDocument3 pagesNT50262MQG Nihon Dempa Kogyo Co LTD Product DetailskevynNo ratings yet

- Schematic Asus k43sd Rev 2.2Document3 pagesSchematic Asus k43sd Rev 2.2JoungAmbon43% (7)

- Quick Installation Guide LVDS VGA Rev1.01Document2 pagesQuick Installation Guide LVDS VGA Rev1.01Emmanuel VenturaNo ratings yet

- Gambit MLK MT - A00 - 20180202 - 01Document107 pagesGambit MLK MT - A00 - 20180202 - 01Tin Học Chí CôngNo ratings yet

- NT71710MFG 000Document1 pageNT71710MFG 000Tahir Hussain50% (4)

- Ali-M3329 819 DatasheetDocument1 pageAli-M3329 819 Datasheetmarcoslemos100043% (14)

- Panel Boe Hv320wxc-100 0 (DS)Document27 pagesPanel Boe Hv320wxc-100 0 (DS)Milorad PajovicNo ratings yet

- Title: HV430FHB-N10 Product Specification: 拟制 审核 批准 DateDocument29 pagesTitle: HV430FHB-N10 Product Specification: 拟制 审核 批准 DateGeovanny Jose Sanjuan Bustamante100% (1)

- WTR2965 PDFDocument1 pageWTR2965 PDFPranay Joshi50% (2)

- 30GXR170-640 Compressor - Carrier ChillerDocument34 pages30GXR170-640 Compressor - Carrier ChillercafonchoNo ratings yet

- Huawei ODN PortfolioDocument3 pagesHuawei ODN PortfolioAlexander Pischulin100% (1)

- V236BJ1-P03 DatasheetDocument33 pagesV236BJ1-P03 DatasheetAlexis UrquetaNo ratings yet

- Ecs V10il1 - 37GV10000-C0 - Rev CDocument32 pagesEcs V10il1 - 37GV10000-C0 - Rev CHendra R. Rattu75% (4)

- HV320WHB-F56 Rev (2024-05-22 07 - 09 - 07)Document34 pagesHV320WHB-F56 Rev (2024-05-22 07 - 09 - 07)bali tennaNo ratings yet

- HV320WX2-176-BOE LCD PanelDocument23 pagesHV320WX2-176-BOE LCD PanelEdwin Ondoy100% (1)

- FUENTE SILERGY MARKING CODES BadcapsDocument2 pagesFUENTE SILERGY MARKING CODES Badcapsmarco guamialama67% (3)

- K24C02 (C) /K24C04/K24C08 (C) /K24C16: Two-Wire Serial EEPROMDocument12 pagesK24C02 (C) /K24C04/K24C08 (C) /K24C16: Two-Wire Serial EEPROMAlex Achmad RisdianNo ratings yet

- SIO KB9012 To RT809F PDFDocument7 pagesSIO KB9012 To RT809F PDFBivek BasnetNo ratings yet

- TH L32C22D PDFDocument73 pagesTH L32C22D PDFmanish100% (5)

- IT8528EDocument80 pagesIT8528EKzher MelikNo ratings yet

- GA-H61M-DS2 R201 Schematic PDFDocument30 pagesGA-H61M-DS2 R201 Schematic PDFscobaNo ratings yet

- Training Material of MS306C&D ChassisDocument42 pagesTraining Material of MS306C&D Chassisبوند بوند100% (1)

- Wistron Hellcat 13 SchematicsDocument105 pagesWistron Hellcat 13 SchematicsCristian Jesus Camarillo TamayoNo ratings yet

- HP Probook 450 g3 Quanta x63 Da0x63mb6h1 R1aDocument67 pagesHP Probook 450 g3 Quanta x63 Da0x63mb6h1 R1aNeven PiscutiNo ratings yet

- TP vst59 PA671+Schematic+DiagramDocument7 pagesTP vst59 PA671+Schematic+DiagramSanjeev smith100% (1)

- User Manual TV Power Demoboard TEA8818DB1440: TEA8818 + TEA1995 130W 13V and 90V Power SupplyDocument29 pagesUser Manual TV Power Demoboard TEA8818DB1440: TEA8818 + TEA1995 130W 13V and 90V Power SupplyCube7 Geronimo50% (2)

- Block Diagram: LGA 775-Pin SocketDocument20 pagesBlock Diagram: LGA 775-Pin SocketRajesh DhanambalNo ratings yet

- H81M-DS2: Power SequenceDocument2 pagesH81M-DS2: Power SequenceHilario Serrano Flores100% (5)

- Panasonic TH l24c20dDocument39 pagesPanasonic TH l24c20dKingsleen33% (3)

- All Laptop Motherboard IC Equivalents - BD-FIXDocument8 pagesAll Laptop Motherboard IC Equivalents - BD-FIXRichard Yoel Perez CarbajalNo ratings yet

- SchematicDocument1 pageSchematicM Namir Hasan100% (1)

- Details PDF: Image Part Number Description Manufacturer QuantityDocument1 pageDetails PDF: Image Part Number Description Manufacturer QuantityLautiSenn100% (5)

- 25Q32BSIGDocument46 pages25Q32BSIGpepe100% (2)

- COF TAB Replacement TableDocument4 pagesCOF TAB Replacement TableHector David EsplugasNo ratings yet

- Package Including: 5pcs "FIX D6 30-30 LVDS Cable"Document5 pagesPackage Including: 5pcs "FIX D6 30-30 LVDS Cable"Ahmad Suffian Ismail100% (1)

- Redmi 6a Schematic DiagramDocument34 pagesRedmi 6a Schematic DiagramKaran Matale80% (5)

- HV320WHB N00 BoeDocument23 pagesHV320WHB N00 Boesivanka ranganaNo ratings yet

- Acer Veriton Z291G Emachines EZ1711 Wistron Pi010L 09194 1 E VMARR PDFDocument31 pagesAcer Veriton Z291G Emachines EZ1711 Wistron Pi010L 09194 1 E VMARR PDFSebastian Matias100% (1)

- BN44 00155aDocument2 pagesBN44 00155aEwerton Correia FrançaNo ratings yet

- T.VST29.03 4Document13 pagesT.VST29.03 4Sutrisno Ok100% (1)

- Panel LG Display Lc216exn-Sfa1 0Document36 pagesPanel LG Display Lc216exn-Sfa1 0Rinaldy100% (1)

- Sony-40bx400 Developer AwladDocument2 pagesSony-40bx400 Developer AwladDeveloper Awlad100% (1)

- Complete DDR3/ DDR4 Memory Power Solution Controller: General Description FeaturesDocument15 pagesComplete DDR3/ DDR4 Memory Power Solution Controller: General Description FeaturesIgor LabutinNo ratings yet

- 3/2/1-Phase Synchronous-Rectified Buck Controller For Mobile GPU PowerDocument12 pages3/2/1-Phase Synchronous-Rectified Buck Controller For Mobile GPU Powernmo1122No ratings yet

- Infineon TDA21472 DataSheet v02 - 00 ENDocument24 pagesInfineon TDA21472 DataSheet v02 - 00 ENaxial1976No ratings yet

- UP1962SDocument14 pagesUP1962Stechgamebr85No ratings yet

- High Efficiency, Main Power Supply Controller For Notebook ComputerDocument23 pagesHigh Efficiency, Main Power Supply Controller For Notebook ComputerLeo CarlosamaNo ratings yet

- RT8223PDocument23 pagesRT8223Pfernando guerreroNo ratings yet

- RT9088ADocument11 pagesRT9088AБахтиёр БехбудовNo ratings yet

- uP1624P uPISemiconductorDocument18 pagesuP1624P uPISemiconductorSony SanNo ratings yet

- Confidential: Dual Synchronous Buck Controller With 5V/3.3V 100ma Ldos For Notebook System PowerDocument18 pagesConfidential: Dual Synchronous Buck Controller With 5V/3.3V 100ma Ldos For Notebook System PowerevilplayerindoNo ratings yet

- Single Synchronous Buck Controller: RT8202L/MDocument19 pagesSingle Synchronous Buck Controller: RT8202L/MDenis DenisovNo ratings yet

- Data SheetDocument15 pagesData Sheetzakie wahyuNo ratings yet

- uPI Confidential: 3A Ultra Low Dropout Linear RegulatorDocument13 pagesuPI Confidential: 3A Ultra Low Dropout Linear RegulatorLEONNo ratings yet

- Single-Phase PWM Controller For CPU / GPU Core Power Supply: RT8152C/DDocument24 pagesSingle-Phase PWM Controller For CPU / GPU Core Power Supply: RT8152C/DakashNo ratings yet

- Integrated Power Solution For TFT-LCD: Global Mixed-Mode Technology IncDocument1 pageIntegrated Power Solution For TFT-LCD: Global Mixed-Mode Technology IncVeicon VecNo ratings yet

- Single Synchronous Buck Controller: RT8202/A/BDocument18 pagesSingle Synchronous Buck Controller: RT8202/A/BMax ReparNo ratings yet

- LP3102Document7 pagesLP3102เจตนิพิฐ วีระพันธ์ไพบูลย์No ratings yet

- NCP81253 5 V MOSFET Driver Compatible With Single-Phase IMVP8 ControllersDocument10 pagesNCP81253 5 V MOSFET Driver Compatible With Single-Phase IMVP8 ControllersBlue StacksNo ratings yet

- Surface Mount Type CS, CT, CX: Conductive Polymer Aluminum Electrolytic CapacitorsDocument4 pagesSurface Mount Type CS, CT, CX: Conductive Polymer Aluminum Electrolytic CapacitorsBlue StacksNo ratings yet

- SSM6N44FE: High Speed Switching Applications Analog Switching ApplicationsDocument5 pagesSSM6N44FE: High Speed Switching Applications Analog Switching ApplicationsBlue StacksNo ratings yet

- Si 2336 DSDocument10 pagesSi 2336 DSBlue StacksNo ratings yet

- Avea 20190627Document2 pagesAvea 20190627Blue StacksNo ratings yet

- Diode Package Cross ReferenceDocument1 pageDiode Package Cross ReferenceBlue StacksNo ratings yet

- Diodes ListDocument20 pagesDiodes ListBlue StacksNo ratings yet

- 2018 Semiconductor Product GuideDocument123 pages2018 Semiconductor Product GuideBlue StacksNo ratings yet

- Wingel Brochure - MLGM - Wingel-Brochure-MlgmDocument4 pagesWingel Brochure - MLGM - Wingel-Brochure-MlgmbambangNo ratings yet

- Boiler Controls Index: Click On TIS Number To View TIS SheetDocument17 pagesBoiler Controls Index: Click On TIS Number To View TIS SheetFreddy YánezNo ratings yet

- Factory Automation - Sensing Your Needs: Pmi Inductive Positioning Measuring SystemsDocument8 pagesFactory Automation - Sensing Your Needs: Pmi Inductive Positioning Measuring SystemsticojfsNo ratings yet

- Dimension Device CompatibilityDocument18 pagesDimension Device CompatibilityChetan The game changerNo ratings yet

- Physics Investigatory Project Work: Jawahar Navodaya Vidyalaya, VATTEM - 509203Document19 pagesPhysics Investigatory Project Work: Jawahar Navodaya Vidyalaya, VATTEM - 509203Md SohelNo ratings yet

- S C C P U: Elf-Ontained Ooling Ackage NitsDocument60 pagesS C C P U: Elf-Ontained Ooling Ackage Nitsdavid villaNo ratings yet

- Next Gen Ford Everest Digital BrochureDocument12 pagesNext Gen Ford Everest Digital Brochureyanafic282No ratings yet

- Iic-Sedena-Mz-09-0 Esp. Téc. Controlador MP-1Document6 pagesIic-Sedena-Mz-09-0 Esp. Téc. Controlador MP-1Héctor RiveraNo ratings yet

- Kobetsu Kaizen Zero Air Leakege PresentationDocument25 pagesKobetsu Kaizen Zero Air Leakege PresentationajaydeepNo ratings yet

- Fpe (22326)Document4 pagesFpe (22326)pratik PTNo ratings yet

- Electric QAQC ProcedureDocument34 pagesElectric QAQC ProcedureDaengkulle Firmansyah Putera100% (1)

- Bomba de EngraseDocument180 pagesBomba de EngraseRONALD ADAN ABARCA BERNARDONo ratings yet

- Product Specification: Product Mode Abbreviation Client Customer Audit SupplierDocument14 pagesProduct Specification: Product Mode Abbreviation Client Customer Audit SupplierZoran Truba TrumbetašNo ratings yet

- EEE3100S 2023 Tutorials 6-7Document3 pagesEEE3100S 2023 Tutorials 6-7Stalin KosterNo ratings yet

- STAMFORD S0 S1 Brochure - Secured - 0Document8 pagesSTAMFORD S0 S1 Brochure - Secured - 0ThijsNo ratings yet

- XDS2000 Series DSO DatasheetDocument2 pagesXDS2000 Series DSO DatasheetpeladillanetNo ratings yet

- 36 - Effective Pages: Beechcraft CorporationDocument32 pages36 - Effective Pages: Beechcraft Corporationaviacion gnaNo ratings yet

- Mitsubishi VFD ManualDocument43 pagesMitsubishi VFD ManuallifttecNo ratings yet

- Operation manual-HM5001 TTRDocument15 pagesOperation manual-HM5001 TTRGio CJNo ratings yet

- Differential and Bevel Gear: - InstallDocument5 pagesDifferential and Bevel Gear: - InstallMuhamad Dwi CahyonoNo ratings yet

- Toyo Pricelist Year 2023Document16 pagesToyo Pricelist Year 2023John Ricky BenicoNo ratings yet

- X67ps1300-Eng V2.25Document4 pagesX67ps1300-Eng V2.25joao oliveiraNo ratings yet

- FHFC-71 + RZFC-71 (SkyAir R32 Inverter)Document1 pageFHFC-71 + RZFC-71 (SkyAir R32 Inverter)Surya LiemNo ratings yet

- Electrical Thumb Rules - (Part 1)Document4 pagesElectrical Thumb Rules - (Part 1)rajdeep maity100% (2)

- MmuDocument113 pagesMmuSunny San100% (1)

- CopelandDocument1 pageCopelandEdwin GallegosNo ratings yet

- Buzzwangle Calado EncendidoDocument4 pagesBuzzwangle Calado EncendidoEusebio Pons FontanalsNo ratings yet