Professional Documents

Culture Documents

DATASHEET Up1542r

DATASHEET Up1542r

Uploaded by

joao doisssOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DATASHEET Up1542r

DATASHEET Up1542r

Uploaded by

joao doisssCopyright:

Available Formats

uP1542

5V/12V Synchronous-Rectified Buck Controller

General Description Features

The uP1542 is a compact synchronous-rectified buck Operates from 5V or 12V Supply Voltage

controller specifically designed to operate from 5V or 12V 3.3V to 12V VIN Input Range

supply voltage and to deliver high quality output voltage

as low as 0.6V for uP1542S/U (linear OCP). VREF with 1.0% Accuracy:

The uP1542 adopts constant frequency, voltage mode uP1542S/U: 0.6V VREF

control scheme, featuring easy-to-use, low external uP1542T/Q/V: 0.8V VREF

component count, and fast transient response. Fixed

Stand Alone Mode Operation

300kHz operation provides an optimal level of integration

to reduce size and cost of the power supply. Simple Single-Loop Control Design

This controller integrates internal MOSFET drivers that Voltage-Mode PWM Control

support 12V+12V bootstrapped voltage for high efficiency Fast Transient Response

power conversion. The bootstrap diode is built-in to simplify

Fixed 300kHz Switching Frequency

the circuit design and minimize external part count.

Other features include internal soft start, over/under High-Bandwidth Error Amplifier

voltage protection, over current protection and shutdown 0% to 90% Duty Cycle

function. With aforementioned functions, this part provides Lossless, Adjuatable Over Current Protection

customers a compact, high efficiency, well-protected and

cost-effective solutions. This part is available in PSOP- Uses Lower MOSFET RDS(ON)

8L and WDFN2x2-8L package. uP1542S/U: Linear OCP

uP1542T/Q/V: Fixed OCP

Pin Configuration

Internal Soft Start

BOOT 1 8 PH Integrated Boot Diode

UG 2 9 7 COMP/EN PSOP-8L and WDFN2x2-8L Package

OCS 3 GND 6 FB RoHS Compliant and Halogen Free

LG 4 5 VCC

Applications

PSOP-8L (uP1542S)

Power Supplies for Microprocessors or

Subsystem Power Supplies

BOOT 1 8 PH Cable Modems, Set Top Boxes, and DSL Modems

UG 2 9 7 COMP/EN Industrial Power Supplies; General Purpose

GND 3 GND 6 FB Supplies

LG 4 5 VCC 5V or 12V Input DC-DC Regulators

PSOP-8L (uP1542Q/T/V)

Low-Voltage Distributed Power Supplies

BOOT 1 8 PH

UG 2 7 COMP/SD

GND

OCS 3 6 FB

LG 4 5 VCC

WDFN2x2-8L (uP1542U)

uP1542-DS-F00A0, Apr. 2018 1

www.upi-semi.com

uP1542

Ordering Information

Order Number Package Type VREF Remark Top Marking

uP1542SSU8 0.6V linear OCP uP1542S

uP1542TSU8 0.8V fixed OCP@225mV uP1542T

PSOP-8L

uP1542QSU8 0.8V fixed OCP@300mV uP1542Q

uP1542VSU8 0.8V fixed OCP@375mV uP1542V

uP1542UDD8 WDFN2x2-8L 0.6V linear OCP DJ

Note:

(1) Please check the sample/production availability with uPI representatives.

(2) uPI products are compatible with the current IPC/JEDEC J-STD-020 requirement. They are halogen-free,

RoHS compliant and 100% matte tin (Sn) plating that are suitable for use in SnPb or Pb-free soldering processes.

Functional Pin Description

Pin Name Pin Function

B ootstrap Supply for the floati ng upper gate dri ver. C onnect the bootstrap capaci tor between

BOOT BOOT pin and the PH pin to form a bootstrap circuit. The bootstrap capacitor provides the charge

to turn on the upper MOSFET.

Upper Gate Driver Output. Connect this pin to the gate of upper MOSFET. This pin is monitored

UG by the adaptive shoot-through protection circuitry to determine when the upper MOSFET has turned

off.

GND Ground.

OCS Over Current Protection Setting. Connect a resistor from this pin to GND to set the OCP level.

Low er Gate Driver Output. Connect this pin to the gate of lower MOSFET. This pin is monitored

LG by the adaptive shoot-through protection circuitry to determine when the lower MOSFET has turned

off.

Supply Voltage. This pin provides the bias supply for the uP1542 and the lower gate driver. Connect

VC C a well-decoupled 4.5V to 13.2V supply voltage to this pin. Ensure that a decoupling capacitor is

placed near the IC.

Feedback Voltage. This pin is the inverting input to the error amplifier. A resistor divider from the

FB output to GND is used to set the regulation voltage. Use this pin in combination with the COMP/EN

pin to compensate the voltage control feedback loop of the converter.

Error Amplifier Output. This is the output of the error amplifier and the non-inverting input of the

PWM comparator. Use this pin in combination with the FB pin to compensate the voltage-control

COMP/EN

feedback loop of the converter. Pulling COMP/EN to a level below 0.3V disables the controller and

causes the oscillator to stop, the UG and LG outputs to be held low.

PHASE Sw itch Node. Connect this pin to the source of the upper MOSFET and the drain of the

lower MOSFET. This pin is used as the sink for the UG driver, and to monitor the voltage drop across

PH

the lower MOSFET for over current protection. This pin is also monitored by the adaptive shoot-

through protection circuitry to determine when the upper MOSFET has turned off.

Ground. The exposed pad is the dominate heat conducting path and should be well soldered to the

Exposed Pad

PCB with multiple vias for optimal thermal performance.

2 uP1542-DS-F00A0, Apr. 2018

www.upi-semi.com

uP1542

Typical Application Circuit

VIN

VCC UG

GND BOOT

PH VOUT

COMP/EN

LG R1

Shut

Down

FB

OCS

R2

Functional Block Diagram

OCS VCC

4.2V

Enable Enable POR VDD Internal

Soft Start POR BOOT

Logic Regulator

SS

Protection

0.3V

VOCP UG

1.0V OCP

COMP/EN

FB PWM Gate

Error Control PH

Amplifier PWM Logic

Comparator VCC

VREF

0.6V/uP1542S/U

Oscillator LG

VFB VFB GND

OVP UVP

1.25xVREF 0.3xVREF

uP1542-DS-F00A0, Apr. 2018 3

www.upi-semi.com

uP1542

Functional Description

The uP1542 is a compact synchronous-rectified buck 1V

controller specifically designed to operate from 5V or 12V

0.3V

supply voltage and to deliver high quality output voltage

COMP/EN

as low as 0.6V. Chip

Disable Enable

Supply Voltage

FB

The VCC pin receives a well-decoupled 4.5V to 13.2V Enable

uP1542

supply voltage to power the control circuit, the lower gate VREF

Error

driver and the bootstrap circuit for the higher gate driver. Amplifier

A minimum 1uF ceramic capacitor is recommended to

bypass the supply voltage. Place the bypassing capacitor Figure 1. Chip Enable Function

physically near the IC. Soft Start

An internal linear regulator regulates the supply voltage A built-in Soft Start is used to prevent surge current from

into a 4.2V voltage VDD for internal control logic circuit. power supply input during turn on (referring to the

No external bypass capacitor is required for filtering the Functional Block Diagram). The error amplifier is a three-

VDD voltage. input device. Reference voltage VREF or the internal soft

The uP1542 integrates MOSFET gate drives that are start voltage SS whichever is smaller dominates the

powered from the VCC pin and support 12V+12V driving behavior of the non-inverting inputs of the error amplifier.

capability. A bootstrap diode is embedded to facilitate PCB SS internally ramps up to VCC and the output voltage will

design and reduce the total BOM cost. No external follow the SS signal and ramp up smoothly to its target

Schottky diode is required. Converters that consist of level.

uP1542 feature high efficiency without special The SS signal keeps ramping up after it exceeds the

consideration on the selection of MOSFETs. reference voltage VREF. However, the reference voltage

Note: The embedded bootstrap diode is not a VREF takes over the behavior of error amplifier after SS >

Schottky diode having a 0.8V forward voltage. VREF. When the SS signal climb to 1.3 x VREF, the uP1542

External Schottky diode is highly recommended if the claims the end of softstart cycle and enables the over and

VCC voltage is expected to be lower than 5.0V. under voltage protection of the output voltage.

Otherwise the bootstrap diode may be too low for the Figure 2 shows a typical start up interval for uP1542 where

device to work normally. the COMP/SD pin has been released from a grounded

Power On Reset and Chip Enable (system shutdown) state.

A power on reset (POR) circuitry continuously monitors The internal 80uA current source starts to charge the

the supply voltage at VCC pin. Once the rising POR compensation network after the COMP/SD pin is released

threshold is exceeded, the uP1542 sets itself to active from grounded at T1. The COMP/SD exceeds 0.3V and

state and is ready to accept chip enable command. The enables the uP1542 at T2. The COMP/SD continues

rising POR threshold is typically 4.2V at VCC rising. ramping up and stays at 1V before the SS starts ramping

up at T3. The uP1542 initializes itself such as current limit

The COMP/EN is a multifunctional pin: control loop

level setting (see the relative section) during the time

compensation and chip enable as shown in Figure 1. An

interval between T2 and T3. The output voltage follows

Enable Comparator monitors the COMP/EN pin voltage

the internal SS and ramps up to its final level during T3

for chip enable. A signal level transistor is adequate to

and T4. At T4, the reference voltage VREF takes over the

pull this pin down to ground and shut down the uP1542. behavior of the error amplifier as the internal SS crosses

An 80uA current source charges the external VREF. The internal SS keeps ramping up and reaches 1.3 x

compensation network with 1.0V ceiling when this pin is VREF at T5, where the uP1542 asserts the end of softstart

released. If the voltage at COMP/EN pin exceeds 0.3V, cycle.

the uP1542 initiates its softstart cycle.

The 80uA current source keeps charging the COMP pin

to its ceiling until the feedback loop boosts the COMP pin

higher than 0.8V according to the feedback signal. The

current source is cut off when VCOMP is higher than 1.0V

during normal operation.

4 uP1542-DS-F00A0, Apr. 2018

www.upi-semi.com

uP1542

Functional Description

Ramp COMP/EN Figure 3. Softstart where VIN does not Present Initially.

Output Voltage Selection

0.3V

SS The output voltage can be programmed to any level

VREF between the reference voltage VREF up to the 90% of VIN

VOUT supply. The lower limitation of output voltage is caused by

the internal reference. The upper limitation of the output

voltage is caused by the maximum available duty cycle

(90% typical). This is to leave enough time for over current

T1 T3 T4 T5

detection. Output voltage out of this range is not allowed.

T2

An voltage divider sets the output voltage (refer to the

Typical Application Circuit on page 3 for detail). In real

COMP (1V/Div) applications, choose R1 in 1kΩ ~ 10kΩ range and choose

appropriate R2 according to the desired output voltage.

R1 + R2

VOUT (1V/Div) VOUT = VREF ×

R2

Over Current Protection (OCP)

The uP1542 detects voltage drop across the lower

LGATE (10V/Div)

MOSFET (VPHASE) for over current protection when it is

turned on. If VPHASE is lower than the user-programmable

voltage VOCP, the uP1542 asserts OCP and shuts down

the converter. The OCP level can be programmed by OCS

pin (uP1542S/U) or fixed at 300mV (uP1542Q).

Time 2ms/Div

The uP1542 sources a 20uA current source out of OCS

Figure 2. Softstart Behavior of uP1542. pin. Connect resistor ROCS at OCS pin to create voltage

Power Input Detection level VOCS for OCP setting. The maximum of VOCP should

not be larger than 375mV.

The uP1542 detects PH voltage for the present of power

input when the UG turns on the first time. If the PH voltage 20uA × R OCS

does not exceed 1.0V when the UG turns on, the uP1542 VOCS =

4

asserts that power input in not ready and stops the softstart

cycle. Another softstart cycle is initiate after a 6ms time

delay. Figure 4 shows the start up interval where VIN does VOCP = VOCS

not present initially.

VOCP

IOCP = (A)

RDS( ON)

For example:

If VOCP = 375mV, and RDS(ON) = 10mΩ, the IOCP will be 37.5A.

VIN (5V/Div)

If VOCP = 225mV, and RDS(ON) = 10mΩ, the IOCP will be 22.5A.

VOUT (1V/Div) Over Voltage and Under Voltage Protection

The uP1542 asserts over voltage protection if the feedback

voltage VFB is higher than 125% of reference voltage VREF.

The uP1542 asserts under voltage protection if the

feedback voltage VFB is lower than 30% of reference

LGATE (10V/Div)

voltage VREF after soft start end. The uP1542 turns off

IL (5A/Div) both higher and lower gate drivers upon UVP and turns

on lower gate driver upon OVP. Both UVP and OVP are

Time 4ms/Div latch-off type and can be reset by POR or toggling the

COMP/EN pin.

uP1542-DS-F00A0, Apr. 2018 5

www.upi-semi.com

uP1542

Absolute Maximum Rating

(Note 1)

Supply Input Voltage, VCC -------------------------------------------------------------------------------------- -0.3V to +15V

BOOT to PH --------------------------------------------------------------------------------------------------------------------- -0.3V to +15V

PH to GND

DC ------------------------------------------------------------------------------------------------------------------------- -0.7V to 15V

< 200ns --------------------------------------------------------------------------------------------------------------------- -8V to 30V

BOOT to GND

DC --------------------------------------------------------------------------------------------------------------- -0.3V to VCC + 15V

< 200ns ------------------------------------------------------------------------------------------------------------------ -0.3V to 42V

UG to PH

DC------------------------------------------------------------------------------------------------------- -0.3V to (BOOT - PH +0.3V)

<200ns ------------------------------------------------------------------------------------------------ -5V to (BOOT - PH + 0.3V)

LG to GND

DC ---------------------------------------------------------------------------------------------------------- -0.3V to + (VCC + 0.3V)

<200ns ---------------------------------------------------------------------------------------------------------- -5V to VCC + 0.3V

Other Pins -------------------------------------------------------------------------------------------------------------------------- -0.3V to +6V

Storage Temperature Range ----------------------------------------------------------------------------------------------- -65OC to +150OC

Junction Temperature --------------------------------------------------------------------------------------------------------------------- 150OC

Lead Temperature (Soldering, 10 sec) ------------------------------------------------------------------------------------------------ 260OC

ESD Rating (Note 2)

HBM (Human Body Mode) ------------------------------------------------------------------------------------------------------- 2kV

MM (Machine Mode) --------------------------------------------------------------------------------------------------------------- 200V

Thermal Information

Package Thermal Resistance (Note 3)

PSOP-8L θJA ----------------------------------------------------------------------------------------------------------------- 47OC/W

WDFN2x2-8L θJA ---------------------------------------------------------------------------------------------------------- 155OC/W

PSOP-8L θJC ---------------------------------------------------------------------------------------------------------------- 17.9OC/W

WDFN2x2-8L θJC ------------------------------------------------------------------------------------------------------------- 20OC/W

Power Dissipation, PD @ TA = 25OC

PSOP-8L ----------------------------------------------------------------------------------------------------------------------------- 2.13W

WDFN2x2-8L ------------------------------------------------------------------------------------------------------------------------ 0.65W

Recommended Operation Conditions

(Note 4)

Operating Junction Temperature Range ------------------------------------------------------------------------------- -40OC to +125OC

Operating Ambient Temperature Range --------------------------------------------------------------------------------- -40OC to +85OC

Supply Input Voltage, VCC ----------------------------------------------------------------------------------------------------- +4.5V to 13.2V

6 uP1542-DS-F00A0, Apr. 2018

www.upi-semi.com

uP1542

Electrical Characteristics

(VCC = 12V, TA = 25OC, unless otherwise specified)

Parameter Symbol Test Conditions Min Typ Max Units

Supply Input

Supply Voltage VCC 4.5 -- 13.2 V

UG and LG Open, VCC = 12V,

Supply Current ICC -- 3 -- mA

Switching

Quiescent Supply Current ICC_Q VFB = VREF + 0.1V, No Switching -- 1.3 -- mA

Power Input Voltage VIN 3.0 -- 13.2 V

Pow er On Reset

POR Threshold VCCRTH VCC rising 4.0 4.2 4.4 V

POR Hysteresis VCCHYS -- 0.5 -- V

Sw itching Frequency

Free Running Frequency fOSC 270 300 330 kHz

Ramp Amplitude ∆VOSC V C C = 12V -- 3 -- VP-P

Reference Voltage

uP1542S/U 0.594 0.60 0.606 V

Internal Reference Voltage Accuracy V FB

uP1542T/Q/V 0.792 0.800 0.808 V

Error Amplifier

Open Loop DC Gain AO Guaranteed by Design 55 70 -- dB

Gain-Bandwidth Product GBW Guaranteed by Design -- 10 -- MHz

Slew Rate SR Guaranteed by Design 3 6 -- V/us

Transconductance 600 800 1000 uA/V

Output Source Current VFB < VREF 80 120 -- uA

Output Sink Current VFB > VREF 80 120 -- uA

Input Offset Voltage -1.0 0 1.0 mV

Input Leakage Current -- 0.1 1.0 nA

PWM Controller Gate Drivers

Upper Gate Source RUG_SRC IUG = 100mA Source -- 3 5 Ω

Upper Gate Sink RUG_SNK IUG = 100mA Sink -- 1.5 3 Ω

Lower Gate Source RLG_SRC IUG = 100mA Source -- 3 5 Ω

Lower Gate Sink RLG_SNK IUG = 100mA Sink -- 1 2 Ω

uP1542-DS-F00A0, Apr. 2018 7

www.upi-semi.com

uP1542

Electrical Characteristics

Parameter Symbol Test C onditions Min Typ Max U nits

PWM C ontroller Gate D rivers

PH Falli ng to LG Ri si ng D elay VPH < 1.2V to VLG > 1.2V -- 30 -- ns

LG Falli ng to UG Ri si ng D elay VLG < 1.2V to (VUG - VPH ) > 1.2V -- 30 -- ns

Mi ni mum D uty C ycle -- 0 -- %

Maxi mum D uty C ycle 85 90 95 %

Soft Start

from C OMP/EN released to VOUT i n

Soft Start Ti me -- 2.5 -- ms

regulati on

Protection

Under Voltage Protecti on VFB_UVP Percentage of VREF -- 30 -- %

Over Voltage Protecti on VFB_OVP Percentage of VREF -- 125 -- %

Over Voltage Protecti on D elay -- 20 -- us

uP1542T -- -225 --

Over C urrent Threshold V PH uP1542Q -- -300 -- mV

uP1542V -- -375 --

OC P Programmable Range VOCP uP1542S/U -375 -- -100 mV

OC S Source C urrent for OC P

IOCS -- 20 -- uA

Setti ng

OC P D elay Ti me -- 3.33 -- us

D i sable Threshold VCOMP/EN 0.25 0.3 0.35 V

O

Over Temperature Protecti on -- 150 -- C

Note 1. Stresses listed as the above “ Absolute Maximum Ratings” may cause permanent damage to the device.

These are for stress ratings. Functional operation of the device at these or any other conditions beyond

those indicated in the operational sections of the specifications is not implied. Exposure to absolute

maximum rating conditions for extended periods may remain possibility to affect device reliability.

Note 2. Devices are ESD sensitive. Handling precaution recommended.

Note 3. θJA is measured in the natural convection at TA = 25°C on a low effective thermal conductivity test board of

JEDEC 51-3 thermal measurement standard.

Note 4. The device is not guaranteed to function outside its operating conditions.

8 uP1542-DS-F00A0, Apr. 2018

www.upi-semi.com

uP1542

Application Information

Component Selection Guidelines Both MOSFETs have I2R losses and the upper MOSFET

The selection of external component is primarily includes an additional term for switching losses, which

determined by the maximum load current and begins with are largest at high input voltages. The lower MOSFET

the selection of power MOSFET switches. The desired losses are greatest when the bottom duty cycle is near

amount of ripple current and operating frequency largely 100%, during a short-circuit or at high input voltage. These

determines the inductor value. Finally, CIN is selected for equations assume linear voltage current transitions and

its capability to handle the large RMS current into the do not adequately model power loss due the reverse-

converter and COUT is chosen with low enough ESR to recovery of the lower MOSFET’s body diode.

meet the output voltage ripple and transient specification. Ensure that both MOSFETs are within their maximum

Power MOSFET Selection junction temperature at high ambient temperature by

The uP1542 requires two external N-channel power calculating the temperature rise according to package

MOSFETs for upper (controlled) and lower (synchronous) thermal-resistance specifications. A separate heatsink may

switches. Important parameters for the power MOSFETs be necessary depending upon MOSFET power, package

are the breakdown voltage V(BR)DSS, on-resistance RDS(ON), type, ambient temperature and air flow.

reverse transfer capacitance CRSS, maximum current The gate-charge losses are mainly dissipated by the

I DS(MAX) , gate supply requirements, and thermal uP1542 and don’t heat the MOSFETs. However, large gate

management requirements. charge increases the switching interval, TSW that increases

The gate drive voltage is supplied by VCC pin that receives the MOSFET switching losses. The gate-charge losses

4.5V~13.2V supply voltage. When operating with a are calculated as:

PG _ C = VCC × (VCC × (C ISS _ UP + C ISS _ LO ) + VIN × C RSS _ UP )× f OSC

7~13.2V power supply for VCC, a wide variety of

NMOSFETs can be used. Logic-level threshold MOSFET

should be used if the input voltage is expected to drop where CISS_UP is the input capacitance of the upper MOSFET,

below 7V. Caution should be exercised with devices CISS_LOW is the input capacitance of the lower MOSFET, and

exhibiting very low VGS(ON) characteristics. The shoot- CRSS_UP is the reverse transfer capacitance of the upper

through protection present aboard the uP1542 may be MOSFET. Make sure that the gate-charge loss will not

circumvented by these MOSFETs if they have large cause over temperature at uP1542, especially with large

parasitic impedances and/or capacitances that would gate capacitance and high supply voltage.

inhibit the gate of the MOSFET from being discharged

Output Inductor Selection

below its threshold level before the complementary

MOSFET is turned on. Also avoid MOSFETs with Output inductor selection usually is based on the

excessive switching times; the circuitry is expecting considerations of inductance, rated current, size

transitions to occur in under 30ns or so. requirements and DC resistance (DCR).

In high-current applications, the MOSFET power Given the desired input and output voltages, the inductor

dissipation, package selection and heatsink are the value and operating frequency determine the ripple

dominant design factors. The power dissipation includes current:

two loss components: conduction loss and switching loss.

1 V

The conduction losses are the largest component of power ∆IL = VOUT (1 − OUT )

dissipation for both the upper and the lower MOSFETs. fOSC × L OUT VIN

These losses are distributed between the two MOSFETs Lower ripple current reduces core losses in the inductor,

according to duty cycle. Since the uP1542 is operating in ESR losses in the output capacitors and output voltage

continuous conduction mode, the duty cycles for the ripple. Highest efficiency operation is obtained at low

MOSFETs are: frequency with small ripple current. However, achieving

V OUT VIN − VOUT this requires a large inductor. There is a tradeoff between

D UP = ; DLOW = component size, efficiency and operating frequency. A

VIN VIN

reasonable starting point is to choose a ripple current that

The resulting power dissipation in the MOSFETs at

is about 20% of IOUT(MAX).

maximum output current are:

PUP = IOUT

2

× RDS( ON) × DUP + 0.5 × IOUT × VIN × TSW × fOSC There is another tradeoff between output ripple current/

voltage and response time to a transient load. Increasing

PLOW = IOUT

2

× RDS( ON) × DLOW the value of inductance reduces the output ripple current

and voltage. However, the large inductance values reduce

where TSW is the combined switch ON and OFF time.

uP1542-DS-F00A0, Apr. 2018 9

www.upi-semi.com

uP1542

Application Information

the converter’s response time to a load transient. capacitors can also be used, but caution must be exercised

Maximum current ratings of the inductor are generally with regard to the capacitor surge current rating. These

specified in two methods: permissible DC current and capacitors must be capable of handling the surge-current

saturation current. Permissible DC current is the allowable at power-up. Some capacitor series available from reputable

DC current that causes 40OC temperature raise. The manufacturers are surge current tested.

saturation current is the allowable current that causes 10% Output Capacitor Selection

inductance loss. Make sure that the inductor will not The selection of COUT is primarily determined by the ESR

saturate over the operation conditions including required to minimize voltage ripple and load step

temperature range, input voltage range, and maximum transients. The equivalent ripple current into the output

output current. capacitor is half of the inductor ripple current while the

The size requirements refer to the area and height equivalent frequency is double of phase operation

requirement for a particular design. For better efficiency, frequency due to two phase operation The output ripple

choose a low DC resistance inductor. DCR is usually ∆VOUT is approximately bounded by:

inversely proportional to size.

∆IL 1

Input Capacitor Selection ∆VOUT = (ESR + )

2 16 × fOSC × COUT

The synchronous-rectified Buck converter draws pulsed

Since ∆IL increases with input voltage, the output ripple is

current with sharp edges from the input capacitor, resulting

highest at maximum input voltage. Typically, once the ESR

in ripples and spikes at the input supply voltage. Use a

requirement is satisfied, the capacitance is adequate for

mix of input bypass capacitors to control the voltage

filtering and has the necessary RMS current rating. Multiple

overshoot across the MOSFETs. Use small ceramic

capacitors placed in parallel may be needed to meet the

capacitors for high frequency decoupling and bulk

ESR and RMS current handling requirements.

capacitors to supply the current needed each time upper

MOSFET turns on. Place the small ceramic capacitors The load transient requirements are a function of the slew

physically close to the MOSFETs to avoid the stray rate (di/dt) and the magnitude of the transient load current.

inductance along the connection trace. These requirements are generally met with a mix of

The important parameters for the bulk input capacitor are capacitors and careful layout. Modern components and

the voltage rating and the RMS current rating. For reliable loads are capable of producing transient load rates above

operation, select the bulk capacitor with voltage and current 1A/ns. High frequency capacitors initially supply the

ratings above the maximum input voltage and largest RMS transient and slow the current load rate seen by the bulk

current required by the circuit. The capacitor voltage rating capacitors. The bulk filter capacitor values are generally

should be at least 1.25 times greater than the maximum determined by the ESR (Effective Series Resistance) and

input voltage and a voltage rating of 1.5 times is a voltage rating requirements rather than actual capacitance

conservative guideline. The RMS current rating requirements.

requirement for the input capacitor of a buck converter is High frequency decoupling capacitors should be placed

calculated as: as close to the power pins of the load as physically

possible. Be careful not to add inductance in the circuit

VOUT ( VIN − VOUT ) board wiring that could cancel the usefulness of these

IIN(RMS ) = IOUT(MAX )

VIN low inductance components. Consult with the

This formula has a maximum at VIN = 2VOUT, where IIN(REMS) manufacturer of the load on specific decoupling

= IOUT(RMS)/2. This simple worst-case condition is commonly requirements.

used for design because even significant deviations do Use only specialized low-ESR capacitors intended for

not offer much relief. Note that the capacitor switching-regulator applications for the bulk capacitors.

manufacturer’s ripple current ratings are often based on The bulk capacitor’s ESR will determine the output ripple

2000 hours of life. This makes it advisable to further derate voltage and the initial voltage drop after a high slew-rate

the capacitor, or choose a capacitor rated at a higher transient. An aluminum electrolytic capacitor’s ESR value

temperature than required. Always consult the is related to the case size with lower ESR available in

manufacturer if there is any question. larger case sizes.

For a through-hole design, several electrolytic capacitors Bootstrap Capacitor Selection

may be needed. For surface mount designs, solid tantalum An external bootstrap capacitor CBOOT connected to the

10 uP1542-DS-F00A0, Apr. 2018

www.upi-semi.com

uP1542

Application Information

BOOT pin supplies the gate drive voltage for the upper filter (LOUT and COUT), with a double pole break frequency at

MOSFET. This capacitor is charged through the internal FLC and a zero at FESR. The DC Gain of the modulator is

diode when the PH node is low. When the upper MOSFET simply the input voltage (VIN) divided by the peak-to-peak

turns on, the PH node rises to VIN and the BOOT pin rises oscillator voltage £GVOSC.

to approximately VIN + VCC. The boot capacitor needs to The output LC filter introduces a double pole, 40dB/decade

store about 100 times the gate charge required by the gain slope above its corner resonant frequency, and a total

upper MOSFET. In most applications 0.47µF to 1µF, X5R phase lag of 180 degrees. The resonant frequency of the

or X7R dielectric capacitor is adequate. LC filter expressed as:

Feedback Loop Compensation

1

Figure 5 highlights the voltage-mode control loop for a FLC =

synchronous-rectified buck converter consisting of 2π L OUT × COUT

uP1542. The control loop includes a compensator and a The ESR zero is contributed by the ESR associated with

modulator, where the modulator consists of the PWM the output capacitor. Note that this requires that the output

comparator, the power stage amplifier and the output filter; capacitor should have enough ESR to satisfy stability

the compensator consists of the error amplifier and requirements as described in the later sections. The ESR

compensating network. A well-designed feedback loop zero of the output capacitor expressed as:

tightly regulates the output voltage (VOUT) to the reference

voltage VREF with fast response to load/line transient and 1

FESR =

good stability. The goal of the compensation network is to 2π × ESR× COUT

provide and the highest 0dB crossing frequency and

Figure 6 illustrates frequency response of a typical

adequate phase margin (greater than 45 degrees). It is

modulator using uP1542.

also recommended to manipulate loop frequency

response that its gain crosses over 0dB at a slope of - 80

20dB/dec. 60

VIN 40 LC

Double

Pole

Gain (dB)

20

Driver Modulator

∠VOSC LOUT 0

ESR

PH Zero

VOUT -20

PWM COUT

Comp.

-40

ESR

-60

1.E+02 1.E+03 1.E+04 1.E+05 1.E+06

VREF

VCOMP Compensator Frequency (Hz)

C1 Error

Amp. R3 Figure 6. Frequency Response of Modulator.

R2 C3

R1

C2 2) Compensator Frequency Equations

ZCOMP ZFB

The uP1542 adopts an operational transconductance

amplifier (OTA) as the error amplifier as shown in Figure

Figure 5. Voltage Control Loop Using uP1542. 7.

Modulator Break Frequency Equations EA+ ∆IOUT= GM x ∆VM

The error amplifier output (VCOMP) is compared with the VOUT

oscillator (OSC) sawtooth waveform to provide a pulse- ∆VM GM

ROUT

width modulated (PWM) waveform with an amplitude of

EA-

VIN at the PH node. The PWM waveform is smoothed by

the output filter (LOUT and COUT). The modulator transfer

function is the small-signal transfer function of VOUT/VCOMP. Figure 7. Operational Transconductance Amplifier.

This function is dominated by a DC Gain and the output

uP1542-DS-F00A0, Apr. 2018 11

www.upi-semi.com

uP1542

Application Information

The transconductance is defined as: regulation and fast response to load/line transient with good

stability. Follow the guidelines for locating the poles and

∆ IOUT

GM = zeros of the compensation network.

∆VM

1. Pick Mid-Band Gain (R1) for desired converter band-

where ∆VM = (EA+) - (EA-); ∆IOUT = E/A output current. width.

Figure 8 illustrates a type II compensation network using 2. Place Zero (C1) below LC double pole (~25% FLC).

OTA. The compensation network consists of the error 3. Place Pole (C2) at half the switching frequency.

amplifier and the impedance networks ZFB and ZCOMP. 4. Check gain against error amplifier open loop gain.

5. Estimate phase margin - repeat if necessary.

VOUT 60

VCOMP

R3 GM

Error 40 Loop Gain

Amplifier

C2 R1 Compensator

20 Gain

ZFB R2

Gain (dB)

VREF Modulator

ZCOMP C1 Gain

0

Figure 8. Type II Compensation Network Using OTA. -20

The compensator transfer function is the small-signal -40

transfer function of VCOMP/VOUT. This function is dominated

by a Mid-Band Gain and compensation network ZCOMP, with -60

a pole at FP1 and a zero at FZ1. The Mid-Band Gain of the 1.E+02 1.E+03 1.E+04 1.E+05 1.E+06

compensation is expressed as: Frequency (Hz)

R2 Figure 10. Frequency Response of Type II Compensation.

Mid _ Band _ Gain = × R1× GM

R 2 × R3 Design Example

The equations below relate the compensation network’s As a design example, take a power supply with the

pole and zero to the components (R1, C1, and C2) in following specifications:

Figure 9. VIN = 10.8V to 13.2V (12V nominal), VOUT = 1.2V Ó

¡5%,

IOUT(MAX) = 20A, fOSC = 300kHz/200kHz, ∆VOUT = 20mV,

1

FP1 = 1 bandwidth = 50kHz.

C1× C2 ; FZ1 =

2π × R1× ( ) 2π × R1× C1 1.) Power Component Selection

C1 + C2

First, choose the inductor for about 20% ripple current at

60

the maximum VIN:

40 1 V

Loop Gain ∆IL = × VOUT × (1 − OUT )

Compensator

fOSC × L OUT VIN

20 Gain

Gain (dB)

Modulator 1 1 .2 V

Gain FZ1 FP1 ∆IL = 20 A × 20% = × 1.2V × (1 − )

R1 0 300kHz × L OUT 13.2V

C1

-20 L OUT = 0 .9 uH

Selecting a standard value of 1.0uH results in a maximum

-40 ripple current of 3.6A.

-60

Choose two 1000uF capacitors with 10mΩ ESR in parallel

to yield equivalent ESR = 5mΩ. The output ripple voltage

1.E+02 1.E+03 1.E+04 1.E+05 1.E+06

is about 18mV accordingly. An optional 22uF ceramic

Frequency (Hz)

output capacitor is recommended to minimize the effect

Figure 9. Frequency Response of Type II Compensation. of ESL in the output ripple.

Figure 10 shows the DC-DC converter’s gain vs. The modulator DC gain and break frequencies are

frequency. Careful design of ZCOMP and ZFB provides tight calculated as:

12 uP1542-DS-F00A0, Apr. 2018

www.upi-semi.com

uP1542

Application Information

V 12

DC Gain = 20 × log( IN ) = 20 × log( ) = 16.5dB double pole. Adding a feedforward capacitor C3 on original

∆VOSC 1. 8 type II compensation network introduces an additional

1 pole-zero pair ( Z2 and P2) as illustrated in Figure 13. The

FLC = = 3 .56kHz new pole-zero pair are expressed as:

2 π 1× 10 − 6 × 2000 × 10 − 6

1 1

1 Z2 = ; P2 =

FESR = = 16kHz 2π × R3 × C3 2π × C3 × (R2 × R3) /(R2 + R3)

2π × 5 × 10 −3 × 2000 × 10 −6

2.) Compensation VOUT

VCOMP

Select R2 = 10kΩ and R3 = 5kΩ to set output voltage as R3 GM

1.2V. R2 and R3 do not affect the compensation, 1kΩ ~ Error

C3 Amplifier

10kΩ is adequate for the application. R1

C2

The modulator gain at zero-crossing frequency (50kHz) ZFB R2 VREF ZCOMP C1

is calculated as -19.5dB. This demands a compensator

with mid-band gain as 19.5dB. Select R1 as:

10(19.5 / 20) × VOUT Figure 12. Type III Compensation Network.

R1 = = 17.7kΩ

GM× VREF While the Mid-Band Gain remains unchanged, the

additional pole-zero pair causes a gain boost at the flat

Select C1 = 10nF to place FZ1 = 0.9kHz, about one forth of

gain region. The gain-boost is limited by the ratio (R1 +R2)/

the LC double pole.

R2. Figures 14 shows the DC-DC converter’s gain vs.

Select C2 = 68pF to place FP1 = 133kHz, about half of the frequency.

switching frequency.

Figure 11 shows the result loop gain vs. frequency relation. 80

60 60 Loop Gain

Loop

Gain Compensator

40

40 Gain

Compensator

Gain (dB)

Gain 20 P2 P1

20 Z1 Z2

Modulator

0

Gain (dB)

Modulator Gain

0 Gain

-20

-20

-40

-40 -60

1.E+01 1.E+02 1.E+03 1.E+04 1.E+05 1.E+06

-60 Frequency (Hz)

1.E+02 1.E+03 1.E+04 1.E+05 1.E+06

Frequency (Hz) Figure 13. Loop Gain of Type III Compensation Network.

Figure 11. Gain vs. Frequency for the Design Example.

Type III Compensation

The ESR zero plays an important role in type II

compensation. Output capacitors with low ESR and small

capacitance push the ESR zero to high frequency band. If

the ESR zero is ten times higher than the LC double pole,

the double pole may cause the loop phase close to 180O

and make the control loop unstable. A type II compensation

cannot stabilize the loop since it has only one zero.

A type III compensation network as shown in Figure 12

that features 2 poles and 2 zeros is necessary for such

applications where ESR zero is far away from the LC

uP1542-DS-F00A0, Apr. 2018 13

www.upi-semi.com

uP1542

Application Information

connection the top layer with wide, copper filled areas.

80

2 Place the power components as physically close as

60 Loop Gain possible.

40 Compensator 2.1 Place the input capacitors, especially the high

Gain

frequency ceramic decoupling capacitors, directly

Gain (dB)

20

to the drain of upper MOSFET ad the source of

Modulator

0 Gain the lower MOSFET. To reduce the ESR replace

the single input capacitor with two parallel units

-20

2.2 Place the output capacitor between the converter

-40 and load.

-60 3 Place the uP1542 near the upper and lower MOSFETs

1.E+01 1.E+02 1.E+03 1.E+04 1.E+05 1.E+06 with UG and LG facing the power components. Keep

Frequency (Hz) the components connected to noise sensitive pins near

the uP1542 and away from the inductor and other noise

Figure 14. Frequency Response of Type III Compensa-

sources.

tion.

4 Use a dedicated grounding plane and use vias to ground

Checking Transient Response

all critical components to this layer. The ground plane

The regulator loop response can be checked by looking layer should not have any traces and should be as close

at the load transient response. Switching regulators take as possible to the layer with power MOSFETs. Use an

several cycles to respond to a step in load current. When immediate via to connect the components to ground

a load step occurs, VOUT immediately shifts by an amount plane including GND of uP1542. Use several bigger

equal to ∆ILOADx(ESR), where ESR is the effective series vias for power components.

resistance of C OUT. ∆I LOAD also begins to charge or

discharge COUT generating a feedback error signal used 5 Apply another solid layer as a power plane and cut this

by the regulator to return VOUT to its steady-state value. plane into smaller islands of common voltage levels.

The power plane should support the input power and

During this recovery time, VOUT can be monitored for

output power nodes to maintain good voltage filtering

overshoot or ringing that would indicate a stability problem.

and to keep power losses low. Also, for higher currents,

PCB Layout Considerations it is recommended to use a multilayer board to help

High speed switching and relatively large peak currents with heat sinking power components.

in a synchronous-rectified buck converter make the PCB 6 The PH node is subject to very high dV/dt voltages.

layout a very important part of design. Fast current Stray capacitance between this island and the

switching from one device to another in a synchronous- surrounding circuitry tend to induce current spike and

rectified buck converter causes voltage spikes across the capacitive noise coupling. Keep the sensitive circuit

interconnecting impedances and parasitic circuit elements. away from the PH node and keep the PCB area small

The voltage spikes can degrade efficiency and radiate to limit the capacitive coupling. However, the PCB area

noise that result in overvoltage stress on devices. Careful should be kept moderate since it also acts as main

component placement layout and printed circuit board heat convection path of the lower MOSFET.

design minimizes the voltage spikes induced in the

7 The uP1542 sources/sinks impulse current with 2A peak

converter.

to turn on/off the upper and lower MOSFETs. The

Follow the layout guidelines for optimal performance of connecting trance between the controller and gate/

uP1542. source of the MOSFET should be wide and short to

1 The upper and lower MOSFETs turn on/off and conduct minimize the parasitic inductance along the traces.

pulsed current alternatively with high slew rate 8 Flood all unused areas on all layers with copper.

transition. Any inductance in the switched current path Flooding with copper will reduce the temperature rise

generates a large voltage spike during the switching. of power component.

The interconnecting wires indicated by red heavy lines

9 Provide local VCC decoupling between VCC and GND

conduct pulsed current with sharp transient and should

pins. Locate the capacitor, CBOOT as close as possible

be part of a ground or power plane in a printed circuit

to the BOOT and PH pins.

board to minimize the voltage spike. Make all the

14 uP1542-DS-F00A0, Apr. 2018

www.upi-semi.com

uP1542

Package Information

PSOP - 8L

0.10 - 0.25

4.80 - 5.00

1.80 - 2.40

5.79 - 6.20

3.80 - 4.00

1.80 - 2.40

0.40 - 1.27

1

1.27 BSC 0.31 - 0.51

1.7 MAX

0.00 - 0.15

Note

1.Package Outline Unit Description:

BSC: Basic. Represents theoretical exact dimension or dimension target

MIN: Minimum dimension specified.

MAX: Maximum dimension specified.

REF: Reference. Represents dimension for reference use only. This value is not a device specification.

TYP. Typical. Provided as a general value. This value is not a device specification.

2.Dimensions in Millimeters.

3.Drawing not to scale.

4.These dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm.

uP1542-DS-F00A0, Apr. 2018 15

www.upi-semi.com

uP1542

Package Information

WDFN2x2 - 8L

1.90 - 2.10 0.20 - 0.50 1.10 - 1.40

5 8

1.90 - 2.10

0.50 - 0.80

4 1

0.50 BSC 0.18 - 0.30

0.70 - 0.80

0.20 REF 0.00 - 0.05

Note

1.Package Outline Unit Description:

BSC: Basic. Represents theoretical exact dimension or dimension target

MIN: Minimum dimension specified.

MAX: Maximum dimension specified.

REF: Reference. Represents dimension for reference use only. This value is not a device specification.

TYP. Typical. Provided as a general value. This value is not a device specification.

2.Dimensions in Millimeters.

3.Drawing not to scale.

4.These dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm.

16 uP1542-DS-F00A0, Apr. 2018

www.upi-semi.com

uP1542

Important Notice

uPI and its subsidiaries reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products

and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information

before placing orders and should verify that such information is current and complete.

uPI products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment. However, no responsibility is

assumed by uPI or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

No license is granted by implication or otherwise under any patent or patent rights of uPI or its subsidiaries.

COPYRIGHT (C) 2011, UPI SEMICONDUCTOR CORP.

uPI Semiconductor Corp. uPI Semiconductor Corp.

Headquarter Sales Branch Office

9F.,No.5, Taiyuan 1st St. Zhubei City, 12F-5, No. 408, Ruiguang Rd. Neihu District,

Hsinchu Taiwan, R.O.C. Taipei Taiwan, R.O.C.

TEL : 886.3.560.1666 FAX : 886.3.560.1888 TEL : 886.2.8751.2062 FAX : 886.2.8751.5064

uP1542-DS-F00A0, Apr. 2018 17

www.upi-semi.com

You might also like

- Ultrasonic Arrays For Non-Destructive Evaluation - A ReviewDocument17 pagesUltrasonic Arrays For Non-Destructive Evaluation - A ReviewThatazita MenezesNo ratings yet

- Mini-Wheel Encoder: Standard InclusionsDocument2 pagesMini-Wheel Encoder: Standard InclusionsGhaithNo ratings yet

- Informe UtDocument37 pagesInforme UtWisthon GrimanNo ratings yet

- United States Marine Corps Mozambique DrillDocument7 pagesUnited States Marine Corps Mozambique DrillJo Hannah Delcano TadlasNo ratings yet

- Handbook 1 A29Document31 pagesHandbook 1 A29srgokuNo ratings yet

- To FDDocument4 pagesTo FDDong Hyun KangNo ratings yet

- ToFD Nuclear Power PlantDocument8 pagesToFD Nuclear Power PlantbacabacabacaNo ratings yet

- Acs 03 UsfdDocument7 pagesAcs 03 UsfdPRAVIN DASSNo ratings yet

- NDT - Magnetic ParticleDocument73 pagesNDT - Magnetic ParticleUmaibalanNo ratings yet

- Manual Olympus Epoch XTDocument240 pagesManual Olympus Epoch XTcpoliNo ratings yet

- ISO-TC135-SC7-WG9 N0024 Review of ISO TR 25107 ISO TR 2510Document253 pagesISO-TC135-SC7-WG9 N0024 Review of ISO TR 25107 ISO TR 2510jbrizuelasanchez4706No ratings yet

- Lecture 7 Intergranular CorrosionDocument18 pagesLecture 7 Intergranular Corrosionprakush01975225403No ratings yet

- PT 2Document91 pagesPT 2safeer ahmadNo ratings yet

- PW3Document49 pagesPW3Mujaffar ShaikhNo ratings yet

- Seb1 57466Document2 pagesSeb1 57466aliextomaNo ratings yet

- TOFD Dead Zone CalculatorDocument3 pagesTOFD Dead Zone CalculatorAromal SNo ratings yet

- Measurement of Prep Ene Trant EtchDocument6 pagesMeasurement of Prep Ene Trant EtchPDDELUCANo ratings yet

- X - Ray Fluorescence Presentation - Alamin - FinalDocument35 pagesX - Ray Fluorescence Presentation - Alamin - FinalAlamin Saj EngineeringNo ratings yet

- Selenium 75Document0 pagesSelenium 75vrapciudorianNo ratings yet

- RT TechniqueDocument3 pagesRT TechniquesubhashpkdNo ratings yet

- Study of The Factors Affecting The Sensitivity of Liquid PenetrantDocument59 pagesStudy of The Factors Affecting The Sensitivity of Liquid PenetrantfallalovaldesNo ratings yet

- Inspection of Austenitic Welds END UTDocument12 pagesInspection of Austenitic Welds END UTalberto QUINTANILLANo ratings yet

- By: Jabran Younas: A New BeginningDocument58 pagesBy: Jabran Younas: A New BeginningM Jafar SidiqNo ratings yet

- Eddy Current Testing Exam Questions Assignment2Document1 pageEddy Current Testing Exam Questions Assignment2Narotam Kumar GupteshwarNo ratings yet

- General Principles of Radiography BSEN 444 PDFDocument17 pagesGeneral Principles of Radiography BSEN 444 PDFThe Normal HeartNo ratings yet

- Cswip - Section 05-Non-Destructive Testing PDFDocument11 pagesCswip - Section 05-Non-Destructive Testing PDFNsidibe Michael EtimNo ratings yet

- An Automated Radiographic NDT System For Weld Inspection - Part I - Weld Extraction PDFDocument6 pagesAn Automated Radiographic NDT System For Weld Inspection - Part I - Weld Extraction PDFaliNo ratings yet

- Metalscan Inspection Services Presents: Nondestructive EvaluationDocument15 pagesMetalscan Inspection Services Presents: Nondestructive Evaluationnaganathan100% (2)

- Brief On RFET Based Systems & ServicesDocument3 pagesBrief On RFET Based Systems & ServicesKollabo SysNo ratings yet

- UT Outline Training LV IIIDocument4 pagesUT Outline Training LV IIITrung Tinh HoNo ratings yet

- Multifilm Techinique PDFDocument7 pagesMultifilm Techinique PDFamitNo ratings yet

- Radiography Testing GuideDocument7 pagesRadiography Testing GuideAmirul Asyraf100% (1)

- ISO 9916 1991 Aluminium and Magnesium Alloy Castings - Liquid Penetrant TestingDocument9 pagesISO 9916 1991 Aluminium and Magnesium Alloy Castings - Liquid Penetrant TestingJOSUE RIOSNo ratings yet

- TOFD by TempleDocument444 pagesTOFD by TempleAlejandro Mejia RodriguezNo ratings yet

- FCPG-00000-CPP143-00-QA-6050-00011-002 - RT ProcedureDocument19 pagesFCPG-00000-CPP143-00-QA-6050-00011-002 - RT Procedurem.rasheed400010No ratings yet

- NDE Associates, Inc. - Ultrasonic Testing - Phased ArrayDocument2 pagesNDE Associates, Inc. - Ultrasonic Testing - Phased Arrayaldeanucu3203No ratings yet

- Chapter-4 Mechanical Testing 08-06-2014Document21 pagesChapter-4 Mechanical Testing 08-06-2014safeer ahmadNo ratings yet

- ASNTDocument5 pagesASNTshifaNo ratings yet

- Chapter-2 Fracture Mechanics and NDTDocument13 pagesChapter-2 Fracture Mechanics and NDTsafeer ahmadNo ratings yet

- 6082 T6 Aluminum Plate SuppliersDocument9 pages6082 T6 Aluminum Plate Supplierssanghvi overseas incNo ratings yet

- Aut & RTDocument12 pagesAut & RTgorkembaytenNo ratings yet

- Cordon Off - 4 (00000003)Document1 pageCordon Off - 4 (00000003)Anonymous PlyxbQ3tNo ratings yet

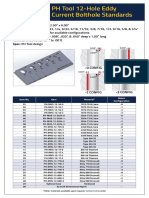

- 12-Hole Standards InteractiveDocument1 page12-Hole Standards InteractivevikramNo ratings yet

- Testing Session TOFD EECI - EurosonicDocument47 pagesTesting Session TOFD EECI - EurosonicRupam BaruahNo ratings yet

- Focal SpotDocument1 pageFocal SpotHappy2021No ratings yet

- Procedure Qualification Requirements For Flaw SizingDocument2 pagesProcedure Qualification Requirements For Flaw SizingAngelTinocoNo ratings yet

- Ut TwiDocument266 pagesUt TwiADAMJSRAONo ratings yet

- Inspeccion VisualDocument31 pagesInspeccion VisualOsvaldo Loyde AlvaradoNo ratings yet

- E243-97 EC Copper TubesDocument6 pagesE243-97 EC Copper TubesveluNo ratings yet

- DR2 L07Document20 pagesDR2 L07JOMAGUESNo ratings yet

- UT Sec.1 Ultrasonic TestingDocument23 pagesUT Sec.1 Ultrasonic TestingSaut Maruli Tua SamosirNo ratings yet

- Fall Protection Writing Better Reports Inspecting Skewed T-JointsDocument36 pagesFall Protection Writing Better Reports Inspecting Skewed T-JointswiNo ratings yet

- 4#600 Body RSSDocument1 page4#600 Body RSSRavi patelNo ratings yet

- Doosan NDE CastingDocument20 pagesDoosan NDE CastingvsnaiduqcNo ratings yet

- Chapter 4bDocument33 pagesChapter 4bAhmed shabanNo ratings yet

- Multiscan Ms5800: User'S ManualDocument160 pagesMultiscan Ms5800: User'S ManualSoorajNo ratings yet

- Up 11541Document14 pagesUp 11541techgamebr85No ratings yet

- 5V/12V Synchronous-Rectified Buck Controller With Reference InputDocument19 pages5V/12V Synchronous-Rectified Buck Controller With Reference InputIgor LabutinNo ratings yet

- Ford S-Max - Customer Ordering Guide and Price List: Effective From 1st April 2019Document16 pagesFord S-Max - Customer Ordering Guide and Price List: Effective From 1st April 2019JumNo ratings yet

- Behringer B300 User GuideDocument13 pagesBehringer B300 User GuideeugeniuNo ratings yet

- The Verb Be Evaluation Affirmative FormDocument2 pagesThe Verb Be Evaluation Affirmative FormMaribel Botero BoteroNo ratings yet

- Japanese Phonetics BibliographyDocument10 pagesJapanese Phonetics BibliographyTANG TSZ HANG鄧旨行No ratings yet

- Bsi en 50600-2-2 (2014) - 318Document9 pagesBsi en 50600-2-2 (2014) - 318saryus20120% (1)

- Preparing For Examinations1Document1 pagePreparing For Examinations1Karan PatilNo ratings yet

- Anurag Gautam: Mobile:+91-9536511773 Email IdDocument3 pagesAnurag Gautam: Mobile:+91-9536511773 Email IdAnurag GautamNo ratings yet

- DLL Sample Mapeh 2Document20 pagesDLL Sample Mapeh 2rey peraltaNo ratings yet

- Materials Controller Job SpecDocument4 pagesMaterials Controller Job SpecHasan AskariNo ratings yet

- Class 10 Case StudyDocument3 pagesClass 10 Case StudyAlka MehraNo ratings yet

- Southeast Asia Before Colonization 1Document4 pagesSoutheast Asia Before Colonization 1Angela GlitterNo ratings yet

- Hesychasm (I) PDFDocument4 pagesHesychasm (I) PDFAWNo ratings yet

- Brahmasphutasiddhanta Brahmagupta Parts 1-4 by Sudhakara-Dvivedin With Sanskrit Commentary 1902 India Compiled by Jonathan Crabtree 2014-AustraliaDocument236 pagesBrahmasphutasiddhanta Brahmagupta Parts 1-4 by Sudhakara-Dvivedin With Sanskrit Commentary 1902 India Compiled by Jonathan Crabtree 2014-AustraliaSuresh KumarNo ratings yet

- Nigeria-Cameroon Over Bakassi-PeninsulaDocument86 pagesNigeria-Cameroon Over Bakassi-PeninsulaOladipo EmmanuelNo ratings yet

- Capstone Update 1Document4 pagesCapstone Update 1api-690035259No ratings yet

- Roadmap To Trading Success, Essential Tips and Techniques For New TradersDocument26 pagesRoadmap To Trading Success, Essential Tips and Techniques For New TradersShehroz HabibNo ratings yet

- Derfull 2Document2 pagesDerfull 2api-253024734No ratings yet

- Math - Study Guide For 1st Endterm Test Checked (Key)Document8 pagesMath - Study Guide For 1st Endterm Test Checked (Key)kienkienNo ratings yet

- FAA 2014 0626 0004 - Attachment - 1Document12 pagesFAA 2014 0626 0004 - Attachment - 1imahjoobiNo ratings yet

- Solution Manual For Essentials of Accounting For Governmental and Not-for-Profit Organizations, 14th Edition, Paul CopleyDocument36 pagesSolution Manual For Essentials of Accounting For Governmental and Not-for-Profit Organizations, 14th Edition, Paul Copleylantautonomyurbeiu100% (24)

- Rashtriya Arogya Nidhi (RAN) and Health Minister's Discretionary Grants (HMDG) PDFDocument48 pagesRashtriya Arogya Nidhi (RAN) and Health Minister's Discretionary Grants (HMDG) PDFChilagani SampathNo ratings yet

- Spur GearDocument3 pagesSpur Gearigualdi53No ratings yet

- Understanding Fashion Consumers' Attitude and Behavioral Intention Toward Sustainable Fashion Products: Focus On Sustainable Knowledge Sources and Knowledge TypesDocument18 pagesUnderstanding Fashion Consumers' Attitude and Behavioral Intention Toward Sustainable Fashion Products: Focus On Sustainable Knowledge Sources and Knowledge TypesBharani Sai PrasanaNo ratings yet

- 300 - Prachet PrakashDocument3 pages300 - Prachet PrakashSAURABH RANGARINo ratings yet

- Cogent Customer User GuideDocument33 pagesCogent Customer User GuideSpamNo ratings yet

- Andy Stanley Leadership Podcast March 2021 Application GuideDocument1 pageAndy Stanley Leadership Podcast March 2021 Application GuidePorras AugustoNo ratings yet

- Horizon Architecture NoindexDocument47 pagesHorizon Architecture NoindexktgeorgeNo ratings yet

- Basf Masterroc Aga 155 TdsDocument2 pagesBasf Masterroc Aga 155 TdsPablo Quinteros PizarroNo ratings yet

- Astm C108 PDFDocument2 pagesAstm C108 PDFAbu WildanNo ratings yet