ASIP Architecture Implementation of Channel Equalization Algorithms For MIMO Systems in WCDMA Downlink

ASIP Architecture Implementation of Channel Equalization Algorithms For MIMO Systems in WCDMA Downlink

Uploaded by

Munish JassiOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ASIP Architecture Implementation of Channel Equalization Algorithms For MIMO Systems in WCDMA Downlink

ASIP Architecture Implementation of Channel Equalization Algorithms For MIMO Systems in WCDMA Downlink

Uploaded by

Munish JassiCopyright:

Available Formats

ASIP Architecture Implementation of Channel

Equalization Algorithms for MIMO Systems in

WCDMA Downlink

Predrag Radosavljevic, Joseph R. Cavallaro, and Alexandre de Baynast

Department of Electrical and Computer Engineering

Rice University, MS-366 - 6100 Main Street

Houston, Texas 77005

Email: {rpredrag, cavallar, debaynas}@rice.edu

Abstract— This paper presents a customized and flexible hard- While computationally efficient and low power solution, ASIC

ware implementation of linear iterative channel equalization processors are not flexible enough to support the necessary

algorithms for WCDMA downlink transmission in 3G wireless variations of implemented wireless applications. On the other

system with multiple transmit and receive antennas (MIMO

system). Optimized (in terms of area and execution time) and hand, DSP processors, although fully programmable, cannot

power efficient Application Specific Instruction set Processors achieve high performance with low power dissipation in highly

(ASIPs) based on Transport Triggered Architecture (TTA) are parallel 3G applications. The drawback of DSP architecture

designed that can operate efficiently in slow and fast fading high solutions is limited level of instruction and data parallelism

scattering environments. The instruction set of TTA processors is that is necessary for future 3G/4G wireless applications. These

extended with several user-defined operations specific for channel

equalization algorithms that dramatically optimize the architec- are the reasons for the recent interest in new reconfigurable

ture solution for the physical layer of the mobile handset. The architectures with some level of programmability [3] and, at

final results of presented design-space exploration method are the same time, possibility for customization that is targeted

the ASIP processors with low cost/performance ratio. Automatic to a class of wireless applications with high levels of data

software-hardware co-design flow for conversion of C application and instruction parallelism. These architectures are called

code into gate-level hardware design of ASIP architectures is

also described. Implemented ASIP solutions achieve real time Application Specific Instruction set Processors (ASIPs) and

requirements for 3GPP wireless standard (1xEV-DV standard, in can replace multiple chip designs implemented as an ASIC

particular) with reasonable clock speed and power dissipation. architecture [4].

In this work we propose the implementation of iterative

I. I NTRODUCTION chip level channel equalization algorithms on ASIP proces-

Efficiency and flexibility are crucial features of processors sors based on Transport Triggered Architecture (TTA) [5] in

in the next generation of wireless cellular systems. Processors WCDMA MIMO downlink transmission. Channel equaliza-

need to be efficient in order to achieve real-time require- tion restores the orthogonality of the spreading waveforms

ments with low power consumption for computationally very destroyed by channel multipaths and suppresses strong Multi-

demanding algorithms in new emerging wireless standards ple Access Interference (MAI) and Inter-Symbol Interference

(3GPP, 4G, 802.11x, DVB-S2, DAB, just to name a few). (ISI). We show that the application specific processor design

Flexibility, on the other hand, allows design modifications in based on TTA is programmable and configurable enough to

order to respond to: different channel environments, changes handle different variations of channel equalization. The de-

of user requirements depending of the quality of service signed ASIP architecture operates efficiently in a broad range

(QoS), different workloads, different kinds of data, etc. Often, of channel environments defined by 3GPP standard (from two-

efficiency and flexibility goals are conflicting. paths Pedestrian A to five-paths Vehicular A channels, speed

In this work we propose both flexible and application of mobile subscriber varies from 3km/h to 120 km/h) [1].

specific (customized) hardware solutions for implementation In order to achieve real-time requirements in high data rate

of channel equalization algorithms at the physical layer of the downlink applications, parallel architectures are developed for

3G mobile handset. Processors for mobile handsets in cellular low power dissipation with the clock frequency limited to

systems that support the 3GPP standard ([1] and [2]) require approximately 150 MHz.

at the same time both high speed and low power dissipation. This paper is organized as follows. The principles of channel

In addition, computationally very demanding algorithms are equalization at the receiver side as well as the equalization-

needed to remove high levels of multiuser interference es- specific operations are introduced in section II. Customized

pecially in the presence of multiple antennas on the base- ASIP architectures for channel equalization algorithm in

station and mobile handset (MIMO wireless system). Tradi- MIMO downlink are proposed in section III. Simulation esti-

tional architecture solutions are ASIC and DSP processors. mates (clock speed, power dissipation, and area) obtained with

0-7803-8521-7/04/$20.00 (C) 2004 IEEE

the TTA software tools are presented in section IV. Detailed provided by implementation of user-defined function units

description of exploration for optimal ASIP architectures can customized for a given application. TTA is programmed by

be found in section V. The automatic software-hardware directly specifying data transports which then trigger the oper-

design flow and gate-level synthesis are presented in section ations as the side effect (implicit data control). The advantages

VI. The conclusions are stated in section VII. of the TTA processors are, also, short cycle time, and fast

and application specific processor design. The MOVE software

II. E QUALIZATION A LGORITHM toolset [10] enables an exhaustive design-space exploration.

Powerful low complexity chip-level channel equalization

based on iterative Conjugate Gradient (CG) algorithm [6] B. Our ASIP Architecture Solution

for inversion of covariance matrix and computation of filter We propose a 32-bit wide ASIP architecture (buses and ports

coefficients in various scattering environments (slow and fast of FUs are 32 bits wide) with 16-bit fixed-point arithmetic

fading channels) has been proposed in [7] and [8]. The main [9] for real-time equalization that is suitable to operate in

feature of CG equalization is fast convergence speed to the low/high scattering and slow/fast fading environments. Real-

LMMSE solution (direct inversion of covariance matrix). To time requirements are related to the 3GPP chip rate of 1.2288

be robust to the channel variations several adaptations of basic Mcps [1] that provides available time of approximately 810

CG equalization have been applied [9] while keeping the same ns for processing one data sample.

architecture. In this work, channel equalization and adaptive

variations for fast fading environments are all mapped to the

same optimized and flexible ASIP architecture. data_out data_in

Equalization algorithm is composed of two main steps: i) RAM

Channel estimation/covariance matrix computation/filter up-

date part mainly consists of sign-test operations followed by LSU LSU ALU ALU ALU CXMUL

complex addition/subtraction operations, as well as complex

RFs

multiplications and real multiplication with shifting capabil-

ity. ii) Filtering+despreading/descrambling (user detection) is 8x4 int

a uniform algorithm that consists mainly of complex multipli- regs

cations and accumulations. Indeed, the equalization algorithm 1x1 bool

consists of some non-standard operations therefore several reg

specific user-defined operations can be designed for efficient

ASIP implementation. The block diagram of channel equalizer ALU ALU SALU SALU SALU MUL

in MIMO downlink based on iterative CG algorithm is shown

in Figure 1. Fig. 2. Optimized architecture: co-processor for CG filter update

Pilot Data The design of ASIP equalizer architecture is optimized by

implementing several Special Functional Units (SFUs). Com-

Channel Estimation plex multiplier (CXMUL in Figures 2, and 3) with shifting

(normalization) is one of the designed SFUs. Packing of 16-bit

Covariance Matrix data (I and Q part of received samples) into 32-bit numbers

Estimation

enables that SFU for complex arithmetic have two, instead

of four, input ports (the operands are two complex 32-bit

CG Filter Update

numbers). Data are unpacked inside the SFU (unpacking of

real and imaginary parts of two complex input operands),

Buffer User complex arithmetic on four 16-bit numbers is performed and

N samples Filtering

detection two results (real and imaginary part) are packed in 32-bit

value. In this way both the instruction and data parallelism

Fig. 1. Block diagram of CG equalizer at the mobile handset are achieved within the CXMUL SFU and the amount of

data transports across the buses is reduced. Consequently,

III. I MPLEMENTATION OF ASIP A RCHITECTURE the number of buses is significantly decreased. Comparison

between traditional solution with real multipliers and real

A. TTA architecture adders and the alternative architecture solution with complex

The implemented ASIP architecture is based on the Trans- multiplier is shown on Figure 3.

port Triggered Architecture (TTA) [5] that is a superclass of An SFU for arithmetic operations with sub-word parallelism

VLIW architecture. TTA exploits both instruction and data is also implemented (sub-word add/subtract operation between

level parallelism. The architecture is flexible and new func- two 32-bit numbers represents two parallel add/subtract op-

tional units (FUs), buses, and registers can be added without erations on packed 16-bit operands, for example). The main

any restrictions. In addition, application specific support is feature of this Special Arithmetic Logic Unit (SALU in

0-7803-8521-7/04/$20.00 (C) 2004 IEEE

32 32

to utilize SFUs [9]. A cost-database of hardware components

MUL MUL MUL MUL

Unpacking

contains estimates for dynamic power dissipation and area

based on the 0.13 µ CMOS technology. Frequency f is

* * CXMUL* * the minimum clock frequency necessary to achieve real-time

+ 16 bits + requirements. In Table I, we consider a six-path Pedestrian

B environment [11] (largest computational complexity) in the

Packing

ADD ADD presence of two transmit and two receive antennas.

32

TABLE I

C OMPARATIVE STATISTICS OF DIFFERENT EQUALIZER ARCHITECTURES

Fig. 3. Real multipliers/adders and corresponding complex FU IMPLEMENTED WITH AND WITHOUT SFU S IN P ED . B ENVIRONMENT

Type Buses P [mW] A[gates] Real Mult f [MHz]

1. W/o SFUs 32 190 262,063 8 203

Figure 2) is sign-test of pilot samples and then, depending 2a. W/o SFUs 32 119 190,554 8 102

on operand sign, the appropriate sub-word operation between 2b. W/o SFUs 32 128 230,009 8 102

I and Q values of received data is performed. This two-stage 1. W SFUs 20 72 130,036 9 135

operation is a very frequent operation in the channel estimation 2a. W SFUs 14 36 76,225 5 104

algorithm. The third kind of SFU that is mainly utilized in up- 2b. W SFUs 9 29 54,519 4 101

dating of filter coefficients using iterative CG algorithm is real

multiplication with right shifting by a varying number of bits. Implementation of SFUs causes less data traffic that leads

Since the fixed-point implementation of CG algorithm requires to a significant reduction in the number of buses. The number

some arithmetic precision adjustments, the implementation of of instructions (data transports - ’move operations’) is signifi-

this SFU helps to achieve better convergence to the LMMSE cantly decreased (from 15,196 to 9,418, for full equalization of

solution. one block of 4096 received chips) by implementing SFUs for

By implementing all of these special function units we are complex arithmetic and sub-word parallelism. The smaller in-

able to significantly reduce the bus traffic and connections terconnection network with fewer buses automatically reduces

between buses and FUs, and to optimize (in terms of area, the instruction length - reduction from 736 bits (architecture

execution time and power dissipation) the overall architecture 1. without SFUs from Table I) to 384 bits (architecture 1. with

design. The cost database is updated with the power and area SFUs). As a consequence, the power dissipation and the area

estimates of the implemented SFUs. Our design still contains of the processor core are also dramatically decreased.

standard FUs such as arithmetic FU (add/subtract, shifting) In the two co-processor architecture, filtering on the second

and load/store units as an interface with data memory. The co-processor is based on the updated filter coefficients that

optimized architecture configuration for CG filter update (full are sent from the first co-processor via the external RAM

equalization algorithm presented in Figure 1 except filtering memory interface (shown in Figure 2). Two co-processors

and user detection) with SFUs is presented in Figure 2. operate simultaneously in a pipelined fashion - filtering of

We show that by exploiting the custom nature of ASIP the previous block of data samples is performed while the

architectures the internal structure is simplified especially the filter update for the current block is computed. The benefit

interconnection network between FUs that is a major concern of the single processor approach is the fact that there is

for area occupation and power dissipation. Furthermore, the no need for additional external interface for inter-processor

architecture design is more general than CG equalization - communication as in the architecture with two co-processors.

the majority of implemented user-defined operations can be The main drawback is the larger workload that needs to be

utilized in other linear equalization schemes such as Least processed leading to a higher clock frequency and eventually

Mean Square (LMS). It can be shown that the identical ASIP to higher power dissipation (see simulation estimates from

architecture design can be programmed for LMS equalization Table I).

[9]. TABLE II

S IMULATION STATISTICS FOR SINGLE TTA PROCESSOR FOR FULL

IV. S IMULATION R ESULTS EQUALIZATION ALGORITHM IN DIFFERENT CHANNEL ENVIRONMENTS

In this section we present two hardware architectures for CG Environment Tex [cycles] P [mW] fclk [MHz]

equalization: i) single processor for full equalization referred PedA2x2 251,305 39 76

to in Table I as ’1’, and ii) a second solution with two parallel PedB2x2 446,490 72 135

co-processors: one for channel estimation/covariance matrix VehA2x2 503,964 90 152

computation/filter update referred to as ’2a’, and the other

co-processor for filtering+despreading/descrambling referred Simulation statistics (for processing one block of 4096 data

to as ’2b’. Both solutions are evaluated with and without samples) on the single TTA processor implementation with

implementation of SFUs. The presented ASIP processors are SFUs for full CG equalization algorithm in pedestrian and

obtained by using MOVE software tools [10] (compiler and vehicular environments [11] is presented in Table II. After the

processor explorer) that have been modified in order to be able design exploration phases (described in the next section for

0-7803-8521-7/04/$20.00 (C) 2004 IEEE

180

two-coprocessor solution), it is determined that the optimal Area: coprocessor for CG update

Area: coprocessor for filtering

architecture (in term of cost/performace ratio) consists of: 20 160

Power: coprocessor for CG update

Power: coprocessor for filtering

buses, 4 load/store units, 8 arithmetic FUs (ALUs), 3 SALUs,

Power [mW], Area [KGates]

140

one real multiplier with shifting ability by various number of

bits, and two CXMULs (total of nine real multipliers, see Table 120

I). Data (received data samples and known training sequence)

are stored in two dual-port RAM blocks. The proposed ASIP 100

processor is a power efficient and flexible solution that can 80

operate in different channel environments and achieve real-

time requirements for 3GPP high data rate downlink standard 60

with a reasonable clock frequency. 40

V. D ESIGN E XPLORATION M ETHODOLOGY 20

60 80 100 120 140 160 180 200

More detailed insight into strategies of TTA design explo- Clock Frequency [MHz]

ration for presented architecture solution with two simulta-

neously operating co-processors is described in this section. Fig. 4. Design exploration of co-processor for CG filter update and co-

processor for filtering, both optimized for Pedestrian B channel

Also, a comparison between the two co-processor architecture

and the single processor solution will be presented. In Figure 4, The most optimal range of clock frequency required to

power and area estimates for both co-processors are shown as a achieve real-time requirements is between 100 MHz and

function of minimum clock frequency needed to achieve real- 133 MHz. For a clock frequency of only 66 MHz, larger

time requirements for the 1xEV-DV standard [2]. Proposed area (more hardware units that operate in parallel) is needed

architectures are optimized for CG equalization in a Pedestrian for achieving real-time requirements. Although the clock

B channel environment (the most computationally complex frequency is relatively low, the power dissipation is high

case) with two transmit and two receive antennas. because of the larger number of functional units, buses, and

The same following strategy for design exploration is ap- interconnections. On the other hand, if the minimum clock

plied for both co-processor architectures. The starting co- frequency is set to be higher (about 200 MHz), the area of the

processor configurations have a large number of: buses (24 corresponding optimal co-processors is only slightly reduced

for co-processor for filter update, and 16 for co-processor for since small architecture reduction in this range of clock

filtering and user detection), register file ports (32 read and frequency can cause significant deterioration of performance.

write ports divided into 8 register files), and hardware units Because of the higher clock frequency the power dissipation

(ALUs, SALUs, CXMULs, LSUs, etc) in order to achieve starts to increase in this region.

real-time requirements with a clock frequency of 66MHz. The As mentioned, the single processor architecture for im-

resource exploration is performed, and the number of registers plementation of full CG equalization (pipelined execution of

and register file ports are reduced to the point where the CG filter update algorithm and user detection on the same

execution time is still approximately the same. Now, both processor) is an alternative solution. The most efficient pro-

co-processors have the same number of buses and FUs as cessor (in terms of power, area, and execution time) is already

before, but the number of register file ports and registers is sig- presented in section III (see Table II). An identical design

nificantly reduced. These become new starting co-processors exploration strategy is applied. The area of approximately

for the next stage of resource optimization - reduction of 130,000 gates and the power dissipation (for clock frequency

mostly buses and function units. The result of this two-stage of 133 MHz) of about 72 mW are somewhat larger than the

resource optimization process is the optimized co-processors cumulative estimates for two co-processors for the same clock

with minimum number of register file ports, registers, buses speed (see Figure 4). The reasons for this are larger workload

and function units. Four discrete values (66, 100, 133, and and non-perfect parallelism between different sub-parts of the

200 MHz) for minimum clock frequency for achieving real- equalization algorithm.

time requirements are chosen for accurate power and area

estimation since the cost database contains power and area VI. G ATE -L EVEL S YNTHESIS OF ASIP A RCHITECTURES

estimates only for discrete values of clock period. This set of In this section, the principles of automatic hardware imple-

co-processors represents initial architectures for the last phase mentation of optimized ASIP processors based on TTA with

of design exploration - the connectivity optimization where the special function units will be described. Synthesis result for

unnecessary connections between buses and function units are gate-level design of ASIP processor for full channel equaliza-

removed. This optimization stage simplifies the interconnec- tion (including the user detection) from Table II is presented.

tion network between FUs and significantly lowers the power We show that by using several software tools from different

dissipation and gate count (area). The final estimates for power vendors it is possible, in a fast and efficient way, to produce

dissipation and area of fully optimized co-processors for the hardware implementation of the target ASIP processor. The

range of clock frequency between 66 MHz and 200 MHz are entire hardware-software co-design flow is presented on Figure

shown in Figure 4. 5.

0-7803-8521-7/04/$20.00 (C) 2004 IEEE

Application

(C/C++)

layer of the mobile handset in MIMO wireless systems that can

operate efficiently in various channel environments including

Library of MOVE Library of high scattering fast fading transmission channels. It is shown

FUs Tool SFUs

that the area and power consumption can be dramatically

Processor

reduced by implementing application-specific functional units.

Description At the same time, additional speedup in the execution time

is achieved. Two different hardware solutions are presented:

MOVEGen single processor for full equalization and two interfaced co-

processors, as well as the methodology for design-space explo-

Processor ration for the optimal ASIP architectures for CG equalization.

CMOS (VHDL Code)

Library It is shown that the solution with two parallel co-processors

achieves real-time with a slower clock frequency but requires

Mentor Predesigned

the use of an external interface.

Xilinx ISE

Graphics Components We also presented an efficient design flow for hardware

implementation of ASIP architectures. This design flow starts

Processor Virtex2

Layout FPGA with fixed-point C code for the application and ends with gate-

level implementation of the target processor. Several software

tools from different vendors are efficiently combined together

Fig. 5. Design flow from HLL code to hardware implementation

in order to achieve automatic software-hardware co-design of

In general, hardware/software co-design [12] is a well ASIP processors based on TTA.

known strategy for fast and flexible ASIC hardware imple- VIII. ACKNOWLEDGEMENTS

mentation of applications described by High Level Languages

This work was supported in part by Nokia Corporation,

(HLLs), such as the C/C++ programming language. This strat-

Texas Instruments, Inc., and by NSF under grants EIA-

egy allows to efficiently avoid design errors and to decrease

0224458, and EIA-0321266.

design costs and time-to-market. In our case, hardware design

starts with a C language description of the equalization algo- R EFERENCES

rithm that needs to be implemented at the physical layer of the [1] “1xEV-DV Evaluation Methodology (Rev.26).” Third Generation Part-

mobile handset in a MIMO wireless system. As mentioned, by nership Project Two (3GPP2), May 2001.

using modified MOVE tools and the library of designed special [2] J. Fonollosa, R. Gaspa, X. Mestre, A. Pages, M. Heikkila, J. Kermoal,

L. Schumacher, A. Pollard, and J. Ylitalo, “The IST METRA project,”

function units we are able to generate descriptions of area IEEE Communications Magazine, vol. 40, pp. 78–86, July 2002.

and power efficient ASIP processors. After that, the processor [3] F. Sun, S. Ravi, A. Raghunathan, and N. K. Jha, “Custom-Instruction

description file is converted into a VHDL representation of the Synthesis for Extensible-Processor Platforms,” IEEE Transactions on

Computer-Aided Design of Integrated Circuits and Systems, vol. 23,

processor core by using our modified MOVEGen (processor pp. 216–228, February 2004.

generator) tool [13]. Automatically generated VHDL code for [4] K. Keutzer, S. Malik, and A. R. Newton, “From ASIC to ASIP: The Next

the processor core together with VHDL code for predesigned Design Discontinuity,” in IEEE International Conference on Computer

Design, pp. 84–90, September 2002.

components (program and data memories and other peripher- [5] H. Corporaal, Microprocessor Architecture: From VLIW to TTA. John

als) can be directly used by the Xilinx XST synthesis tool [14] Wiley and Sons, 1997.

for fast FPGA prototyping. The same VHDL design can be [6] G. Golub and C. Van Loan, Matrix Computations. The Johns Hopkins

University Press, 1991.

used by Mentor Graphics tools (Leonardo Spectrum [15] and [7] M. Heikkilla, K. Routsallainen, and J. Lilleberg, “Space-Time Equal-

IC Station [16]) in order to obtain gate-level representation ization using Conjugate-Gradient Algorithm in WCDMA Downlink,” in

and layout of the target processors. CMOS libraries have to Personal, Indoor and Mobile Radio Communications, Sept. 2002.

[8] A. de Baynast, P. Radosavljevic, and J. R. Cavallaro, “Chip Level

be also included in Mentor Graphics design flow. LMMSE Equalization for Downlink MIMO CDMA in Fast Fading

The gate level representation of the proposed ASIP proces- Environments,” in IEEE Globecom, Dec. 2004.

sor for full channel equalization is obtained by using Mentor [9] P. Radosavljevic, “Channel Equalization Algorithms for MIMO Systems

and ASIP Architectures,” Master’s thesis, Rice University, April 2004.

Graphics tools. The ASIP processor for CG/LMS equalization [10] J. Heikkinen, J. Sertamo, T. Rautiainen, and J. Takala, “Design of Trans-

with special function units is synthesized by using ASIC port Triggered Architecture Processor for Discrete Cosine Transform,”

library for 0.5µ CMOS technology. The synthesis estimate in 15th Annual IEEE International ASIC/SOC Conference, Sept. 2002.

[11] L. Schumacher, J. Kermoal, and P. Mogensen, “I-METRA D2 Channel

of the processor core area (the area of processor without Characterisation,” 3GPP I-METRA Project, Oct. 2002.

peripherals) is 135,014 gates which approximately corresponds [12] W. Wolf, “A Decade of Hardware/Software Codesign,” IEEE Computer,

to the area given by the TTA software simulator (see Table I) vol. 36, pp. 38–43, April 2003.

[13] “MOVEGen User’s Manual.” Tampere University of Technology, Jan-

although the gate count is obtained by using 0.5µ instead of uary 2004.

0.13µ CMOS libraries. [14] “Xilinx ISE Foundation [Online].” Available: http://www.xilinx.com/

products.

VII. C ONCLUSION [15] “Leonardo Spectrum [Online].” Available: http://www.mentor.com/

leonardospectrum.

We proposed an optimized and flexible ASIP architecture [16] “IC Station [Online].” Available: http://www.mentor.com/cicd/ icsta-

based on TTA for 3GPP channel equalization at the physical tion.html.

0-7803-8521-7/04/$20.00 (C) 2004 IEEE

You might also like

- Bolted Joints Integrity Management Guidelines PDFDocument54 pagesBolted Joints Integrity Management Guidelines PDFghetto_bmx_boyNo ratings yet

- An Efficient ASIC Architecture For Real-Time Edge DetectionDocument10 pagesAn Efficient ASIC Architecture For Real-Time Edge Detectionprakashjyoti0901No ratings yet

- Cascaded Multilevel InvertersDocument6 pagesCascaded Multilevel InvertersMinhaj NaimNo ratings yet

- A New Vlsi Architecture For Modi EdDocument6 pagesA New Vlsi Architecture For Modi Edsatishcoimbato12No ratings yet

- Design A Pipelined Datapath Synthesis System For Digital Signal ProcessingDocument12 pagesDesign A Pipelined Datapath Synthesis System For Digital Signal ProcessingVashist ManagariNo ratings yet

- High-Performance 8-Bit Modulator Used For Sigma-Delta Analog To Digital ConverterDocument7 pagesHigh-Performance 8-Bit Modulator Used For Sigma-Delta Analog To Digital ConverterAmeya DeshpandeNo ratings yet

- FPGA Design and Implementation Issues of Artificial Neural Network BasedDocument3 pagesFPGA Design and Implementation Issues of Artificial Neural Network Basedvigneshwaran50No ratings yet

- Embedded Node Around A DSP Core For Mobile Sensor Networks Over 802.11 InfrastructureDocument4 pagesEmbedded Node Around A DSP Core For Mobile Sensor Networks Over 802.11 Infrastructureb42eluNo ratings yet

- Transactions Letters: Efficient and Configurable Full-Search Block-Matching ProcessorsDocument8 pagesTransactions Letters: Efficient and Configurable Full-Search Block-Matching ProcessorsrovillareNo ratings yet

- A Software-Programmable Multiple-Standard Radio PlatformDocument5 pagesA Software-Programmable Multiple-Standard Radio PlatformdvdreadsNo ratings yet

- Tam MetinDocument4 pagesTam MetinerkandumanNo ratings yet

- Hardware Performance Simulations of Round 2 Advanced Encryption Standard AlgorithmsDocument55 pagesHardware Performance Simulations of Round 2 Advanced Encryption Standard AlgorithmsMihai Alexandru OlaruNo ratings yet

- Function Unit Specialization Through Code AnalysisDocument4 pagesFunction Unit Specialization Through Code AnalysisdanbenyaminNo ratings yet

- Anjali Kumari ReportDocument8 pagesAnjali Kumari ReportGirdhar Gopal GautamNo ratings yet

- Dept. of Ece, Sreebuddha College of Engineering 1Document34 pagesDept. of Ece, Sreebuddha College of Engineering 1SARATH MOHANDASNo ratings yet

- Self Optimization Remote Eletrical-TiltDocument5 pagesSelf Optimization Remote Eletrical-TiltLêninho CarvalhoNo ratings yet

- VLSI Implementation of Modified Booth Algorithm: Rasika Nigam, Jagdish NagarDocument4 pagesVLSI Implementation of Modified Booth Algorithm: Rasika Nigam, Jagdish NagarerpublicationNo ratings yet

- 7 IJAEST Volume No 3 Issue No 1 Performance Evaluation of Adaptive Modulation Techniques of WiMax Network With Cyclic Prefix 034 038Document5 pages7 IJAEST Volume No 3 Issue No 1 Performance Evaluation of Adaptive Modulation Techniques of WiMax Network With Cyclic Prefix 034 038iserpNo ratings yet

- Performance Analysis of Uncoded & Coded Ofdm System For Wimax NetworksDocument5 pagesPerformance Analysis of Uncoded & Coded Ofdm System For Wimax NetworksInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- 307 - An Efficient Two-Phase 3387-11439-1-PBDocument7 pages307 - An Efficient Two-Phase 3387-11439-1-PBMTP FilmboxNo ratings yet

- Fpga Implementation of A License Plate Recognition Soc Using Automatically Generated Streaming AcceleratorsDocument8 pagesFpga Implementation of A License Plate Recognition Soc Using Automatically Generated Streaming AcceleratorsMuhammad Awais Bin AltafNo ratings yet

- Digital Coherent Optical Receivers Algorithms and SubsystemsDocument16 pagesDigital Coherent Optical Receivers Algorithms and SubsystemsHebaNo ratings yet

- Alternating Optimization Based Hybrid Precoding Strategies For Millimeter Wave MIMO SystemsDocument12 pagesAlternating Optimization Based Hybrid Precoding Strategies For Millimeter Wave MIMO Systemsanthony uwaechiaNo ratings yet

- The Role of Programmable Digital Signal Processors (DSP) For 3G Mobile Communication SystemsDocument8 pagesThe Role of Programmable Digital Signal Processors (DSP) For 3G Mobile Communication Systemsdd bohraNo ratings yet

- FPGA Implementation of MIMO AlgorithmsDocument4 pagesFPGA Implementation of MIMO AlgorithmsNors NoorNo ratings yet

- Optimal Complexity Architectures For Pipelined Distributed Arithmetic-Based LMS Adaptive FilterDocument13 pagesOptimal Complexity Architectures For Pipelined Distributed Arithmetic-Based LMS Adaptive FiltertresaNo ratings yet

- VlsiDocument32 pagesVlsibalasaravanan0408No ratings yet

- Vlsi Impimentation of OfdmDocument13 pagesVlsi Impimentation of Ofdmprashanth68760100% (1)

- Chameleon ChipDocument26 pagesChameleon Chipkrushang kananiNo ratings yet

- Performance Analysis of MAC Unit Using Booth, Wallace Tree, Array and Vedic MultipliersDocument8 pagesPerformance Analysis of MAC Unit Using Booth, Wallace Tree, Array and Vedic MultipliersSanchariniNo ratings yet

- Application of Parallel Processors To Real-Time Sensor Array ProcessingDocument7 pagesApplication of Parallel Processors To Real-Time Sensor Array ProcessingAnonymous epg6ultNo ratings yet

- Scalable Digital CMOS Comparator Using A Parallel Prefix TreeDocument10 pagesScalable Digital CMOS Comparator Using A Parallel Prefix TreeRamesh SNo ratings yet

- CC C!C" C##: C C C C C CCJDocument12 pagesCC C!C" C##: C C C C C CCJsatyagireeshNo ratings yet

- Deeksha Scopus PaperDocument6 pagesDeeksha Scopus PaperbalajiNo ratings yet

- LATW2009 Analog Test Bus Architecture For Small Die Size and Limited Pin Count Devices With Internal IPs Testability Emphasis RMaltioneDocument6 pagesLATW2009 Analog Test Bus Architecture For Small Die Size and Limited Pin Count Devices With Internal IPs Testability Emphasis RMaltioneDaniel FerrãoNo ratings yet

- Building Custom FIR Filters Using System GeneratorDocument4 pagesBuilding Custom FIR Filters Using System Generatordwivedi89No ratings yet

- The Islip Scheduling Algorithm For Input-Queued Switches: Nick MckeownDocument14 pagesThe Islip Scheduling Algorithm For Input-Queued Switches: Nick MckeownAshish FugareNo ratings yet

- Most Resource Efficient Matrix Vector Multiplication On FPGAsDocument18 pagesMost Resource Efficient Matrix Vector Multiplication On FPGAspsathishkumar1232544No ratings yet

- Vlsi Imlememt of OdfmDocument10 pagesVlsi Imlememt of OdfmShrey MalikNo ratings yet

- 2010 Patmos JulianDocument10 pages2010 Patmos JulianMohammad Seemab AslamNo ratings yet

- Wireless Sensor NetworksDocument5 pagesWireless Sensor NetworksBase Building AcademyNo ratings yet

- Low-Power Viterbi Decoder Design For TCM DecodersDocument5 pagesLow-Power Viterbi Decoder Design For TCM DecodersPooja BanNo ratings yet

- Very High-Level Synthesis of Datapath and Control Structures For Reconfigurable Logic DevicesDocument5 pagesVery High-Level Synthesis of Datapath and Control Structures For Reconfigurable Logic Devices8148593856No ratings yet

- Implementation of Reconfigurable Adaptive Filtering AlgorithmsDocument5 pagesImplementation of Reconfigurable Adaptive Filtering AlgorithmsChaitanyaNo ratings yet

- 4th Process TomograpgyDocument6 pages4th Process TomograpgyEmmanuel Abdias Romano CastilloNo ratings yet

- Roba MulDocument56 pagesRoba MulNishitha NishiNo ratings yet

- A Methodology To Design and Prototype Optimized Embedded RobDocument6 pagesA Methodology To Design and Prototype Optimized Embedded RobHelder Anibal HerminiNo ratings yet

- Innovus Implementation System - CadenceDocument9 pagesInnovus Implementation System - CadenceSyed Saud Ur RehmanNo ratings yet

- Why Con Gurable Computing? The Computational Density Advantage of Con Gurable ArchitecturesDocument17 pagesWhy Con Gurable Computing? The Computational Density Advantage of Con Gurable ArchitecturesHari KrishnaNo ratings yet

- Assignment No 4 EmbeddedDocument5 pagesAssignment No 4 Embeddedsatinder singhNo ratings yet

- Performance Analysis of Low Complexity MAP Decoder For Low Power ApplicationsDocument14 pagesPerformance Analysis of Low Complexity MAP Decoder For Low Power ApplicationsSundarRajanNo ratings yet

- Priyanka - 50300 16 130Document4 pagesPriyanka - 50300 16 130Aravind GopaganiNo ratings yet

- Major Conference PaperDocument14 pagesMajor Conference Papermanishmeenahlm2No ratings yet

- Ijesrt: Performance Analysis of An Noc For Multiprocessor SocDocument5 pagesIjesrt: Performance Analysis of An Noc For Multiprocessor SocRajesh UpadhyayNo ratings yet

- Design and Implementation of High Speed Carry Select AdderDocument6 pagesDesign and Implementation of High Speed Carry Select AdderseventhsensegroupNo ratings yet

- FPGA Implementation of CORDIC-Based QRD-RLS AlgorithmDocument5 pagesFPGA Implementation of CORDIC-Based QRD-RLS Algorithmsappal73asNo ratings yet

- Multilevel Power Optimization For ICA ProcessorDocument4 pagesMultilevel Power Optimization For ICA ProcessorIJSTENo ratings yet

- Design and Experimental Evaluation of A Time-Interleaved ADC Calibration Algorithm For Application in High-Speed Communication SystemsDocument12 pagesDesign and Experimental Evaluation of A Time-Interleaved ADC Calibration Algorithm For Application in High-Speed Communication SystemsRahul ShandilyaNo ratings yet

- 即時高清晰度車牌定位與辨識加速器適用於物聯網端點系統單晶片Document11 pages即時高清晰度車牌定位與辨識加速器適用於物聯網端點系統單晶片qqnicetwNo ratings yet

- Implementation of AMBA APB Bridge With Efficient Deployment of System ResourcesDocument4 pagesImplementation of AMBA APB Bridge With Efficient Deployment of System Resourcesprojects allNo ratings yet

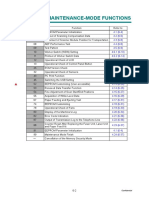

- List of Maintenance-Mode Functions: ConfidentialDocument1 pageList of Maintenance-Mode Functions: ConfidentialPreda AlexandraNo ratings yet

- Thermo Scientific APCatalogue 2015 MIDRES (New)Document168 pagesThermo Scientific APCatalogue 2015 MIDRES (New)patologic123No ratings yet

- DX DiagDocument40 pagesDX Diagvicente.gonzalez123321No ratings yet

- A Novel Data Packing Techniques For QC-LDPC Decoder Architecture Applied To NAND Flash ControllerDocument3 pagesA Novel Data Packing Techniques For QC-LDPC Decoder Architecture Applied To NAND Flash ControllerHeekwan SonNo ratings yet

- OSY MicroprojectDocument23 pagesOSY MicroprojectIrshad ShaikhNo ratings yet

- Data SDM 2020 Di AspakDocument7 pagesData SDM 2020 Di AspakPuskesmas Kuta BlangNo ratings yet

- Sibas wpr32Document41 pagesSibas wpr32conganthonNo ratings yet

- Great Sound! Powerful Bass!! Perfect Combination With Denon Av Receivers!!!Document2 pagesGreat Sound! Powerful Bass!! Perfect Combination With Denon Av Receivers!!!EnisNo ratings yet

- Master Learning MapsDocument9 pagesMaster Learning MapssriNo ratings yet

- 08 TIA-Portal PracticalDocument3 pages08 TIA-Portal PracticalAnkitNo ratings yet

- Font AwesomeDocument24 pagesFont AwesomeBrahim LetaiefNo ratings yet

- Transmitter e Htj-E002Document5 pagesTransmitter e Htj-E002masatusNo ratings yet

- Jusco Gaurav KumarDocument23 pagesJusco Gaurav KumarGaurav KumarNo ratings yet

- C.V of Muhammad Anwar HussainDocument2 pagesC.V of Muhammad Anwar HussainNida AnwarNo ratings yet

- Nvam 1Document660 pagesNvam 1justinmallari09No ratings yet

- Brosur - Specification Fairbanks FB2550 NEMADocument1 pageBrosur - Specification Fairbanks FB2550 NEMAPT. OMETRACO ARYA SAMANTANo ratings yet

- IC200CPU001Document1 pageIC200CPU001ahmedNo ratings yet

- Aduan Peralatan ICT Sekolah Negeri Perak 2018pkgslimriverDocument4 pagesAduan Peralatan ICT Sekolah Negeri Perak 2018pkgslimrivereidda74No ratings yet

- Shepherd PDFDocument119 pagesShepherd PDFjoseprudencio8848No ratings yet

- User Manual LCD Signature Pad Signotec GammaDocument16 pagesUser Manual LCD Signature Pad Signotec GammaAlexander MoralesNo ratings yet

- 8255 Programmable Peripheral InterfaceDocument27 pages8255 Programmable Peripheral InterfaceSivaprakasam KarthikeyanNo ratings yet

- AMD Software Release Notes Ver. 3.08.06.148: Package Contents and Compatible Operating SystemsDocument4 pagesAMD Software Release Notes Ver. 3.08.06.148: Package Contents and Compatible Operating Systemssantiago jimenezNo ratings yet

- 32 Bit AluDocument4 pages32 Bit AluJanakiSreeramNo ratings yet

- BPDB (03 June 2011 BUET)Document2 pagesBPDB (03 June 2011 BUET)জাকির হোসেন100% (3)

- TV Remot Home ApplicationsDocument4 pagesTV Remot Home ApplicationsMahesh NeelarapuNo ratings yet

- CV MariamDocument3 pagesCV Mariamapi-322494265No ratings yet

- GC 1018Document12 pagesGC 1018Goran Gero VukovicNo ratings yet

- HCIA-Cloud Computing V4.0 Mock ExamDocument5 pagesHCIA-Cloud Computing V4.0 Mock ExamAnonymous XZnkpMecNo ratings yet