Digital System Design Jan 2018 (2015 Scheme)

Digital System Design Jan 2018 (2015 Scheme)

Uploaded by

sukanta majumderCopyright:

Available Formats

Digital System Design Jan 2018 (2015 Scheme)

Digital System Design Jan 2018 (2015 Scheme)

Uploaded by

sukanta majumderCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Digital System Design Jan 2018 (2015 Scheme)

Digital System Design Jan 2018 (2015 Scheme)

Uploaded by

sukanta majumderCopyright:

Available Formats

For More Question Papers Visit - www.pediawikiblog.

com

USN [

15EE35

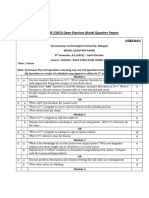

Third Semester B.E. Degree Examination, Dec.2017/Jall.2018

Digital System Design

m

Time: 3 hrs. r lax. Marks: 80

ote;Answer any ,FIYE full questions, choosing one full que tion from each module.

Module-l

co

1 a. With basic block diagram, explain the combinational logic circuit. (04 Marks)

b. Reduce the following function using K-map technique and implement using basic gates

i) f(P, Q, R, S) = 2.m(O, 1,4,8,9, 10) + d (2, 11)

ii) f(A, B, C, D) = 1eM (0, 2, 4, 10, 11, 14, 15) (12 Marks)

g.

OR

lo

2 a. Simplify using the Quine-Mcclusky minimization technique.

Y = f{a, b, c, d) = Lm (0, 2, 8, 10) (08 Marks)

b. Simplify the given function using MEV technique.

ib

f{a, b, c, d) = L(2, 3, 4,5, 13, 15) + td 8,9, 10, 11). (08 Marks)

ik

Module-2

a. With the aid 0 eneral structure, clearly distingui h between a decoder and encoder.

(05 Marks)

w

b. Implement following multiple output function using one 74LS138 and external gates.

FI (A, B, C) = Lm (I, 4, 5, 7)

F2 (A, B, C) = reM (2, 3, 6, 7) (06 Marks)

ia

c. Draw the interfacing diagram of ten keypad interface to a digital system using decimal to

BCD encoder (IC 74LS 14 7: Decimal to BCD priority encoder). (05 Marks)

ed

OR

4 a. Design a full adder by constructing the truth table and simplify the output equations.

.p

(06 Marks)

b. Write a truth table for two-bit magnitude comparator. Write the Kamaugh map for each

output of two bit magnitude comparator and the resulting equation. (10 Marks)

w

Module-3

w

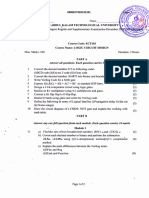

5 a. What Js the difference between a flip-flop and a latch? With logic diagram and truth table,

explain the operation of gated SR latch. (08 larks)

J!

o

Z

6. £xp(ain (he 6peratidn ofMa tel" slave JK Flip-flop along with it circuit diagram. (08 Marks)

w

C

~'o"

0. OR

E

6 a. Explain the working principle of four bit binary ripple counter, with the help of a logic

diagram, timing diagram and counting sequence. (10 Marks)

b. With logic diagram and counting sequence explain Mod - 4 ring counters. (06 Marks)

10f2

For More Question Papers Visit - www.pediawikiblog.com

For More Question Papers Visit - www.pediawikiblog.com

F f /

~

.)

'v '15EE35

/o~

m

Module-4

co

7 a. Distinguish between Moore and Mealy model with necessary block diagrams. (08 Marks)

b. Give output function a. transition table and state diagram by analyzing the sequential circuit

shown in Fig. Q7(b). ./ '(08 Marks)

g.

tr;=

CLK >4

lo

ib

OR

Fig. Q7(b)

ik

8 a. Write the basic recommended steps for the design of a clocked synchronous sequential

circuit. (06 Marks)

b. Design a synchronous counter using J-K flip flops to count the sequence 0, 1, 2, 4, 5, 6, 0, 1,

2. Use state diagram and state table. (10 Marks)

w

Module-5

a. Explain brief history ofHDL and structure ofHDL module.

ia

9 (06 Marks)

b. List the classificationervant data types. Compare the VaDL data types and Verilog data

types. (10 Marks)

~

ed

OR

10 a. Explain signal declaration and signal assignment statements with relevant example.

(06 Marks)

.p

b. Write a data flow description VHDL for a system that has three l-bit inputs a (1), a(2) and

a(3) one l-bit output b. The least significant bit is a(1) ; and b is 1, only when (a(1) a(2)

a(3» = 1,3, 6 or 7 (all in decimal) otherwise b is 0. Derive a minimized Boolean function of

the system and write the data flow description. (10 Marks)

w

w

w

20f2

For More Question Papers Visit - www.pediawikiblog.com

You might also like

- King Air C90ABGT Pilot Training ManualDocument409 pagesKing Air C90ABGT Pilot Training ManualFabio100% (8)

- Seminar Report On PollutionDocument50 pagesSeminar Report On PollutionRanjuSingla100% (2)

- Bielenda Pro 2018 PDFDocument76 pagesBielenda Pro 2018 PDFbielenda83% (6)

- (12 Marks) (04 Marks)Document2 pages(12 Marks) (04 Marks)Mr PerfectNo ratings yet

- Module-1: Set No. 1Document2 pagesModule-1: Set No. 1Omkar MutalikNo ratings yet

- Digital Electronics 32470Document3 pagesDigital Electronics 32470bulkeshsinhmar67No ratings yet

- Drttit - Gvet.edu - in Drttit - Gvet.edu - in Drttit - Gvet.edu - in Drttit - Gvet.edu - inDocument2 pagesDrttit - Gvet.edu - in Drttit - Gvet.edu - in Drttit - Gvet.edu - in Drttit - Gvet.edu - inrama KrishnaNo ratings yet

- March-2022 (1) - 231101 - 193459Document1 pageMarch-2022 (1) - 231101 - 193459nanikarthikreddy2002No ratings yet

- P17ec33 - Z1Document1 pageP17ec33 - Z1aeunNo ratings yet

- EC8392 DE Model Exam QuesDocument2 pagesEC8392 DE Model Exam Queskpkarthi80No ratings yet

- Logic Design Jan 2010 ESDocument2 pagesLogic Design Jan 2010 ESPrasad C MNo ratings yet

- Subject Code-2092: FamilyDocument3 pagesSubject Code-2092: Familyनीरज बंसलNo ratings yet

- Adobe Scan 07-Feb-2024Document3 pagesAdobe Scan 07-Feb-2024bulkeshsinhmar67No ratings yet

- Coa-June 2023Document2 pagesCoa-June 2023examlab57No ratings yet

- 18CS32 April 2021Document3 pages18CS32 April 20213BR20CS072 Mallika begum ksNo ratings yet

- DLD Important QuestionsDocument9 pagesDLD Important Questionsmallurajareddy1456No ratings yet

- 2 IT201 Digital System Design - Supple - July 2017 1Document2 pages2 IT201 Digital System Design - Supple - July 2017 1Gayatri SharmaNo ratings yet

- P15ec33 Z1Document2 pagesP15ec33 Z1Arun Kumar K MNo ratings yet

- DLC - 22-23 - 21EC304 - Model QPDocument2 pagesDLC - 22-23 - 21EC304 - Model QPArun Kumar K MNo ratings yet

- QBank DPSD cs2202Document6 pagesQBank DPSD cs2202kunarajNo ratings yet

- Exa/iaq/01 (01) Exa/iaq/01 (01) Exa/iaq/01 (01) : U I T U I TDocument2 pagesExa/iaq/01 (01) Exa/iaq/01 (01) Exa/iaq/01 (01) : U I T U I TsrisridivineNo ratings yet

- 15 Ec 661Document6 pages15 Ec 661Prajwal ShettykpNo ratings yet

- Digital Electronic & Fundamentals of Microprocessor: B.E. Third Semester (Information Technology) (C.B.S.)Document2 pagesDigital Electronic & Fundamentals of Microprocessor: B.E. Third Semester (Information Technology) (C.B.S.)Hamit BisaneNo ratings yet

- Logic Design Jan 2010 OldDocument1 pageLogic Design Jan 2010 OldPrasad C MNo ratings yet

- DIGITAL ELECTRONICS NovemberDecember-2020Document1 pageDIGITAL ELECTRONICS NovemberDecember-2020ethanNo ratings yet

- 2EC6302-Digital Electronics QBDocument12 pages2EC6302-Digital Electronics QBSurendar PNo ratings yet

- EE3302-DLC MODEL QP UpdatedDocument3 pagesEE3302-DLC MODEL QP UpdatedKeerthana SahadevanNo ratings yet

- Logic Design July 2009 ESDocument1 pageLogic Design July 2009 ESPrasad C MNo ratings yet

- Ec6302 - Digital Electronics Question Bank Unit - I Minimization Techniques and Logic GatesDocument12 pagesEc6302 - Digital Electronics Question Bank Unit - I Minimization Techniques and Logic GatesSurendar PNo ratings yet

- De MJ07Document2 pagesDe MJ07prayog8No ratings yet

- Nov - Dec 2021Document3 pagesNov - Dec 2021Pandyselvi BalasubramanianNo ratings yet

- School of Electronics Engineering ECE 2003 (Fall 20-21) / Assignment / D1 Slot / Dr.M.Geetha Priya Max Marks: 100 Si - No. Questions MarksDocument4 pagesSchool of Electronics Engineering ECE 2003 (Fall 20-21) / Assignment / D1 Slot / Dr.M.Geetha Priya Max Marks: 100 Si - No. Questions MarksBarath KumarNo ratings yet

- PUEC3TL02 Question BankDocument11 pagesPUEC3TL02 Question Bankprasanna5002No ratings yet

- Ect203 Scheme 2020Document8 pagesEct203 Scheme 2020ShakiraNo ratings yet

- QP Dec-2023Document2 pagesQP Dec-2023ayshazeba2005No ratings yet

- Cse 205Document39 pagesCse 205sharminmin92No ratings yet

- VTU Question PapersDocument12 pagesVTU Question PapersQwertyNo ratings yet

- Ect203 Logic Circuit Design, December 2022Document2 pagesEct203 Logic Circuit Design, December 2022ShakiraNo ratings yet

- Gtu Computer 3130704 Summer 2023Document2 pagesGtu Computer 3130704 Summer 2023madhavjani06No ratings yet

- EC6302-Digital ElectronicsDocument14 pagesEC6302-Digital Electronicsmagy1989No ratings yet

- LCDPYQSDocument8 pagesLCDPYQSsreehari14shrNo ratings yet

- AprilMay - 2018 DEDocument2 pagesAprilMay - 2018 DESAMMAIAHNo ratings yet

- Guessing Papers 1-2-12th Electronics Sub Code C2Document6 pagesGuessing Papers 1-2-12th Electronics Sub Code C2snigdhagulhane0922No ratings yet

- Digital ElectronicsDocument7 pagesDigital ElectronicsAlakaaa PromodNo ratings yet

- Digital Logic Design March 2022Document2 pagesDigital Logic Design March 2022Gopl KuppaNo ratings yet

- R19ES1213082021Document2 pagesR19ES1213082021kittukpraveen1No ratings yet

- UNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Document18 pagesUNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Deepak NaiduNo ratings yet

- ANALOG & DIGITAL INTEGRATED CIRCUIT (ADIC) Model Question PaperDocument3 pagesANALOG & DIGITAL INTEGRATED CIRCUIT (ADIC) Model Question PaperMATHANKUMAR.SNo ratings yet

- LOC (1st) Dec2018Document2 pagesLOC (1st) Dec2018Anshul JangraNo ratings yet

- WWW - Manaresults.Co - In: (Common To Ece, Eie, Etm)Document2 pagesWWW - Manaresults.Co - In: (Common To Ece, Eie, Etm)Anil Kumar BNo ratings yet

- Digital Electronics & Fundamentals of Microprocessor: B.E. (Information Technology) Third Semester (C.B.S.)Document2 pagesDigital Electronics & Fundamentals of Microprocessor: B.E. (Information Technology) Third Semester (C.B.S.)Hamit BisaneNo ratings yet

- L-2/T-Licse Date: 08/08/2017: - 'Ds (Jia)Document22 pagesL-2/T-Licse Date: 08/08/2017: - 'Ds (Jia)Na ThakaNo ratings yet

- L-3/T - 2/EEE Date: 28/0312022: IS) +D (I, 3,6,7)Document19 pagesL-3/T - 2/EEE Date: 28/0312022: IS) +D (I, 3,6,7)Sanjid ElahiNo ratings yet

- Information TechnologyDocument7 pagesInformation TechnologyDEVANAND ANo ratings yet

- 14 Ee 305 Dec15Document2 pages14 Ee 305 Dec15Bhanath ShankerNo ratings yet

- QP DLCDocument2 pagesQP DLCDivya PriyaNo ratings yet

- Srinivasa Ramanujan Institute of TechnologyDocument2 pagesSrinivasa Ramanujan Institute of TechnologyPandu RangareddyNo ratings yet

- Bec 3022Document4 pagesBec 3022h.s.surabhi2005No ratings yet

- Unit-1-2-3 Question Bank DEC 2131004Document2 pagesUnit-1-2-3 Question Bank DEC 2131004Amit KumarNo ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Log-Linear Models, Extensions, and ApplicationsFrom EverandLog-Linear Models, Extensions, and ApplicationsAleksandr AravkinNo ratings yet

- The Elements of Computing Systems, second edition: Building a Modern Computer from First PrinciplesFrom EverandThe Elements of Computing Systems, second edition: Building a Modern Computer from First PrinciplesNo ratings yet

- Ficha Tecnica Legrand-407859Document1 pageFicha Tecnica Legrand-407859jhernandezNo ratings yet

- E-Ration Card Management System Using RFIDDocument18 pagesE-Ration Card Management System Using RFIDKaataRanjithkumarNo ratings yet

- Down Hole Heat Ex ChangersDocument11 pagesDown Hole Heat Ex ChangersSaudah ShaikhNo ratings yet

- Petroleum Plant Design Open and Closed Drains SystemDocument4 pagesPetroleum Plant Design Open and Closed Drains SystemKaren Isabel Ambiado RivasNo ratings yet

- Curriculum VitaeDocument1 pageCurriculum VitaeMEBERU100% (1)

- Moot Court Competition 19 2022Document17 pagesMoot Court Competition 19 2022Prince KumarNo ratings yet

- STIHL MS 210 230 250 Instruction Manual PDFDocument152 pagesSTIHL MS 210 230 250 Instruction Manual PDFDavid WestNo ratings yet

- 2 2C TowerDocument13 pages2 2C TowerAhmed GadNo ratings yet

- Women in AgricultureDocument3 pagesWomen in AgricultureRajul C DasNo ratings yet

- Versele Laga Wegwijzer Duivencataloog 2017 4t Final Oe LRDocument148 pagesVersele Laga Wegwijzer Duivencataloog 2017 4t Final Oe LRTomitaNo ratings yet

- Ch7 Port Hinterlands LogisticsDocument37 pagesCh7 Port Hinterlands LogisticsAswinanderst Twilight-Forever TbcKuadratNo ratings yet

- Tak Tik Book - Movie Tickets & Movie Times Sri LankaDocument1 pageTak Tik Book - Movie Tickets & Movie Times Sri LankaGaming OfficerNo ratings yet

- Schedule An Appointment - Confirmation USPSDocument1 pageSchedule An Appointment - Confirmation USPSJose RiveraNo ratings yet

- Fate Core Cheat Sheet and Vet Guide Landscape PDFDocument2 pagesFate Core Cheat Sheet and Vet Guide Landscape PDFVikshadeNo ratings yet

- G.R. No. L-23002 July 31, 1967 CONCEPCION FELIX VDA. DE RODRIGUEZ, Plaintiff-AppellantDocument19 pagesG.R. No. L-23002 July 31, 1967 CONCEPCION FELIX VDA. DE RODRIGUEZ, Plaintiff-AppellantHello123No ratings yet

- System Analysis and DesignDocument13 pagesSystem Analysis and DesigncakiirceydaNo ratings yet

- TR50502SSLPT4WFRBR UpdatedDocument117 pagesTR50502SSLPT4WFRBR UpdatedVinicius JoseNo ratings yet

- Raw Material List With Status of Standard 29-4-2021 - 1624084042 (SW) - 1624806964Document9 pagesRaw Material List With Status of Standard 29-4-2021 - 1624084042 (SW) - 1624806964swapon kumar shillNo ratings yet

- Mona Tank 10 Installation Guide SpecifierDocument1 pageMona Tank 10 Installation Guide SpecifierdonNo ratings yet

- Pattern Drafting Grading CurDocument44 pagesPattern Drafting Grading Curmahendran50% (2)

- Power Filter Options For The FPD-Link Interfaces in TRAVEO™ T2G FamilyDocument15 pagesPower Filter Options For The FPD-Link Interfaces in TRAVEO™ T2G Familygshgeje hehjwjeNo ratings yet

- DataMine OverviewDocument21 pagesDataMine OverviewMarlon Torres TerronesNo ratings yet

- 22 - Balancing Personal and Professional NeedsDocument11 pages22 - Balancing Personal and Professional NeedsLoi CrespoNo ratings yet

- Bakery DataDocument101 pagesBakery DataSatya SharmaNo ratings yet

- Nptel CourseDocument2 pagesNptel CourseAnnappa N ANo ratings yet

- Bond GraphDocument5 pagesBond GraphMila Dhari NovianaNo ratings yet