AN2094 - PSoC® 1 GPIO Pin-Port Reconfiguration

AN2094 - PSoC® 1 GPIO Pin-Port Reconfiguration

Uploaded by

Daniel Eneas Calderon RodriguezCopyright:

Available Formats

AN2094 - PSoC® 1 GPIO Pin-Port Reconfiguration

AN2094 - PSoC® 1 GPIO Pin-Port Reconfiguration

Uploaded by

Daniel Eneas Calderon RodriguezOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

AN2094 - PSoC® 1 GPIO Pin-Port Reconfiguration

AN2094 - PSoC® 1 GPIO Pin-Port Reconfiguration

Uploaded by

Daniel Eneas Calderon RodriguezCopyright:

Available Formats

PSoC 1 GPIO Pin-Port Reconfiguration

AN2094

Associated Project: Yes Associated Part Families: CY8C24x23A, CY8C24x94, CY8C21x34, CY8C20x34, CY8C21x23, CY8C27x43, CY8C28xxx, CY8C29x66, CY7C64215, CYWUSB6953 Software Version: PSoC Designer 5.1 SP1 Associated Application Notes: AN2033

Application Note Abstract

AN2094 shows how to change the configuration of PSoC 1 device pins during code execution. The general-purpose input/outputs (GPIOs) of PSoC 1 device have eight drive modes that can be switched between throughout device operation. TM They can be easily initially configured using the PSoC Designer IDE. They may also be changed during runtime by performing specific register writes. This application note describes how to perform those register writes, and gives examples of how it is done in both assembly and C.

Introduction

Input and output (I/O) pin configuration is performed using two methods. The first method is to define the configuration as part of the initialization in PSoC Designers Device Editor. The easiest way to configure the pins is if the pin configuration is fixed at all times. The second method is to use firmware to reconfigure a pin. Pin configuration may be changed at any time by using assembler or C code.

In the first field shown in Figure 1, Name, the name of the pin is shown. You can rename the pin to make its purpose more obvious. The Port field shows the physical mapping of the pin. This field is not editable. The Select field configures some of the special behaviors of pins: AnalogInput. Only Port 0 and Port 2 have additional analog input and analog output options. AnalogInput gets analog signals from the outside world and connects to the analog column input MUX or to PSoC blocks directly. For example, if you use an ADC, you must configure at least one of the pins as AnalogInput to get analog signals from the outside world. AnalogOutputBuf. Only Port 0 has additional analog output options. Default. The global bus is not connected and the drive strength is High Z Analog. StdCPU. Normal I/O through the port. This is controlled by the CPU. Global_IN, Global_OUT. Global inputs and outputs provide capability to route clock and data signals to the digital PSoC blocks. If you configure a pin as a Global_IN (input) or Global_OUT (output), then that pin can talk to the digital blocks. For example, if the Global_IN is selected, then this selection connects that particular pin to the Global_INPUT bus. This bus is then used as an input to the digital PSoC blocks. Apart from the previously mentioned pin types, there are pins that have special features, and are listed. For example, P1[0] and P1[1] have XtalOut and XtalIn, P1[4] has ExtSysClk, P1[5] and P1[7] have I2C_SDA and I2C_SCL, and so on.

Device Editor Configuration

I/O pins may be configured by using the Pinout View mode of the Device Editor. Inside the Pinout View mode, a table appears in the lower left corner of the PSoC Designer interface. This table is shown in Figure 1. Figure 1. PSoC Designer Pinout Window(Drive List)

June 15, 2011

Document No. 001-40480 Rev. *D

AN2094

Pin Drive Modes

You can configure the pin as input or output by selecting the drive property. These drive modes are summarized in Figure 2. A description of the drive properties follows. High Z. High Z or high impedance mode is used for digital inputs that are driven high and low externally. High Z Analog. This mode is similar to the High Z state, but the digital input section is disabled. Select this mode to use this pin as an analog input or output. This mode should be selected if the pin is unused. Each GPIO pin has a Schmitt trigger cell which interfaces with the internal digital data bus. In High Z Analog mode, this Schmitt trigger cell is disabled. This prevents oscillations at the Schmitt trigger output when the analog signal on the pin is at threshold levels. Open-drain High. In this mode, the HIGH output is driven with a strong drive. The LOW output is High Z. Open-drain Low. In this mode, the LOW output is driven with a strong drive and HIGH output is open. This mode is 2 suitable for I C bus where external pull-up resistors are used. Strong. Use the Strong mode if your pin is an output driving a load. The pin has a low impedance connection to VSS and VDD when driven high and low. Do not use the Strong mode if the pin is an input.

Pull-down. In this mode, HIGH output is driven strong, and LOW output is through an internal pull-down resistor of approximately 5.6K. This mode may be used as an input, for example with a switch connected to VCC. This mode may also be used as output. Pull-up. This mode is the opposite of the Pull-down mode. In this mode, HIGH output is driven strong and LOW output is through an internal pull-down resistor of approximately 5.6K. This mode may be used as an input, for example with a switch connected to GND. When used as input, the corresponding bit in the PRTxDR register must be set to enable the pull-up resistor. Once the pull-up resistor is enabled, the state of the pin is read using the PRTxDR register. This mode may also be used as output. Strong Slow. This mode is similar to the Strong mode, but the slope of the output is slightly controlled so that high harmonics are not present when the output switches. The Interrupt field in the Pinout window sets the interrupt type of the pins. Pins may have rising edge or falling edge interrupts, or both, or neither. The Initial Value field in the Pinout window sets the initial output value of the pin at startup. This value is imposed by populating the pins data register during the execution of automatically generated boot code, and can be overridden by the user at runtime.

Figure 2. PSoC 1 Drive Modes and Simplified Equivalent Circuits

June 15, 2011

Document No. 001-40480 Rev. *D

AN2094

Code Level Configuration

Another method to configure I/O pins is to directly modify certain registers in the code using assembly or C language. This method allows you to configure I/O ports dynamically during program execution. Note If the pin configuration is fixed, then user authored code is not required to configure the pins. PSoC Designer automatically generates startup code to configure the pins according to the settings in the Device Editor. There are three registers for each port that sets the drive mode of every port pin. They are called PRTxDM0, PRTxDM1, and PRTxDM2 registers. The bits in the three registers together configure a particular pin. For example, bit0 of PRT0DM0, PRT0DM1, and PRT0DM2 controls the P0[0] drive mode. Figure 2 lists the drive modes and shows a simplified equivalent circuit. The following tables list the combination of these registers and the corresponding drive mode. Table 1. Port m Drive Mode 0 Registers (PRTxDM0)

Control Pin # Bit Name Port_x_7 DM0[7] Port_x_6 DM0[6] Port_x_5 DM0[5] Port_x_4 DM0[4] Port_x_3 DM0[3] Port_x_2 DM0[2] Port_x_1 DM0[1] Port_x_0 DM0[0]

Note Port Drive Mode 0 Registers are 8 bits wide. All bits are Read or Write.

Port 0 Drive Mode 0 Register (PRT0DM0, Address = Bank 1, 00h) Port 1 Drive Mode 0 Register (PRT1DM0, Address = Bank 1, 04h) Port 2 Drive Mode 0 Register (PRT2DM0, Address = Bank 1, 08h) Port 3 Drive Mode 0 Register (PRT3DM0, Address = Bank 1, 0Ch) Port 4 Drive Mode 0 Register (PRT4DM0, Address = Bank 1, 10h) Port 5 Drive Mode 0 Register (PRT5DM0, Address = Bank 1, 14h) Port 6 Drive Mode 0 Register (PRT5DM0, Address = Bank 1, 18h) Port 7 Drive Mode 0 Register (PRT5DM0, Address = Bank 1, 1Ch) Table 2. Port m Drive Mode 1 Registers (PRTxDM1)

Control Pin # Bit Name Port_x_7 DM1[7] Port_x_6 DM1[6] Port_x_5 DM1[5] Port_x_4 DM1[4] Port_x_3 DM1[3] Port_x_2 DM1[2] Port_x_1 DM1[1] Port_x_0 DM1[0]

Note Port Drive Mode 1 Registers are 8-bits wide. All bits are Read or Write.

Port 0 Drive Mode 1 Register (PRT0DM1, Address = Bank 1, 01h) Port 1 Drive Mode 1 Register (PRT1DM1, Address = Bank 1, 05h) Port 2 Drive Mode 1 Register (PRT2DM1, Address = Bank 1, 09h) Port 3 Drive Mode 1 Register (PRT3DM1, Address = Bank 1, 0Dh) Port 4 Drive Mode 1 Register (PRT4DM1, Address = Bank 1, 11h) Port 5 Drive Mode 1 Register (PRT5DM1, Address = Bank 1, 15h) Port 6 Drive Mode 1 Register (PRT6DM1, Address = Bank 1, 19h) Port 7 Drive Mode 1 Register (PRT7DM1, Address = Bank 1, 1Dh) Table 3. Port m Drive Mode 2 Registers (PRTxDM2)

Control Pin # Port_x_7 Port_x_6 Port_x_5 Port_x_4 Port_x_3 DM2[3] Port_x_2 DM2[2] Port_x_1 DM2[1] Port_x_0 DM2[0]

Bit Name DM2[7] DM2[6] DM2[5] DM2[4] Note Port Drive Mode 2 Registers are 8-bits wide. All bits are Read or Write.

Port 0 Drive Mode 2 Register (PRT0DM2, Address = Bank 0, 03h) Port 1 Drive Mode 2 Register (PRT1DM2, Address = Bank 0, 07h) Port 2 Drive Mode 2 Register (PRT2DM2, Address = Bank 0, 0Bh) Port 3 Drive Mode 2 Register (PRT3DM2, Address = Bank 0, 0Fh) Port 4 Drive Mode 2 Register (PRT4DM2, Address = Bank 0, 13h) Port 5 Drive Mode 2 Register (PRT5DM2, Address = Bank 0, 17h) Port 6 Drive Mode 2 Register (PRT6DM2, Address = Bank 0, 1Bh) Port 7 Drive Mode 2 Register (PRT7DM2, Address = Bank 0, 1Fh) The Port x Drive Mode 0, Port x Drive Mode 1 and Port x Drive Mode 2 registers together control the I/O configuration of pins (ports) as shown in Figure 2. DM2[0] DM1[0] DM0[0] control pin 0 of port x DM2[1] DM1[1] DM0[1] control pin 1 of port x DM2[2] DM1[2] DM0[2] control pin 2 of port x

June 15, 2011

DM2[3] DM1[3] DM0[3] control pin 3 of port x DM2[4] DM1[4] DM0[4] control pin 4 of port x DM2[5] DM1[5] DM0[5] control pin 5 of port x DM2[6] DM1[6] DM0[6] control pin 6 of port x DM2[7] DM1[7] DM0[7] control pin 7 of port x

Document No. 001-40480 Rev. *D

AN2094

For example, to configure Port_2_5 then you must write to the DM2[5], DM1[5] and DM0[5] bits of PORT 2 DRIVE MODE registers (PRT2DM2, PRT2DM1, PRT2DM0). For example, configure P2_0 to be a Strong drive. The following steps must be performed. From Figure 2 on page 3 find the DM2, DM1, DM0 values for Strong. (If you want a pin to be output, you may choose Strong. Do not choose High Z for digital outputs.) DM2 = 0 DM1 = 0 and DM0 = 1 for Strong drive. Use assembly or C instructions to set bit 5 of PRT2DM0 and clear bit 5 of PRT2DM1 and PRT2DM2 registers.

Port 6 Data Register (PRT6DR, Address = Bank 0, 18h) Port 7 Data Register (PRT7DR, Address = Bank 0, 1Ch)

To write to a particular port pin, use the corresponding mask and bitwise AND or OR operation. For example, to set and clear P3[4]:

Assembly Example

or reg[PRT3DR], 0x10 ; Set P3[4] and reg[PRT3DR], ~0x10 ; Clear P3[4]

C Example

PRT3DR |= 0x10; PRT3DR &= ~0x10; To read from a port pin, read the PRTxDR register and use the corresponding bit mask. For example, to check the status of P2[3]:

Assembly Example

M8C_SetBank1 or reg[PRT2DM0], 0x20 and reg[PRT2DM1], ~0x20 M8C_SetBank0 and reg[PRT2DM2], ~0x20 In the previous assembly example, the first line is a call to the M8C_SetBank1 macro, which switches the register bank to 1. This is done because PRT2DM0 and PRT2DM1 are in register bank 1. Then using the OR instruction and using a mask of 0x20, bit 5 of PRT2DM0 register is set. Then using AND instruction and a mask of inverse of 0x20, bit 5 of the PRT2DM1 register is cleared. Using M8C_SetBank0, it is switched back to register bank 0, and using the AND instruction and a mask of inverse of 0x20, bit 5 or the PRT2DM2 register is cleared. The OR and AND instructions are read, modify or write instructions. The content of the register is first read, a OR or AND operation is done on the value and then the result is written back to the same register. With this method, particular bits are modified without affecting the others.

Assembly Example

mov A, reg[PRT2DR] and A,0x08 jnz PinHigh ; Code to process Pin cleared state PinHigh: ; Code to process Pin set state C Example if (PRT2DR & 0x08) { // Code to process Pin Set state } Else { // Code to process Pin cleared state }

C Example

PRT2DM0 |= 0x20; PRT2DM1 &= ~0x20 PRT2DM2 &= ~0x20; In C, the code becomes much simpler. The switching of the banks is taken care of by the C compiler. The bitwise AND (&=) or the bitwise OR (|=) must be used with the corresponding masks on the registers.

Reading and Writing to a Port

After configuring I/O ports, the PORT DATA registers are used to write or read data. PORT DATA registers are 8 bits wide. The bytes show the value read from pins of a particular port or the content of these registers is written directly to the port.

Port 0 Data Register (PRT0DR, Address = Bank 0, 00h) Port 1 Data Register (PRT1DR, Address = Bank 0, 04h) Port 2 Data Register (PRT2DR, Address = Bank 0, 08h) Port 3 Data Register (PRT3DR, Address = Bank 0, 0Ch) Port 4 Data Register (PRT4DR, Address = Bank 0, 10h) Port 5 Data Register (PRT5DR, Address = Bank 0, 14h)

June 15, 2011

Document No. 001-40480 Rev. *D

AN2094

Example Projects

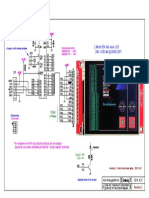

Example projects in assembly and C have been created to demonstrate the reconfiguration of pins. In this example, Port 1 is reconfigured. They are meant to be run on a CY3210-PSoC EVAL1 kit attached to a CY3215-DK PSoC1 debugger. Four LEDs are connected to Port 1 and the effects of the pin drive modes are observed by checking the status of the LEDs. The test setup is shown in Figure 3 and Figure 4. The project may be modified to operate on different hardware by changing the port registers that are modified to a different port. Figure 3. Picture of the Complete Test Setup

Figure 4. Detail of Port 1 and LED Wiring

June 15, 2011

Document No. 001-40480 Rev. *D

AN2094

Appendix A Example Code

Assembly Example Source Code

_main: ; Place a break point here nop ; Initially, the pins are configured for analog Hi-Z, and LEDs are off ; Configure the pins of Port2 to Strong drive mode ; DM2=0 DM1=0 DM0=1 M8C_SetBank1 mov reg[PRT1DM0], FFh mov reg[PRT1DM1], 00h M8C_SetBank0 mov reg[PRT1DM2], 00h ; Now we are writing FFh to the port 2 ; Write FFh to Port2. mov reg[PRT1DR], FFh nop ; Now you see that the 4 LEDs on the PSoC EVAL1 board are on ; Let us turn Off P2[7], P2[6], P2[3] and P2[2] ; For this we perform an "AND" operation with the inverse of ; the bit mask CCh and reg[PRT1DR],~CCh nop ; Now you see 0011 on the LEDs ; Let us switch off all LEDs mov reg[PRT1DR], 00h ; Let's configure pins as input! (High Z with Digital Input Enabled) ; DM2=0 DM1=1 DM0=0 M8C_SetBank1 mov reg[PRT1DM0], 00h ;Remember that DM0=0 DM1=1 for High Z. mov reg[PRT1DM1], FFh M8C_SetBank0 mov reg[PRT1DM2], 00h nop ; Now all LEDs are switched off! Because all pins are input now. ; You do not need to write data to the port again after a new configuration. ; Let's configure pins as pull-down ; DM2=0 DM1=0 DM0=0 M8C_SetBank1 mov reg[PRT1DM0], 00h ;Remember that DM0=0 DM1=0 for Pull-down. mov reg[PRT1DM1], 00h M8C_SetBank0 mov reg[PRT1DM2], 00h ; Let's write FFh to the port data registers mov reg[PRT1DR], FFh nop ; Now you see all LEDs are ON. Same with STRONG Drive. ; Let's configure pins as pull-up. M8C_SetBank1 mov reg[PRT1DM0], FFh ;Remember that DM0=1 DM1=1 for Pull-up. mov reg[PRT1DM1], FFh M8C_SetBank0 mov reg[PRT1DM2], 00h nop ; Now you see all LEDs are ON but they are not bright. ; This is because of the internal 5.6K pullup resistor. It limits the output current.

June 15, 2011

Document No. 001-40480 Rev. *D

AN2094

C Example Source Code

void main(void) { // Place a break point here asm("nop"); //Initially, all pins are high-z analog, and the LEDs are off. while(1) { // Configure the pins of Port1 to Strong drive mode // DM2=0 DM1=0 DM0=1 PRT1DM0 = 0xFF; PRT1DM1 = 0x00; PRT1DM2 = 0x00; // Let's write 0xFF to Port1 PRT1DR = 0xFF; // Place breakpoint here asm("nop"); // Now you see 4 LEDs of PSoC EVAL1 Board are ON // Let us turn Off P1[7], P1[6], P1[3] and P1[2] // For this we perform an "AND" operation with the inverse of // the bit mask 0xCC PRT1DR &= ~0xCC; // Place breakpoint here asm("nop"); // Now you see 0011 on the LEDs // Let us switch Off all LEDs PRT1DR = 0x00; // Let's configure pins as input! (High Z with Digital Input Enabled) // DM2=0 DM1=1 DM0=0 PRT1DM0 = 0x00; PRT1DM1 = 0xFF; PRT1DM2 = 0x00; // Place breakpoint here asm("nop"); // Now all LEDs are switched Off! Because all pins are input now. // You do not need to write data to the port again after a new configuration. // Let's configure pins as pull-down // DM2=0 DM1=0 DM0=0 PRT1DM0 = 0x00; PRT1DM1 = 0x00; PRT1DM2 = 0x00; // Let's write 0xFF to the port data registers PRT1DR = 0xFF; // Place breakpoint here asm("nop"); // Now you see all LEDs are ON. Same with STRONG Drive. // Let's configure pins as pull-up. PRT1DM0 = 0xFF; PRT1DM1 = 0xFF; PRT1DM2 = 0x00; // Place breakpoint here asm("nop"); // Now you see all LEDs are ON but they are not bright. // This is because of the internal 5.6K resistor. It limits the output current. } }

June 15, 2011 Document No. 001-40480 Rev. *D 7

AN2094

Document History

Document Title: PSoC 1 GPIO Pin-Port Reconfiguration Document Number: 001-40480

Revision ECN Orig. of Change Submission Date Description of Change

** *A *B *C

1532004 1778285 2188526 3181445

SFV SFV MAXK MAXK

11/13/2007 12/18/2007 06/05/2008 02/24/2011

Recatalogued application note. Associated Project files zipped with source document. Corrected Table 1. Drive Mode Configuration. (project files zipped with source files) Adapted example project to operate on CY3210-EVAL1 board. Updated firmware for PSoC Designer 5.1 SP1. General information and readability updates.

*D

3283657

MAXK

06/15/2011

Template changes. No Technical updates. Document title updated.

In March of 2007, Cypress recataloged all of its Application Notes using a new documentation number and revision code. This new documentation number and revision code (001-xxxxx, beginning with rev. **), located in the footer of the document, will be used in all subsequent revisions. PSoC is a registered trademark of Cypress Semiconductor Corp. "Programmable System-on-Chip," PSoC Designer and PSoC Express are trademarks of Cypress Semiconductor Corp. All other trademarks or registered trademarks referenced herein are the property of their respective owners.

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709 Phone: 408-943-2600 Fax: 408-943-4730 http://www.cypress.com/ Cypress Semiconductor Corporation, 2003-2011. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges. This Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress. Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges. Use may be limited by and subject to the applicable Cypress software license agreement.

June 15, 2011

Document No. 001-40480 Rev. *D

You might also like

- CJ840 - Bosch SemiconductorsDocument5 pagesCJ840 - Bosch SemiconductorsMohammed MochrifNo ratings yet

- Using The HITECH C Compiler With FlowcodeDocument3 pagesUsing The HITECH C Compiler With FlowcodeleonewbNo ratings yet

- LED Running Lights ExperimentDocument9 pagesLED Running Lights ExperimentElimar C JaymeNo ratings yet

- Philips A7h.1 Quadriga ChassisDocument40 pagesPhilips A7h.1 Quadriga ChassisToth VasileNo ratings yet

- Programming A Cypress PSoC Using PSoC DesignerDocument12 pagesProgramming A Cypress PSoC Using PSoC DesignerThanhha NguyenNo ratings yet

- Philips 8051Document114 pagesPhilips 8051bhavyashankerNo ratings yet

- PIC Timer 0 Calculation ExampleDocument3 pagesPIC Timer 0 Calculation Examplef.last100% (1)

- Debounce PDFDocument11 pagesDebounce PDFEmanuel CrespoNo ratings yet

- PIC TutorialDocument203 pagesPIC TutorialUnwana James0% (1)

- SPI ProtocolDocument2 pagesSPI ProtocolMohanNo ratings yet

- TMS320F2812-Serial Communication InterfaceDocument28 pagesTMS320F2812-Serial Communication InterfacePantech ProLabs India Pvt Ltd75% (4)

- Ejemplos Pic 16f887 PBPDocument13 pagesEjemplos Pic 16f887 PBPleo2tvNo ratings yet

- Digital Temperature Meter Using PIC16F688Document3 pagesDigital Temperature Meter Using PIC16F688Bhuvaneswaran VutwobwnNo ratings yet

- 8086 Interfacing-Chap 5Document36 pages8086 Interfacing-Chap 5Krishnaveni DhulipalaNo ratings yet

- ILI9341 2R8 240x320 Cir ENDocument1 pageILI9341 2R8 240x320 Cir ENBeenish MirzaNo ratings yet

- RC5 Protocol Decoding With 8051 Microcontroller (Embedded C) - ProEmbSys TechnologiesDocument4 pagesRC5 Protocol Decoding With 8051 Microcontroller (Embedded C) - ProEmbSys TechnologieskhhoaNo ratings yet

- UT61D Computer Interface SoftwareDocument7 pagesUT61D Computer Interface Softwaredaniel villaNo ratings yet

- Dell Inspiron n5110 m5110 Dq15 Wistron Queen 15 Intel Discrete Uma Sandy Bridge Rev A00 SCHDocument108 pagesDell Inspiron n5110 m5110 Dq15 Wistron Queen 15 Intel Discrete Uma Sandy Bridge Rev A00 SCHMaula HassanNo ratings yet

- 8257 DmaDocument6 pages8257 DmaAdarsh AmzeNo ratings yet

- Study of Arm Evaluation System-Lpc2148Document6 pagesStudy of Arm Evaluation System-Lpc2148Thenmozhi Selvaraj100% (1)

- 25.ACCESSIBLE DISPLAY DESIGN TO CONTROL HOME AREA NETWORKSDocumentDocument84 pages25.ACCESSIBLE DISPLAY DESIGN TO CONTROL HOME AREA NETWORKSDocumentdileeppatraNo ratings yet

- Metrodyne Microsystem Corp: MPS-2100 SeriesDocument3 pagesMetrodyne Microsystem Corp: MPS-2100 SeriesAhmed ShadeedNo ratings yet

- 8051 Asembler I C Programiranje PDFDocument150 pages8051 Asembler I C Programiranje PDFVladimir SimićNo ratings yet

- LPC17xx ARM Cortex M3 Assembly Language ExampleDocument11 pagesLPC17xx ARM Cortex M3 Assembly Language ExampleDaniel Ramos50% (2)

- AVR Programming Logical Operations PDFDocument125 pagesAVR Programming Logical Operations PDFNivaldoSilva50% (2)

- ARM Cortex M3 Based Collision Detection SystemDocument3 pagesARM Cortex M3 Based Collision Detection SystemseventhsensegroupNo ratings yet

- Blinking of Led Using C Using Parallel PortDocument8 pagesBlinking of Led Using C Using Parallel Portsandipnair06No ratings yet

- CNC Milling (Arabic Book)Document146 pagesCNC Milling (Arabic Book)Mohamed WahidNo ratings yet

- 8279 Keyboard and Display ControllerDocument33 pages8279 Keyboard and Display Controllergutzz0079197100% (1)

- RT809H FLASH Programmer: User ManualDocument76 pagesRT809H FLASH Programmer: User Manualvw5wbv6c5mNo ratings yet

- 89s52 Microcontroller TutorialDocument30 pages89s52 Microcontroller Tutorialm_adavoodi6479No ratings yet

- Mplab IDE TutorialDocument12 pagesMplab IDE Tutorialahsoopk100% (1)

- War Field Spying Robot With Night Vision Wireless Camera by Android ApplicationsDocument32 pagesWar Field Spying Robot With Night Vision Wireless Camera by Android ApplicationsharshithaNo ratings yet

- User Guide For 8051 Development BoardDocument3 pagesUser Guide For 8051 Development Boardsopath3ticNo ratings yet

- Easyavr v7 Manual v101-238271Document33 pagesEasyavr v7 Manual v101-238271Luis TavisNo ratings yet

- Electronic Devices and Circuits (EME-306) Lab 1: ObjectiveDocument7 pagesElectronic Devices and Circuits (EME-306) Lab 1: ObjectiveAhmed SayedNo ratings yet

- Unit 5 - A CASE STUDY - Using Pic MicrocontrollerDocument33 pagesUnit 5 - A CASE STUDY - Using Pic MicrocontrollerPoonthalirNo ratings yet

- Lab9 ReportDocument4 pagesLab9 ReportASAD REHANNo ratings yet

- Lab 1 - OLED, GPIO, InterruptDocument6 pagesLab 1 - OLED, GPIO, Interruptprakash_shrNo ratings yet

- Design and Implementation of VGA Controller On FPGADocument8 pagesDesign and Implementation of VGA Controller On FPGAVenkatGollaNo ratings yet

- Schematic TV LG CT 29q91rbDocument36 pagesSchematic TV LG CT 29q91rbhuudung100% (8)

- CPU921-922 6ES5998-0UL22 (E) OCRDocument548 pagesCPU921-922 6ES5998-0UL22 (E) OCRnasir_khan_24No ratings yet

- CAN Bus in PSoC Report210Document16 pagesCAN Bus in PSoC Report210Marcos Antonio EstremoteNo ratings yet

- PacketFront DRG 580 DatasheetDocument2 pagesPacketFront DRG 580 DatasheetClayton MartinezNo ratings yet

- Creating Programs S2000Document3 pagesCreating Programs S2000EwanColsell100% (1)

- 16 Channel Rail RS485 Relay ManualDocument7 pages16 Channel Rail RS485 Relay Manualfenix12330% (1)

- Microcontroller Based Digital Code Lock: Submitted By: C. Theja DeepakDocument31 pagesMicrocontroller Based Digital Code Lock: Submitted By: C. Theja DeepakDeepak Tej100% (3)

- Interfacing P10 LED Display With ArduinoDocument8 pagesInterfacing P10 LED Display With ArduinoRaju D PuthusserryNo ratings yet

- LCDWIKI KBV Lib ManualDocument12 pagesLCDWIKI KBV Lib ManualMosFet Elektronik AlaattinNo ratings yet

- Renesas Flash Programmer Sample Circuit For Programming PC Serial PDFDocument5 pagesRenesas Flash Programmer Sample Circuit For Programming PC Serial PDFAjay J VermaNo ratings yet

- CP1H Easy Modbus Master Section of Top Gun 2006 Training PDFDocument19 pagesCP1H Easy Modbus Master Section of Top Gun 2006 Training PDFTito Rano PradibtoNo ratings yet

- Connection & Operation of RS-232 Option For BF250 Mark 8 ControlDocument17 pagesConnection & Operation of RS-232 Option For BF250 Mark 8 Controlnigh_tmareNo ratings yet

- PIC Microcontroller Hello World, PIC16F1823Document1 pagePIC Microcontroller Hello World, PIC16F1823Nolan Manteufel100% (3)

- Lecture 5 Communicating With Peripherals 2021Document44 pagesLecture 5 Communicating With Peripherals 2021Pavan DhakeNo ratings yet

- TC358774XBG 75XBG V1.7Document158 pagesTC358774XBG 75XBG V1.7Manjunath100% (1)

- Up CX 530 EnglishDocument8 pagesUp CX 530 EnglishuongquocvuNo ratings yet

- 16-B D S P A/D C: FeaturesDocument60 pages16-B D S P A/D C: FeatureskrajasekarantutiNo ratings yet

- Programmable Peripheral Interface 8255: Specworld - inDocument27 pagesProgrammable Peripheral Interface 8255: Specworld - inSachinAggarwalNo ratings yet

- MSP430 Programming Reference r3-1 PDFDocument77 pagesMSP430 Programming Reference r3-1 PDFDaneangelaKNo ratings yet

- Mpmcnotesunit IIIDocument34 pagesMpmcnotesunit IIIAmy OliverNo ratings yet

- TRISC 0 // Set Direction To Be Output 0 Output 1 InputDocument7 pagesTRISC 0 // Set Direction To Be Output 0 Output 1 Inputiri_scribdNo ratings yet

- ECE371 Lab1Report Group2Document9 pagesECE371 Lab1Report Group2Le HieuNo ratings yet

- Preparation of P-Type Na-Doped Cu2O by Electrodeposition For A P-N Homojunction Thin Film Solar CellDocument9 pagesPreparation of P-Type Na-Doped Cu2O by Electrodeposition For A P-N Homojunction Thin Film Solar CellLoubna MentarNo ratings yet

- Laser Beams Theory Properties and Applications PDFDocument547 pagesLaser Beams Theory Properties and Applications PDFdada12100% (1)

- Magnetic Properties and ParamagnetismDocument20 pagesMagnetic Properties and Paramagnetismnkar0370% (1)

- Veic PCB Layout Tutorial 010709Document52 pagesVeic PCB Layout Tutorial 010709Hüseyin AgaNo ratings yet

- Power ConvertersDocument2 pagesPower Converterssrikanth kallemNo ratings yet

- Insulation Resistance Testing Guide ENGDocument28 pagesInsulation Resistance Testing Guide ENGRahul More100% (1)

- 2023 - MDPI - Laser Scribing of Photovoltaic Solar Thin Films - A ReviewDocument26 pages2023 - MDPI - Laser Scribing of Photovoltaic Solar Thin Films - A ReviewP SamuelNo ratings yet

- Commutation Techniques of SCR PDFDocument2 pagesCommutation Techniques of SCR PDFLeasaNo ratings yet

- Pickit Linux Manual UbuntuDocument17 pagesPickit Linux Manual Ubuntukz300No ratings yet

- Relays and TimersDocument133 pagesRelays and Timerskarstegg100% (1)

- Embedded Systems LecturesDocument58 pagesEmbedded Systems Lecturesahmdaldys2No ratings yet

- PriceDocument4 pagesPriceCikgu CikguNo ratings yet

- 01051759Document5 pages01051759Aarif MalikNo ratings yet

- Ec 1Document20 pagesEc 1helenseelanNo ratings yet

- Scrolling Message Display - Project Report - Nov 15, 2011Document71 pagesScrolling Message Display - Project Report - Nov 15, 2011Arun Arya33% (3)

- TRL27 Installation Instructions - IL04910003EDocument2 pagesTRL27 Installation Instructions - IL04910003Ericardo_ro_4No ratings yet

- SilDocument3 pagesSilSandipNanawareNo ratings yet

- 4 5780930464638307470 PDFDocument41 pages4 5780930464638307470 PDFYihun DesalegnNo ratings yet

- Zapi H2 Traction ControllerDocument5 pagesZapi H2 Traction ControllerHartanto DwiNo ratings yet

- 12 Bitcoin Win ScriptDocument42 pages12 Bitcoin Win Scriptfrank rialNo ratings yet

- Origami RobotsDocument10 pagesOrigami RobotsMidhun LNo ratings yet

- TKR750Document69 pagesTKR750Vicente Espinoza VillarrealNo ratings yet

- Car Parking SensorDocument39 pagesCar Parking SensorSubarna Poddar100% (10)

- R1Z6 Datasheet JDL BAB 50 23 905 TE 200 4.0Document2 pagesR1Z6 Datasheet JDL BAB 50 23 905 TE 200 4.0Galin GospodinovNo ratings yet

- Reliable Performance For Standard Industrial Environments.: Cylindrical Proximity SensorDocument20 pagesReliable Performance For Standard Industrial Environments.: Cylindrical Proximity SensorLucas Vinícius CostaNo ratings yet

- DC DC Design GuideDocument23 pagesDC DC Design Guidehammouche_soufianeNo ratings yet

- Structure of Welded Joint and Cracking Phenomena in Steel WeldDocument27 pagesStructure of Welded Joint and Cracking Phenomena in Steel WeldaunginternetNo ratings yet