0 ratings0% found this document useful (0 votes)

45 viewsDLC Model I

DLC Model I

Uploaded by

EEE DEPTThis document contains exam questions for a Digital Logic Circuits course. It is divided into three parts:

Part A contains 10 multiple choice questions worth 2 marks each, covering topics like fan in/fan out, number systems, logic gate types, shift registers, hazards, PROM, and VHDL.

Part B contains 5 questions worth 5-13 marks each, involving binary to gray code conversion, TTL NAND gate operation, full adder/subtractor design, demultiplexer design, JK flip-flop explanation, shift register types, PLA design, and asynchronous circuit design.

Part C contains 2 questions worth 15 marks each, about hazards in sequential circuits and 8 to 1 multiple

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

DLC Model I

DLC Model I

Uploaded by

EEE DEPT0 ratings0% found this document useful (0 votes)

45 views2 pagesThis document contains exam questions for a Digital Logic Circuits course. It is divided into three parts:

Part A contains 10 multiple choice questions worth 2 marks each, covering topics like fan in/fan out, number systems, logic gate types, shift registers, hazards, PROM, and VHDL.

Part B contains 5 questions worth 5-13 marks each, involving binary to gray code conversion, TTL NAND gate operation, full adder/subtractor design, demultiplexer design, JK flip-flop explanation, shift register types, PLA design, and asynchronous circuit design.

Part C contains 2 questions worth 15 marks each, about hazards in sequential circuits and 8 to 1 multiple

Original Title

dlc model i

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

This document contains exam questions for a Digital Logic Circuits course. It is divided into three parts:

Part A contains 10 multiple choice questions worth 2 marks each, covering topics like fan in/fan out, number systems, logic gate types, shift registers, hazards, PROM, and VHDL.

Part B contains 5 questions worth 5-13 marks each, involving binary to gray code conversion, TTL NAND gate operation, full adder/subtractor design, demultiplexer design, JK flip-flop explanation, shift register types, PLA design, and asynchronous circuit design.

Part C contains 2 questions worth 15 marks each, about hazards in sequential circuits and 8 to 1 multiple

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

0 ratings0% found this document useful (0 votes)

45 views2 pagesDLC Model I

DLC Model I

Uploaded by

EEE DEPTThis document contains exam questions for a Digital Logic Circuits course. It is divided into three parts:

Part A contains 10 multiple choice questions worth 2 marks each, covering topics like fan in/fan out, number systems, logic gate types, shift registers, hazards, PROM, and VHDL.

Part B contains 5 questions worth 5-13 marks each, involving binary to gray code conversion, TTL NAND gate operation, full adder/subtractor design, demultiplexer design, JK flip-flop explanation, shift register types, PLA design, and asynchronous circuit design.

Part C contains 2 questions worth 15 marks each, about hazards in sequential circuits and 8 to 1 multiple

Copyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

Download as docx, pdf, or txt

You are on page 1of 2

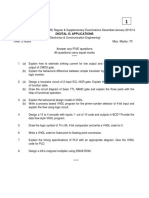

Reg No :

6214-MAHABARATHI ENGINEERING COLLEGE - CHINNASALEM

B.E./B.Tech. DEGREE EXAMINATION, OCT-2021

Third Semester / Electrical and Electronics Engineering

EE-8351 DIGITAL LOGIC CIRCUITS

(Regulation 2017)

Model EXAM -1

DATE: 15.11.2021(AN) Maximum Marks:100

TIME: 3.00 Hours

Answer ALL Questions

PART A — (10 × 2 = 20 Marks)

1. Define Fan in and Fan out.

2. Convert (19.625)10 to Binary,Octal and Hexadecimal Number System.

3. Define min term and max term.

4. Differentiate decoder and demultiplexer.

5. Give the design steps for synchronous sequential circuit.

6. What are the types of Shift Registers?

7. Define hazards and its types.

8. Define PROM.

9. What is VHDL.

10. Write the program for half adder using in VHDL.

PART-B (13*5=65 Marks)

11. a)i)Explain about binary to gray code conversion. (06)

ii)Explain the operation of TTL NAND gate with a neat circuit diagram. (07)

(OR)

b) Name and Briefly Explain About Characteristics Of Digital IC’s. (13)

12.a) Design and implement the full adder and full subtractor circuit using only NAND Gates.

(OR)

b) Design and implement 1 to 8 demultiplexer using AND Gates. (13)

13.a) With neat digram .explain about JK flip-flop. (13)

(OR)

b)Explain about different types of shift registers. (13)

14.a)Draw the block diagram of a PLA device and briefly explain each block. . (13)

(OR)

b).summarize the design procedure for asynchronous sequential circuit. (13)

15.a)Explain the structure and working principles of TTL based Totem-pole output

configuration. (13)

(OR)

b) Write a VHDL code to realize a half adder using behavioral modeling and structural modeling

(13)

PART-C (15*1=15 Marks)

16. a)Illustrate about hazards in sequential circuits and the steps to avoid hazards in it. (15)

(OR)

b) Design and implement 8 to 1 multiplexer using AND Gates (15)

Reg No :

6214-MAHABARATHI ENGINEERING COLLEGE - CHINNASALEM

B.E./B.Tech. DEGREE EXAMINATION, OCT-2021

Third Semester

Electrical and Electronics Engineering

EE-8351 DIGITAL LOGIC CIRCUITS

(Regulation 2017)

Common Internal Assessment Test-I

DATE: 22 .10.2021(AN) Maximum Marks: 50

TIME: 1.30 Hours

Answer ALL Questions

PART A — (09 × 2 = 18 Marks)

1. List out the Numbering System.

2. Convert (19.625)10 to Binary,Octal and Hexadecimal Number System.

3. Convert (3A.2F)16 to Decimal,Binary and Octal Number System.

4. Convert (1100.1011)2 to Decimal, Hexadecimal and Octal Number System.

5. How you will represent signed binary numbers in computers?

6. Give A=1010 B=1111 perform (a)A-B (b)B-A using 1’s complement.

7. Using 2’s Complement Perform (42)10 – (68)10.

8. Define Fan in and Fan out.

9. Define Noise Margin Noise Immunity.

PART-B (10*2=20 Marks)

10. a) Explain About Different Types Of Logic Gates. (10)

(OR)

b) Briefly Explain About Characteristics Of Digital IC’s. (10)

11.a) Briefly Explain About Different Types Of Bipolar Logic Families. (10)

(OR)

b) Briefly Explain About Different Types Of Mos Families.(10)

PART-C (12*1=12 Marks)

12. Explain About Different Types Of Numbering System. Give Example For Each. (12)

You might also like

- VOX AC30CC Mod SchematicDocument1 pageVOX AC30CC Mod Schematicapi-3731627No ratings yet

- Radar Radar: Introduction and BasicsDocument37 pagesRadar Radar: Introduction and BasicsShreyas S RNo ratings yet

- University Question Papers - VLSIDocument26 pagesUniversity Question Papers - VLSIVijayNo ratings yet

- Question Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodeDocument2 pagesQuestion Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodePrabu KumarNo ratings yet

- Nov - Dec 2021Document3 pagesNov - Dec 2021Pandyselvi BalasubramanianNo ratings yet

- QP DLCDocument2 pagesQP DLCDivya PriyaNo ratings yet

- DF - Question BankDocument6 pagesDF - Question Bankjignasha.patelNo ratings yet

- QBank DPSD cs2202Document6 pagesQBank DPSD cs2202kunarajNo ratings yet

- De Model Exam SET 1 & 2Document2 pagesDe Model Exam SET 1 & 2menaka53No ratings yet

- Mr3492 Esp Model QN PaperDocument3 pagesMr3492 Esp Model QN PaperKeerthana SahadevanNo ratings yet

- Vlsi QP 21,22Document11 pagesVlsi QP 21,22Arunitha ArulnathanNo ratings yet

- Vlsi Ques 66Document3 pagesVlsi Ques 66michalNo ratings yet

- B Tech. Degree Examination, November 20: Answer Al Questions. Uest On Arr Es 3 MarksDocument2 pagesB Tech. Degree Examination, November 20: Answer Al Questions. Uest On Arr Es 3 MarksVargheseMartinNo ratings yet

- EC2354 - VLSI DesignDocument2 pagesEC2354 - VLSI DesignSriramNo ratings yet

- ec6801 qp2Document2 pagesec6801 qp2ECE JPRNo ratings yet

- Seca1508 Nov 22Document2 pagesSeca1508 Nov 22sharichandran86No ratings yet

- 9A04504 Digital IC Applications6Document4 pages9A04504 Digital IC Applications6subbuNo ratings yet

- Bharath Niketan Engineering College: HoursDocument2 pagesBharath Niketan Engineering College: HourseeeNo ratings yet

- Model Question Paper - ECT203Document3 pagesModel Question Paper - ECT203mohdhasikvNo ratings yet

- Digital ElectronicsDocument7 pagesDigital ElectronicsAlakaaa PromodNo ratings yet

- Question Paper Code: X10348: Reg. NoDocument2 pagesQuestion Paper Code: X10348: Reg. NoJaikumar RajendranNo ratings yet

- MechatronicsDocument2 pagesMechatronicsSaravanan MathiNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)kenny kannaNo ratings yet

- DSP Integrated Circuits 3Document3 pagesDSP Integrated Circuits 3brindkowsiNo ratings yet

- EE3302-DLC MODEL QP UpdatedDocument3 pagesEE3302-DLC MODEL QP UpdatedKeerthana SahadevanNo ratings yet

- Deco QB 23-24 MainDocument9 pagesDeco QB 23-24 Mainsyedizaan9876No ratings yet

- B.E Degree Model Examinations-November 2024: Fifth Semester Computer Science and EngineeringDocument2 pagesB.E Degree Model Examinations-November 2024: Fifth Semester Computer Science and EngineeringmancymithinNo ratings yet

- EC2354 - Nov 2011 - AU QP Anna University Exams - VLSIDocument3 pagesEC2354 - Nov 2011 - AU QP Anna University Exams - VLSISHARANYANo ratings yet

- FPGA Based System DesignDocument2 pagesFPGA Based System Designammayi9845_930467904No ratings yet

- DPSDDocument24 pagesDPSDdigital1206No ratings yet

- Ec 1401 Vlsi DesignDocument2 pagesEc 1401 Vlsi DesignsubhazNo ratings yet

- Question Paper CodeDocument2 pagesQuestion Paper CodeDinesh SrinivasanNo ratings yet

- S 24Document3 pagesS 24santoshvane80No ratings yet

- Question Paper Code:: (10×2 20 Marks)Document3 pagesQuestion Paper Code:: (10×2 20 Marks)rajkumarsac100% (2)

- r05310402 Digital Ic ApplicationsDocument6 pagesr05310402 Digital Ic ApplicationsSrinivasa Rao G100% (7)

- Question Paper Code:: (10 2 20 Marks)Document2 pagesQuestion Paper Code:: (10 2 20 Marks)AbdulAzizNo ratings yet

- Civil-Nd-2021-Ge 6252-Basic Electrical and Electronics Engineering-513782540-70647 (Ge6252-Ptge6252)Document3 pagesCivil-Nd-2021-Ge 6252-Basic Electrical and Electronics Engineering-513782540-70647 (Ge6252-Ptge6252)Karthiga KSNo ratings yet

- Stucor QP Ee8551Document8 pagesStucor QP Ee8551NagendranNo ratings yet

- 2020Document7 pages2020Sanjida RahmanNo ratings yet

- Erts - Model 1Document3 pagesErts - Model 1Ece DeptNo ratings yet

- Answer All Questions PART A - (5 2 10)Document3 pagesAnswer All Questions PART A - (5 2 10)Anonymous NV7nnJDeNo ratings yet

- 6C0065Document4 pages6C0065Joshua prabuNo ratings yet

- LCDPYQSDocument8 pagesLCDPYQSsreehari14shrNo ratings yet

- Nov 2019Document6 pagesNov 2019ponniNo ratings yet

- EEE 2102 DIGITAL ELECTRONICS IDocument2 pagesEEE 2102 DIGITAL ELECTRONICS ISylvester WasongaNo ratings yet

- Smart Materials, Sensors and ActuatorsDocument2 pagesSmart Materials, Sensors and ActuatorsmanojNo ratings yet

- 6-Apply Basic Electronic SkillsDocument5 pages6-Apply Basic Electronic Skillsjackhacktivist17No ratings yet

- 2EC6302-Digital Electronics QBDocument12 pages2EC6302-Digital Electronics QBSurendar PNo ratings yet

- Copy of 20pespc103 Design of Embedded SystemsDocument2 pagesCopy of 20pespc103 Design of Embedded SystemsulaganathanNo ratings yet

- Stucor Qp-Me8791Document6 pagesStucor Qp-Me8791sramalingam288953No ratings yet

- 22323-2019-Winter-Question-Paper (Msbte Study Resources)Document3 pages22323-2019-Winter-Question-Paper (Msbte Study Resources)Parth patkarNo ratings yet

- Digital Nov 07Document6 pagesDigital Nov 07skssushNo ratings yet

- JanuaryFebruary 2021Document1 pageJanuaryFebruary 2021vishwatejkachu944No ratings yet

- Vlsi Model 4-QPDocument2 pagesVlsi Model 4-QPsanthoshNo ratings yet

- 2008 Anna UniversityDocument1 page2008 Anna UniversitysasitsnNo ratings yet

- Em - Unit 1-A (1) NewDocument2 pagesEm - Unit 1-A (1) NewdeepakNo ratings yet

- PUT Sol MergedDocument12 pagesPUT Sol Mergedharshsingh87408No ratings yet

- Computer Architecture Question BankDocument10 pagesComputer Architecture Question BankMalk Malik0% (1)

- DLC Series IaDocument1 pageDLC Series IaAnusha NatarajanNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNo ratings yet

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionFrom EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionNo ratings yet

- Polarity Test of TransformerDocument4 pagesPolarity Test of TransformerBhatia AdvancedNo ratings yet

- LFR Tutorial CompleteDocument22 pagesLFR Tutorial CompleteTraic Club0% (1)

- Giraffe Infant Scale: Service ManualDocument40 pagesGiraffe Infant Scale: Service ManualjonathanNo ratings yet

- Home Made Metal DetectorDocument9 pagesHome Made Metal DetectorDeep PatelNo ratings yet

- Micro Controller M 8051Document95 pagesMicro Controller M 8051Jyothish A GhoshNo ratings yet

- LintDocument13 pagesLintKingston 546No ratings yet

- Advanced Vehicle Security System: Key To The Programmable WorldDocument40 pagesAdvanced Vehicle Security System: Key To The Programmable WorldTajinder SinghNo ratings yet

- Water Level IndicatorDocument10 pagesWater Level IndicatorMansab Ali100% (1)

- 2sc6011 Ds enDocument7 pages2sc6011 Ds enCah YonoNo ratings yet

- Silicon NPN Power Transistor: DescriptionDocument2 pagesSilicon NPN Power Transistor: DescriptionBarry LeppanNo ratings yet

- Stepper Motor Driver MC3479: ON SemiconductorDocument12 pagesStepper Motor Driver MC3479: ON SemiconductornudufoqiNo ratings yet

- S35 DatasheetDocument2 pagesS35 Datasheetdiegol0083No ratings yet

- Chapter 11 Wiring/Circuit DiagramsDocument29 pagesChapter 11 Wiring/Circuit Diagramsminoltaep4050No ratings yet

- syllabus_2025Document1 pagesyllabus_2025bhandaridhruvin7No ratings yet

- Shatterpro Sensor Ds PDFDocument2 pagesShatterpro Sensor Ds PDFOmar Andres Novoa MartinezNo ratings yet

- EE 302 Exam 2 and Histogram F11Document3 pagesEE 302 Exam 2 and Histogram F11Perry_Feng_44440% (1)

- Expt1 - HWR and FWRDocument10 pagesExpt1 - HWR and FWRMaheswariRVNo ratings yet

- Znc401unmeac PDFDocument8 pagesZnc401unmeac PDFKp NairNo ratings yet

- Generation of Computer ': Rajiv Academy For Technology and Management, Mathura ONDocument26 pagesGeneration of Computer ': Rajiv Academy For Technology and Management, Mathura ONsouarvNo ratings yet

- Low Power Design MethodologyDocument3 pagesLow Power Design Methodologychiranjeevi muppalaNo ratings yet

- Deliver Data at The Speed of Now: Micron 9200 Nvme SSDDocument2 pagesDeliver Data at The Speed of Now: Micron 9200 Nvme SSDEmilyNo ratings yet

- Comba Anten TipleriDocument139 pagesComba Anten TiplerisaffetgulnarNo ratings yet

- ASUS Product GuideDocument35 pagesASUS Product GuideAgung Khairul Muttaqien100% (1)

- Triple Broadband AntennaDocument2 pagesTriple Broadband AntennaMaksim PatrushevNo ratings yet

- PIC16 (L) F18455/56: 28-Pin Full-Featured, Low Pin Count Microcontrollers With XLPDocument706 pagesPIC16 (L) F18455/56: 28-Pin Full-Featured, Low Pin Count Microcontrollers With XLPLab TyrcoNo ratings yet

- Ac To DC ConverterDocument24 pagesAc To DC ConverterABHISHEK KUMARNo ratings yet

- EEE419 QuizDocument2 pagesEEE419 Quizsusmoy.kundu.infoNo ratings yet

- WB WB WB WBD D D D1 1 1 130 30 30 300 0 0 03 3 3 3D D D D: Highvoltagefast-SwitchingnpnpowertransistorDocument5 pagesWB WB WB WBD D D D1 1 1 130 30 30 300 0 0 03 3 3 3D D D D: Highvoltagefast-SwitchingnpnpowertransistorAkmal FirdausNo ratings yet