Model1 COA 2022

Model1 COA 2022

Uploaded by

Hritik KaulCopyright:

Available Formats

Model1 COA 2022

Model1 COA 2022

Uploaded by

Hritik KaulOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Model1 COA 2022

Model1 COA 2022

Uploaded by

Hritik KaulCopyright:

Available Formats

(Page 1 of 2)

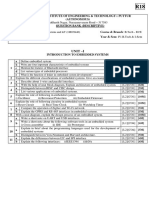

USN 21CST304

Dr. Ambedkar Institute of Technology, Bangalore

B. E. Third Semester End Examination

Model Paper - 1

Computer Organization and Architecture

[Time: 3 Hours ] [ Maximum Marks: 100]

Note: 1. Answer ANY FIVE fully Question.

Marks CO RBT

Level

1.a) Describe the basic functional units of a computer with a neat [10Marks] CO1 L1

diagram.

b) What is a bus? Explain single bus structruced in a computer. [04Marks] CO1 L2

c) Explain the following: [06Marks] CO1 L2

Byte addressability

Big-endian assignment

Little-endian

OR

2.a) What is an addressing mode? Explain different addressing [10Marks] CO1 L1

modes.

b) Register R1, R2, R3 of a processor contain the decimal value [10Marks] CO1 L2

1250, 5500 and 25. Determine the values of the registers after

each instruction is executed.

a) Load R3, (R2)

b) Move #0250,R5

c) Store R5,20(R1,R2)

d) Add (R2)+,R5

e) Add –(R2),R1

3.a) Differentiate between subroutine and interrupt service routine [06Marks] CO2 L2

b) Discuss Interrupt I/O method for data transfer. [06Marks] CO2 L2

c) Write a note on bus arbitration. [08Marks] CO2 L3

OR

4.a) Explain a synchronous bus. Also give the timing diagram of an [06Marks] CO2 L2

input transfer on s synchronous bus.

b) Define the following: [06Marks] CO2 L2

a) Burst Mode.

b) Handshaking Mechanism.

c) What is bus arbitration? Explain the centralized arbitration with [06Marks] CO2 L2

a neat diagram.

5.a) Explain the Read/Write operation of an SRAM cell designed [08Marks] CO3 L2

using CMOS, with the help of a neat diagram.

b) Discuss the organization of 1K × 1 memory chip. [08Marks] CO3 L1

c) Write briefly about Read-only memory. [04Marks] CO3 L1

OR

6.a) [08Marks] CO3 L2

b) [10Marks] CO3 L2

Dr. Ambedkar Institute of Technology, Bangalore – 560056

(Autonomous Institution Affiliated to Visvesveraya Technological University, Belgaum)

(Page 2 of 2)

c) [02Marks] CO3 L2

7.a) What general roles are performed by processor registers? [06Marks] CO4 L2

b) List and briefly explain various ways in which an instruction [08Marks] CO4 L2

pipeline can deal with conditional branch instructions.

c) What are some typical distinguishing characteristics of RISC [08Marks] CO4 L2

organization.

OR

8.a) What are the tasks that a processor must accomplish? [05Marks] CO4 L2

b) Describe the registers that are essential to instruction execution. [08Marks] CO4 L2

c) Describe the common fields or flags included in the program [07Marks] CO4 L1

status word (PSW)

9.a) Define the term superscalar. How is the superscalar organization [10Marks] CO5 L1

different from the traditional scalar organization?

b) Briefly define the following term: [10Marks] CO5 L1

i)True data dependency ii) Procedure dependency iii) Resource

conflicts iv) output dependency v) Antidependency

OR

10. List and briefly define the four categories of computer systems [08Marks] CO5 L1

a) proposed by Fynn.

b) What are the chief characteristics of an SMP [05Marks] CO5 L2

c) What are some of the key benefit of clustering? [05Marks] CO5 L2

d) List out the four states in MESI protocol. [02Marks] CO5 L1

Dr. Ambedkar Institute of Technology, Bangalore – 560056

(Autonomous Institution Affiliated to Visvesveraya Technological University, Belgaum)

You might also like

- Chapter6 AnsDocument8 pagesChapter6 Ansdaria77No ratings yet

- Model2 COA 2022Document2 pagesModel2 COA 2022Hritik KaulNo ratings yet

- 21EIT403 - Model QP - 1Document2 pages21EIT403 - Model QP - 1Adithya A RNo ratings yet

- 23MET14DDocument2 pages23MET14Dajmotors28No ratings yet

- Vlsi QBDocument5 pagesVlsi QBManaswiNo ratings yet

- 21EIT403 - Model QP - 2Document2 pages21EIT403 - Model QP - 2Adithya A RNo ratings yet

- MSD Model Latest For 2020 (1) MMN 2023Document2 pagesMSD Model Latest For 2020 (1) MMN 2023srujangowdasj2002No ratings yet

- Me 8073 - Unconventional Machining Processes: Kothandaraman Nagar, Dindigul - 624 622Document2 pagesMe 8073 - Unconventional Machining Processes: Kothandaraman Nagar, Dindigul - 624 622balajimeieNo ratings yet

- CCN MQPDocument3 pagesCCN MQPraomanusha3No ratings yet

- Introduction To Programming (23CS0501) Question Bank1Document5 pagesIntroduction To Programming (23CS0501) Question Bank1thizbrownboii7No ratings yet

- Os - Set 2Document2 pagesOs - Set 2saraswathiNo ratings yet

- Sathish S 18me731 2023 24 Cim Model 1Document3 pagesSathish S 18me731 2023 24 Cim Model 1srujangowdasj2002No ratings yet

- CO MP CS45O JUNE 2020Document2 pagesCO MP CS45O JUNE 2020shrinidhipawar09No ratings yet

- R23 CMSICD Model Question Paper SET 1Document2 pagesR23 CMSICD Model Question Paper SET 1gopikrishnaraoNo ratings yet

- IoT ELE Model Question Paper 3Document2 pagesIoT ELE Model Question Paper 3SobjianNo ratings yet

- 23mca2co1 Os MQPDocument2 pages23mca2co1 Os MQPyuktakusanale2002No ratings yet

- 16EC423-Microprocessors & MicrocontrollersDocument3 pages16EC423-Microprocessors & MicrocontrollersThiruvenkadam KNo ratings yet

- A18-AC - (EEE, ECE & ECM) - 25-08-2021 - (Regular)Document1 pageA18-AC - (EEE, ECE & ECM) - 25-08-2021 - (Regular)BATHULA BALAKRISHNANo ratings yet

- Internal Test Question Paper format-CBCS Scheme: SjcitDocument2 pagesInternal Test Question Paper format-CBCS Scheme: SjcitRoopa GururajNo ratings yet

- 16792161294operating SystemsDocument1 page16792161294operating Systemsmynameisluka501No ratings yet

- Coa Cie 1Document1 pageCoa Cie 1Vinay VarumaniNo ratings yet

- CN-model Qps-June 2023Document6 pagesCN-model Qps-June 2023wooyoung654No ratings yet

- Introduction To Programming (23e05101t) Question BankDocument8 pagesIntroduction To Programming (23e05101t) Question BankSrinivasan Nagaraj NNo ratings yet

- Sree Vidyanikethan Engineering College: III B.Tech II Semester (SVEC-16) Supplementary Examinations March - 2021Document2 pagesSree Vidyanikethan Engineering College: III B.Tech II Semester (SVEC-16) Supplementary Examinations March - 2021Umesh MosurNo ratings yet

- Rns Institute of Technology: Electronics and Communication EngineeringDocument1 pageRns Institute of Technology: Electronics and Communication EngineeringVinaykumar ANo ratings yet

- 16ec416-Electronic Measurementsand InstrumentationDocument6 pages16ec416-Electronic Measurementsand InstrumentationAjit PatraNo ratings yet

- Sem 4 PCS M1 Retest QP FinalDocument2 pagesSem 4 PCS M1 Retest QP Finalsaran kumarNo ratings yet

- Emi QB & BBDocument26 pagesEmi QB & BBswetha bagadi it's good but how it will workNo ratings yet

- Pcs 3Document2 pagesPcs 3Karan JagannathNo ratings yet

- MC - R21 External Model Paper-1Document3 pagesMC - R21 External Model Paper-1sdsameena2No ratings yet

- 18EE0216-Power Systems - IIDocument7 pages18EE0216-Power Systems - IIfaisal sbennaNo ratings yet

- IoT ELE Model Question Paper 2Document2 pagesIoT ELE Model Question Paper 2Sathish SinghNo ratings yet

- Code No: R05320402Document4 pagesCode No: R05320402chvsrsettiNo ratings yet

- MODEL QP FOR AI&DS alphaDocument2 pagesMODEL QP FOR AI&DS alphaithodNo ratings yet

- BTCS403 End Sem With CODocument4 pagesBTCS403 End Sem With COeverlovingmansiNo ratings yet

- Coa Ese Q (2022)Document2 pagesCoa Ese Q (2022)Aayush Kumar DubeyNo ratings yet

- 16ec416-Electronic Measurementsand InstrumentationDocument6 pages16ec416-Electronic Measurementsand InstrumentationplanningratnagiriNo ratings yet

- Et343t - Embedded Systems DesignDocument2 pagesEt343t - Embedded Systems Designatharv musaleNo ratings yet

- 20EC0454 - MATLAB ProgrammingDocument5 pages20EC0454 - MATLAB ProgrammingVishnu SushmanthNo ratings yet

- COA Question Paper CAT 1Document1 pageCOA Question Paper CAT 1Thamaraiselvi SNo ratings yet

- 19ECE349 - VI Sem May 2022Document3 pages19ECE349 - VI Sem May 2022karthiksuvines11No ratings yet

- Ramaiah: Makeup Examinations - March 2017Document2 pagesRamaiah: Makeup Examinations - March 2017ArunNo ratings yet

- MQ3 21cst602-CgipDocument3 pagesMQ3 21cst602-Cgiptanushreeshankar3No ratings yet

- IP - PVP23 Question BankDocument9 pagesIP - PVP23 Question Bank23501a0568No ratings yet

- IV-i Question Bank (r15)Document82 pagesIV-i Question Bank (r15)kd17209No ratings yet

- Se mqp2Document2 pagesSe mqp2tanushreeshankar3No ratings yet

- MPMC End SemDocument2 pagesMPMC End Semharshini.kNo ratings yet

- ARM Tutorial 1Document2 pagesARM Tutorial 1Roopa Gururaj0% (1)

- Question Bank COADocument3 pagesQuestion Bank COAMohd NadeemNo ratings yet

- 523 BA19 Ad 01Document5 pages523 BA19 Ad 01ramesh1926No ratings yet

- 21CST601 - MQP1Document3 pages21CST601 - MQP1Anirudh RNo ratings yet

- Bvrajuinstitute Oftechnology, Narsap UR: Code No: A27AF R15Document1 pageBvrajuinstitute Oftechnology, Narsap UR: Code No: A27AF R15rajeshNo ratings yet

- 4th Sem AssignmentsDocument8 pages4th Sem Assignmentszore zoreNo ratings yet

- Dspa Model QPDocument3 pagesDspa Model QPVikas JsvNo ratings yet

- 18EC0440 Embedded Systems and IoTDocument5 pages18EC0440 Embedded Systems and IoTM.Ranjith kumarNo ratings yet

- CC Model PaperDocument2 pagesCC Model Papersbasha2200No ratings yet

- Ese 2023 CoaDocument4 pagesEse 2023 Coaprathmeshpote95No ratings yet

- Questions 4 1Document95 pagesQuestions 4 1Anik PaulNo ratings yet

- Sathyabama: Register NumberDocument2 pagesSathyabama: Register Numbersharichandran86No ratings yet

- B) All Sub-Parts of A Question Must Be Answered at One Place Only, Otherwise It Will Not Be Valued. C) Missing Data Can Be Assumed SuitablyDocument1 pageB) All Sub-Parts of A Question Must Be Answered at One Place Only, Otherwise It Will Not Be Valued. C) Missing Data Can Be Assumed SuitablyGayathri KalyankarNo ratings yet

- Nanotechnology Commercialization: Manufacturing Processes and ProductsFrom EverandNanotechnology Commercialization: Manufacturing Processes and ProductsNo ratings yet

- Fenris Debug-0Document7 pagesFenris Debug-0marcosryanhmaranhaoNo ratings yet

- Syed Ammal Engineering College: Department of Computer Science and EngineeringDocument34 pagesSyed Ammal Engineering College: Department of Computer Science and EngineeringGuru BalanNo ratings yet

- Jboss Enterprise Application Platform: Troubleshooting GuideDocument15 pagesJboss Enterprise Application Platform: Troubleshooting GuidebonzoxNo ratings yet

- Operating SystemDocument28 pagesOperating SystemKunalNo ratings yet

- What Is Dma? Function? Wat If No Dma?Document5 pagesWhat Is Dma? Function? Wat If No Dma?sudhamsagNo ratings yet

- Cambridge Assessment International Education: Computer Science 2210/13 October/November 2019Document14 pagesCambridge Assessment International Education: Computer Science 2210/13 October/November 2019Sarim JavedNo ratings yet

- New Mpi Lab ManualDocument31 pagesNew Mpi Lab ManualBasava RajuNo ratings yet

- V & VI SEM SyllabusDocument78 pagesV & VI SEM SyllabusNarjiss ShimiNo ratings yet

- HPJPC Christopher and ThiruvathukalDocument420 pagesHPJPC Christopher and ThiruvathukalDeepak GandheNo ratings yet

- Unit4 VTU Format PDFDocument100 pagesUnit4 VTU Format PDFammayi9845_930467904No ratings yet

- SoftwareDocument89 pagesSoftwarezydusNo ratings yet

- Microprocessor Speed: Techniques Built Into Contemporary Processors IncludeDocument21 pagesMicroprocessor Speed: Techniques Built Into Contemporary Processors Includeyusha habibNo ratings yet

- MPMC Course FileDocument41 pagesMPMC Course FileSetlam Tarun KrishnaNo ratings yet

- 1151CS110 Computer Organization and ArchitectureDocument2 pages1151CS110 Computer Organization and ArchitectureArun Kumar DashNo ratings yet

- Mitron 1Document43 pagesMitron 1c2556273No ratings yet

- Synchronization Specification - DG PLC PDF - PDF 2Document5 pagesSynchronization Specification - DG PLC PDF - PDF 2Jatin HazarikaNo ratings yet

- 01 Introduction To Computers and ProgrammingDocument42 pages01 Introduction To Computers and Programmingryanzhang357No ratings yet

- Beginning Windows 10 IoT Core Raspberry Pi 2 - Alison Watson PDFDocument82 pagesBeginning Windows 10 IoT Core Raspberry Pi 2 - Alison Watson PDFego100% (2)

- Question Bank COADocument5 pagesQuestion Bank COAsirishaNo ratings yet

- Csi3021 Advanced-computer-Architecture TH 1.0 66 Csi3021 61 AcpDocument2 pagesCsi3021 Advanced-computer-Architecture TH 1.0 66 Csi3021 61 AcpakkichettygreeshmaNo ratings yet

- Mysql MonitoringDocument20 pagesMysql Monitoringgopinathkarangula100% (1)

- ITE REVIEWER - Information TechnologyDocument12 pagesITE REVIEWER - Information TechnologyaylaxdumpNo ratings yet

- Modul PBM 4 (Assembly Basic)Document19 pagesModul PBM 4 (Assembly Basic)Fajar FatahillahNo ratings yet

- Professional Obdii/Chip Tuning System For The Recalibration of Stock Ecu Engine Working ParametersDocument20 pagesProfessional Obdii/Chip Tuning System For The Recalibration of Stock Ecu Engine Working ParametersqwertyNo ratings yet

- EPK I7010Document2 pagesEPK I7010AMNo ratings yet

- 1 - Module 1Document36 pages1 - Module 1sammy CNo ratings yet

- Intel 8051Document6 pagesIntel 8051yadavshailendra3No ratings yet

- How To Read Linux Top Command Output and Uses: Your Email Address Subscribe!Document10 pagesHow To Read Linux Top Command Output and Uses: Your Email Address Subscribe!Tej SharmaNo ratings yet

- CSE332 / EEE336 Computer Organization & Architecture MIPS Datapath and Its ControlDocument33 pagesCSE332 / EEE336 Computer Organization & Architecture MIPS Datapath and Its ControlSamrat ShovonNo ratings yet