100%(1)100% found this document useful (1 vote)

811 viewsUvm Code Examples

The document discusses UVM components, objects, and the factory in UVM. It provides answers to questions on:

1. The difference between components and objects and their constructor arguments. Components have a parent argument while objects do not.

2. How the factory knows which constructor to call using the type_id.

3. The different ways of registering a class with the factory using macros like `uvm_component_utils for components.

Uploaded by

kavya devulapalliCopyright

© © All Rights Reserved

Available Formats

Download as PDF, TXT or read online on Scribd

100%(1)100% found this document useful (1 vote)

811 viewsUvm Code Examples

The document discusses UVM components, objects, and the factory in UVM. It provides answers to questions on:

1. The difference between components and objects and their constructor arguments. Components have a parent argument while objects do not.

2. How the factory knows which constructor to call using the type_id.

3. The different ways of registering a class with the factory using macros like `uvm_component_utils for components.

Uploaded by

kavya devulapalliCopyright

© © All Rights Reserved

Available Formats

Download as PDF, TXT or read online on Scribd

You are on page 1/ 115

1 ===================================================================================================================

2 //================================================QUESTION & ANSWERS===============================================

3 ===================================================================================================================

4

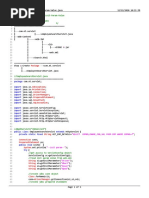

5 create(string ="name",uvm_component parent);

6

7 //QSN.why create accept two argument during building a components but only one during building objects ?????

8

9 ANS. Because componets follow hierarchy so they have name and parent

10 but object did not follow any hierarchy so they dont have parent that is why only one constructor which is of

11 string type name only passed

12

13 //QSN.IN SV we pass the interface handle as an argumnt in new() constructor to connect the driver .and DUT can we

14 .do.this in UVM ?????

15

16 ANS. NO, Because in uvm to create any component we .use create() method which can accept only two arguments we

17 can't give additional arguments

18

19 //QSN.How create() method will know which class constructor it should call ????

20

21 ANS. Based on the type_id given during creating object .for a component

22 eg. drv=driver::type_id::create("drv",this);

23

24 //QSN.IN How many ways you can implemented standard method inside the Transaction class ?????

25

26 ANS. Two Ways : BY Using field macros by registring the properties

27 : By Using Override Methods

28 Override methods are recommended

29 - do_copy

30 - do_compare

31 - do_print

32

33 //QSN.What is the return type of clone() ?????

34

35 ANS. uvm_object: Clone will first create object then it will copy .and .return destination object.

36 destination object is .return through uvm_object parent handle

37 We need here $cast()

38 //QSN.What is the difference between uvm_object and uvm_component ?????

39

40 ANS. classes which are used to build testbench structure are called components and classes which are used to .

41 .generate stimulus are called object.& object will.not follow any hierarchy.

42

43

44 //QSN.In UVM Liabrary which classes are not virtual classes ???

45

46 ANS. uvm_driver and uvm_sequencer are non_virtual classes.

47

48 //QSN.Inside the components where did we write executable code ???

49

50 ANS. In Phases

51

52 //QSN.How to register a class to the factory ????

53

54 ANS. By using macros :

55

56 `uvm_component_utils() for components

57 `uvm_object_utils() for objects

58 `uvm_component_utils() for parametrized components

59 `uvm_object_utils() for parametrized objects

60

61 these macros will get expended in three parts

62

63 1. wrapper --> uvm_component_registry/uvm_object_registry which typedefed to type_id

64 2. get_type() -->.static method which returns type_id

65 3. get_type_name() --> method which .return component/object name as a string

66

67 //QSN.What is difference between new() and create() ?????

68

69 ANS. 1. create() is the factory method which is used in uvm to create components .and transaction .class objects &

70 it is a .static method defined in registry .class

71 2. create() internally call new() constructor

72 3. new() is the system verilog constructor to create components .and transaction .class objects

73

74 //QSN.How create() method will know which class constructor new() it should call ????

75

76 ANS. By type_id

77

78

79

80

81

82

83

84

85

86

87 -----------------------------------------------------=============------------------------------------------------

88 //====================================================UVM FACTORY=================================================

89 -----------------------------------------------------=============------------------------------------------------

90 class

91

92 1. We have to register the .class to the factory

93 2. It is a .class where it creates the components.and objects.

94 3. from test we can control, configure the factory to create whether parent.class .or child.class

95 for .this we have to register a .class .with the factory

96 4. There are three steps to register the .class .with factory

97 1. Create Wrapper around component registry .class, typedefed to type_id

98 2. static .function to get the type_id

99 3. function to get the .type name

100

101

102 //STEPS TO REGISTER CLASS WITH FACTORY

103 -----------------------------------------

104

105 class my_component extends uvm_component;

106 //wrapper class around the component/object registry class

107 typedef uvm_component_registry#(my_component) type_id;

108 /*//incase of object

109 typedef uvm_object_registry#(my_object) type_id;*/

110

111 //used to get the type_id wrapper

112 static function type_id get_type();

113 return type_id::get();

114 endfunction : get_type

115

116 //used to get the type_name as string

117 function string get_type_name();

118 return "my_component";

119 endfunction : get_type_name

120

121 endclass : my_component

122

123 1. so writing .this much code to register the .class everytime is .bit lengthy

124 2. so .for registering the component/object .with factory we will .use macros

125

126

127

128

129

130 //MACRO FOR COMPONENT CLASSES //MACRO FOR PARAMETRIZED COMPONENT CLASSES

131 ------------------------------ -------------------------------------------

132 `uvm_component_utils() `uvm_component_param_utils()

133

134 //MACRO FOR OBJECT CLASSES //MACRO FOR PARAMETRIZED OBJECT CLASSES

135 --------------------------- ----------------------------------------

136 `uvm_object_utils() `uvm_object_param_utils()

137

138

139

140 //CONSTRUCTOR DEFAULTS

141 ------------------------

142

143 1. The uvm_component and uvm_object constructor are virtual methods

144 2. The defaults are different for components and objects

145

146 //For COMPONENT

147 class my_component extends uvm_component;

148 function new(string name="my_component",uvm_component parent=null)

149 super.new(name,parent);

150 endfunction

151 endclass

152

153 //For OBJECT

154 class my_item extends uvm_sequence_item;

155 function new(string name="my_item")

156 super.new(name);

157 endfunction

158 endclass

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173 uvm_top

174 uvm_test_top

175 env

176 SB

177

178 agt

179 drv

180 mon

181 seqr

182

183 =============

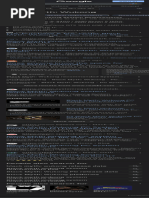

184 //MY_DRIVER

185 =============

186

187 class my_driver extends uvm_driver;

188 `uvm_component_utils(my_driver)

189

190 function new(string name,uvm_component parent)

191 super.new(name,parent);

192 endfunction

193

194 endclass

195

196 ===============

197 //CHILD_DRIVER

198 ===============

199

200 class child_driver extends my_driver;

201 `uvm_component_utils(child_driver)

202

203 function new(string name,uvm_component parent)

204 super.new(name,parent);

205 endfunction

206

207 endclass

208

209

210

211

212

213

214

215

216 ============

217 //MY_AGENT

218 ============

219

220 class my_agent extends uvm_agent;

221 `uvm_component_utils(my_agent)

222

223 function new(string name,uvm_component parent)

224 super.new(name,parent);

225 endfunction

226

227 my_driver drv;

228 my_monitor mon;

229 my_sequencer seqr;

230

231 function void build_phase(uvm_phase phase);

232 super.build_phase(phase);

233

234 /* drv=new("drv",this);

235 mon=new("mon",this); for drv,mon & seqr parent(in which class they enclosed in

236 seqr=new("seqr",this); hierarchy) is agent so we pass this keyword as

237 second argument which refers agent */

238

239 drv = my_driver::type_id::create("drv",this); //create() is the factory method which will call new();

240 mon = my_monitor::type_id::create("mon",this); //It is static method defined in registry class

241 seqr= my_sequencer::type_id::create("seqr",this);

242

243 endfunction

244

245 endclass

246

247

248

249

250

251

252

253

254

255

256

257

258

259 ==============

260 //ENVIRONMENT

261 ==============

262

263 class environment extends uvm_env;

264 `uvm_component_utils(environment)

265

266 function new(string name,uvm_component parent)

267 super.new(name,parent);

268 endfunction

269

270 function void build_phase(uvm_phase phase);

271 super.build_phase(phase);

272

273 my_agent agt; //Here for agent parent will be environment

274

275 agt=my_agent::type_id::create("agt",this);

276 endfunction

277

278 endclass

279

280 =============

281 //TEST CLASS

282 =============

283

284 class test extends uvm_test;

285 `uvm_component_utils(test)

286

287 function new(string name,uvm_component parent)

288 super.new(name,parent);

289 endfunction

290

291 function void build_phase(uvm_phase phase);

292 super.build_phase(phase);

293

294 environment env; //Here for environment parent will be test

295

296 env=environment::type_id::create("env",this);

297 // set_type_override_by_type(my_driver::get_type(),child_driver::get_type());

298 endfunction

299

300 endclass

301

302 =============

303 //TOP MODULE

304 =============

305

306 module top();

307

308 initial

309 begin

310

311 run_test("test"); /* It will create uvm_top(uvm_root) which is nothing but handle of

312 uvm_root and inside uvm_top, test will be created and given name

313 uvm_test_top */

314 end

315 endmodule

316

317

318

319

320 //run_test("test")

321 -------------------

322 1. It will take test name as an argument which is string .type .for which .instance will be created

323 2. After creating test

324 3. run_test() will call build_phase of

325 |_ env -> agent -> where drv,mon & seqr will be created

326

327

328 =====================

329 //FACTORY OVERRIDEN

330 =====================

331

332 //GLOBAL OVERRIDE

333 ------------------

334

335 1.Make sure both classes should be polymorphically compatible

336 eg. original and substitude should have parent child relation

337 .---------------------------------------------------------------------------------------------------.

338 | set_type_override_by_type(original_type::get_type(),substitude_type::get_type(),bit replace=1); |

339 '---------------------------------------------------------------------------------------------------'

340

341 //EXAMPLE

342 .------------------------------------------------------------------------------.

343 | set_type_override_by_type(my_driver::get_type(),child_driver::get_type()); |

344 '------------------------------------------------------------------------------'

345

346 1. It will override type_id of parent .with type_id of child.

347 2. type_id of driver will be override by type_id of child_driver in entire testbench.

348 so now driver will have type_id of child_driver

349 3. whenever create() method will called by driver it will create object .for child_driver.

350

351 this is how override will happen.

352

353 //INSTANCE OVERRIDE

354 --------------------

355

356 .----------------------------------------------------------------------------------------------------------.

357 | set_inst_override_by_type("path",original_type::get_type(),substitude_type::get_type(),bit replace=1); |

358 '----------------------------------------------------------------------------------------------------------'

359 /*Why replace=1 here so that if again want to override this instance with other then by checking this value

360 simulator will understand that previous overriding happened so it will first convert it to original type then

361 override again with new type

362 */

363

364 //EXAMPLE

365

366

367

368

369

370

371

372

373

374

375

376

377

378

379

380

381

382

383

384

385

386

387

388 test

389 env

390 agent_top

391 agent1

392 bus_wr_driver

393 monitor

394 sequencer

395

396 agent2

397 bus_wr_driver

398 monitor

399 sequencer

400

401 class test extends uvm_test;

402

403 virtual function build_phase(uvm_phase phase);

404

405 set_inst_override_by_type("*.agent1.*",bus_wr_driver::get_type(),apb_wr_driver::get_type());

406

407 endfunction

408

409 endclass

410

411

412 test

413 env

414 agent_top

415 agent1

416 apb_wr_driver

417 monitor

418 sequencer

419

420 agent2

421 bus_wr_driver

422 monitor

423 sequencer

424 endclass

425

426

427

428

429

430

431 ---------------------------------------------------===================--------------------------------------------

432 //==================================================STIMULUS MODELING=============================================

433 ---------------------------------------------------===================--------------------------------------------

434 class

435

436 1.Transaction .class extends from uvm_sequence_item

437 2.Inside transaction.class we declare properties which is used as.input to the DUT.and valid constraints .and

438 methods required.for the.class variables(properties) eg. copy,clone,compare,print etc.

439

440

441 what is purpose of field macros ????

442 register the.property.for copy,compare,clone & print method

443

444 There are two ways to implement those methods

445

446 1. Using field macros we can automate the methods by enabling the methods .for all the properties

447 2. By override the.virtual methods eg. do_copy, do_compare, do_print etc.

448

449

450

451 //Using the field macro

452 -------------------------

453 1. It will not recommended because each field macros will expend in so many lines which affect

454 performance of simulator

455 2. Hard to debug

456 3. Time taken by simulator is more when used field macros

457

458

459

460

461

462

463

464

465

466

467

468

469

470

471

472

473

474 class write_xtn extends uvm_sequence_item;

475

476 rand int addr,data;

477 rand bit wr;

478

479 function new(string name);

480 super.new(name);

481 endfunction

482 //constraints

483

484 //post_randomize method

485

486 `uvm_object_utils_begin(write_xtn)

487

488 `uvm_field_int(addr,UVM_ALL_ON) //UVM_ALL_ON ---> all the method will be enabled

489 `uvm_field_int(data,UVM_ALL_ON|UVM_DEC) //UVM_DEC ---> it will display in decimal

490 `uvm_field_int(wr,UVM_ALL_ON|UVM_NOCOMPARE) //UVM_NOCOMPARE ---> all the methods enabled except

491 //compare method

492 `uvm_object_utils_end

493

494 endclass

495

496 .-------------------------------------------------.

497 | write_xtn t1,t2; |

498 | |

499 | initial |

500 | begin |

501 | t1=write_xtn::type_id::create("t1"); |

502 | t2=write_xtn::type_id::create("t2"); |

503 | |

504 | assert(t1.randomize()); |

505 | |

506 | t1.print(); |

507 | t2.copy(t1); |//t2.do_copy(t1) => it will copy object t1 to t2

508 | if(t2.compare(t1)); |//t2.do_compare(t1) =>it will return 1 or 0

509 | end |

510 '-------------------------------------------------'

511

512

513

514

515

516

517 //By OVERRIDE the methods

518 ---------------------------

519

520 copy will call virtual method do_copy so we will override do_copy.

521 print will call virtual method do_print so we will override do_print

522

523 class write_xtn extends uvm_sequence_item;

524

525 `uvm_object_utils(write_xtn)

526

527 rand int addr,data;

528 rand bit wr;

529

530 function new(string name);

531 super.new(name);

532 endfunction

533 //constraints

534

535 //post_randomize method

536

537 //Rules to override virtual method of parent in child

538 /* 1. The return type, function name , argument should be same

539 eg. prototype of function should be same

540

541 2. virtual methods do_copy,do_print,do_compare all are inherited from uvm_object class

542 */

543

544

545

546

547

548

549

550

551

552

553

554

555

556

557

558

559

560 ==================

561 //DO_COPY METHOD

562 ==================

563

564 virtual function void do_copy(uvm_object rhs) //rhs=t1 (though it is a vlid assignment still

565 // parent can't access child class properties)

566

567 write_xtn xtn;

568

569 if(!$cast(xtn,rhs)) //xtn->rhs->t1, => xtn=t1

570 begin

571 `uvm_fatal("do_copy","casting of rhs object failed")

572 end t2 t1

573 super.do_copy(rhs); .----------. .----------. o

574 | data | | data |

575 this.data=xtn.data; /*this -> t2, xtn -> t1*/ | addr | | addr |

576 this.addr=xtn.addr; | wr | | wr |

577 this.wr=xtn.wr; | | | |

578 | | | |

579 endfunction | | | |

580 '----------' '----------'

581 /* so for access the child class properties here we will take another child class handle xtn

582 and cast rhs handle to xtn

583 now xtn will start pointing to rhs which is already pointing to t1

584 now we can access child class properties using xtn handle

585

586 t2.addr=xtn.addr

587 t2.data=xtn.data

588 t2.wr=xtn.wr

589

590 super.do_copy(rhs)

591 ==> It is required in child_xtn class when parent_xtn class have some properties

592 and we create a child_xtn class so in child_xtn class do_copy method we call

593 super.do_copy() so that it will call parent class do_copy method and copy parent class

594 properties also

595 */

596

597

598

599

600

601

602

603

604 ====================

605 //DO_COMPARE METHOD

606 ====================

607

608 virtual function bit do_compare(uvm_object rhs)

609 write_xtn xtn;

610 if(!$cast(xtn,rhs))

611 begin

612 `uvm_fatal("do_compare","casting of rhs object failed")

613 return 0;

614 end

615 super.do_compare(rhs);

616 return(

617 (this.data==xtn.data) &&

618 (this.addr==xtn.addr) &&

619 (this.wr ==xtn.wr) &&

620 )

621 endfunction

622

623 endclass

624

625 .-------------------------------------------------------------------------------------------.

626 | write_xtn t1,t2; |

627 | initial |

628 | begin |

629 | t1=write_xtn::type_id::create("t1"); |

630 | t2=write_xtn::type_id::create("t2"); |

631 | |

632 | assert(t1.randomize()); |

633 | |

634 | t1.print(); /*it will print all the properties in table format*/ |

635 | t2.copy(t1); /*it will copy object t1 to t2 */ |

636 | if(t2.compare(t1)); /*it will return 1 or 0 */ |

637 | end |

638 '-------------------------------------------------------------------------------------------'

639

640

641

642

643

644

645

646

647 ==================

648 //CLONE() METHOD

649 ==================

650

651

652 1. While using copy mtheod we will make sure object for destination handle already created

653 but for clone there is no need to create a destination object

654

655 2. clone does two things ---> create+copy

656 1. first it will create object for destination

657 2. then it call the copy method

658

659 after the copy the object which is created it will return that object reference through the parent

660 handle.

661

662 3. The return type of clone is uvm_object

663

664

665 function uvm_object clone();

666

667 write_xtn t=write_xtn::type_id::create("t1");

668 t.copy(t1);

669 uvm_object p=t;

670 return p;

671

672 endfunction

673

674

675 .-----------------------------------.

676 | write_xtn t1,t2; |// t1 is of write_xtn type so clone will create a object of

677 | |// write_xtn type and copy all the properties of t1 to that object

678 | initial |// and it pass handle of that object through parent handle.

679 | begin |

680 |/* t2=t1.clone(); */|

681 | $cast(t2,t1.clone()); |

682 | end |

683 '-----------------------------------'

684

685

686 //t2=t1.clone(); ===> //t2.copy(t1) --> t2.do_copy(t1)

687 /*it is returning through parent handle so we can't directly assign

688 parent handle to child ,we use $cast here.*/

689

690 ==================

691 //DO_PRINT METHOD

692 ==================

693

694 1. It accept an argument which is uvm_printer type printer & it has a default value

695 uvm_default_table_printer

696 which will tell us in which format the transaction .class properties should be displayed

697

698 1. line printer

699 2. table printer

700 3. tree printer

701

702 so .for that .inside the printer .class we have method

703 print_field("variable_name",variable_name,width,Radix);

704

705 eg. printer.print_field("data",data,32,UVM_DEC);

706

707

708 virtual function void do_print(uvm_printer printer=uvm_default_table_printer);

709

710 printer.print_field("data",data,32,UVM_DEC);

711 printer.print_field("addr",addr,12,UVM_HEX);

712 printer.print_field("wr",wr,1,UVM_BIN);

713

714 endfunction

715

716 .-----------------------.

717 | write_xtn xtn; |

718 | |

719 | initial |

720 | begin |

721 | xtn.print(); | //It will print all the properties in table format

722 | end |

723 '-----------------------'

724

725

726

727

728

729

730

731

732

733 // TABLE VIEW TREE VIEW

734 ========== ==========

735

736 ------------------------------------------- xtn:(write_xtn@1150)

737 Name Type Size Value { data:'d15

738 ------------------------------------------- addr:'h26

739 xtn Packet - @1150 wr :'b1 }

740 data integral 32 'd15

741 addr integral 12 'h26

742 wr integral 1 'b1

743 -------------------------------------------

744

745

746 // LINE VIEW

747 =========

748

749 xtn: (write_xtn@1150) {data:'d15 addr:'h26 wr:'b1}

750

751

752 .===========================================================================.

753 |/* RADIX | DESCRIPTION */|

754 .===========================================================================.

755 | UVM_BIN | Print the given variable in binary format |

756 | UVM_DEC | Print the given variable in decimal format |

757 | UVM_HEX | Print the given variable in hexadecimal format(default) |

758 | UVM_OCT | Print the given variable in octal format |

759 | UVM_STRING | Print the given variable in .string format |

760 | UVM_TIME | Print the given variable in .time format |

761 '---------------------------------------------------------------------------'

762

763 .============================================================================.

764 |/* FLAG | DESCRIPTION */|

765 .============================================================================.

766 | UVM_ALL_ON | All operations are turned on |

767 | UVM_DEFAULT | Enables all operations and equivalent to UVM_ALL_ON |

768 | UVM_NOCOPY | Do not copy the given variable |

769 | UVM_NOCOMPARE | Do not compare the given variable |

770 | UVM_NOPRINT | Do not print the given variable |

771 | UVM_NOPACK | Do not pack or unpack the given variable |

772 | UVM_REFERENCE | Operate only on handles, i.e. for object types |

773 | | do not do deep copy, etc |

774 '----------------------------------------------------------------------------'

775

776

777

778 .=================.================.=============================================================.

779 |/* METHOD CALLED | VIRTUAL | DESCRIPTION */|

780 |/* BY USER | METHOD | */|

781 '.==============================================================================================.'

782 | copy | do_copy | Performs a deep copy of an object |

783 | clone | do_copy | Creates a new object and then does a deep copy of an object |

784 | compare | do_compare | Compares one object to another of the same type |

785 | print | do_print | Prints a the result of convert2string to the screen |

786 | sprint | do_print | Returns the result of convert2string |

787 | record | do_record | Handles transaction recording |

788 | pack | do_pack | Compresses object contents into a bit format |

789 | unpack | do_unpack | Converts a bit format into the data object format |

790 | convert2string | - | Returns a string representation of the object |

791 '------------------------------------------------------------------------------------------------'

792

793 endclass

794

795

796

797

798

799

800

801

802

803

804

805

806

807

808

809

810

811

812

813

814

815

816

817

818

819 ------------------------------------------------------============------------------------------------------------

820 //=====================================================UVM PHASES=================================================

821 ------------------------------------------------------============------------------------------------------------

822 class

823 /

824 //ORDER OF EXECUTION OF PHASES

825 -------------------------------

826 1. build_phase }

827 2. connect_phase } // PRE-RUN PHASES

828 3. end_of_elaboration_phase }

829 4. start_of_simulation_phase }

830 5. run_phase ---------------------------------------

831 6. extract_phase }

832 7. check_phase } // POST-RUN PHASES

833 8. report_phase }

834 9. final_phase }

835

836 //All above phases automatically called by run_test() method

837

838 //SUB-RUN PHASES

839 ------------------

840

841 run_phase

842 |

843 | //pre_reset

844 |--> 1.reset : In .this phase drive reset

845 | //post_reset

846 |

847 | //pre_configure

848 |--> 2.configure : In .this phase configure the DUT

849 | //post_configure

850 |

851 | //pre_main

852 |--> 3.main : In .this phase we drive the data

853 | //post_main

854 |

855 | //pre_shutdown

856 |--> 4.shutdown : In .this phase will .do .final adjustments

857 | //post_shutdown

858

859

860

861

862 //EXECUTION OF PHASES

863

864

865 run_test();

866

867 time=0 ns | | time=100 ns

868 | |

869 | |

870 | |

871 | |

872 |---------------------------------->>>>|

873 | |

874 | |

875 build_phase | ---->>>> |extract_phase

876 connect_phase | TIME |check_phase

877 end_of_elaboration_phase | |report_phase

878 start_of_simulation_phase| |final_phase

879

880 <--------------run_phase--------------->

881

882

883 //BUILD_PHASE

884 --------------

885 1.It is used to construct sub-components

886 2.Component hierarchy is therefore build top-down

887

888 //CONNECT_PHASE

889 ----------------

890 1.It is used to connect the components .or any connection like connecting static and virtual interface

891 2.It follow bottom-up approach

892 3.First connect_phase of driver,monitor,sequencer executed then agents--->env

893

894 //END_OF_ELABORATION_PHASE

895 ---------------------------

896 1.It is used to make any .final adjustments to the structure,configuration .or connectivity of the

897 testbench .before simulation starts

898 2.It follow bottom-up approach

899

900 //START_OF_SIMULATION_PHASE

901 ----------------------------

902 1.It is used to display banners: testbench topology,.or configuration information

903 2.It follow bottom-up approach

904

905 //RUN_PHASE

906 ------------

907 1. It is the only phase which is task remaining all phases is function.

908 2. It consumes simulation .time remaining phases completes in zero simulation .time

909 3. run tasks are executed in parallel, run_phases of all components executed in parallel.

910 4. 12 Sub phases are added in parallel with run_phase

911 5. It is recommended either .use run_phase .or sub-run_phases don't .use both coz multiple driver

912 issue can happen like multiple driver driving same bus

913

914 DRIVER

915 ,---------------------------------,

916 | fork |

917 | run_phase(); |

918 | begin |

919 | reset_phase(); |

920 | configure_phase(); |

921 | main_phase(); |

922 | shutdown_phase(); |

923 | end |

924 | join |

925 '---------------------------------'

926

927 6. driver.and monitor should .use run_phase

928 7. don't.use phase domain .or jumping

929

930

931 //PHASE SYNCHRONIZATION

932 -------------------------

933 /

934

935 By default, all components allow all other components to complete a phase before all components move to next

936 phase

937

938 1. Like there are three drivers in which we are using run_phase

939 So each driver may take different .time to complete sub-run_phases

940

941 2. Like DRV1 reset_phase taking less .time

942 DRV2 reset_phase taking little more.time

943 But Configure_phase of all drivers will start at same.time

944

945 3. Like reset_phase , configure_phase may take different .time to complete its execution

946 But Main_phase will start at same .time in all drivers.

947

948 4. Like all other phases shutdown_phase may take different .time as soon as shutdown_phase of all drivers

949 completed then start post-run_phases

950

951 */ ||

952 .---------------------------.--------------. .-------------. .---------------.||

953 DRV1: | Reset | Configure | | Main | | Shutdown |||

954 '---------------------------'--------------' '-------------' '---------------'||

955 ||//POST

956 .---------------. .-------------------. .--------------------.---------------.||//RUN

957 DRV2: | Reset | | Configure | | Main | Shutdown |||//PHASES

958 '---------------' '-------------------' '--------------------'---------------'||

959 ||

960 .-------------------. .------------------------.----------. .---------------.||

961 DRV3: | Reset | | Configure | Main | | Shutdown |||

962 '-------------------' '------------------------'----------' '---------------'||

963 ||

964 ===================================================================>>>>>>>>>>>>>>>>>>>>>>>>

965 TIME

966

967

968 or

969 ||

970 .--------------------------------------. ||

971 DRV1: | run_phase | ||

972 '--------------------------------------' ||

973 ||

974 .-----------------------------------------------------------------------.||

975 DRV2: | run_phase ||| //post-run_phases

976 '-----------------------------------------------------------------------'||

977 ||

978 .---------------------------------------------------. ||

979 DRV3: | run_phase | ||

980 '---------------------------------------------------' ||

981 ||

982 ======================================================>>>>>>>>>>>>>>>>>>>

983 TIME

984

985

986

987

988

989

990

991 //PHASE DOMAINS

992 ---------------

993 1. By creating domains,each components can complete a phase independent of the other components.

994 2. It is .not recommended

995

996

997 .===================================================================================.

998 |/* .---------------------------.--------------.-------------.---------------. */|

999 DRV1: |/* | Reset | Configure | Main | Shutdown | */|

1000 |/* '---------------------------'--------------'-------------'---------------' */|

1001 '==================================================================================='

1002

1003 .====================================================================================.

1004 |/* .---------------.-----------------.-----------------.---------------. */|

1005 DRV2: |/* | Reset | Configure | Main | Shutdown | */|

1006 |/* '---------------'-----------------'-----------------'---------------' */|

1007 '===================================================================================='

1008

1009 .====================================================================================.

1010 |/* .-------------------.------------------------.----------.---------------. */|

1011 DRV3: |/* | Reset | Configure | Main | Shutdown | */|

1012 |/* '-------------------'------------------------'----------'---------------' */|

1013 '===================================================================================='

1014

1015 ===============================================================>>>>>>>>>>>>>>>>>

1016 TIME

1017

1018 /

1019 //EXTRACT_PHASE

1020 ----------------

1021 1. It retrieves and processes information from scoreboards and functional coverage monitors

1022 2. It also follows bottom-up approach

1023

1024 //CHECK_PHASE

1025 ---------------

1026 1. It checks it the DUT behaved correctly and identifies errors that may have occurred during the

1027 execution

1028 2. It follows bottom-up approach

1029

1030 //REPORT_PHASE

1031 ---------------

1032 1. It is used to displays the results of the simulation,informations

1033 2. It follows bottom-up approach

1034

1035 //FINAL_PHASE

1036 ---------------

1037 1. It performs all the .final adjustments,outstanding works,wrapping the simulation

1038 2. It follows top-down approach same as build_phase

1039

1040 */

1041 ====================

1042 //ENVIRONMENT CLASS

1043 ====================

1044

1045 class ram_env extends uvm_env;

1046

1047 // Factory Registration

1048 `uvm_component_utils(ram_env)

1049

1050 // Declare the ram_wr_agent handle

1051 ram_wr_agent wr_agnth;

1052

1053

1054 //------------------------------------------

1055 // METHODS

1056 //------------------------------------------

1057

1058 // Standard UVM Methods:

1059 extern function new(string name = "ram_env",uvm_component parent);

1060 extern function void build_phase(uvm_phase phase);

1061 extern function void connect_phase(uvm_phase phase);

1062 extern function void end_of_elaboration_phase(uvm_phase phase);

1063 extern function void start_of_simulation_phase(uvm_phase phase);

1064 extern task run_phase(uvm_phase phase);

1065 extern function void extract_phase(uvm_phase phase);

1066 extern function void check_phase(uvm_phase phase);

1067 extern function void report_phase(uvm_phase phase);

1068

1069 endclass

1070

1071

1072

1073

1074

1075

1076

1077 =========================

1078 //constructor new method

1079 =========================

1080

1081 function ram_env::new(string name="ram_env",uvm_component parent);

1082 super.new(name,parent);

1083 endfunction

1084

1085

1086

1087 // Add UVM phases

1088 // NOTE : Call super.*_phase() in every phase method ,* indicates build,connect,etc

1089 // Hint : `uvm_info(“RAM_ENV”,”This is Build Phase ”, UVM_LOW)

1090

1091 ================

1092 //build() phase

1093 ================

1094

1095 function void ram_env::build_phase(uvm_phase phase);

1096 super.build_phase(phase);

1097 // Create the instance of agent in the build phase

1098 wr_agnth=ram_wr_agent::type_id::create("wr_agnth",this);

1099 `uvm_info("RAM_ENV","THIS IS BUILD PHASE OF ram_env",UVM_LOW)

1100 endfunction

1101

1102

1103 ==================

1104 //connect() phase

1105 ==================

1106

1107 function void ram_env::connect_phase(uvm_phase phase);

1108 super.connect_phase(phase);

1109 `uvm_info("RAM_ENV","THIS IS CONNECT PHASE OF ram_env",UVM_LOW)

1110 endfunction

1111

1112 =============================

1113 //end_of_elaboration() phase

1114 =============================

1115

1116 function void ram_env::end_of_elaboration_phase(uvm_phase phase);

1117 super.end_of_elaboration_phase(phase);

1118 `uvm_info("RAM_ENV","THIS IS AN END OF ELABORATION OF ram_env",UVM_LOW)

1119 endfunction

1120

1121 ===============================

1122 //start_of_simulation() phase

1123 ===============================

1124

1125 function void ram_env::start_of_simulation_phase(uvm_phase phase);

1126 super.start_of_simulation_phase(phase);

1127 `uvm_info("RAM_ENV","THIS IS START OF SIMULATION OF ram_env",UVM_LOW)

1128 endfunction

1129

1130 ==============

1131 //run() phase

1132 ==============

1133 // Raise and drop objections

1134 // With in raising ans dropping the objections add 100 delay in the run phase before printing

1135

1136 task ram_env::run_phase(uvm_phase phase);

1137 super.run();

1138 phase.raise_objection(this);

1139 #100;

1140 `uvm_info("RAM_ENV ","THIS IS RUN PHASE OF ram_env",UVM_LOW)

1141 phase.drop_objection(this);

1142 endtask

1143

1144

1145 //This is the only phase which is task and it is time consuming remaining all other phases are functions & completes

1146 in zero simulation time.

1147 //

1148 ==================

1149 //extract() phase

1150 ==================

1151

1152 function void ram_env::extract_phase(uvm_phase phase);

1153 super.extract_phase(phase);

1154 `uvm_info("RAM_ENV","THIS IS EXTRACT PHASE OF ram_env",UVM_LOW)

1155 endfunction

1156

1157

1158

1159

1160

1161

1162

1163 ================

1164 //check() phase

1165 ================

1166

1167 function void ram_env::check_phase(uvm_phase phase);

1168 super.check_phase(phase);

1169 `uvm_info("RAM_ENV","THIS IS CHECK PHASE OF ram_env",UVM_LOW)

1170 endfunction

1171

1172 =================

1173 //report() phase

1174 =================

1175

1176 function void ram_env::report_phase(uvm_phase phase);

1177 super.report_phase(phase);

1178 `uvm_info("RAM_ENV","THIS IS REPORT PHASE OF ram_env",UVM_LOW)

1179 endfunction

1180

1181

1182

1183

1184 endclass

1185

1186

1187

1188

1189

1190

1191

1192

1193

1194

1195

1196

1197

1198

1199

1200

1201

1202

1203

1204

1205

1206 -----------------------------------------------------============-------------------------------------------------

1207 //====================================================OBJECTIONS==================================================

1208 -----------------------------------------------------============-------------------------------------------------

1209 class

1210

1211

1212 /

1213 1. Components and Objects can raise and drop the objections

1214 2. It remains in same phase till all the objections are dropped

1215 3. Used in the run_phase

1216

1217

1218 //OBJECTIONS

1219 --------------

1220 1. IN COMPONENTS

1221 -> Phase.raise_objection(this);

1222 -> Phase.drop_objection(this);

1223

1224 2. IN OBJECTS

1225 -> Starting_phase.raise_objection(this);

1226 -> Starting_phase.drop_objection(this);

1227

1228

1229 Component which is using run_phase should tell the simulator that I'm using the run_phase by raising a

1230 objections

1231

1232 once it complete all the.task.or functionalities in run_phase then it should drop the objection

1233

1234 Simulator will track the objections , It will done via variable count, .this count variable will increment

1235 every .time when a component raise_objection.and will decrement every.time when component drop the

1236 objection..

1237

1238 So when all the raise_objection will droped the count will become zero at that.time simulator will

1239 understand that all the components have completed the run_phase,.and then it will terminate the run_phase

1240 .and move to post run_phases

1241

1242

1243 uvm_objection::raise_objection(uvm_object null,string description="",int count=1);

1244

1245 uvm_objection::raise_objection(uvm_object null,string description="",int count=1);

1246

1247 1. uvm_object ---> only.this argument we have to passed

1248 2. description ---> default value =""

1249 3. count ---> default value = 1

1250

1251 */

1252

1253 //EXAMPLES

1254 ------------

1255

1256 class agent extends uvm_agent;

1257

1258 virtual task run_phase(uvm_phase phase);

1259 phase.raise_objection(this); //this keyword will tell which component raised the objection

1260 #100; //phase will tell phase eg. reset,configure,main,shutdown

1261 phase.drop_objection(this); //this keyword will tell which component droped the objection

1262 endtask

1263

1264 endclass

1265

1266

1267 class driver extends uvm_driver;

1268

1269 virtual task run_phase(uvm_phase phase);

1270 phase.raise_objection(this);

1271 #10;

1272 phase.drop_objection(this);

1273 endtask

1274

1275 endclass

1276

1277

1278 /*

1279 at time= 0 ns both agent and driver will raise objection,so the value of count will get incremented two times

1280

1281 time= 0 ns count=2; //both agent,driver raise_objection

1282 time= 10 ns count=1; //driver drop_objection

1283 time= 100 ns count=0; //agent drop_objection & run_phase terminated

1284 */

1285

1286

1287

1288

1289

1290

1291

1292

1293 test

1294 ---------------------------------------------------- -------------------------------------------------

1295 | virtual task run_phase(uvm_phase phase); | | virtual task run_phase(uvm_phase phase); |

1296 | | | |

1297 | phase.raise_objection(this); | | phase.raise_objection(this); |

1298 | #10; | |/* #10; */ |

1299 | /* #5; */ | | #5; |

1300 | phase.drop_objection(this); | | phase.drop_objection(this); |

1301 | endtask | | endtask |

1302 | | | |

1303 | | | |

1304 driver | | | |

1305 | | | |

1306 | virtual task run_phase(uvm_phase phase); | | virtual task run_phase(uvm_phase phase); |

1307 | #6 */ | | #6 |

1308 | phase.raise_objection(this); | | phase.raise_objection(this); |

1309 | #15; */ | | #15; |

1310 | phase.drop_objection(this); | | phase.drop_objection(this); |

1311 | endtask | | endtask |

1312 ----------------------------------------------------- -------------------------------------------------

1313

1314 class solution

1315

1316 time = 0 ns count=1 time = 0 ns count=1

1317 time = 6 ns count=2 time = 5 ns count=0

1318 time = 10 ns count=1 run_phase will get terminated time = 5 ns

1319 time = 21 ns count=0 driver run_phase suspended

1320

1321 run_phase terminated time = 21 ns

1322

1323 endclass

1324

1325

1326

1327

1328

1329

1330

1331

1332

1333

1334

1335

1336 test

1337 ----------------------------------------------------- -------------------------------------------------

1338 | virtual task run_phase(uvm_phase phase); | | virtual task run_phase(uvm_phase phase); |

1339 | | |/* #1 */ |

1340 | phase.raise_objection(this); | |/* phase.raise_objection(this); */ |

1341 | #10; | | |

1342 | /* #5; */ | | #5; |

1343 |/* phase.drop_objection(this); */ | |/* phase.drop_objection(this); */ |

1344 | endtask | | endtask |

1345 | | | |

1346 | | | |

1347 driver | | | |

1348 | | | |

1349 | virtual task run_phase(uvm_phase phase); | | virtual task run_phase(uvm_phase phase); |

1350 | #6 */ | | #6 |

1351 | phase.raise_objection(this); | |/* phase.raise_objection(this); */ |

1352 | #15; */ | | #15; |

1353 | phase.drop_objection(this); | |/* phase.drop_objection(this); */ |

1354 | endtask | | endtask |

1355 ----------------------------------------------------- -------------------------------------------------

1356

1357 class solution

1358

1359 /*Suppose a component raise a objection | simulator will terminate run_phase at zero

1360 but not droped that objection ????? | simulation time */

1361 in that .case simulator will give fatal error | at time = 0 ns atleast one component should raise

1362 after certain time that is timeout condition | an objection

1363

1364 endclass

1365

1366

1367

1368

1369

1370

1371

1372

1373

1374

1375

1376

1377

1378

1379 test

1380 -----------------------------------------------------

1381 | virtual task run_phase(uvm_phase phase); |

1382 | #1; |

1383 | phase.raise_objection(this); |

1384 | #10; |

1385 | /* #5; */ |

1386 |/* phase.drop_objection(this); */ |

1387 | endtask |

1388 | |

1389 | |

1390 driver | |

1391 | |

1392 | virtual task run_phase(uvm_phase phase); |

1393 | #6 */ |

1394 | phase.raise_objection(this); |

1395 | #15; */ |

1396 | phase.drop_objection(this); |

1397 | endtask |

1398 -----------------------------------------------------

1399

1400

1401 class solution

1402

1403 simulator will terminate run_phase at zero simulation .time

1404

1405 at time = 0 ns atleast one component should raise an

1406 objection

1407

1408 endclass

1409

1410 endclass

1411

1412

1413

1414

1415

1416

1417

1418

1419

1420 ------------------------------------------------=====================---------------------------------------------

1421 //===============================================REPORTING MECHANISM==============================================

1422 ------------------------------------------------=====================---------------------------------------------

1423 class

1424

1425 1. IT is used to display message on terminal according to verbosity level

1426

1427 //Why Reporting Mechanism over $display ?????

1428 =============================================

1429 1.It can filter display message manually

1430 2.We can enable/disable certain message from MakeFile without going back to tb.and change it in code

1431 3.We can give severity here

1432 eg. fatal,error,warning,info etc.

1433 4.We can call reporting mechanism by.function or UVM Macros(recommended).

1434 5.During developing tb we want certain messages and after completing TB, We don't want these messages so we

1435 can simply filter out using verbosity levels.

1436

1437

1438 /* virtual function void uvm_report_info(string id,

1439 string message,

1440 int verbosity=UVM_HIGH,

1441 string filename="",

1442 int line=0);

1443 */

1444 $display("THIS IS DRIVER CLASS");

1445

1446 Instead of using $display we use

1447

1448 uvm_report_info("DRIVER","THIS IS DRIVER CLASS",UVM_MEDIUM,driver,20);

1449

1450 ID: We can give any string here

1451 MESSAGE: We can give any message

1452 VERBOSITY: verbosity to filter out

1453 FILENAME: .class name

1454 LINE NO: line no

1455

1456 It is very tough to track line no. everytime as an argument here, so coz of this we use uvm_macros.

1457

1458 `uvm_info("DRIVER","THIS IS DRIVER CLASS",UVM_MEDIUM)

1459

1460 this macro again call method ----> uvm_report_info only

1461

1462 but whenever it is calling it is able to provide the.class name and line no.

1463

1464 / 2. uvm_report_warning 3. uvm_report_error 4.uvm_report_fatal

1465

1466 virtual function void uvm_report_warning(string id,

1467 string message,

1468 int verbosity=UVM_NONE,

1469 string filename="",

1470 int line=0);

1471

1472 virtual function void uvm_report_error(string id,

1473 string message,

1474 int verbosity=UVM_NONE,

1475 string filename="",

1476 int line=0);

1477

1478 virtual function void uvm_report_fatal(string id,

1479 string message,

1480 int verbosity=UVM_NONE,

1481 string filename="",

1482 int line=0);

1483

1484 */

1485

1486 ===================

1487 //SEVERITY MACROS:

1488 ===================

1489

1490 It is very tough to track line no. everytime as an argument here, so coz of this we use uvm_macros.

1491

1492 In Macros only 3 arguments we need to pass

1493 1.id

1494 2.message

1495 3.verbosity

1496

1497 UVM Reporting provides Macros to embed report messages. Followings are the Macros to be used:

1498

1499 `uvm_info (string ID, string MSG, verbosity);

1500 `uvm_error (string ID, string MSG);

1501 `uvm_warning(string ID, string MSG);

1502 `uvm_fatal (string ID, string MSG);

1503

1504 1. It is not recommended to filter out warning,fatal and error messages

1505 2. By default for warning,fatal,error verbosity is UVM_NONE So third argument verbosity no need to pass

1506

1507 `uvm_info(string ID, string MSG, verbosity=UVM_MEDIUM);

1508

1509 Example: `uvm_info("DRIVER","Driver data",UVM_MEDIUM);

1510

1511

1512 //OUTPUT:

1513 .==========================================================================================.

1514 |/* file_name time scope ID Message */|

1515 | _____________|_____________ _|_ ________|__________ ___|____ ____|______ |

1516 | UVM_INFO../wr_agt_top/ram_wr_driver.sv(50)@0:top.wr_agt_agth.drvh [DRIVER] Driver data |

1517 | | | |

1518 |/* severity line_no*/ |

1519 '=========================================================================================='

1520

1521 TIP: get_type_name() --> returns id of the .class type

1522 instead of giving type id which is .class name generally we can use method get_type_name().

1523

1524 TO DISABLE File name and Line no we use command ---> +define+UVM_REPORT_DISABLE_FILE_LINE in command line

1525

1526 //OUTPUT:

1527 // time scope ID Message

1528 _|_ ________|__________ ___|____ ____|______

1529 UVM_INFO../@0:top.wr_agt_agth.drvh [DRIVER] Driver data

1530 |

1531 // severity

1532 =============

1533 //VERBOSITY:

1534 =============

1535

1536 Printing message can be controlled by giving different verbosity

1537

1538 by default verbosity is UVM_MEDIUM

1539 It is an enum data type defined in liabrary .class itself.

1540

1541 typedef enum{UVM_NONE=0, UVM_LOW=100, UVM_MEDIUM=200, UVM_HIGH=300, UVM_FULL=400, UVM_DEBUG=500}

1542 uvm_verbosity;

1543

1544 .***********************************************************************************************************.

1545 |/* IMPORTANT: We are not suppossed to use verbosity UVM_DEBUG it used for debugging UVM liabrary classes */|

1546 |/* if we give this as verbosity so many messages will get displayed. */|

1547 '***********************************************************************************************************'

1548

1549 .============.

1550 | VERBOSITY |

1551 |============|

1552 | UVM_NONE |

1553 | UVM_LOW |

1554 | UVM_MEDIUM |-------> Set the verbosity

1555 | UVM_HIGH | UVM_MEDIUM,UVM_LOW & UVM_NONE will print

1556 | UVM_FULL | UVM_HIGH & UVM_FULL will be ignored

1557 '------------'

1558

1559 Suppose we set default verbosity UVM_LOW so it will display only UVM_LOW and UVM_NONE but in scoreboard we

1560 want to display messages with UVM_MEDIUM verbosity also

1561 then it can be done by

1562

1563 //set_report_verbosity_level(verbosity);

1564 =======================================

1565

1566 env.sb.set_report_verbosity_level(UVM_MEDIUM);

1567

1568

1569 ==================================

1570 //MODIFY SIMULATOR DEFAULT ACTION:

1571 ==================================

1572

1573 As mentioned above, UVM allows to bind a Reporting Severity with a particular valid Simulator Action.

1574 Usually its done inside the start_of_simulation() phase.

1575

1576 Actions can be assigned using set_report_*_action() functions.

1577 These can be done for one or all in the priority order from lowest to highest.

1578

1579 .---------------------------------------------------------.

1580 /*BY SEVERITY:*/ | set_report_severity_action(Severity, Action); | //[Lowest Priority]

1581 /*BY ID*/ | set_report_id_action(ID, Action); |

1582 /*BY BOTH*/ | set_report_severity_id_action(Severity, ID, Action); | //[Highest Priority]

1583 '---------------------------------------------------------'

1584 //EXAMPLE:

1585

1586

1587

1588

1589

1590

1591

1592 ==============================

1593 //LOGGING INTO SEPERATE FILE:

1594 ==============================

1595

1596 For suppose in driver.class want to display all the message of severity as an UVM_ERROR

1597 instead of showing them in terminal we want to log into a seperate file

1598

1599 drv.set_report_severity_action(UVM_ERROR,UVM_LOG+UVM_EXIT);

1600

1601 SEVERITY: UVM_ERROR

1602 ACTION : UVM_LOG+UVM_EXIT ---> log into seperate file and exit

1603

1604 So for Log into seperate file

1605

1606 1. First we need to open a file

1607 default_fd = $fopen("default_file","w"); // w --> write permission

1608

1609

1610 TEST

1611 BUILD_PHASE

1612

1613 warning_fd = $fopen("warning_file","w");

1614

1615 // BASED ON SEVERITY:

1616 ------------------

1617 env.sb.set_report_severity_file(UVM_WARNING,warning_fd);

1618

1619 env.sb.set_report_severity_action(UVM_WARNING,UVM_LOG);

1620

1621 // BASED ON ID:

1622 -------------

1623 env.sb.set_report_id_file("SB",warning_fd);

1624

1625 env.sb.set_report_id_action("SB",UVM_LOG);

1626

1627 // BASED ON SEVERITY_ID:

1628 ---------------------

1629 env.sb.set_report_severity_id_file(UVM_WARNING,"SB",warning_fd);

1630

1631 env.sb.set_report_severity_id_action(UVM_WARNING,"SB",UVM_LOG);

1632

1633

1634

1635 ========================================

1636 //SETTING VERBOSITY FROM COMMAND LINE:

1637 ========================================

1638 One of the biggest advantage of the controlling Verbosity level from the command line is that we don’t need to re-

1639 compile the Design & Testbench if we want to change the .generate different log information from our next simulation

1640 run.

1641

1642 The simplest option is the command line switch:

1643

1644 +UVM_VERBOSITY=<verbosity>

1645

1646 eg.

1647

1648 % simv +UVM_VERBOSITY=UVM_HIGH

1649

1650 //NOW LETS SEE BELOW SOME MORE ADVANCED VERBOSITY SETTING FROM THE COMMAND LINE:

1651

1652 If you find the messages from a simulation run is extremely verbose, the simulation can be re-run with command line

1653 switches to filter some of the noise that appears on the our screen and log:

1654

1655 +uvm_set_verbosity=<comp>,<id>,<verbosity>,<phase>

1656

1657 eg.

1658

1659 To change the verbosity level to UVM_LOW for the uvm_test_top.env.agnt.drv instance with ID as DRV during the run

1660 phase, which would suppress all the messages with verbosity setting of UVM_MEDIUM or higher, execute the following

1661 command:

1662

1663 % simv +UVM_TESTNAME=test1 +uvm_set_verbosity=uvm_test_top.env.agnt.drv,DRV,UVM_LOW,run

1664

1665

1666 .=========================================. .=======================================================.

1667 |/* Severity ||Default Simulator Action*/| | Simulator Action | Description |

1668 .=========================================. .===================.===================================.

1669 | UVM_FATAL | UVM_DISPLAY + UVM_EXIT | | UVM_EXIT | Exit from simulation immediately |

1670 | UVM_ERROR | UVM_DISPLAY + UVM_COUNT | | UVM_COUNT | Increment globar error count |

1671 | UVM_WARNING | UVM_DISPLAY | | UVM_DISPLAY | Display message on console |

1672 | UVM_INFO | UVM_DISPLAY | | UVM_LOG | Capture message in a named file |

1673 '--------------'--------------------------' | UVM_CALLBACK | Calls callback methods |

1674 | UVM_NO_ACTION | Do nothing |

1675 '-------------------'-----------------------------------'

1676

1677 endclass

1678 ---------------------------------------------===========================------------------------------------------

1679 //============================================TRANSACTION LEVEL MODELING==========================================

1680 ---------------------------------------------===========================------------------------------------------

1681 class

1682

1683 //WHY TLM ?????

1684 ================

1685

1686 1. TLM Stands for Transaction Level MODELING

1687 2. TLM Promoted Re-usability as they have same .interface

1688 3. Interoperability for mixed language verification environment

1689 4. Maximizes reuse and minimize the time and effort

1690

1691

1692

1693 //WHAT IS TLM ??

1694 ================

1695

1696 1. Messsage passing system

1697 2. TLM Interface

1698 1. Ports- set of methods Ex. Get(), Put(), Peek() etc

1699 2. Exports/Imp- Implementation for the METHODS

1700

1701

1702

1703

1704

1705 PORT: 1.In a initiator you will have a port with port we call the method.

1706 eg. get_port or put_port

1707

1708 -> Denoted by square

1709 -> If component is initiator and sending the data then it should have put_port

1710 -> If component is initiator and recieving the data then it should have get_port

1711 -> Port always parametrize by single parameter which is transaction type

1712 (write_xtn)

1713

1714 IMPLEMENTATION PORT: 2.get(),put() methods are implemented by the implementation port inside the target

1715 eg. get_imp or put_imp

1716 -> put()/get() method should be implemented by imp_ports otherwise it will give

1717 error.

1718 -> Denoted by circle(O)

1719 -> imp_port always parametrize by two parameter which is transaction type

1720 (write_xtn) & .class name in which put/get method is implemented

1721

1722 EXPORT: 3. It will not implement any method

1723

1724 TLM FIFO: 4. Both are initiator here and Generator sending the data so it should have put_port

1725 -> Driver recieving the data so it should have get_port

1726 -> TLM_FIFO have put_export & get_export

1727 -> Methods like get(), put(), peek() etc are implemented inside TLM_FIFO

1728

1729 ANALYSIS PORT: 4. Denoted by diamond/rhombus symbol

1730 --> One to Many connection

1731 --> It acts like a Broadcaster

1732 --> Analysis port may be connected to zero, one or many analysis_export

1733 --> Analysis port has single write() method

1734 --> If analysis_export not implemented write() method in target then it won't

1735 give any error

1736

1737 ANALYSIS FIFO: 5. Analysis fifo have analysis_imp port and write() method is implemented here

1738

1739

1740 //It does not matter who is initiator wether driver or generator data always come from generator

1741

1742 RE-USABILITY:-

1743 --------------

1744 /*Let's suppose we want to call the put method which is inside the driver,

1745 what we can do is declare handle of driver inside generator and call it, but by doing this

1746 we can't use same generator for another driver, so here we use this put_port method*/

1747

1748 //Port and Implementation Port should parametrized by same transaction otherwise compatiblity issue occur,

1749 it will not work.

1750

1751

1752 // In SV MAILBOX is Target and GENERATOR, DRIVER both are initiator because mailbox have put and get

1753 methods.

1754

1755 /*Soppose here in UVM Both are initiator what we will do then ??????

1756 -> We use TLM_FIFO

1757 */

1758

1759

1760

1761

1762

1763

1764 ---------------------------------------------------=============--------------------------------------------------

1765 //===================================================TLM PORTS===================================================

1766 ---------------------------------------------------=============--------------------------------------------------

1767 class

1768 =====================

1769 // BLOCKING GET PORT:

1770 =====================

1771 //AHB GENERATOR:(Target)

1772 -------------------------

1773

1774 class ahb_gen extends uvm_component;

1775

1776 uvm_blocking_get_imp

1777 #(write_xtn,ahb_gen) get_imp;

1778 //2 parameter

1779 virtual task get(output write_xtn t);

1780 write_xtn tmp = new();

1781 //assign value to tmp

1782 t=temp;

1783 endtask

1784 endclass

1785

1786 //AHB DRIVER:(Initiator)

1787 -------------------------

1788

1789 class ahb_driver extends uvm_component;

1790 uvm_blocking_get_port#(write_xtn) get_port;

1791 // 1 parameter

1792 function new(string name,uvm_component parent);

1793 super.new(name,parent);

1794 get_port = new("get_port",this);

1795 endfunction

1796

1797 virtual task run_phase(uvm_phase phase);

1798 write_xtn t;

1799 for(int i=0;i<N;i++);

1800 begin

1801 //generate t

1802 get_port.get(t); //It invoke get method inside generator

1803 end

1804 endtask

1805 endclass

1806

1807 //How driver will know that from which generator class the get() method should it call ??????

1808 --> Through the connection between driver and generator which we did in environment

1809

1810 =====================

1811 // BLOCKING PUT PORT:

1812 =====================

1813

1814 //APB GENERATOR:(Initiator)

1815 ----------------------------

1816 class apb_gen extends uvm_component;

1817 uvm_blocking_put_port#(write_xtn) put_port;

1818 //1 parameter

1819 function new(string name,uvm_component parent);

1820 super.new(name,parent);

1821 put_port = new("put_port",this);

1822 endfunction

1823

1824 virtual task run_phase(uvm_phase phase);

1825 write_xtn t;

1826 for(int i=0;i<N;i++);

1827 begin

1828 //generate t

1829 put_port.put(t); //It invoke put method inside driver

1830 end

1831 endtask

1832 endclass

1833

1834 //APB DRIVER:(Target)

1835 ----------------------

1836

1837 class apb_driver extends uvm_component;

1838 uvm_blocking_put_imp

1839 #(write_xtn,apb_driver) put_imp;

1840 //2 parameter

1841 virtual task put(input write_xtn t);

1842

1843 case(t.kind)

1844 READ: //Do read

1845 WRITE: //Do write

1846 endcase

1847 endtask

1848

1849 endclass

1850 ========================

1851 //CONNECTING TLM PORTS:

1852 ========================

1853

1854 --> When connecting components at the same level of hierarchy, port are always connected to export

1855 eg. ___.port.connect(___.export)

1856

1857 --> When connecting port to implementation port ,port are always connected to implementation port

1858 eg. ___.port.connect(___.imp_port)

1859

1860

1861 class my_env extends uvm_env;

1862 //GET

1863 ahb_gen ahb_genh;

1864 ahb_driver ahb_drvh;

1865

1866 //PUT

1867 apb_gen apb_genh;

1868 apb_driver apb_drvh;

1869

1870 function void connect(uvm_phase phase);

1871

1872 ahb_drvh.get_port.connect(ahb_genh.get_imp); //Driver(Initiator)--->Generator(Target)

1873 apb_genh.put_port.connect(apb_drvh.put_imp); //Generator(Initiator)--->Driver(Target)

1874

1875 endfunction

1876

1877 endclass

1878

1879

1880 endclass

1881

1882

1883

1884

1885

1886

1887

1888

1889

1890

1891

1892

1893 ---------------------------------------------------============---------------------------------------------------

1894 //===================================================TLM FIFO:===================================================

1895 ---------------------------------------------------============---------------------------------------------------

1896 class

1897

1898 1. Both are initiator here and Generator sending the data so it should have put_port

1899 2. Driver recieving the data so it should have get_port

1900 3. TLM_FIFO have put_export & get_export

1901 4. Methods like get(), put(), peek() etc are implemented inside TLM_FIFO

1902

1903 Producer puts the transaction into uvm_tlm_fifo, while consumer gets the transaction from fifo.

1904

1905 uvm_tlm_fifo#(write_xtn) fifoh;

1906

1907

1908

1909 //APB GENERATOR:(Initiator)

1910 ----------------------------

1911

1912 class apb_gen extends uvm_component;

1913 uvm_blocking_put_port#(write_xtn) put_port;

1914

1915 function new(string name,uvm_component parent);

1916 super.new(name,parent);

1917 put_port = new("put_port",this);

1918 endfunction

1919

1920 virtual task run_phase(uvm_phase phase);

1921 write_xtn t;

1922 for(int i=0;i<N;i++);

1923 begin

1924 put_port.put(t);

1925 end

1926 endtask

1927 endclass

1928

1929

1930

1931

1932

1933

1934

1935

1936 //APB DRIVER:(Initiator)

1937 -------------------------

1938

1939 class apb_driver extends uvm_component;

1940 uvm_blocking_get_port#(write_xtn) get_port;

1941

1942 function new(string name,uvm_component parent);

1943 super.new(name,parent);

1944 get_port = new("get_port",this);

1945 endfunction

1946

1947 virtual task run_phase(uvm_phase phase);

1948 write_xtn t;

1949 for(int i=0;i<N;i++);

1950 begin

1951 //generate t

1952 get_port.get(t); //It invoke get method inside TLM FIFO

1953 end

1954 endtask

1955 endclass

1956

1957 //APB_AGENT:(CONNECTION)

1958 --------------------------

1959 class apb_agent extends uvm_component;

1960

1961 apb_gen apb_genh;

1962 apb_driver apb_drvh;

1963

1964 uvm_tlm_fifo#(write_xtn) fifoh;

1965

1966 function new(string name, uvm_component parent);

1967 super.new(name,parent);

1968 fifoh = new("fifoh",this);

1969 endfunction

1970

1971 function void connect_phase(uvm_phase phase);

1972

1973 apb_genh.put_port.connect(fifoh.put_export);

1974 apb_drvh.get_port.connect(fifoh.get_export);

1975

1976 endfunction

1977

1978 endclass

1979

1980 INCASE WE DON'T WANT TO USE FIFO THEN:

1981

1982 //TARGET CLASS

1983 ---------------

1984

1985 class target extends uvm_component;

1986

1987 uvm_blocking_get_imp#(write_xtn,target) get_imp;

1988 uvm_blocking_put_imp#(write_xtn,target) put_imp;

1989

1990 virtual task put(input write_xtn t);

1991

1992 case(t.kind)

1993 READ: //Do read

1994 WRITE: //Do write

1995 endcase

1996

1997 endtask

1998

1999 virtual task get(output write_xtn t);

2000 write_xtn tmp = new();

2001 //assign value to temp

2002 tmp.addr = 15;

2003 tmp.data = 16;

2004

2005 t = tmp;

2006 endtask

2007

2008 endclass

2009

2010 **********WARNING*******

2011 //These get and put method in target should implemented in such a way data should be first in first out

2012 //We declare handle of target class in a class in which driver and initiator enclosed and do connection

2013 //we do not need to write those methods It is already defined inside uvm_tlm_fifo class

2014

2015

2016

2017

2018

2019

2020

2021

2022 //TLM FIFO METHODS

2023 ====================

2024

2025 1. new()

2026 This is a constructor method used for the creation of TLM FIFO

2027

2028 function new (string name,

2029 uvm_component parent,

2030 int size=1

2031 );

2032 endfunction

2033

2034 The name and parent are the normal uvm_component constructor arguments

2035 The size indicates the maximum size of the FIFO; a value of zero indicates no upper bound

2036

2037 2. size() --> Calling size() returns the size of the FIFO

2038 A return value of 0 indicates the FIFO capacity has no limit

2039

2040 3. used() --> Returns the number of entries put into the FIFO

2041

2042 4. is_empty() --> Returns 1 when there are no entries in the FIFO, 0 otherwise

2043

2044 5. is_full() --> Returns 1 when the number of entries in the FIFO is equal to its size, 0 otherwise

2045

2046 6. flush() --> Calling flush method will Remove all entries from the FIFO

2047 after the flush method call used method returns 0 and the is_empty method returns 1

2048

2049 endclass

2050

2051

2052

2053

2054

2055

2056

2057

2058

2059

2060

2061

2062

2063

2064

2065 -------------------------------------------------=================------------------------------------------------

2066 //=================================================ANALYSIS PORT=================================================

2067 -------------------------------------------------=================------------------------------------------------

2068 class

2069

2070 --> Denoted by diamond/rhombus symbol

2071 --> One to Many connection

2072 --> It acts like a Broadcaster

2073 --> Analysis port may be connected to zero, one or many analysis_export

2074 --> Analysis port has single write() method

2075 --> If analysis_export not implemented write() method in target then it won't get any error

2076

2077

2078

2079

2080

2081 //APB MONITOR:

2082 ---------------

2083

2084 class apb_mon extends uvm_component;

2085 uvm_analysis_port#(write_xtn) ap_h;

2086

2087 function new(string name, uvm_component parent);

2088 super.new(name,parent);

2089

2090 ap_h = new("ap_h",this);

2091

2092 endfunction

2093

2094 task run_phase(uvm_phase phase);

2095

2096 write_xtn t;

2097 forever

2098 begin

2099 //Sample interface signals

2100 t.addr = vif.addr;

2101 t.data = vif.data;

2102 t.wr = vif.wr;

2103

2104 ap_h.write(t); //write transaction

2105 end

2106 endtask

2107 endclass

2108 //SCOREBOARD:

2109 -------------

2110

2111 class scoreboard extends uvm_scoreboard;

2112 uvm_analysis_imp#(write_xtn,scoreboard) analysis_imph;

2113

2114 function void write(write_Xtn xtn);

2115 //record coverage information of xtn

2116 endfunction

2117

2118 endclass

2119

2120

2121

2122 //ENVIRONMENT(CONNECTION):

2123 ----------------------------

2124

2125 class my_env extends uvm_env;

2126

2127 apb_mon apb_monh;

2128 scoreboard sbh;

2129 cov_collector covh;

2130

2131 function void connect_phase(uvm_phase phase);

2132

2133 apb_monh.ap_h.connect(sbh.analysis_imph);

2134 apb_monh.ap_h.connect(covh.analysis_imph);

2135

2136 endfunction

2137 endclass

2138

2139 endclass

2140