0 ratings0% found this document useful (0 votes)

84 viewsOverview of Electronic Packaging Evolution

Overview of Electronic Packaging Evolution

Uploaded by

Allen SuThis document summarizes the evolution of electronic packaging technology from the 1960s to the 2000s. It describes key milestones such as the development of TO packages in the 1960s, the rise of DIPs and early PGAs in the 1970s, the dominance of QFPs in the 1980s, the introduction of BGA and CSP concepts in the 1990s, and more advanced packaging technologies emerging in the 2000s like SiP and 3D WLP. The document traces how packaging has pursued smaller sizes and higher densities to meet the needs of semiconductors and electronic products over the decades.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Overview of Electronic Packaging Evolution

Overview of Electronic Packaging Evolution

Uploaded by

Allen Su0 ratings0% found this document useful (0 votes)

84 views2 pagesThis document summarizes the evolution of electronic packaging technology from the 1960s to the 2000s. It describes key milestones such as the development of TO packages in the 1960s, the rise of DIPs and early PGAs in the 1970s, the dominance of QFPs in the 1980s, the introduction of BGA and CSP concepts in the 1990s, and more advanced packaging technologies emerging in the 2000s like SiP and 3D WLP. The document traces how packaging has pursued smaller sizes and higher densities to meet the needs of semiconductors and electronic products over the decades.

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

This document summarizes the evolution of electronic packaging technology from the 1960s to the 2000s. It describes key milestones such as the development of TO packages in the 1960s, the rise of DIPs and early PGAs in the 1970s, the dominance of QFPs in the 1980s, the introduction of BGA and CSP concepts in the 1990s, and more advanced packaging technologies emerging in the 2000s like SiP and 3D WLP. The document traces how packaging has pursued smaller sizes and higher densities to meet the needs of semiconductors and electronic products over the decades.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

84 views2 pagesOverview of Electronic Packaging Evolution

Overview of Electronic Packaging Evolution

Uploaded by

Allen SuThis document summarizes the evolution of electronic packaging technology from the 1960s to the 2000s. It describes key milestones such as the development of TO packages in the 1960s, the rise of DIPs and early PGAs in the 1970s, the dominance of QFPs in the 1980s, the introduction of BGA and CSP concepts in the 1990s, and more advanced packaging technologies emerging in the 2000s like SiP and 3D WLP. The document traces how packaging has pursued smaller sizes and higher densities to meet the needs of semiconductors and electronic products over the decades.

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1of 2

Overview of Electronic Packaging Evolution

108033113 Youtin Su

Power Mechanical Engineering Dept.

National Tsing Hua University

Abstract: In this report, we introduce the 2. 1970s

evolution of electronic packaging technology 2.1. Era of DIPs

over time, including packaging from early In 1960s, TO with leads was used for IC,

time to CSP packaging. but with the I/O pins increased, the round

body of TO was no longer suitable. The

Keywords: Packaging, TO, PTH, DIP, SIP, rectangular appearance of DIP, which can

SMT, QFP, SOP, BGA, CSP. increase I/O pins with simple layout, and the

density of the components made DIP a

Introduction: With the rapid development mainstay of the industry in 1970s.

of the semiconductor industry, IC chips

become smaller and smaller, but require 2.2. first PGA

more and more I/Os. This situation forces the Musashi Semiconductor Works is

electronic packaging technology to upgrade Hitachi Corporation's oldest and largest

and meet the requirements. Since the TOP semiconductor factory. The first PGA (pin

(transistor outline package) was first used in grid array) was developed at Musashi Works

1960s, packaging technology has been in 1974, which has 52-pin and higher

continuously innovated. Realizing the mounting efficiency.

history of package is necessary and important.

2.3. first QFP

1. 1960s As mentioned before, Musashi Works

1.1. Era of TO not only developed the first PGA but also

On December 16, 1947, William give birth to the first QFP (quad flat package)

Shockley, John Bardeen, and Walter Brattain in 1977, which was called FPP (flat plastic

succeeded in making the first transistor at package) when it was first developed. The

Bell Labs. With the application of transistors, first QFP was 14mm in width, 20mm in

TO packaging technology has begun to length, and 2mm in thickness.

develop and be used in 1960s.

3. 1980s

1.2. first DIP 3.1. Era of QFPs

The first DIP (dual in-line package) was With the demand for memory products

invented by Don Forbes, Rex Rice, and and portable devices grew, DIP with dual

Bryant Buck Rogers of Fairchild sides and the PTH (pin through hole)

Semiconductor in 1964, which had 14 leads. mechanism couldn’t meet the needs. QFP

had two major advantages. Due to the 5. 2000s

quadruple sides of QFP, the package outline 5.1 Era of Advanced Packaging

of QFP became smaller than that of DIP. It In 2000s, with the increase in the

allowed QFP to contain more I/Os in same requirement of electronic product

area. Also, with the mechanism of SMT performance and the integration of functions,

(surface mount technology), which QFP packaging become more and more advanced,

featured, it enabled us to package on both including SiP (system in package), FCBGA

sides of PCB boards. QFP has better (flip chip ball grid array), WLCSP(wafer

dimension efficiency than DIP and SOP level chip size package), 3D WLP (3

(small out-line package), which made it a dimensional wafer level package), FO-WLP

mainstream technology in 1980s. (Fan-Out wafer level package), FO-PoP

(Fan-Out package on package), Embedded

4. 1990s SiP, etc.

4.1. Era of BGA

The research of BGA (ball grid array) 6. Conclusion

started in 1960s. However, it didn’t enter the Packaging technology has been

market until early 1990s. BGA is a kind of pursuing small size and high efficiency, such

area array technology. When the demand as changing from dual sides to quadruple

came to hundreds of I/Os, the pitch between sides, or from planer to 3D. From the past to

pin needs to be smaller, which increase the the present, many packaging methods have

difficulty of production. Furthermore, the been invented, some are still in use, and some

previous fine lead was easy to bend. With have been eliminated by time, so when we try

BGA design, it eliminates the production to design a new packaging method, finding

difficulty and warping defects but also an approach can stand the test of time is our

improve the performance by low inductance best choice.

pins.

7. References

4.2. CSP concept 1. https://polymerinnovationblog.com/pol

Junichi Kasai of Fujitsu Limited, ymers-electronic-packaging-

Kawasaki, Japan, and Gen Murakami of introduction-flip-chip-packaging/

Hitachi Cable proposed the concept of CSP 2. https://anysilicon.com/semiconductor-

(chip size package) in 1992. CSP has 2 packaging-history-trends/

meaning, one for chip size package and the 3. https://ieeexplore.ieee.org/author/3795

other is chip scale package. For chip scale 8612800

package, the area of packaging is usually not 4. https://www.shmj.or.jp/english/packagi

greater than 1.2 times the area of the die. ng/pac70s.html

In late 1990s, CSP started mass production 5. https://www.youtube.com/watch?v=F

due to its less area than BGA. Y5V600ceuU

You might also like

- Alif E1 Datasheet v2.5-1Document161 pagesAlif E1 Datasheet v2.5-1alex.gurioNo ratings yet

- Parametric On-Chip Variation A Step Towards Accurate Timing AnalysisDocument12 pagesParametric On-Chip Variation A Step Towards Accurate Timing AnalysisRoshan RajuNo ratings yet

- stk412 240 PDFDocument1 pagestk412 240 PDFluisclaudio3170% (10)

- Kef psw2010 SMDocument12 pagesKef psw2010 SMjohara8067% (3)

- LDICA Digital NotesDocument263 pagesLDICA Digital NotesAbhishek Reddy Garlapati80% (5)

- Walking Marching GallopingDocument8 pagesWalking Marching Gallopingembedhw100% (1)

- Unersampling LectureDocument16 pagesUnersampling Lecturenoopreply5316No ratings yet

- Lecture 11. Delay Testing (Students)Document102 pagesLecture 11. Delay Testing (Students)rakhi0070No ratings yet

- Lecture 1. Introduction PDFDocument112 pagesLecture 1. Introduction PDFAmandeep VaishNo ratings yet

- Primer: IEEE STD 1149.1 (JTAG) TestabilityDocument130 pagesPrimer: IEEE STD 1149.1 (JTAG) TestabilityteomondoNo ratings yet

- Intel Shows: - How A CPU Is MadeDocument33 pagesIntel Shows: - How A CPU Is MadeStanislaus LasradoNo ratings yet

- Preview of Introduction To IDDQ TestingDocument20 pagesPreview of Introduction To IDDQ TestingywkaiNo ratings yet

- ATPG and Fault Simulation: Alberto BosioDocument63 pagesATPG and Fault Simulation: Alberto BosioAdb dizonNo ratings yet

- Design For Testability (DFT) For A Chip - HBRP PublicationDocument10 pagesDesign For Testability (DFT) For A Chip - HBRP Publicationkarthikp207No ratings yet

- Gaisler Research IP LibraryDocument1,055 pagesGaisler Research IP LibraryrazvanvgNo ratings yet

- 1149 6 Tutorial Test Ac Coupled Differential NetsDocument17 pages1149 6 Tutorial Test Ac Coupled Differential Netsthao nguyen leNo ratings yet

- VLSI Anna University New Syllabus 2013Document33 pagesVLSI Anna University New Syllabus 2013princeram123No ratings yet

- 4 BistDocument165 pages4 Bistpravallika vysyarajuNo ratings yet

- 8B-4 MOS TransistorDocument4 pages8B-4 MOS TransistorkammohNo ratings yet

- Ahb-Lite To Apb Protocol: BY Shraddha Devaiya EC - 018 Anand Therattil EC - 092Document29 pagesAhb-Lite To Apb Protocol: BY Shraddha Devaiya EC - 018 Anand Therattil EC - 092AnandNo ratings yet

- 1500 Core WrapperDocument22 pages1500 Core WrapperprabhavkumarnitcNo ratings yet

- How Microprocessors Work 23Document13 pagesHow Microprocessors Work 23nafeesNo ratings yet

- DFT For SRAMDocument9 pagesDFT For SRAMsuneeldvNo ratings yet

- Boundary Scan, JTAG, IEEE 1149.1 TutorialDocument6 pagesBoundary Scan, JTAG, IEEE 1149.1 Tutorialmelvin45No ratings yet

- Smartscan - Hierarchical Test Compression For Pin-Limited Low Power DesignsDocument43 pagesSmartscan - Hierarchical Test Compression For Pin-Limited Low Power DesignsjagruthimsNo ratings yet

- TestingDocument23 pagesTestingsangeethabgNo ratings yet

- DFTDocument4 pagesDFTkienukiru100% (1)

- Hspice Simulation ManualDocument694 pagesHspice Simulation Manualapi-26731722100% (1)

- On The Detectability of Scan Chain Internal Faults - An Industrial Case StudyDocument6 pagesOn The Detectability of Scan Chain Internal Faults - An Industrial Case StudynagarjunaNo ratings yet

- 05 Fault ModelsDocument38 pages05 Fault Modelsv chandrasekharNo ratings yet

- Fault Types and Models: Pathak Anushri Roll No.:208Document4 pagesFault Types and Models: Pathak Anushri Roll No.:208Dissen_cNo ratings yet

- Soc DesignDocument42 pagesSoc Designmaharajm98No ratings yet

- VLSI Design and TestingDocument2 pagesVLSI Design and TestingsirapuNo ratings yet

- Thorough Test Means Testing Through The RAMDocument2 pagesThorough Test Means Testing Through The RAMpreety100inNo ratings yet

- DFT-the Easier Way To Test Analog ICsDocument9 pagesDFT-the Easier Way To Test Analog ICsnishantsoni90100% (1)

- EE 5316 - Phase Locked Loop - ArchDocument17 pagesEE 5316 - Phase Locked Loop - ArchSharath_Patil_7623No ratings yet

- Tmax 2017.09 LGDocument121 pagesTmax 2017.09 LGrajitkarmakarNo ratings yet

- Syi EDGRQtup ZKN NMDocument130 pagesSyi EDGRQtup ZKN NMshashindra KGNo ratings yet

- Enhanced Broadside Testing For Improved Transition Fault CoverageDocument6 pagesEnhanced Broadside Testing For Improved Transition Fault CoverageKishore ThatiNo ratings yet

- Electronic Syatem Design PPT - Design For TestabilityDocument9 pagesElectronic Syatem Design PPT - Design For TestabilityAnoop Mathew0% (1)

- UNIT01 Defects and YieldDocument42 pagesUNIT01 Defects and YieldraghudatheshNo ratings yet

- Jtag - AN IEEE 1149.1 STDDocument42 pagesJtag - AN IEEE 1149.1 STDkanchanstiwariNo ratings yet

- How To Use JTAG With ARM7 MCUDocument20 pagesHow To Use JTAG With ARM7 MCUGurpreet SinghNo ratings yet

- Low Power Atpg For Path Delay FaultsDocument6 pagesLow Power Atpg For Path Delay Faultsemail2pr2639No ratings yet

- False Path Multicycle PathDocument7 pagesFalse Path Multicycle Pathjagneswar.dharuaNo ratings yet

- Ec1354 Vlsi by Suresh.mDocument75 pagesEc1354 Vlsi by Suresh.mSuresh Muthu100% (1)

- Viraj N SLB-IIDocument45 pagesViraj N SLB-IIViraj NevrekarNo ratings yet

- Creating A TDR Inside The IJTAG Network by Reading in The DftSpecification For The TDR Using The Read - Config - Data CommandDocument3 pagesCreating A TDR Inside The IJTAG Network by Reading in The DftSpecification For The TDR Using The Read - Config - Data Command魏宇No ratings yet

- Test Programming An ATE For Diagnosis - 2015Document30 pagesTest Programming An ATE For Diagnosis - 2015Mahmoud WafaNo ratings yet

- A Reconfigurable High Speed Dedicated BISR Scheme For Repair Intra Cell Faults in Memories.Document15 pagesA Reconfigurable High Speed Dedicated BISR Scheme For Repair Intra Cell Faults in Memories.Editor IJTSRDNo ratings yet

- Thesis On LFSRDocument104 pagesThesis On LFSRKaran RoyNo ratings yet

- TN005 Reset Synchronization v00Document6 pagesTN005 Reset Synchronization v00Brahmam MadamanchiNo ratings yet

- Vlsi FabDocument8 pagesVlsi FabhaheNo ratings yet

- JTAGDocument19 pagesJTAGSantosh Kumar DadiNo ratings yet

- VlsiDocument13 pagesVlsiRajaganapathi RajappanNo ratings yet

- Application-Specific Integrated Circuit ASIC A Complete GuideFrom EverandApplication-Specific Integrated Circuit ASIC A Complete GuideNo ratings yet

- Topic 1 Dec50143Document65 pagesTopic 1 Dec50143hazlindaidrisNo ratings yet

- Dual In-Line Package: ApplicationsDocument5 pagesDual In-Line Package: ApplicationsDhenish MariyaNo ratings yet

- Integrated Circuits Lecture NotesDocument9 pagesIntegrated Circuits Lecture NotesJoanna Fabricante100% (2)

- Package Information 1. Package ClassificationsDocument25 pagesPackage Information 1. Package ClassificationsClarisse GambotaNo ratings yet

- Integrados ToshibaDocument27 pagesIntegrados ToshibaPablo JavierNo ratings yet

- The Common-Base Amplifier Basic Circuit: BB + 2 1 1 2 BB 1 2 EE E CC + CC C BE BB EE C C BB BE C EEDocument8 pagesThe Common-Base Amplifier Basic Circuit: BB + 2 1 1 2 BB 1 2 EE E CC + CC C BE BB EE C C BB BE C EEdominggoNo ratings yet

- D1KPro Schematic Ver.4aDocument2 pagesD1KPro Schematic Ver.4aWahyudi100% (3)

- H20R1353 InfineonDocument15 pagesH20R1353 InfineonMinh TiếnNo ratings yet

- STLD Lab ManualDocument37 pagesSTLD Lab Manualvenkata satishNo ratings yet

- Introduction To Second Order Circuit: Natural Response of RLC CircuitDocument34 pagesIntroduction To Second Order Circuit: Natural Response of RLC CircuitSyed AbdullahNo ratings yet

- Phys 3102Document23 pagesPhys 3102myo htetNo ratings yet

- 74HC193Document15 pages74HC193jnax101No ratings yet

- LM339, LM239, LM139, LM2901 Quad Differential Comparators: 1 Features 3 DescriptionDocument33 pagesLM339, LM239, LM139, LM2901 Quad Differential Comparators: 1 Features 3 DescriptionIslam El-saiedNo ratings yet

- Running Message DisplayDocument1 pageRunning Message DisplayGarima Lakhanpal100% (1)

- 04-MB-4 Version Anglaise - Mai 2014Document4 pages04-MB-4 Version Anglaise - Mai 2014LuisAranaNo ratings yet

- Pic 16 LF 1574Document332 pagesPic 16 LF 1574SUPER ENGINEERING WORKSNo ratings yet

- Orange Encoder 360 PPR ManualDocument2 pagesOrange Encoder 360 PPR Manualscada.wupptclNo ratings yet

- Blood Glucose DetectorDocument18 pagesBlood Glucose DetectorKIZZA RONALDNo ratings yet

- Diode DetectorDocument3 pagesDiode DetectorkaibilsamNo ratings yet

- Amplifier TBA820MLDocument5 pagesAmplifier TBA820MLaeaccorp1224No ratings yet

- RGPV Syllabus Cbgs Ec 3 Sem All SubjectsDocument8 pagesRGPV Syllabus Cbgs Ec 3 Sem All SubjectsAyushNo ratings yet

- Digi QBDocument68 pagesDigi QBAlvin Jan YapNo ratings yet

- TL 074Document10 pagesTL 074Alexandre S. CorrêaNo ratings yet

- The Integrating A/D Converter (ICL7135) : Application Note February 1999Document5 pagesThe Integrating A/D Converter (ICL7135) : Application Note February 1999ytnateNo ratings yet

- Nokia Ultrasite BTS: Company ConfidentialDocument19 pagesNokia Ultrasite BTS: Company Confidentiallukelar100% (1)

- Software Defined Radio Lec 3 - RF Front-End For SDR: Sajjad Hussain, Mcs-NustDocument40 pagesSoftware Defined Radio Lec 3 - RF Front-End For SDR: Sajjad Hussain, Mcs-NustAamir HabibNo ratings yet

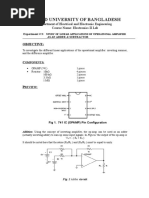

- World University of Bangladesh: ObjectiveDocument3 pagesWorld University of Bangladesh: ObjectiveshajibNo ratings yet

- Asa2310 High-Speed TMR Analog Front-End 1piDocument2 pagesAsa2310 High-Speed TMR Analog Front-End 1piMohammed Abdul HamidNo ratings yet

- Universal Shift RegisterDocument33 pagesUniversal Shift RegisterAayush Yadav100% (1)

- Efm8bb1 DatasheetDocument57 pagesEfm8bb1 DatasheetManuel Jesus Delgado LaraNo ratings yet

- EXPERIMENT No 5 - MuX and DeMuxDocument6 pagesEXPERIMENT No 5 - MuX and DeMuxSaksham Dhawan100% (1)