了解内存

- 1. 了解内存 核心系统数据库组 余锋 http://yufeng.info @淘宝褚霸 2012-03-17 1

- 2. 内存体系变更 过去 现在 2

- 3. 服务器内存条 3

- 4. 内存总体信息 Memory: 31.5GB / 32GB 1333MHz DDR3 == 8 x 4GB - 4GB PC3- 10600 Samsung DDR3-1333 ECC Registered CL9 2Rx8 4

- 5. 单条内存信息 asset="02120761" speed="1333MHz" cas="9" type="DDR3" form="DIMM" width="72 bits“ handle="76" part_number="M393B5273CH0- locator="DIMM_A1" YH9“ org=“x8” pretty="4GB PC3-10600 Samsung ranks="2" DDR3-1333 ECC Registered CL9 2Rx8” serial="87BE9BB9" size="4096 MB" 5

- 6. 模组型号解读 M393B5273CH0-YH9 DIMM、x72 240pin Registered、2Gb颗粒、x8位 宽、第四代产品、无铅无汞 FBGA封装、1.35V低电压、 DDR3-1333 6

- 7. 功耗 7

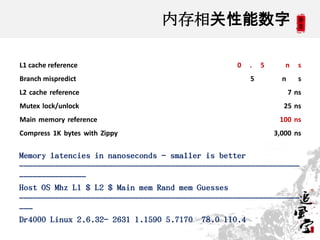

- 8. 内存相关性能数字 L1 cache reference 0 . 5 n s Branch mispredict 5 n s L2 cache reference 7 ns Mutex lock/unlock 25 ns Main memory reference 100 ns Compress 1K bytes with Zippy 3,000 ns Memory latencies in nanoseconds - smaller is better --------------------------------------------------------------- --------------- Host OS Mhz L1 $ L2 $ Main mem Rand mem Guesses --------------------------------------------------------------- --- Dr4000 Linux 2.6.32- 2631 1.1590 5.7170 78.0 110.4 8

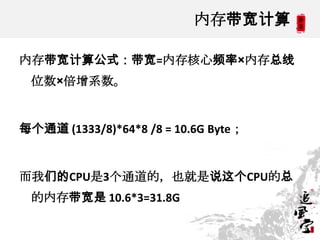

- 9. 内存带宽计算 内存带宽计算公式:带宽=内存核心频率×内存总线 位数×倍增系数。 每个通道 (1333/8)*64*8 /8 = 10.6G Byte; 而我们的CPU是3个通道的,也就是说这个CPU的总 的内存带宽是 10.6*3=31.8G 9

- 10. QPI和内存通道理论带宽 10

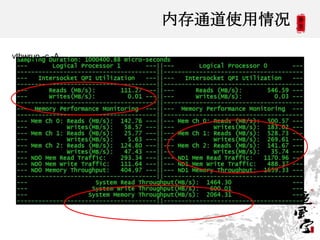

- 11. 内存通道使用情况 vtbwrun -c -A 11

- 12. NUMA节点内存访问速度差异 12

- 13. DRAM总体位置 13

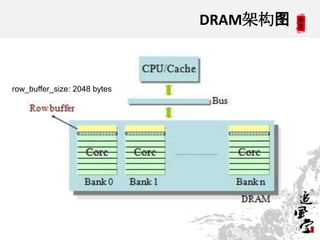

- 14. DRAM结构图 14

- 16. DRAM 访问流程 • Precharge: charge a DRAM bank before arow access • Row access: activate a row (page) of a DRAM bank • Column access: select and return a block of data in an activated row • Refresh: periodically read and write DRAM to keep data 16

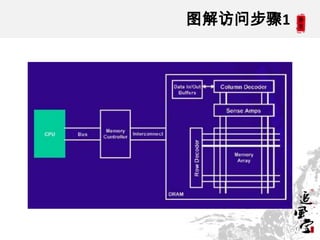

- 17. 图解访问步骤1 17

- 18. 图解访问步骤2 18

- 19. 图解访问步骤3 19

- 20. 图解访问步骤4 20

- 21. 图解访问步骤5 21

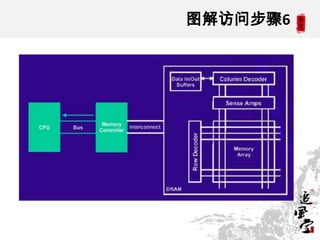

- 22. 图解访问步骤6 22

- 23. DRAM bank选择 23

- 24. DRAM访问延时分布 24

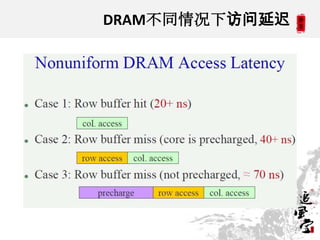

- 25. DRAM不同情况下访问延迟 25

- 26. DRAM延时演化 26

- 27. 参考 • http://en.wikipedia.org/wiki/Prefetch_buffer • 详解服务器内存带宽计算和使用情况测量: http://blog.yufeng.info/archives/1511 • DDR3 内存带宽如何计算: http://zhidao.baidu.com/question/107154668 • hwconfig查看硬件信息: http://blog.yufeng.info/archives/2086 • Exploiting Locality in DRAM, Xiaodong Zhang 27

- 28. 提问时间 谢谢大家! 28