高速シリアル通信を支える技術

- 2. アジェンダ 自己紹介 高速シリアル通信とは バス規格のおさらい 高速シリアル通信で使われている技術 作動信号 CDR(クロックデータリカバリ) 8B/10Bエンコーディング Elasticバッファ 特に出典を書いていない図表は、「Xilinx 7 シリーズ FPGA GTP トラ ンシーバー UG482 (v1.0) 2012 年 1 月 3 日」から引用しています。

- 3. 自己紹介 夏谷実 パソナテック勤務 エンジニアリング事業部 西日本エンジニアリ ンググループ ブログ ぱたヘネ http://d.hatena.ne.jp/natsutan/

- 4. 高速シリアル通信とは 1ペアの作動信号のみで通信する技術 数100Mbps~数Gbps以上 信号数が少ないため、ケーブルや基板を小型化 できる 使われているところ PCI-Express SATA Infiniband Xilinx Whitepaper WP431 (v1.0) Figure 5 イメージ図

- 5. 物理的形状の比較 http://www.atmarkit.co.jp/fsys/kaisetsu/047pe1800/pe1800.html ①⑤が64bit PCI 133MHz×64bit = 約8.5Gbps ②③がPCI-e x8 2.5G × 8 lane = 20Gbps PowerEdge 1800

- 6. PC周辺規格の進化 非同期 同期 多重化 高速シリアル PCI- Express ISA PCI シリア ルポー ト USB USB 3.0 SCSI SATA DRAM SDRAM DDR VGA DVI ATA CLK DATA 多重化(x4)

- 7. 高速シリアル通信で使われている技術 自己紹介 高速シリアル通信とは バス規格のおさらい 高速シリアル通信で使われている技術 作動信号 CDR(クロックデータリカバリ) 8B/10Bエンコーディング Elasticバッファ

- 8. FPGA2FPGA1 セパレートクロック方式 OSC1 OSC2 PLL(x20) PLL(x20) TX 125MHz 125MHz2.5GHz 2.5GHz ・今回想定しているクロック系統図 ・両方のFPGAにそれぞれOSCの出力を入力している。 ・FPGA内部のPLLで20倍のクロックを作成している。 ・基板上でケアする部分が少ない。 ・詳しくは後で 125MHz RX TX RX 2.5GHz 2.5GHz125MHz

- 10. ①作動信号 ①作動信号

- 13. ②クロックデータリカバリ 受信データ E0 E 1 E2 D0 D 1 D2 データの変化点から、クロックを作り出し、変化点の真ん中でサンプリングを 行う データが変化しない時はどうするの? ⇒ 後で 送信クロッ ク (基板上に は存在しな い) リカバリされ た クロック

- 14. ②クロックデータリカバリ a) 受信データから変化点を抜き出す b) 抜き出したデータから受信用のクロック(Recovered Clock)の 生成 c) 受信用のクロックから、データを再サンプリング a b c

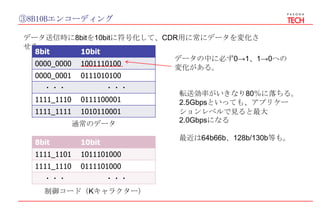

- 16. ③8B10Bエンコーディング データ送信時に8bitを10bitに符号化して、CDR用に常にデータを変化さ せる。 8bit 10bit 0000_0000 1001110100 0000_0001 0111010100 ・・・ ・・・ 1111_1110 0111100001 1111_1111 1010110001 8bit 10bit 1111_1101 1011101000 1111_1110 0111101000 ・・・ ・・・ 制御コード(Kキャラクター) 通常のデータ データの中に必ず0→1、1→0への 変化がある。 転送効率がいきなり80%に落ちる。 2.5Gbpsといっても、アプリケー ションレベルで見ると最大 2.0Gbpsになる 最近は64b66b、128b/130b等も。

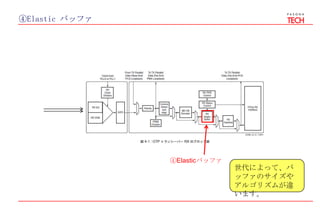

- 18. FPGA2FPGA1 ④Elasticバッファ OSC1 OSC2 PLL(x20) PLL(x20) TX 125MHz 125MHz2.5GHz 2.5GHz ・クロック再び ・両方のFPGAにそれぞれOSCの出力を入力している。 ・FPGA内部のPLLで20倍のクロックを作成している。 ・基板上でケアする部分が少ない。 125MHz RX

- 19. ④Elasticバッファ 書込み 125MHz (Recovered Clock) 源振: 送信側の基板に実装さ れているOSC 読出し 63 0 125MHz 源振: 受信側の基板に実装 されているOSC Elastic Buffer 64エントリーのリングバッファ 125.000・・・・ MHz?

- 24. まとめ 高速シリアル通信で使われている技術 作動信号 CDR(クロックデータリカバリ) 8B/10Bエンコーディング Elasticバッファ

- 25. 宣伝