Cited By

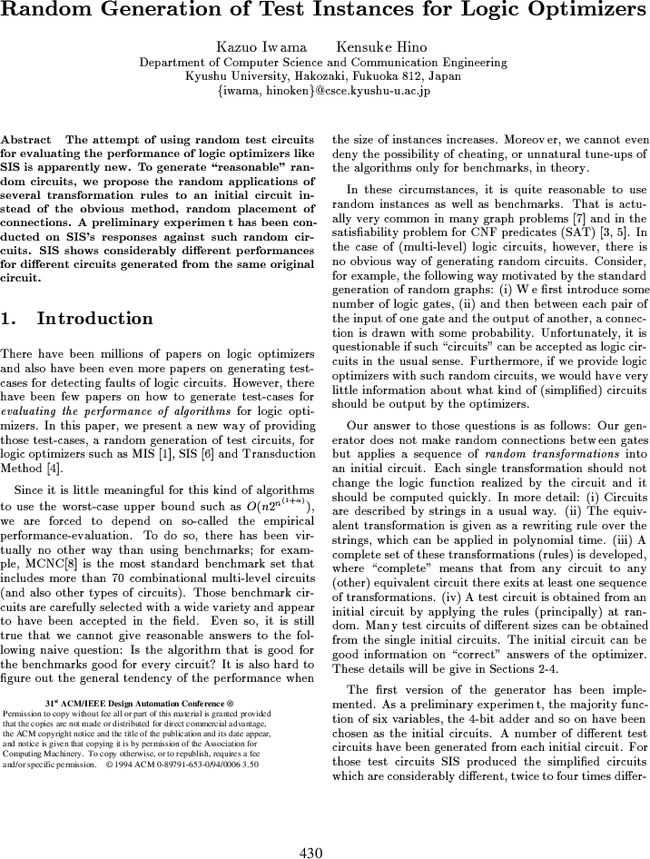

View all- Li BLin R(2022)Scalable Synthetic Circuit Generation using Geometry Embedding for CAD Tool Assessment2022 IEEE International Symposium on Circuits and Systems (ISCAS)10.1109/ISCAS48785.2022.9937638(3239-3243)Online publication date: 28-May-2022

- Vela ACruz-Duarte JOrtiz-Bayliss JAmaya I(2021)Tailoring Job Shop Scheduling Problem Instances Through Unified Particle Swarm OptimizationIEEE Access10.1109/ACCESS.2021.30764269(66891-66914)Online publication date: 2021

- Kundarewich PRose J(2006)Synthetic circuit generation using clustering and iterationIEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems10.1109/TCAD.2004.82813223:6(869-887)Online publication date: 1-Nov-2006

- Show More Cited By