Cited By

View all- Ranjan ASrivastava AKarnam VSarrafzadeh MRoy KKang SKoh C(2001)Layout aware retimingProceedings of the 11th Great Lakes symposium on VLSI10.1145/368122.368153(25-30)Online publication date: 1-Mar-2001

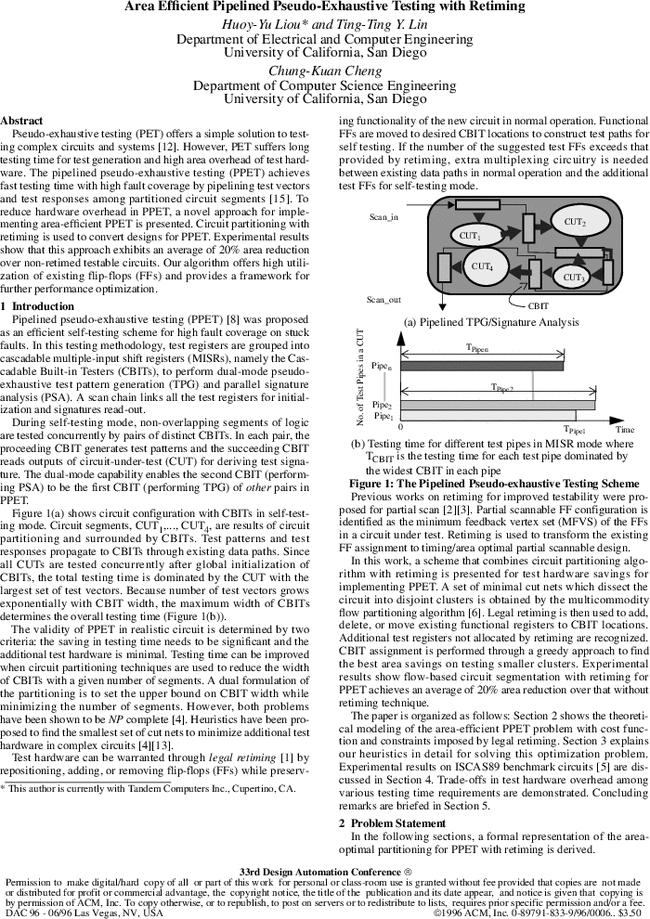

Abstract: In pseudo-exhaustive testing, the partitioning technique consists of placing segmentation cells in an acyclic sequential circuit in order to reduce the size of cones. These segmentations, which are transparent in normal mode and active during ...

In this paper, a new two's complement radix-2n area-efficient digit serial divider is presented. The proposed digit serial divider is designed by cascading N (wordlength) digital controlled add/subtract DCAS cells where each cell is used to generate one ...

Association for Computing Machinery

New York, NY, United States

Check if you have access through your login credentials or your institution to get full access on this article.

Sign in