Corrigé BTS SE 2009

Corrigé BTS SE 2009

Transféré par

Essaid AjanaDroits d'auteur :

Formats disponibles

Corrigé BTS SE 2009

Corrigé BTS SE 2009

Transféré par

Essaid AjanaDescription originale:

Copyright

Formats disponibles

Partager ce document

Partager ou intégrer le document

Avez-vous trouvé ce document utile ?

Ce contenu est-il inapproprié ?

Droits d'auteur :

Formats disponibles

Corrigé BTS SE 2009

Corrigé BTS SE 2009

Transféré par

Essaid AjanaDroits d'auteur :

Formats disponibles

CORRIGÉ

Partie A : Fréquence d'échantillonnage du signal ECG

Q1. bande passante : 0,5Hz à 40Hz

fcard_mini en battements par minute : 30bpm

durée minimum du motif QRS : 20ms

dV dV

Q2. = A ⋅ ω ⋅ cos(ωt ) ⇒ = A ⋅ ωmax ⋅1 = A ⋅ 2 ⋅ π ⋅ f max

dt dt max

dV

pendant la phase QRS : dV = 2.A, dt = 10ms soit = 0,2 ⋅ A(V / ms)

dt max

dV 0,2 ⋅ A 1

= A ⋅ 2 ⋅ π ⋅ f max = 0,2 ⋅ A soit f max = = = 31,83Hz

dt max 2 ⋅ A ⋅ π 10 ⋅ π ⋅ 10 − 3

Q3. fe = 448Hz > 2*100Hz donc le théorème de SHANNON est respecté.

f scld _ clk 1,892352 ⋅ 106

Q4. fo = = = 59,136kHz

32 32

f

f e = scld _ clk = 4224 ⇒ f scld _ clk = 4224 ⋅ f e

448

Partie B : Génération du signal 448HZ (micro programmation)

TMOD = 0b00000110 ; TCON = 0b00010000 ; TH0 = 0xBE

Q5. le timer/compteur 0 fonctionne en compteur et dans le mode 2.

TMOD.0 M0 Timer 0 mode selector bit.

TMOD.1 M1 Timer 0 mode selector bit.

C/T Selects Timer0 or Counter0 operation. When set to 1, the Counter operation

TMOD.2 C/T

is performed, when cleared to 0, the register will function as a Timer.

BTS Systèmes Électroniques

Session 2009

Épreuve U4.1- Électronique Page C1 sur 10

9SEE4EL1CORR Corrigé

Gestion de la division à l’aide d’un sous-programme d’interruption

Q6. la division de fréquence étant réalisé par U29.

Sachant que la fréquence d’entrée de HT0 est f o = 59,136kHz et que la fréquence doit être de

448Hz sur P1.4, la division de fréquence doit être de 132.

f0 59136

= = 132

448 448

Comme l’on charge la valeur de départ du compteur et qu’il va évoluer jusqu’à 255 (compteur 8

bits), on peut déduire facilement la valeur de chargement souhaité.

132

256 - = 190

2

Soit 190 en décimal (BE en héxa) a charger dans le registre TH0.

Q7.

1 TCON = TCON & 0b11011111 ; // remise à zéro du drapeau d’interruption TF0

2 if ( (P1 & 0b00010000) == 0x00) ; // test de l’état logique de P1.4 (448Hz)

3 {

4 P1 = P1 | 0b00010000 ; // mettre à 1 la patte P1.4 (448Hz)

5 }

6 else

7 {

8 P1 = P1 & 0b11101111 ; // mettre à 0 la patte P1.4 (448Hz)

9 }

10 rti; //retour du sous programme

Q8.

HT0

t

TL0 190 191 192 193 253 254 255 190 191 253 254 255 190 1

t

TF0

t

448HZ

t

Partie C : Détection des électrodes débranchées

Q9. démultiplexage 1 vers 8.

Q10.

SEL3 SEL2 SEL1 SEL0

0 0 0 1

BTS Systèmes Électroniques

Session 2009

Épreuve U4.1- Électronique Page C2 sur 10

9SEE4EL1CORR Corrigé

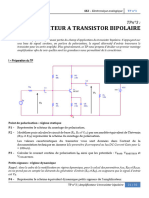

U15

+7V

14 3 2k

20k

22,1k 10nF

2,3V

connecteur

HEF4051B ICM U18

14 13

100M R0

0,0mV -

100M

100M

10k

-9,3mV

+

23nA VCM

U17A

-3,1mV I0 -9,3mV HEF4052

câble 46nA - VLAB

LA 34k 100k LAD 301k

+

ILA 220pF 68pF 68pF

U14D RAB 20k 20k

LAB

-3,1mV 0,0mV

23nA

k

20

20

RA - VRAB

k

34k 100k RAD 301k

+

IRA 220pF 68pF

0,0mV

68pF

U14B

IICM IIICM

k

20

20

k

0,0mV

-3,1mV états

23nA LL - VLLB LLB logiques

34k 100k LLD 301k

+

ILL 220pF 68pF 68pF

U14C -

0,0mV 20k

+

LA_FAULT 0

10nF

U23A

20k

-

RA_FAULT

0

+

+7V 10nF

U23C

1,5k

20k

-

LL_FAULT 0

+

20k

k

10nF

1,5

1,5

patient 0,6V U23B

k

VREF

1N4148

100nF

électrodes

Q11. voir schéma ci-dessus.

2,3 - 0 2,3

Q12. IO = = = 23nA

RO 100MΩ

Q13. voir schéma ci-dessus.

Q14. Étant donné que la différence de potentiel VRAD est égale à 2,3V (IRA = OA), alors en sortie de

U14B VRAB est égale 2,3V.

VRAB - VLLB

VIICM = ⇒ VLLB = VRAB - 2 ⋅ VIICM

2

AN : VLLB = -2,3 - 2 * 0 = -2,3V

Q15. voir schéma page suivante.

Q16. voir schéma page suivante.

Q17. Une sortie au niveau haut indique un défaut sur l’électrode correspondante.

BTS Systèmes Électroniques

Session 2009

Épreuve U4.1- Électronique Page C3 sur 10

9SEE4EL1CORR Corrigé

U15

+7V

14 3 2k

20k

22,1k 10nF

2,3V

connecteur

HEF4051B ICM U18

14 60 13

100M R0

0,0mV -

100M

100M

-2,3V

10k

+

46nA VCM

U17A

-2,3V I0 -2,3V HEF4052

câble 46nA - VLAB

LA 34k 100k LAD 301k FS17

+

ILA 220pF 68pF 68pF

U14D RAB 20k 20k

LAB

2,3V 2,3V

OnA

k

20

VRAB FS15

20

RA -

k

34k 100k RAD 301k

+

IRA 220pF 68pF

2,3V

68pF

U14B

IICM IIICM

k

20

20

k

-2,3V -2,3V états

46nA LL - VLLB LLB logiques

34k 100k LLD 301k

+

ILL 220pF 68pF

-2,3V

68pF

U14C 20k

-

+

LA_FAULT 0

10nF

U23A

20k

-

RA_FAULT 1

+

+7V 10nF

U23C

1,5k

-

20k LL_FAULT 0

+

20k

k

10nF

1,5

1,5

patient 0,6V U23B

k

V REF

100nF

électrodes

Partie D : Acquisition d'une voie d'électrocardiogramme

Q18.

relation entre V2 et V1 : V2 = 10 ⋅ V1 ⇒ G1 (f ) = 20dB

ème

type du 2 étage G 2 (f) : le continu passe l'étage, mais pas les fréquences élevées : c'est donc un filtre

passe Bas.

ème

type du 3 étage G 3 (f) : le continu ne traverse pas l'étage, de même que les fréquences élevées :

c'est donc un filtre passe bande.

Q19. G(f) = 20log (| A(f) |) = G1(f) + G2(f) + G3(f)

Q20. Avec les valeurs relevées sur les graphes, on trouve A(f) = 10 G1(f) + G2(f) + G3(f) = 10 ( 20+ 2+33) = 560 .

Et sur | A(f) | , on relève 580. on constate des valeurs légèrement différentes dues à la précision

de mesure.

Q21. calcul préalable de l’amplification a -3dB.

580

| A(f) | à - 3dB = = 410

2

voir graphe page suivante.

BTS Systèmes Électroniques

Session 2009

Épreuve U4.1- Électronique Page C4 sur 10

9SEE4EL1CORR Corrigé

G1 (f) dB

G 2 (f) dB

G 3 (f) dB

A (f )

580

410

60 fmin = 0,045Hz fmax = 40Hz

f = fe/2

BTS Systèmes Électroniques

Session 2009

Épreuve U4.1- Électronique Page C5 sur 10

9SEE4EL1CORR Corrigé

Q22. la bande passante sur la courbe va de 0,045Hz à 40Hz. Dans la documentation, il faut une bande

passante de 0,05Hz à 100Hz ±10%. La structure satisfait à la doc. constructeur du module ECG.

Q23. À 224Hz, on trouve l’amplification égale à 60 (voir graphe page précédente). Par rapport à

l’amplification dans la bande passante (580), on en déduit que l’affaiblissement est de :

60

= 0,103 ⇒ 20 ⋅ log(0,103) = −19,7dB

580

L’affaiblissement est bien supérieur au 6dB demandé.

Ce filtre élimine le repliement du spectre.

Q24.

sélection voie I voie II

256µs

+4V

VMUXOUT

0V t

VTRIANGLE

-4V

TH

VPWM +5V

0V

Q25. Évaluer graphiquement la durée à l'état haut TH

Voie sélectionnée Voie I Voie II

Tension VMUXOUT 0V 2V

TH 128µs 64µs

Q26. Calculer les coefficients a et b de l'équation TH = a ⋅ VMUXOUT + b .

Pour calculer a et b, on a deux point de la courbe :

er

1 point : 128µs = a ⋅ 0 + b ⇒ b = 128µs

64 - 128 - 64

2

ème

point : 64µs = a ⋅ 2 + b ⇒ a = = ⇒ a = -32µs / V

2V 2V

Équation finale : TH(µs) = -32 ⋅ VMUXOUT + 128

Q27. ∆TH = a ⋅ ∆q

AN : ∆TH = -32 ⋅ 2 ⋅ 10 −3 V = -64ns

BTS Systèmes Électroniques

Session 2009

Épreuve U4.1- Électronique Page C6 sur 10

9SEE4EL1CORR Corrigé

Partie E : Numérisation du signal ECG et sortie analogique

amplifiée (signal HLO)

Q28. mode 4 quadrants.

Q29. VREF = 2,5V

Q30. application du théorème de Millman par exemple :

- Vref ⋅ N

VHLO Vref

+ + 4096 - Vref ⋅ N

R R 245 R 248 V V

0 = 242 ⇒ HLO + ref + 4096 = 0

1 1 1 R 242 R 245 R 248

+ +

R 242 R 245 R 248

- Vref ⋅ N

VHLO Vref V ⋅ N R 242 R

=- - 4096 ⇒ VHLO = ref ⋅ - Vref ⋅ 242

R 242 R 245 R 248 4096 R 248 R 245

2,5 ⋅ N 267 ⋅103 267 ⋅103

AN : VHLO = ⋅ - 2,5 ⋅

4096 42,2 ⋅103 82,5 ⋅103

N

VHLO = 15,8 ⋅ - 8,1

4096

Q31.

Minimum Maximum

N 0 4096

VHLO -8,1 7,7

Q32. voir graphe Q36.

Q33. un front montant sur /WR6 permet l'écriture de la donnée à convertir dans le(s) registre(s) de

conversion choisi(s).

Q34. A368

Q35.

Rang du bit 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Valeur binaire 1 0 1 0 0 0 1 1 0 1 1 0 1 0 0 0

BTS Systèmes Électroniques

Session 2009

Épreuve U4.1- Électronique Page C7 sur 10

9SEE4EL1CORR Corrigé

Q36.

Extrait du listing du programme de test

MOV AX,0xA368

OUT 0x300,AX

Chronogrammes associés à l'éxécution de ces 2 instructions

instruction instruction

MOV AX,0xA368 OUT 0x300,AX

CLKOUT

ALE

AD[15:0] 0x0300 0xA368

/PCS6

/WR

/WR6

N XXX

A36

N

Q37. VHLO = 15,8 ⋅ - 8,1 avec N = A36(hex) = 2614( dec )

4096

2614

AN : VHLO = 15,8 ⋅ - 8,1 = 1,98V

4096

Partie F: Transfert des données d'ECG au moniteur

Q38. voir ci-dessous

CH1

CH1 : 2V/div

CH2 : 2V/div

MATH : 1V/div

0V CH1, CH2

TIME : 100ns

+0,2v

0V MATH -0,2v

SDLC_CLK

BTS Systèmes Électroniques

Session 2009

Épreuve U4.1- Électronique Page C8 sur 10

9SEE4EL1CORR Corrigé

Q39. voir graphe précédent.

Q40. voir graphe précédent.

Q41. la mesure de la période sur le graphe est de :

1

Tmesuré = 100ns ⋅ 5,3carreaux = 530ns ⇒ d binaire mesuré = = 1,886792Mbit / s

530.10 − 9

d binaire s tan dard = 1,892352Mbit / s .

d binaire s tan dard ≈ d binaire mesuré ⇒ Les deux débit binaire sont voisin l’un de l’autre.

Q42. c’est le moniteur qui délivre les signaux CLK+ et CLK-.

Q43. « half duplex » : les périphérique « parle à tour de rôle » donc la transmission ne se fait que dans

un seul sens à la fois.

Q44.

Émetteur Récepteur

Broche 2 Broche 3 Broche 2 Broche 3

1 1 0 0

Q45.

Nom du signal de

Émetteur Récepteur

sélection du mode

RECV_ENAB 0 1

Q46.

RS232 RS485

Liaison asymétrique x

Liaison symétrique (meilleure immunité au bruit) x

Distance liaison < 50m x

Distance liaison < 1km x

Débits < 20 kbauds x

Débits < 10 Mbauds x

Q47.

SDLC_CLK

SDLC_DATA

Q48. et Q49.

SDLC_DATA 1 1 1 1 1 0 1 1 1 1 1 0 1 0 0 1 0 1 1 1 0 0 1 0 1 1 1 1 1 0 1 0 0 1 1

noms des champs adresse destinataire commande | FCS

BTS Systèmes Électroniques

Session 2009

Épreuve U4.1- Électronique Page C9 sur 10

9SEE4EL1CORR Corrigé

Question bârème

Partie A Q1 3,001+1+1

Q2 2,001+1

Q3 2,001+1

Q4 2,001+1

9 points

Partie B Q5 3,00 1.5+1.5

Q6 2,00

Q7 6,00 3*2

Q8 1,50

12,5 points

Partie C Q9 1,00

Q10 3,00 3*1

Q11 2,00 4*0.5

Q12 2,00 1+2*0.5

Q13 1,50

Q14 3,00 1+1+1

Q15 1,50 3*0.5

Q16 1,50 3*0.5

Q17 1,00

16,5 points

Partie D Q18 3,00 1+1+1

Q19 1,00

Q20 2,00

Q21 2,00 0.5+1.5

Q22 1,00

Q23 2,00 0.5+1+0.5

Q24 1,00

Q25 0,50

Q26 1,00

Q27 1,00

14,5 points

Partie E Q28 1,00

Q29 1,00

Q30 2,00

Q31 1,00 2*0.5

Q32 1,00

Q33 1,50

Q34 1,50

Q35 1,00

Q36 1,00

Q37 1,00

12 points

Partie F Q38 1,00

Q39 1,00

Q40 2,00

Q41 1,50

Q42 0,50

Q43 1,00

Q44 2,00

Q45 1,50

Q46 1,50 6*0.25

Q47 1,00

Q48 1,50 3*0.5

Q49 1,00 2*0.5

15,5 points

80,00

BTS Systèmes Électroniques

Session 2009

Épreuve U4.1- Électronique Page C10 sur 10

9SEE4EL1CORR Corrigé

Vous aimerez peut-être aussi

- PLL Exercice CorrectionDocument2 pagesPLL Exercice Correctionintissar abbesPas encore d'évaluation

- TP ElectroniqueDocument14 pagesTP ElectroniqueSoufianeBattal100% (5)

- Diapo OFDMDocument22 pagesDiapo OFDMLE BARON100% (1)

- Iut MC Et2 TDDocument54 pagesIut MC Et2 TDjeremy Burlet0% (1)

- Serie 1Document3 pagesSerie 1feriel aissiPas encore d'évaluation

- Moteur Asynchrone A Cage ManipulationDocument11 pagesMoteur Asynchrone A Cage Manipulationtabdou17Pas encore d'évaluation

- 1990-Photocopieuse Corrigé PDFDocument2 pages1990-Photocopieuse Corrigé PDFChabehou0% (1)

- Td4 PLL Elm CorrDocument4 pagesTd4 PLL Elm Corrمحمد الأمير الحازميPas encore d'évaluation

- TD4 PLL CorrectionDocument7 pagesTD4 PLL CorrectionGhania ZerariPas encore d'évaluation

- Commande Autonome À L'ouverture Et À La Fermeture D'un Transistor de PuissanceDocument4 pagesCommande Autonome À L'ouverture Et À La Fermeture D'un Transistor de Puissancetabdou17100% (1)

- ESA EFF V1 - CorrigeDocument9 pagesESA EFF V1 - Corrigemustapha bougharioun100% (1)

- TD7 PLL CorrectionDocument7 pagesTD7 PLL CorrectionMalick THIAMPas encore d'évaluation

- Oscillateurs TPDocument8 pagesOscillateurs TPMohamed BelaounPas encore d'évaluation

- TP2 PLLDocument8 pagesTP2 PLLRaghadPas encore d'évaluation

- 627 Corrige Bts Se 2010Document9 pages627 Corrige Bts Se 2010etiennePas encore d'évaluation

- Cnc2020 CorrDocument4 pagesCnc2020 Corrab elPas encore d'évaluation

- TP 02Document16 pagesTP 02Belkacem HedadiPas encore d'évaluation

- TP N°3 Generateur D'horloge A Base de Ne555 1Document3 pagesTP N°3 Generateur D'horloge A Base de Ne555 1ahabchPas encore d'évaluation

- TP 05 Co-2022-2023Document3 pagesTP 05 Co-2022-2023Yazid ZitouniPas encore d'évaluation

- Telf TP2 Anane AmghouziDocument6 pagesTelf TP2 Anane Amghouzifirouzanane03Pas encore d'évaluation

- TP GradiateurDocument8 pagesTP GradiateurFiroDjinsoNanoPas encore d'évaluation

- BT 2K14 TechnoDocument2 pagesBT 2K14 Technoniangpapeousmane12Pas encore d'évaluation

- 82 101 CorDocument20 pages82 101 Corcherif yahyaouiPas encore d'évaluation

- Compte Rendu PLL PDFDocument7 pagesCompte Rendu PLL PDFMouhamed AmarPas encore d'évaluation

- Calcul Des Courants de Court-Circuit: N 20 CC J CCDocument5 pagesCalcul Des Courants de Court-Circuit: N 20 CC J CCMehdi IddirPas encore d'évaluation

- Ampli TransistorDocument6 pagesAmpli Transistorchaima2003poshPas encore d'évaluation

- Régulation TORDocument6 pagesRégulation TORabdelgoui rymPas encore d'évaluation

- Chapitre1 PLL 2Document14 pagesChapitre1 PLL 2Ayoub BarcaPas encore d'évaluation

- Circuit CoupleDocument15 pagesCircuit Coupleعالم المعرفةPas encore d'évaluation

- 612b3b2d9563esujet Corrige Turbidimetre Etude Des Systeme TechnDocument40 pages612b3b2d9563esujet Corrige Turbidimetre Etude Des Systeme Technchantalbiyeme01Pas encore d'évaluation

- TP3 Essain Des MachinesDocument10 pagesTP3 Essain Des MachinesSylvainPas encore d'évaluation

- Bts 96Document10 pagesBts 96Professeur BoughrietPas encore d'évaluation

- TP 3Document6 pagesTP 3zakPas encore d'évaluation

- TP Redressement FiltrageDocument12 pagesTP Redressement Filtrageواعر ياسينPas encore d'évaluation

- Générateurs Très Haute Tension Et Séparation Isotopique Par Laser MonomodeDocument27 pagesGénérateurs Très Haute Tension Et Séparation Isotopique Par Laser Monomodeoleg anitoffPas encore d'évaluation

- Chapitre 1 GrafcetDocument6 pagesChapitre 1 GrafcetdarknightPas encore d'évaluation

- TP E. Numérique (EEA)Document38 pagesTP E. Numérique (EEA)Tas ManPas encore d'évaluation

- TP2: Paramètres Du Schéma Équivalent de La Machine AsynchroneDocument9 pagesTP2: Paramètres Du Schéma Équivalent de La Machine AsynchroneFar Idd ag100% (1)

- TP Essai A Vide Sur Un Transformateur Monophasé.Document10 pagesTP Essai A Vide Sur Un Transformateur Monophasé.mkdbilaPas encore d'évaluation

- TP Electronique REDRESSEMENT FILTRAGE Par Armel Sitou AfanouDocument11 pagesTP Electronique REDRESSEMENT FILTRAGE Par Armel Sitou AfanouHamid BendjelloulPas encore d'évaluation

- S2I CCP TSI 2005 GE (Enoncé)Document6 pagesS2I CCP TSI 2005 GE (Enoncé)FZLPas encore d'évaluation

- Raccordement A LelectriciteDocument2 pagesRaccordement A LelectriciteGarcia BourdierPas encore d'évaluation

- TP Electronique REDRESSEMENT FILTRAGE Par Armel Sitou AfanouDocument11 pagesTP Electronique REDRESSEMENT FILTRAGE Par Armel Sitou Afanoukima lachgarPas encore d'évaluation

- t2 Electro2015Document4 pagest2 Electro2015Yahya AidaraPas encore d'évaluation

- TD Optocoupleurs ProfDocument5 pagesTD Optocoupleurs ProfSalah-Eddine NasmiPas encore d'évaluation

- 30W Nrds PDFDocument5 pages30W Nrds PDFpascalb41Pas encore d'évaluation

- Devoir de Synthèse Appareillage 2020-2021Document7 pagesDevoir de Synthèse Appareillage 2020-2021Heni DaoudPas encore d'évaluation

- Ep Unsa Elec4 TP Electronique 03 PLLDocument11 pagesEp Unsa Elec4 TP Electronique 03 PLLAyoub AyayPas encore d'évaluation

- DT1Document6 pagesDT1bobbyuiPas encore d'évaluation

- TP2: Moteur Asynchrone Triphasé Modèle Linéaire: Réaliser Par: Hassine Abir Classe & Filière & GroupeDocument4 pagesTP2: Moteur Asynchrone Triphasé Modèle Linéaire: Réaliser Par: Hassine Abir Classe & Filière & GroupeSarra SdiriPas encore d'évaluation

- TP3 Identification de MCCDocument5 pagesTP3 Identification de MCCBounegab YoucefPas encore d'évaluation

- Fichier PDF CourantDocument21 pagesFichier PDF CourantAli BOUKHRISSPas encore d'évaluation

- Applications Relais MeDocument51 pagesApplications Relais MeBra BicabaPas encore d'évaluation

- CR tp2 CAODocument5 pagesCR tp2 CAOAmina Abir AissaouiPas encore d'évaluation

- TD Rdresseur Code MCCDocument4 pagesTD Rdresseur Code MCCESSADIKE ZAITAPas encore d'évaluation

- Banque de filtres: Aperçu des techniques de banque de filtres de Computer VisionD'EverandBanque de filtres: Aperçu des techniques de banque de filtres de Computer VisionPas encore d'évaluation

- Le syndrome périodique associé à la cryopyrine (CAPS)D'EverandLe syndrome périodique associé à la cryopyrine (CAPS)Pas encore d'évaluation

- Presentation Du ProjetDocument3 pagesPresentation Du ProjetEssaid AjanaPas encore d'évaluation

- 1 Poly Adc Cours Prof 2steDocument79 pages1 Poly Adc Cours Prof 2steEssaid AjanaPas encore d'évaluation

- FR 090914 150215 ME 6vpS5rDocument2 pagesFR 090914 150215 ME 6vpS5rEssaid AjanaPas encore d'évaluation

- Chap2 1Document9 pagesChap2 1Essaid AjanaPas encore d'évaluation

- ANALYSE FONCTIONNELLE Chapitre 1. Comment Décrire Un SystèmeDocument10 pagesANALYSE FONCTIONNELLE Chapitre 1. Comment Décrire Un SystèmeEssaid AjanaPas encore d'évaluation

- Correction Examen Thermodynamique Session 2Document5 pagesCorrection Examen Thermodynamique Session 2Essaid AjanaPas encore d'évaluation

- Serie 2opDocument6 pagesSerie 2opEssaid AjanaPas encore d'évaluation

- Serie 2opDocument6 pagesSerie 2opEssaid AjanaPas encore d'évaluation

- Poly SIDocument120 pagesPoly SIEssaid AjanaPas encore d'évaluation

- TP EclairageDocument6 pagesTP EclairageEssaid AjanaPas encore d'évaluation

- Trans MettreDocument80 pagesTrans MettreEssaid AjanaPas encore d'évaluation

- Thermo Cours ch6 Machines Thermiques 3Document12 pagesThermo Cours ch6 Machines Thermiques 3Essaid AjanaPas encore d'évaluation

- Bts 2008Document43 pagesBts 2008Essaid AjanaPas encore d'évaluation

- 7 SegmentsDocument2 pages7 SegmentsEssaid AjanaPas encore d'évaluation

- Alimentations - À - Decoupage2Document86 pagesAlimentations - À - Decoupage2Essaid AjanaPas encore d'évaluation

- Eleve Store Automatique Act3Document2 pagesEleve Store Automatique Act3Essaid AjanaPas encore d'évaluation

- TP IntensiteDocument4 pagesTP IntensiteEssaid AjanaPas encore d'évaluation

- Cours Mécanique Du SolideDocument33 pagesCours Mécanique Du SolideEssaid AjanaPas encore d'évaluation

- 02 - Séminaire Circuits Séquentielles - GE-FF-S02Document36 pages02 - Séminaire Circuits Séquentielles - GE-FF-S02Lotfi ElaoudPas encore d'évaluation

- Formation STM32 DAC: MAHER BoumizaDocument3 pagesFormation STM32 DAC: MAHER BoumizahelaliPas encore d'évaluation

- CH 01 PIVDocument17 pagesCH 01 PIVAnonymous Qx8YclZ9Pas encore d'évaluation

- Lm380 Sitene (Electronique Pratique 044 Decembre 1981)Document2 pagesLm380 Sitene (Electronique Pratique 044 Decembre 1981)Peeters GuyPas encore d'évaluation

- Série D'exercices N°5-3tech-Compteurs Asynchrones-2013-2014Document4 pagesSérie D'exercices N°5-3tech-Compteurs Asynchrones-2013-2014Barnoussi Chafik100% (3)

- TD07 LesRegistresDocument3 pagesTD07 LesRegistresAhmed Yacine abdelmalekPas encore d'évaluation

- TP2 BasculesV0Document6 pagesTP2 BasculesV0valencemb31Pas encore d'évaluation

- Compte Rendu Éléctronuque TP2Document6 pagesCompte Rendu Éléctronuque TP2Lamyae ChPas encore d'évaluation

- 6 9 SchemasDocument79 pages6 9 Schemasbenoit lemayPas encore d'évaluation

- Le Livre Technique de La BluDocument74 pagesLe Livre Technique de La BluSzilvester SzilvesterPas encore d'évaluation

- COURS CONDENSATEUR Et Dipole RCDocument23 pagesCOURS CONDENSATEUR Et Dipole RCnoull100% (1)

- PDF Cours2Document16 pagesPDF Cours2chabane_148549Pas encore d'évaluation

- Capteur CANDocument21 pagesCapteur CANYorrick Valquin NgouyouPas encore d'évaluation

- Chapitre 3 Logiques CombinatoiresDocument20 pagesChapitre 3 Logiques Combinatoireslilian camillePas encore d'évaluation

- Devoir de Contrôle N°1 - Génie Électrique UNITE DE PERCAGE OLEO-PNEUMATIQUE - Bac Tech (2010-2011) MR Ben AouichaDocument4 pagesDevoir de Contrôle N°1 - Génie Électrique UNITE DE PERCAGE OLEO-PNEUMATIQUE - Bac Tech (2010-2011) MR Ben AouichaHichem HamdiPas encore d'évaluation

- Projet MPIDocument4 pagesProjet MPIhm' ssPas encore d'évaluation

- User Manual Kenwood X700-5 (English - 2 Pages)Document4 pagesUser Manual Kenwood X700-5 (English - 2 Pages)ronaldrivera17Pas encore d'évaluation

- Cours PLL-RMST PDFDocument19 pagesCours PLL-RMST PDFhammoumiPas encore d'évaluation

- TP Filtre Actif L3 Juste Corrige Terminer1 222 TerminerDocument4 pagesTP Filtre Actif L3 Juste Corrige Terminer1 222 TerminerSouna Fatima ZahraPas encore d'évaluation

- Conversion Numérique - Analogique:) 8R A0 + 4R A1 + 2R A2 + R A3 (Vref R' Vs - IDocument2 pagesConversion Numérique - Analogique:) 8R A0 + 4R A1 + 2R A2 + R A3 (Vref R' Vs - Imichel.kouame214Pas encore d'évaluation

- Elect 4Document3 pagesElect 4Mario DelviraPas encore d'évaluation

- Electronique Numérique Niveau Licence 3Document235 pagesElectronique Numérique Niveau Licence 3yayaPas encore d'évaluation

- GELE2442 Notes3Document8 pagesGELE2442 Notes3Voundai Mahamat100% (1)

- Cours Divers en Électronique 2Document11 pagesCours Divers en Électronique 2mhamedsaadi.bachirPas encore d'évaluation

- Correction de L'épreuve1Document5 pagesCorrection de L'épreuve1Dimitry MabomPas encore d'évaluation

- Questions D'entretien Chez Électronique NumériqueDocument21 pagesQuestions D'entretien Chez Électronique NumériqueScribdTranslationsPas encore d'évaluation

- Circuit Couplage Etage HFDocument12 pagesCircuit Couplage Etage HFGloire MATHE-MUKUHIPas encore d'évaluation

- Circuits Csequentiels Partie1Document36 pagesCircuits Csequentiels Partie1Nidal LaatabPas encore d'évaluation

- Untitled 1Document3 pagesUntitled 1Fradj TriplexPas encore d'évaluation

- TP03Document4 pagesTP03dbmariem8Pas encore d'évaluation