Mathais Mebrahtu

Lakehead University, Electrical Engineering, Undergraduate

- Electrical Engineer interested in Power Electronics, Analog Electronics and Power Systems.

Youtube Channel: https://www.youtube.com/channel/UCY5dU2-Iccm1T_qujsDyazgedit

My project involved the use of hardware description language (HDL) to analyze, synthesize and simulate a digital circuit. To accomplish this, Verilog was chosen to model a parallel in serial out (PISO) shift register. Verilog is most... more

My project involved the use of hardware description language (HDL) to analyze, synthesize and

simulate a digital circuit. To accomplish this, Verilog was chosen to model a parallel in serial out

(PISO) shift register. Verilog is most commonly used in the design and verification of digital

circuits. Part of the assignment therefore involved learning the language’s syntax and the use of

industry standard development tools such as Altera’s Quartus II to compile and simulate the given

assignment. We also used online tool called Edaplayground @ http://www.edaplayground.com

to quickly model and test part of our code before inserting it back to Quartus II software.

simulate a digital circuit. To accomplish this, Verilog was chosen to model a parallel in serial out

(PISO) shift register. Verilog is most commonly used in the design and verification of digital

circuits. Part of the assignment therefore involved learning the language’s syntax and the use of

industry standard development tools such as Altera’s Quartus II to compile and simulate the given

assignment. We also used online tool called Edaplayground @ http://www.edaplayground.com

to quickly model and test part of our code before inserting it back to Quartus II software.

Research Interests:

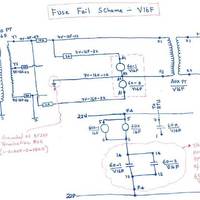

The purpose of the project was to design a high-power inverter to rival that of use in the market in terms of cost and efficiency. The efficiency was the key driving force in the project. The inverter consists of 3 stages: the boost... more

The purpose of the project was to design a high-power inverter to rival that of use in the market in terms of cost and efficiency. The efficiency was the key driving force in the project. The inverter consists of 3 stages: the boost stage, inverter stage, and filter/load stage. The boost stage consists of an isolated DC-DC converter which will take a low DC input supply and boost it to a regulated high DC output. (controlled by PWM signals). The inverter takes the high DC bus from the boost stage and inverts it to a chopped AC, which is filtered to output a pure sine wave. Load testing and efficiency calculations are done on the inverter.