825482C54

825482C54

Uploaded by

Anonymous lubWipsrWCopyright:

Available Formats

825482C54

825482C54

Uploaded by

Anonymous lubWipsrWOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

825482C54

825482C54

Uploaded by

Anonymous lubWipsrWCopyright:

Available Formats

8254/82C54: Introduction to Programmable<BR> Interval Timer

Page 1 of 4

8254/82C54: Introduction to Programmable Interval Timer

WHY IS THE DEVICE NEEDED?

It generates accurate time delays under software control. Instead of setting up timing loops in software, the programmer configures the interval timer to match system requirements and programs the counter for the desired delay or for the desired output. Some common timer/counter/output functions which microprocessors require are: real time clock, event counter, digital one-shot, programmable rate generator, square wave generator, binary rate multiplier, complex wave form generator, and complex motor control.

HOW DOES IT WORK?

BASIC OPERATION: 1. The user inputs a control word and then an initial count. The Control Word itself specifies which Counter is being programmed and which counting Mode is desired. 2. Counting is enabled via the GATE input. 3. Either at the end of a count or during the count, transitions occur on the Counter OUT pin. 4. These OUT pin transitions are used to do things in the system. 5. The types of OUT pin transitions depend on the Mode which was programmed.

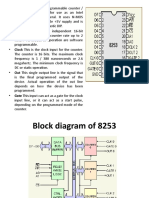

MAJOR DEVICE BLOCKS:

DATA BUS BUFFER: 1. 3-state, bi-directional, 8-bit buffer. 2. Interfaces the 8254 to the system bus. READ/WRITE LOGIC BLOCK: 1. the Read/Write Logic Block accepts inputs from the system bus and generates control signals for the other functional blocks of the 8254. 2. A1 and A0 select one of the three counters or the Control Word Register to be read from or written into. 3. A low on RD# tells the 8254 that the CPU is reading one of the counters. 4. A low on WR# tells the 8254 that the CPU is writing either a Control Word or an initial count. 5. Both RD# and WR# are qualified by CS#. CONTROL WORD REGISTER: 1. This register is selected by the Read/Write Logic when A1,A0=11. 2. If the CPU then does a write operation to the 8254, the data is stored in the Control Word Register and is interpreted as a Control Word used to define the operation of the counters. 3. The Control Word Register can only be written to. Status information is available with the Read-Back command. COUNTERS: 1. There are three Counters. Each is fully independent of the others. Each Counter may operate in a different Mode. 2. Each counter is a 16-bit synchronous down counter.

file://F:\Backup Old Hdds\DpFun\Utile\PROBL\DPNT\7203.HTM

6/1/2013

8254/82C54: Introduction to Programmable<BR> Interval Timer

Page 2 of 4

3. After power-up, the count value and output of all Counters are undefined. 4. Each counter must be programmed before it can be used. 5. Unused counters need not be programmed. 6. Counters are programmed by writing a Control Word and then an initial count. 7. GATE=1 enables counting, GATE=0 disables counting.

COUNTER DESCRIPTION:

COUNTING ELEMENT, OLm, OLl, OL: 1. The actual Counter is "CE" in figure 5. 2. OLm and OLl are two 8-bit latches. OL is "Output Latch" The subscripts m and l stand for "Most significant byte" and "Least significant byte". Both are normally referred to as one unit and called just OL. These latches "follow" the CE as it counts. 3. If a suitable Counter Latch Command is sent to the 8254, the latches capture the present count until read by the CPU. Once read, the latches return to "following" the CE. 4. One latch at a time is enabled by the counter's control logic to drive the internal bus. This is how the 16bit counter communicates over the 8-bit bus. 5. The CE itself cannot be read. If the user wants to read the count, it is the OL that is being read. CE, CRm, CRl, CR: 1. There are two 8-bit registers called CRm and CRl. These are the Count Register (Most significant byte and Least significant byte.) Both are normally just called the CR. 2. When a new count is written to the counter, the count is stored in the CR and later transferred to the CE. 3. The Control Logic allows one register at a time to be loaded from the internal bus. 4. Both bytes are transferred to the CE simultaneously. 5. CRm and CRl cleared when the Counter is programmed so that if the Counter has been programmed for one byte counts (either lsb or msb only) the other byte will be zero. 6. Note that the CE cannot be written into; whenever a count is written, it is written into the CR.

PROGRAMMING THE 8254:

1. Counters are programmed by writing a Control Word and then an initial count. 2. Control Words are written into the Control Word Register, which is selected when A0,A1=11. The Control Word itself specifies which Counter is being programmed. 3. Initial counts are written into the Counters, not the Control Word Register. The A0,A1 inputs are used to select the Counter to be written into. 4. The format of the initial count is determined by the Control Word used.

WRITE OPERATIONS:

There are two conventions for writing to the 8254: 1. For each Counter, the Control Word must be written before the initial count is written. 2. The initial count must follow the count format specified in the Control Word (lsb only, msb only, or lsb then msb). A new initial count may be written to a Counter at any time without affecting the Counter's programmed Mode in any way. However, the actual counting in the Counter will be affected as described in the various Mode definitions.

READ OPERATIONS:

The value of a Counter can be read by any one of the following three methods: 1. A simple READ operation: a. Select the Counter with the A1,A0 inputs. b. Inhibit the CLK of the selected counter by using either the GATE input or external logic. (The CLK must be inhibited or the count may be in the process of changing when it is read, giving an undefined result.)

file://F:\Backup Old Hdds\DpFun\Utile\PROBL\DPNT\7203.HTM

6/1/2013

8254/82C54: Introduction to Programmable<BR> Interval Timer

Page 3 of 4

c. Note that stopping the CLK stops the count. 2. Counter Latch Command (does not disturb the count in progress): a. It is written to the Control Word Register like a Control Word, but two bits (D5,D4) distinguish this command from a Control Word. b. The selected Counter's OL latches the count at the time the Counter Latch Command is received. c. The count is held in the latch until it is read by the CPU. d. The count is then unlatched automatically and the OL returns to "following" the CE. 3. Read-Back Command: a. This command allows the user to check the count value, programmed Mode, and current states of the OUT pin and Null Count flag of the selected counter(s). b. This command is similar to several Counter Latch Commands, one for each counter latched.

MODE DEFINITIONS:

CLK PULSE: a rising edge, then a falling edge, in that order, of a Counter's CLK input. Trigger: a rising edge of a Counters GATE input. Counter loading: the transfer of a count from the CR to the CE. MODE 0: INTERRUPT ON TERMINAL COUNT 1. Event counting. 2. After the Control Word is written, OUT is initially low and remains low. 3. When the counter reaches zero. OUT then goes high and remains high until a new count or a new Mode 0 Control Word is written into the Counter. MODE 1: HARDWARE RETRIGGERABLE ONE-SHOT 1. OUT will be initially high. OUT will go low on the CLK pulse following a trigger to begin the one-shot pulse, and remain low until the Counter reaches zero. 2. OUT will then go high and remain high until the CLK pulse after the next trigger. MODE 2: RATE GENERATOR 1. Functions like a divide-by-N counter and used to generate a Real Time Clock interrupt. 2. OUT will initially be high. 3. When the initial count has decremented to one, OUT goes low for one CLK pulse. 4. Out then goes high again, the Counter reloads the initial count and the process is repeated. 5. MODE 2 is periodic. The same sequence is repeated indefinitely. MODE 3: SQUARE WAVE MODE 1. Typically used for baud rate generation. 2. Out will initially be high. 3. When half the initial count is expired, OUT goes low for the remainder of the count. 4. MODE 3 is periodic. The same sequence is repeated indefinitely. MODE 4: SOFTWARE TRIGGERED STROBE 1. OUT will initially be high. 2. When the initial count expires, OUT will go low for one CLK pulse and then go high again. 3. The counting sequence is "triggered" by writing the initial count. 4. The Counter is loaded on the next CLK pulse following writing a Control Word and initial count. MODE 5: HARDWARE TRIGGERED STROBE (RETRIGGERABLE) 1. OUT will initially be high. 2. Counting is triggered by a rising edge of GATE. 3. When the initial count expires, OUT will go low for one CLK pulse and then go high again. 4. The difference between MODE 4 and MODE 5 is that in MODE 5 the count will not be loaded until the CLK pulse after a trigger.

file://F:\Backup Old Hdds\DpFun\Utile\PROBL\DPNT\7203.HTM

6/1/2013

8254/82C54: Introduction to Programmable<BR> Interval Timer

Page 4 of 4

OPERATION COMMON TO ALL MODES:

1. When a Control Word is written to a Counter, all Control Logic is immediately reset and OUT goes to the initial state. It does not take a CLK transition to do this. 2. The GATE input is always sampled on the rising edge of CLK 3. In some MODES the GATE input is level sensitive and some are rising-edge sensitive. In some MODES the GATE input is both edge and level sensitive. 4. New counts are loaded and Counters are decremented on the falling edge of CLK. 5. The largest possible initial count is zero. This is equivalent to 2^16 binary and 10^4 BCD. 6. The Counter does not stop when it reaches zero. In MODES 0, 1, 4, and 5 the Counter wraps around to the highest count (FFFFh or 9999bcd) and continues counting. In MODES 2 and 3 (which are periodic) the Counter reloads itself with the initial count and continues counting from there.

* Legal Information and Privacy Policy 2001 Intel Corporation

file://F:\Backup Old Hdds\DpFun\Utile\PROBL\DPNT\7203.HTM

6/1/2013

You might also like

- Agile Project ManagementToc PDFDocument1 pageAgile Project ManagementToc PDFAnonymous lubWipsrW0% (2)

- Johansen, S. (1988) - Statistical Analysis of Cointegration VectorsDocument24 pagesJohansen, S. (1988) - Statistical Analysis of Cointegration VectorsJoshua Maverick Ecafssa Sparrow100% (2)

- Direct Memory AccessDocument6 pagesDirect Memory AccessPratik SandilyaNo ratings yet

- 6.timer 8254Document15 pages6.timer 8254Akram TahaNo ratings yet

- 82C54 Programmable Interval Timer: Microprocessors ApplicationsDocument18 pages82C54 Programmable Interval Timer: Microprocessors ApplicationsAliNo ratings yet

- The 8253Document29 pagesThe 8253Soumya Ranjan PandaNo ratings yet

- Programmable Interval Timer 8254Document46 pagesProgrammable Interval Timer 8254shazidahmed832264No ratings yet

- By K. Vijay Kumar Assistant Professor Dept. of ECEDocument31 pagesBy K. Vijay Kumar Assistant Professor Dept. of ECEsignjpcoeNo ratings yet

- 8254 Programmable Interval TimerDocument4 pages8254 Programmable Interval Timerapi-26100966100% (1)

- Unit III 8254Document29 pagesUnit III 8254Sahil SinghNo ratings yet

- 8254 ModesDocument39 pages8254 ModesVamsi KrishnaNo ratings yet

- Programmable Interval Timer.Document68 pagesProgrammable Interval Timer.BETHWEL KIPROTICH100% (1)

- 8253Document17 pages8253Parv SharmaNo ratings yet

- 8254 Micro ProcessorDocument16 pages8254 Micro Processornishukaushal100% (2)

- 8253 54-1Document14 pages8253 54-1crsarinNo ratings yet

- Segment 7: Rogrammable Nterval ImerDocument36 pagesSegment 7: Rogrammable Nterval ImerDOUNIANo ratings yet

- Programmable Interval Timer - 8254Document35 pagesProgrammable Interval Timer - 8254Arnav BansalNo ratings yet

- 8254 TimerDocument9 pages8254 TimerHarisankar R N R 21BRS1524No ratings yet

- MicroprocessorDocument23 pagesMicroprocessorSahilPrabhakarNo ratings yet

- The 8253 Data Sheets Are List in The Following: Functional DescriptionDocument13 pagesThe 8253 Data Sheets Are List in The Following: Functional Descriptionharijai26No ratings yet

- C8254 ADocument6 pagesC8254 AHongryul ChunNo ratings yet

- CS305 M6 Ktunotes - inDocument35 pagesCS305 M6 Ktunotes - inDipin Preet SinghNo ratings yet

- 8254 MICROPROCESSOR (Driste)Document13 pages8254 MICROPROCESSOR (Driste)CSE7 NDUBNo ratings yet

- Microprocessor Interfacing Microprocessor Interfacing & Application & ApplicationDocument19 pagesMicroprocessor Interfacing Microprocessor Interfacing & Application & ApplicationMoses BrandNewNo ratings yet

- 8254 Programmable Interval Timer (Andres Suarez-201210937)Document21 pages8254 Programmable Interval Timer (Andres Suarez-201210937)Andres SuarezNo ratings yet

- Clock This Is The Clock Input For The CounterDocument22 pagesClock This Is The Clock Input For The CounterSri NikethanNo ratings yet

- 8253 NotesDocument8 pages8253 NotesSushmita SharmaNo ratings yet

- 8254 - Programmable Interval TimerDocument21 pages8254 - Programmable Interval Timeray1975507No ratings yet

- Part2 Expr03Document10 pagesPart2 Expr03akaka1392781No ratings yet

- Unit 4 - Microprocessor & Its Application - WWW - Rgpvnotes.inDocument9 pagesUnit 4 - Microprocessor & Its Application - WWW - Rgpvnotes.inJayesh JoshiNo ratings yet

- 8253 NotesDocument7 pages8253 NotesSarthak DidwaniaNo ratings yet

- MP Module 4 8254Document15 pagesMP Module 4 8254Lekshmi SasidharanNo ratings yet

- 8155 Is An Integrated RamDocument22 pages8155 Is An Integrated RamVipan SharmaNo ratings yet

- Interfacing Techniques: The 8254 Programmable Interval Timer (PIT)Document11 pagesInterfacing Techniques: The 8254 Programmable Interval Timer (PIT)yaseen jobaNo ratings yet

- Programmable Timer 8254Document20 pagesProgrammable Timer 8254Axe AxeNo ratings yet

- Practical 2 PicDocument7 pagesPractical 2 PicPrerna Sanjivan MhatreNo ratings yet

- Adc0808 and 8253Document35 pagesAdc0808 and 8253Avanish NiranjanNo ratings yet

- Adc0808 and 8253Document35 pagesAdc0808 and 8253Avanish NiranjanNo ratings yet

- Rohini 83704014962Document6 pagesRohini 83704014962punjan6No ratings yet

- Module 4 Interfacing ChipsDocument12 pagesModule 4 Interfacing ChipsaviralNo ratings yet

- Intel 8253/8254 - Programmable Interval TimerDocument15 pagesIntel 8253/8254 - Programmable Interval TimerAjnamol N RNo ratings yet

- Programmable Interval Timer 8253 (PIT) : COE305 LabDocument10 pagesProgrammable Interval Timer 8253 (PIT) : COE305 LabudayNo ratings yet

- Setup and Use The AVR® TimersDocument16 pagesSetup and Use The AVR® Timersmike_helplineNo ratings yet

- PIT: Programmable Interval Timer: Introduction To 8253/8254Document34 pagesPIT: Programmable Interval Timer: Introduction To 8253/8254Sayan GhoshNo ratings yet

- En - stm32f7 WDG Timers GptimDocument61 pagesEn - stm32f7 WDG Timers GptimLODELBARRIO RDNo ratings yet

- 8253 - Timer: Features of 8253Document5 pages8253 - Timer: Features of 8253srikrishnathotaNo ratings yet

- Programmable Interval Timer 8253: Architecture of 8253Document13 pagesProgrammable Interval Timer 8253: Architecture of 8253Srikanth KodothNo ratings yet

- 8255 PpiDocument22 pages8255 PpiAswin AswinNo ratings yet

- En - STM32G4-WDG TIMERS-General Purpose Timer GPTIMDocument91 pagesEn - STM32G4-WDG TIMERS-General Purpose Timer GPTIMnorbertscribdNo ratings yet

- Lab3 Rev eDocument13 pagesLab3 Rev eSaad Sulaiman KhanNo ratings yet

- Lab 7 - TimersDocument6 pagesLab 7 - Timersjnfgames1No ratings yet

- Stm32g0 Wdg Timers General Purpose Timer GptimDocument70 pagesStm32g0 Wdg Timers General Purpose Timer Gptimabdularrehman139No ratings yet

- 8254 PDFDocument14 pages8254 PDFMehul Shah100% (1)

- 8254-Programmable Interval TimerDocument21 pages8254-Programmable Interval TimerSanthosh SandyNo ratings yet

- Lecture 12 8051 Timer Programing v2Document22 pagesLecture 12 8051 Timer Programing v2Faisal Bin Abdur Rahman 1912038642No ratings yet

- lecture 7Document27 pageslecture 7Md.Shamrat SharkerNo ratings yet

- MPCyberModule 4Document13 pagesMPCyberModule 4Anjana SHIBUNo ratings yet

- 8254 AnniDocument43 pages8254 AnniCSE7 NDUBNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- Testul Din Anul 2014 - en - Şcoala de Agenţi de Poliţie Vasile Lascăr CâmpinaDocument24 pagesTestul Din Anul 2014 - en - Şcoala de Agenţi de Poliţie Vasile Lascăr CâmpinaAnonymous lubWipsrWNo ratings yet

- Descriere Curs OxfordDocument11 pagesDescriere Curs OxfordAnonymous lubWipsrWNo ratings yet

- Testul Din Anul 2014 - en - Şcoala de Agenţi de Poliţie Vasile Lascăr CâmpinaDocument24 pagesTestul Din Anul 2014 - en - Şcoala de Agenţi de Poliţie Vasile Lascăr CâmpinaAnonymous lubWipsrWNo ratings yet

- Import Import Import Import Import Import ImportDocument3 pagesImport Import Import Import Import Import ImportAnonymous lubWipsrWNo ratings yet

- Famous PlacesDocument4 pagesFamous PlacesAnonymous lubWipsrWNo ratings yet

- Electricalworld 24 NewyDocument706 pagesElectricalworld 24 NewySyæfül BåhryNo ratings yet

- 04 - Notebook4 - Additional InformationDocument5 pages04 - Notebook4 - Additional InformationLokesh LokiNo ratings yet

- Prevention and Control of Soil-Transmitted Helminthiasis With Focus On DewormingDocument51 pagesPrevention and Control of Soil-Transmitted Helminthiasis With Focus On DewormingDaxw JlmiNo ratings yet

- Drag Coefficient Determination of A Bus Model UsinDocument7 pagesDrag Coefficient Determination of A Bus Model UsinJesus AguilarNo ratings yet

- PMC Projexis Bungalow Presentation FinalDocument28 pagesPMC Projexis Bungalow Presentation FinalNur FarehaNo ratings yet

- Alka L. Gupta - Polymer Chemistry - Pragati Prakashan (2010)Document271 pagesAlka L. Gupta - Polymer Chemistry - Pragati Prakashan (2010)Snehapriya Subramanian100% (1)

- McKee Chapter8 Sample PDFDocument44 pagesMcKee Chapter8 Sample PDFMustafa Kırca100% (1)

- The Ant and The GrasshopperDocument4 pagesThe Ant and The GrasshopperMyla RicamaraNo ratings yet

- XC4411 ManualmainDocument1 pageXC4411 ManualmainfahadNo ratings yet

- Scicent QRN U8 Final Bilingual PDFDocument16 pagesScicent QRN U8 Final Bilingual PDFngethan520No ratings yet

- B. Agro Processing Cluster - DasconsultantDocument11 pagesB. Agro Processing Cluster - DasconsultantDiwan Singh JakharNo ratings yet

- Reaksi Transfusi, TRALI Vs TACODocument12 pagesReaksi Transfusi, TRALI Vs TACOifadhrohayatNo ratings yet

- A Light Extinguished (A Jumpstart For Scion Second Edition)Document41 pagesA Light Extinguished (A Jumpstart For Scion Second Edition)TarusentNo ratings yet

- A New Platform For Rail Communications - Adopting 5G For RailwaysDocument17 pagesA New Platform For Rail Communications - Adopting 5G For RailwaysShashikant ChaudhariNo ratings yet

- Nucleic Acids - How Structure Conveys Information - A CritiqueDocument3 pagesNucleic Acids - How Structure Conveys Information - A Critiquejessamae.bucad.cvtNo ratings yet

- LM 339Document51 pagesLM 339vantri27082004No ratings yet

- Gothic ArchitectureDocument28 pagesGothic ArchitectureHAZIM A ALHAZMI100% (1)

- McKenzie Explained PDFDocument4 pagesMcKenzie Explained PDFItai IzhakNo ratings yet

- Charles Babbage BiographyDocument2 pagesCharles Babbage BiographyhfNo ratings yet

- Ncert Exemplar Solutions For Class 12 Chemistry Chapter 2 Solutions PDFDocument13 pagesNcert Exemplar Solutions For Class 12 Chemistry Chapter 2 Solutions PDFaxenNo ratings yet

- 2DG & 2 SOLAR-nugal WaterDocument1 page2DG & 2 SOLAR-nugal WaterMajeed aliNo ratings yet

- Casos Parcial 3 PDFDocument5 pagesCasos Parcial 3 PDFRafa GarciaNo ratings yet

- PP QM - Flow in SAPDocument1 pagePP QM - Flow in SAPAbelardo Muzquiz100% (1)

- Anjali BbaDocument81 pagesAnjali BbaGaurav100% (1)

- Tracking The Path of Transcending The Source of Creativity in Lope de VegaDocument15 pagesTracking The Path of Transcending The Source of Creativity in Lope de VegaAMTRNo ratings yet

- Mehul Dhru: Work ExperienceDocument4 pagesMehul Dhru: Work ExperienceEhab IbrahimNo ratings yet

- Catalogo ProMusic 2015Document182 pagesCatalogo ProMusic 2015ale_rosi74No ratings yet

- From Beyond The Ley Gate Issue 1Document48 pagesFrom Beyond The Ley Gate Issue 1Arvin Kayz0% (1)

- Auxiliary Electrical SystemDocument17 pagesAuxiliary Electrical Systemreva_rkNo ratings yet