Lesson Plan: R.V. College of Engineering, Bangalore

Lesson Plan: R.V. College of Engineering, Bangalore

Uploaded by

Veena Divya KrishnappaCopyright:

Available Formats

Lesson Plan: R.V. College of Engineering, Bangalore

Lesson Plan: R.V. College of Engineering, Bangalore

Uploaded by

Veena Divya KrishnappaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Lesson Plan: R.V. College of Engineering, Bangalore

Lesson Plan: R.V. College of Engineering, Bangalore

Uploaded by

Veena Divya KrishnappaCopyright:

Available Formats

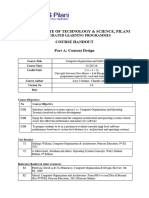

Department of Instrumentation Technology

R.V. College of Engineering, Bangalore

IT-10/Rev.1.0

Lesson Plan

Cover Page: Course Overview Semester: VII Course Title: Real Time Systems and Applications and Lab Total Contact Hours: 42 hrs SEE Marks: 100+50 Lesson Plan Author: Soumya M Checked By: Year: 2011-12 Course Code: 07IT73 Duration of SEE: 3+3 hrs CIE Marks: 100+50 Date: Date:

Prerequisites: To understand Real time systems, a student must have strong basics of embedded system and C programming. Course Overview: The course is about understanding basic concepts of operating systems, Real time system, real time memory management and its associated embedded system. Course Learning Objectives-CLO 1. 2. 3. 4. 5. To explore through the basics of RTOS and to master the essential command set, that can be used to work comfortably. RTOS provides a number of real time concepts like semaphores, mutex, thread, process, priorities, etc. The ability to combine commands to perform tasks that are not possible to achieve using single command. Understand the significance of C programming to attain real time objectives. Acquire knowledge of real time memory management.

Department of Instrumentation Technology

R.V. College of Engineering, Bangalore

Course Content

Course Code: 07IT73 Course Title: REAL TIME SYSTEMS AND APPLICATIONS AND LAB Teaching Hours: 42 Part A 1. Basic Real time concepts: Basic computer architecture bus transfer mechanism, input and output memory, CPU operation: Terminology, software concepts, system concepts, real time definitions, 03 hours events and determination, synchronous and asynchronous events, determinism, time loading; real time design issues. 2. Real time specification and design techniques: Natural languages: mathematical specifications, flow charts, structure charts, pseudo code and programming design languages, finite state automata, data flow diagrams DeMarcos rules, Hately and Pribhais extensions; petri nets, warnier-orr notation Indexed loop, state charts depth, orthogonality, broadcast communication, sanity in using graphical techniques 3. Real time kernels: Polled loop system, polled loop with interrupts, phase/state driven code, co routines, interrupt driven systems, context switching, round robin systems, pre emptive priority systems, major and minor cycles, hybrid systems, foreground-background systems, background processing, initialization, real-time operation, full featured real time operation systems Task control block model, Build or buy POSIX Part B 4. Intertask communication and Synchronization: Buffering data Time relative buffering, ring buffers, mailboxes mailboxes and semaphores, counting semaphores, problems with semaphores, the test and set instruction, event flags and signals, deadlock avoidance, detect and recover, priority inversion. 10 hours 06 hours 07 hours L-T-P: 3-1-3 CIE: 100+50 SEE: 100+50

5. Real time memory management:

06 hours

2

Department of Instrumentation Technology

R.V. College of Engineering, Bangalore Process stack management, task control block model, managing the stack, run time ring buffer, maximum stack size, multiple stack arrangements, task control block model, dynamic allocation swapping, overlays, MFT, MVT, demand paging, working sets, real-time garbage collection, contiguous fils systems; static schemes. Part - C 6. Interrupt servicing mechanism: Context and the periods for context switching; deadline and interrupt latency, language features: parameter passing, recursion, dynamic allocation, typing, exception handling, abstract data typing. 7. Case studies: Vx Works and MuCOS 05hours 5hours

Reference Books: 1. Philip A Laplante Real time systems design and analysis and engineers handbook, PHI publication, Second edition, 2000 2. Rajkamal Embedded systems architecture programming and design Tata McGraw Hill, 2004. 3. Dr. K.V.K.K Prasad Embedded/Real time systems: concepts, design and programming, Dreamtech press, 2005. 4. Steve Heath, Embedded systems design:, Second edition. 5. Krishna and shinkong Real time systems, McGraw Hill Publications, 2nd edition.

Evaluation Scheme

Department of Instrumentation Technology

R.V. College of Engineering, Bangalore CIE Scheme Assessment 2 Quiz 2 Internals Total Weightage in Marks 20 30 50

Best out of 2 Quiz and 2 Internals will be considered for CIE marks. Course Unitization for Internals and Semester End Examination

Part 1 A 2 Chapter Basic real time concepts Real time specification and design techniques Real time kernels Intertask communication and Synchronization Real time memory management 6 C 7 Interrupt servicing mechanism Case studies 5 2 5 3 2 Teaching Hours 3 7 3 6 10 6 1 2 3 2 No. of Questions in Internals I 2 Internals II Compensatory Internals 3 No. of Questions in SEE

3 4

Note: 1. Eight questions will be asked in the internals out of which student should answer five questions. Each question carries 10 Marks. 2. Eight questions will be asked in the Examination out of which student should answer five questions choosing atleast Two from PART-A, One from PART-B and Two from PART-C. Faculty In-charge Head of Department

4

Department of Instrumentation Technology

R.V. College of Engineering, Bangalore Date:

Department of Instrumentation Technology

R.V. College of Engineering, Bangalore Chapter wise Plan Part A

Course Code and Title: (07IT73 ) REAL TIME SYSTEMS AND APPLICATIONS AND LAB Planned Hours:04 hrs

Chapter Number and Title: 01 Basic Real-Time Concepts

Learning Objectives 1. This chapter will explore through the basics of RTOS, and also helps to master the command set. 2. The multiprogramming, multiuser and multitasking nature of RTOS. 3. What System calls are and how they enrich the RTOS programming environment. 4. The other features of RTOS its vast collection of tools, pattern matching and wide variety of its documentation sources. Lesson Schedule Class No. Portion covered per hour 1. Basic computer architecture bus transfer mechanism, input and output memory, CPU operation. 2. Terminology, software concepts, system concepts, real time definitions, events and determination. 3. Synchronous and asynchronous events, determinism, time loading; real time design issues. Model Questions What are hard, firm and Soft Real Time systems? Consider a payroll processing system for a small manufacturing firm. Describe three different scenarios in which the system can be justified as hard, firm or soft real time. Define response time. Model a real time system describing its features and how it is different from a typical I/O system. When can we say that a system is deterministic? Illustrate it with an example. What do we mean by CPU utilization? Enumerate scenarios where CPU utilization factor is essential in determining its performance. What are the services offered by Kernel? Describe a pre-emptive and nonpreemptive kernel highlighting the difference between the two.

1.

2. 3. 4.

5.

Department of Instrumentation Technology

R.V. College of Engineering, Bangalore Learning Objectives

Course Code and Title: (07IT73 ) REAL TIME SYSTEMS AND APPLICATIONS AND LAB Chapter Number and Title: 02 Real-Time specification and Design Techniques Planned Hours: 06 hrs

1. This chapter helps in developing knowledge in languages required for basic programming and mathematical specifications 2. Discern in depth about formulating flowcharts and state charts for different real time problems. 3. Be acquainted with pseudo code generation for a problem. 4. Be familiar with petrinets ,data flow diagrams and orthogonality. Lesson Schedule Class No. Portion covered per hour 1. Natural languages: mathematical specifications 2. Flow charts, structure charts 3. 4. Pseudo code and programming design languages Finite state automata

5. Data flow diagrams DeMarcos rules, Hately and Pribhais extensions 6. Petri nets, warnier-orr notation Indexed loop, state charts depth 7. Orthogonality, broadcast communication, sanity in using graphical techniques

Model Questions 1. 2. 3. 4. 5. 6. 7. What are the disadvantages of modeling using state chart Taking an example of a digital clock, model it using the state chart. state all the assumptions made. How is state chart better than FSM modeling an embedded system. Describe finite state automata with a example. Explain about data flow diagrams. and Demarcos rules. What are petrinets ? show a typical petrinet and firing for typical petrinet? With an explain pseudo code for an automatic teller machine.

Department of Instrumentation Technology

R.V. College of Engineering, Bangalore

Course Code and Title: (07IT73 ) REAL TIME SYSTEMS AND APPLICATIONS AND LAB Chapter Number and Title: 03 Real-Time Kernels Planned Hours: 05 hrs

Learning Objectives 1. Comprehend pooled loop systems and polled loop with interrupts. 2. Identify phase and state driven systems and co routines and their significance in rael time design. 3. Distinguish between Round robin and pre emptive systems and their importance. 4. Realize full featured RTOS. Lesson Schedule Class No. Portion covered per hour 1. Polled loop system, polled loop with interrupts 2. Phase/state driven code, coroutines 3. Interrupt driven systems, context switching 4. Round robin systems, pre emptive priority systems, major and minor cycles, hybrid systems 5. Foreground-background systems, background processing, initialization, real-time operation 6. Full featured real time operation systems Task control block model, Build or buy POSIX Model Questions 1. What is interrupt-only driven system? Explain a foreground-background system highlighting its improvement over interrupt only systems. Describe the process how a co-routine executes with the help of a pseudo code. What is interrupt-only driven system? Explain a foreground-background system highlighting its improvement over interrupt only systems. What are cyclic executives? Construct a cyclic executive with four processes, 1, 2, 3, 4; Process_2 runs two times as frequently as Process_1 and Process_3 and Process_2 runs four times as frequently as Process_4. Explain TCB model with different task states.

2. 3.

4.

5.

Department of Instrumentation Technology

R.V. College of Engineering, Bangalore Part - B

Course Code and Title: (07IT73 ) REAL TIME SYSTEMS AND APPLICATIONS AND LAB Chapter Number and Title: 04 Intertask communication and synchronization Planned Hours: 04 hrs

Learning Objectives 1. 2. 3. 4. Be acquainted with the various buffering methods in real time system design. Be familiar with semaphores and mailboxes and use them in programming. Realize the importance of deadlock and deadlock avoidance in real time design. Appreciate the significance of priority inversion and how to avoid it.

Lesson Schedule Class No. Portion covered per hour 1. Buffering data Time relative buffering, 2. Ring buffers, 3. Mailboxes mailboxes 4. 5. Semaphores, counting semaphores, Problems with semaphores,

6. The test and set instruction, 7. Event flags and signals, 8. Deadlock avoidance, 9. Detect and recover, 10. Priority inversion. Model Questions 1. 2. 3. What are the advantages of ring buffer over buffering or time-relative buffering? With pseudo code, explain the operation of a ring buffer. In brief, write a note on mailbox and message queue highlighting the difference between the two concepts. What are semaphores and where is it implemented? Explain the types of semaphores available in an RTOS and illustrate with an example of its utilization. Explain priority inversion with an example and how to overcome it?

4. 5. 6.

Department of Instrumentation Technology

R.V. College of Engineering, Bangalore

Course Code and Title: (07IT73 ) REAL TIME SYSTEMS AND APPLICATIONS AND LAB Chapter Number and Title: 05 Real-Time Memory Management Planned Hours: 03 hrs

Learning Objectives 1. Discern Dynamic memory management of any kind in real time systems. 2. Identify the techniques for managing stacks and task control blocks. 3. Value of memory management or paging of memory in real time systems. Lesson Schedule Class No. Portion covered per hour 1. Process stack management, task control block model, managing the stack, run time ring buffer 2. Maximum stack size, multiple stack arrangements 3. Task control block model, dynamic allocation swapping, overlays 4. MFT, MVT, demand paging, working sets, real-time garbage collection 5. Contiguous fils systems; static schemes. Model Questions 1. 2. 3. How does state chart better the FSM way of modeling embedded system? Write a note on modeling hierarchy. Describe the history mechanism involved in a state chart. Taking an example of a digital clock, model it using the state chart. State all the assumptions made. What are the disadvantages of modeling using a state chart? In memory management, how can we use a single list instead of multiple lists while implementing the TCB model of real time multitasking? Mention its advantage and 6. 7. 8. 9. disadvantage Which technique allows single program to be larger than the allowable program memory? Elaborate on the technique. In demand memory page systems, when is page staling done? How do we access a desired page by referencing via a page table? What are the disadvantages of using memory paging? Explain the concept of replacement algorithm. Take an example of a paged memory system divided into sixteen 256kb pages of which any 5 can be loaded at the same time

4. 5.

Part C

10

Department of Instrumentation Technology

R.V. College of Engineering, Bangalore Learning Objectives

Course Code and Title: (07IT73 ) REAL TIME SYSTEMS AND APPLICATIONS AND LAB Chapter Number and Title: 06 Interrupt Servicing mechanism Planned Hours: 04 hrs

1. Significance of context switching in real time design. 2. Prediction of worst case performance in real time design. 3. Considering the trade off in time and memory requirements. 4. Value of exception handling. Lesson Schedule Class No. Portion covered per hour 1. Context and the periods for context switching; 2. Deadline and interrupt latency 3. Language features: parameter passing 4. Recursion, dynamic allocation, typing

5. Exception handling, abstract data typing.

Model Questions 1. 2. 3. 4. 5. 6. Explain about context switching in detail What do you mean by dead line and interrupt latency in and RTOS With the help of a pseudo code illustrate recursion With the help of a pseudo code illustrate dynamic allocation With the help of a pseudo code illustrate exception handling Write short notes on abstract data typing and parameter passing

Learning Objectives

Course Code and Title: (07IT73 ) REAL TIME SYSTEMS AND APPLICATIONS AND LAB Chapter Number and Title: 07 Case studies Planned Hours: 02 hrs

1. Real time communication tools and an impressive collection of email agents and tools. 2. Locking user information with Vx Works , online text chat with MuCOS .

11

Department of Instrumentation Technology

R.V. College of Engineering, Bangalore

Lesson Schedule Class No. Portion covered per hour 1. Vx Works: Details of Users, mesg: Your Willingness to Communicate, write: Communicating alternatively 2. MuCOS: Online Communication, wall: writing on all terminals, news: knowing the local events, Email Basics, The mail command Model Questions 1. 2. Design a class diagram using UML for an Automatic Chocolate Vending Machine. Also give examples for any one of class and object representations. Design the hardware and software architectures for a Digital camera. State your assumptions made for the performance of the system prior to the design.

12

Department of Instrumentation Technology

R.V. College of Engineering, Bangalore

DEPARTMENT OF INSTRUMENTATION TECHNOLOGY R.V. COLLEGE OF ENGINEERING, BANGALORE 560 059. Model Question Paper REAL TIME SYSTEMS AND APPLICATIONS AND LAB Semester VII Sem B.E Subject Code: 07IT73 DATE: Max. Marks: 100 Marks TIME: Exam Time Note: 1. Answer five questions choosing at least Two from PART-A, One from PART-B and Two from PART-C. 2. Write neat diagrams wherever required. 1 PART A a) Define synchronous and asynchronous events.map them against periodic aperiodic [06] and sporadic event. b) Discuss whether the following are hard, soft or firm real-time system: (a) The library [04] of a congress print manuscript database system. (b) Automatic teller machine c) What are the design issues we come across dealing with real time systems? give one example of an RTS you come across on day to day basis and enumerate the design issues of that system. 2 a) Explain basic petrinet. model a system on an assembly line that counts 5 items and then sends a signal to the operator. [10]

b) Determine whether the following set is RM schedulable or not. If not schedule it with [10] EDF [T1(5,8),T2(1,9),T3(1,5)] 3 a) What are the disadvantages of EDF over fixed priority algorithm? Show the rm schedule of i si 1 0 2 1 3 2 ei 2 1 2 Pi=di 5 4 20 [02] [10] [10]

b) When is an ISR said to be re-entrant? c) Explain a context switch with a pseudo code. why should it be minimized?

13

Department of Instrumentation Technology

R.V. College of Engineering, Bangalore

PART B 4 a) What are the ways to avoid deadlock in intertask communication? explain bankers algorithm illustrating safe and unsafe states for 3 process. b) When does priority inversion occur? How does priority inheritance protocol solves inversion problem . describe both with timing diagrams 5 a) Discuss issues related to buffering data using global variables. How is time related buffering done by readers and writers problem. [10]

[10] [10]

b) Give an example of mailbox implementation which has 4 tasks and 3 recourses. Draw [06] task resource request table and resource table and state your assumptions. c) Write short note on critical region with example. 6 a) What are the basic differences between a mutex and a semaphore? Illustrate their implementation in detail with pseudo code. b) Explain process stack management using run time stack and TCB model. PART C 7 a) What do you mean by throwing an exception? How is the exception condition during [10] execution of a function handled. b) Why is the context switching in an embedded processor faster than saving the pointers and variables on the stack using stack pointer. How does the context switching time [10] reduce in processor architectures for embedded system. 8 a) Design a class diagram using UML for an Automatic Chocolate Vending Machine. Also give examples for any one of class and object representations. b) Design the hardware and software architectures for a Digital camera. State your assumptions made for the performance of the system prior to the design. [10] [10] [04] [10] [10]

14

You might also like

- AWS Academy Cloud Foundations Module 02 Student Guide: 100-ACCLFO-20-EN-SGDocument69 pagesAWS Academy Cloud Foundations Module 02 Student Guide: 100-ACCLFO-20-EN-SGperbankan75% (4)

- Sustainability Tool (Takaful)Document21 pagesSustainability Tool (Takaful)khamini dilly kannanNo ratings yet

- Multiplefull NewDocument42 pagesMultiplefull NewVeena Divya KrishnappaNo ratings yet

- Real Time and Embedded System New Curriculum Based Course OutlineDocument4 pagesReal Time and Embedded System New Curriculum Based Course OutlineAyano BoresaNo ratings yet

- Course Outline FinalDocument4 pagesCourse Outline Finaldaniel asefaNo ratings yet

- Esd Lesson PlanDocument13 pagesEsd Lesson PlanShivaprasad B KNo ratings yet

- Vishwakarma Institute of TechnologyDocument23 pagesVishwakarma Institute of TechnologyEr Shubham RaksheNo ratings yet

- 2nd SemDocument18 pages2nd SemSuman Raj SharmaNo ratings yet

- Laboratory Exercises On Task Scheduling in Real-Time-Systems CourseDocument13 pagesLaboratory Exercises On Task Scheduling in Real-Time-Systems Courseأيوب علاءNo ratings yet

- CSE422-Real Time Operating SystemDocument4 pagesCSE422-Real Time Operating Systemnarendra29000No ratings yet

- BITSG553 HandoutDocument2 pagesBITSG553 HandoutRps DeepanNo ratings yet

- Syllabus OSRTSDocument8 pagesSyllabus OSRTSPrem TVNo ratings yet

- Third Semester SyllabusDocument10 pagesThird Semester SyllabusDil Prasad KunwarNo ratings yet

- SCHEME - G Fifth Semester (CO)Document42 pagesSCHEME - G Fifth Semester (CO)RazeenKhanNo ratings yet

- CSC 35Document4 pagesCSC 35Nguyen NguyenNo ratings yet

- Discrete Structure: Logic, Induction and ReasoningDocument8 pagesDiscrete Structure: Logic, Induction and ReasoningGovindaNo ratings yet

- Syllabus of Second Year B.E. Computer Engg.Document35 pagesSyllabus of Second Year B.E. Computer Engg.dalberquesafisNo ratings yet

- BScIT Syllabus 13.9.23Document20 pagesBScIT Syllabus 13.9.23snigdhopikubackup06No ratings yet

- Syllabus 5th SemDocument3 pagesSyllabus 5th SemAnkur PrasadNo ratings yet

- Microcontroller & Embedded Systems ScheduleDocument3 pagesMicrocontroller & Embedded Systems Scheduleshasky21No ratings yet

- ICP Syllabus FinalDocument3 pagesICP Syllabus FinalMr. Nikhil Mohan ShindeNo ratings yet

- RtosDocument4 pagesRtosSubhajit TewaryNo ratings yet

- CS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24Document4 pagesCS - ECE - EEE - INSTR F215 Digital Design Handout I Sem 2023-24f20220264No ratings yet

- M.C.A. Mumbai UniversityDocument30 pagesM.C.A. Mumbai Universitymalisachin5126No ratings yet

- Sem 620Document40 pagesSem 620Rahul ranjan KumarNo ratings yet

- Computer UG New Syllabus.Document46 pagesComputer UG New Syllabus.Ujjawal TyagiNo ratings yet

- UT Dallas Syllabus For cs4397.001 05s Taught by Farokh Bastani (Bastani)Document2 pagesUT Dallas Syllabus For cs4397.001 05s Taught by Farokh Bastani (Bastani)UT Dallas Provost's Technology Group0% (1)

- Week Wise Syllabus 1st SemesterDocument7 pagesWeek Wise Syllabus 1st SemesterRehman Ahmad ChNo ratings yet

- IT UG - New SyllabusDocument48 pagesIT UG - New SyllabusParush AryaNo ratings yet

- SyllabusDocument3 pagesSyllabusDev Shankar PaulNo ratings yet

- Scope and Objectives of The CourseDocument3 pagesScope and Objectives of The CourseAbhinav GuptaNo ratings yet

- CS C372Document3 pagesCS C372sky_davisNo ratings yet

- CS 4th Semester SyllabusDocument13 pagesCS 4th Semester SyllabusManish KumarNo ratings yet

- ECE 666 Real Time Computer SystemDocument3 pagesECE 666 Real Time Computer SystemRamnarayan ShreyasNo ratings yet

- University of Mumbai University of Mumbai University of MumbaiDocument19 pagesUniversity of Mumbai University of Mumbai University of MumbaiJaya PillaiNo ratings yet

- 17-619 Introduction To Real-Time Software and Systems: Carnegie MellonDocument7 pages17-619 Introduction To Real-Time Software and Systems: Carnegie Mellonbkit_n_haiNo ratings yet

- COAVITDocument3 pagesCOAVITnikshithNo ratings yet

- ComputerOrganizationAndSoftwareSystems Flipped HODocument10 pagesComputerOrganizationAndSoftwareSystems Flipped HOraghunathanNo ratings yet

- BTech CPSDocument4 pagesBTech CPSpranavNo ratings yet

- BSCS SubjectsDocument20 pagesBSCS SubjectsMark Dipad100% (2)

- 21CS43 Microcontroller and Embedded SystemsDocument4 pages21CS43 Microcontroller and Embedded SystemsNikhil chandNo ratings yet

- Bits Pilani, Dubai Campus Instruction Division: Second Semester 2012 - 2013 Course Handout (Part - II)Document2 pagesBits Pilani, Dubai Campus Instruction Division: Second Semester 2012 - 2013 Course Handout (Part - II)anupam20099No ratings yet

- Ss Zg553 Course HandoutDocument8 pagesSs Zg553 Course HandoutDivyaeraNo ratings yet

- 4th Sem PDFDocument12 pages4th Sem PDFKloseNo ratings yet

- Computer Organization: Course ObjectivesDocument2 pagesComputer Organization: Course Objectivesರಘು ಕಟಗಲ್ಲNo ratings yet

- Open Electrive I - 3rd Year VI Semester - AICTE 2020-21 - 9 March 2021Document15 pagesOpen Electrive I - 3rd Year VI Semester - AICTE 2020-21 - 9 March 2021aniruddha sharmaNo ratings yet

- Subject Code Subject Name Credits: Overview of Computer Architecture & OrganizationDocument4 pagesSubject Code Subject Name Credits: Overview of Computer Architecture & Organizationanon_71491248No ratings yet

- ZERO Lecture CSE316 Jan - April 2024Document39 pagesZERO Lecture CSE316 Jan - April 2024what90642No ratings yet

- COA Full Syllabus-CSEDocument3 pagesCOA Full Syllabus-CSEAMARTYA KUMARNo ratings yet

- MCA SyllabusDocument35 pagesMCA Syllabusnitesh63No ratings yet

- Computer Science: and Python Programming With PracticalDocument23 pagesComputer Science: and Python Programming With Practicalrekha_1234No ratings yet

- Digital Design Using HDL PDFDocument2 pagesDigital Design Using HDL PDFMarvin MayormenteNo ratings yet

- Thapar MCA Syllabus PDFDocument53 pagesThapar MCA Syllabus PDFsunnykinger100% (2)

- Mom24 25Document3 pagesMom24 25mdahmerusmaniNo ratings yet

- 10) WASE 2018 - Comp - Org - Archi - Flipped - HODocument14 pages10) WASE 2018 - Comp - Org - Archi - Flipped - HOShreyansh AnshumanNo ratings yet

- With Effect From The Academic Year 2013-2014 CS 404 Principles and Applications of Embedded SystemsDocument2 pagesWith Effect From The Academic Year 2013-2014 CS 404 Principles and Applications of Embedded Systemsvedavyas99No ratings yet

- Computer Organisation (15CS34) New Syllabus: NotesDocument119 pagesComputer Organisation (15CS34) New Syllabus: NotesAkanksha SonkarNo ratings yet

- ECE205Document4 pagesECE205IgorRyaskovNo ratings yet

- Vit Ece 5th Year SyllabusDocument16 pagesVit Ece 5th Year Syllabuspranavateja12399No ratings yet

- Models and Analysis for Distributed SystemsFrom EverandModels and Analysis for Distributed SystemsSerge HaddadNo ratings yet

- C++ Advanced Programming: Building High-Performance ApplicationsFrom EverandC++ Advanced Programming: Building High-Performance ApplicationsNo ratings yet

- Introduction To Digital Hardware DesignDocument25 pagesIntroduction To Digital Hardware DesignVeena Divya KrishnappaNo ratings yet

- Ai ModelDocument3 pagesAi ModelVeena Divya KrishnappaNo ratings yet

- Introduction To Digital Hardware DesignDocument25 pagesIntroduction To Digital Hardware DesignVeena Divya KrishnappaNo ratings yet

- Introduction To Digital Hardware DesignDocument25 pagesIntroduction To Digital Hardware DesignVeena Divya KrishnappaNo ratings yet

- Computer Communication Networks (Sub., Code: 10EC71) : Unit-IDocument75 pagesComputer Communication Networks (Sub., Code: 10EC71) : Unit-IVeena Divya KrishnappaNo ratings yet

- AESDocument22 pagesAESVeena Divya KrishnappaNo ratings yet

- Identify The Type of Instrument GroupingDocument2 pagesIdentify The Type of Instrument GroupingVeena Divya KrishnappaNo ratings yet

- Business and Commercial Aviation MagazineDocument10 pagesBusiness and Commercial Aviation MagazineVeena Divya KrishnappaNo ratings yet

- Identify The Network Shown in The FigureDocument2 pagesIdentify The Network Shown in The FigureVeena Divya KrishnappaNo ratings yet

- The RSA AlgorithmDocument15 pagesThe RSA AlgorithmVeena Divya KrishnappaNo ratings yet

- jeHR7q - HMW - 1486899278 - WORKSHEET GRADE 3 MONEY PDFDocument4 pagesjeHR7q - HMW - 1486899278 - WORKSHEET GRADE 3 MONEY PDFVeena Divya Krishnappa100% (4)

- jeHR7q - HMW - 1486899278 - WORKSHEET GRADE 3 MONEY PDFDocument4 pagesjeHR7q - HMW - 1486899278 - WORKSHEET GRADE 3 MONEY PDFVeena Divya Krishnappa100% (4)

- Grammar Workbook 1Document25 pagesGrammar Workbook 1Mohamed Kamara33% (3)

- Unit 1 BDocument79 pagesUnit 1 BVeena Divya KrishnappaNo ratings yet

- Datalink Layer 1Document81 pagesDatalink Layer 1Veena Divya KrishnappaNo ratings yet

- DC - Module IIDocument19 pagesDC - Module IIVeena Divya KrishnappaNo ratings yet

- Unit 1 Module 2 Air Data InstrumentsDocument37 pagesUnit 1 Module 2 Air Data InstrumentsVeena Divya Krishnappa100% (1)

- Error Detection and CorrectionDocument46 pagesError Detection and CorrectionVeena Divya KrishnappaNo ratings yet

- TOPIC: "ICT Powering An Inclusive Education - Telecom Namibia's Contribution" 4 National ICT Summit 2017Document33 pagesTOPIC: "ICT Powering An Inclusive Education - Telecom Namibia's Contribution" 4 National ICT Summit 2017Veena Divya KrishnappaNo ratings yet

- Signal Flow GraphDocument36 pagesSignal Flow GraphVeena Divya Krishnappa100% (1)

- State Variable Models: Dorf and Bishop, Modern Control SystemsDocument39 pagesState Variable Models: Dorf and Bishop, Modern Control SystemsVeena Divya KrishnappaNo ratings yet

- Nlcs Quiz 2018Document2 pagesNlcs Quiz 2018Veena Divya KrishnappaNo ratings yet

- Chapter 18 CVR & FDRDocument41 pagesChapter 18 CVR & FDRVeena Divya KrishnappaNo ratings yet

- Quad Store (TM) - 37 in 1 Sensor Modules Kit For Arduino Uno R3, Mega 2560, Raspberry Pi With BoxDocument1 pageQuad Store (TM) - 37 in 1 Sensor Modules Kit For Arduino Uno R3, Mega 2560, Raspberry Pi With BoxVeena Divya KrishnappaNo ratings yet

- Mikrokontrolerski SistemiDocument175 pagesMikrokontrolerski SistemimuhamedNo ratings yet

- The College Magazine Java Project20240201100452Document3 pagesThe College Magazine Java Project20240201100452sukeshbhalke10No ratings yet

- Circuit Setter: Calibrated Balance Valves With Flanged ConnectionsDocument2 pagesCircuit Setter: Calibrated Balance Valves With Flanged ConnectionsJulio MorenoNo ratings yet

- S190311 SAMSUNG Memory Over Provisioning White PaperDocument8 pagesS190311 SAMSUNG Memory Over Provisioning White PaperCesare RomanoNo ratings yet

- SDMS Performance Test Summary Report v2.0Document22 pagesSDMS Performance Test Summary Report v2.0Santosh Das100% (1)

- Xerox Versant 180 Press: User GuideDocument166 pagesXerox Versant 180 Press: User GuidebggNo ratings yet

- M-Series T-Series: Head Office: No.6 President Terrace. Takli Road, Dwarka. Nashik-422011 Phone:0253 - 6418632Document4 pagesM-Series T-Series: Head Office: No.6 President Terrace. Takli Road, Dwarka. Nashik-422011 Phone:0253 - 6418632Hanane ZgtNo ratings yet

- List of Faculties Tokyo Institute of Technology International Graduate Program (C) Commencing in April 2021Document19 pagesList of Faculties Tokyo Institute of Technology International Graduate Program (C) Commencing in April 2021fayoNo ratings yet

- Level II BASIC Reference Manual (1979) (Radio Shack)Document196 pagesLevel II BASIC Reference Manual (1979) (Radio Shack)wavvkaNo ratings yet

- InvoiceDocument1 pageInvoicesrinu vasuNo ratings yet

- Cybernetic Deconstruction Cyberpunk and PostmodernismDocument17 pagesCybernetic Deconstruction Cyberpunk and PostmodernismFeiyu HuangNo ratings yet

- Log TrackDocument3 pagesLog TrackguillemvhNo ratings yet

- Privileged Account Security System RequirementsDocument69 pagesPrivileged Account Security System RequirementsLee OdhowNo ratings yet

- Cat It28g Technical SpecificationsDocument2 pagesCat It28g Technical Specificationsbrandy100% (61)

- Vdocument - in 17 1project Management William J Stevenson Operations Management 8 TH EditionDocument34 pagesVdocument - in 17 1project Management William J Stevenson Operations Management 8 TH EditionHeidi raei100% (1)

- Boiler Control Philosophy R00Document6 pagesBoiler Control Philosophy R00Raj Kumar TiwariNo ratings yet

- Branch High Availability in The Distributed Enterprise: Implementation GuideDocument23 pagesBranch High Availability in The Distributed Enterprise: Implementation GuidePablo EzequielNo ratings yet

- TSX Spare PartsDocument41 pagesTSX Spare PartsΩρωπου 90No ratings yet

- LangChain Cheat Sheet KDnuggetsDocument1 pageLangChain Cheat Sheet KDnuggetskristoflerouxNo ratings yet

- UntitledDocument232 pagesUntitledДарья ДеркачNo ratings yet

- Subscribe For Free Job UpdatesDocument5 pagesSubscribe For Free Job UpdatessathyajiNo ratings yet

- Charge Owners ManualDocument76 pagesCharge Owners ManualNiyazi GasimovNo ratings yet

- Class Ex - 18 - R-L Circuit SimulationDocument5 pagesClass Ex - 18 - R-L Circuit Simulation6tqjwtk9sfNo ratings yet

- Shashikant Sanjay Shedge Contact No: +91 8459420238: Program: Parts Details: Software: Client: DescriptionDocument3 pagesShashikant Sanjay Shedge Contact No: +91 8459420238: Program: Parts Details: Software: Client: DescriptionShashikant ShedageNo ratings yet

- Uber TechnologiesDocument4 pagesUber Technologiesmohammed khayyumNo ratings yet

- CODESYS Engineering enDocument12 pagesCODESYS Engineering enAnonymous yugocxnNo ratings yet

- PV2006 7760Document1 pagePV2006 7760Bombang LompoNo ratings yet

- 1-Implementing A Java ProgramDocument13 pages1-Implementing A Java Programpratigya gNo ratings yet