Appendix A

Uploaded by

swapnil_joshi_55Copyright:

Available Formats

Appendix A

Uploaded by

swapnil_joshi_55Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Appendix A

Uploaded by

swapnil_joshi_55Copyright:

Available Formats

Appendix pend

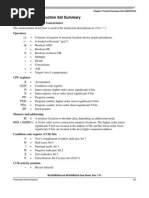

* Instruction Set Summary*

Possible Flag settings are indicated by following symbols. 0 1 m d r AM Not affected Reset Set Modified according to Result Undefined (dont care) Restored from previously stored value Addressing Mode

Addressing Mode No. of Clock Cycles (AM) Direct Mode 6 Indirect Mode 5 Register Relative 9 Based Indexed Base pointer with Destination Index Register Base register with Source Index Register Base Base

7 U V W Pointer with Source Index Register 8 U register with Destination Index Register V W

AM BP BX

SI 8 7

DI 7 8

Compiled By Harshad Tambde (B.E. E & T) Rishikesh Agashe (B.E. E & T)

Appendix A

635

Based indexed relative Base Base Base Base

AM BP BX

pointer register pointer register

SI 12 11

with with with with

Destination Index Register + Disp source Index Register + Disp source index register + Disp. destination index register + Disp.

7 + 4 = 11 U V W 8 + 4 = 12 U V W

DI 11 12

Table A.1 Data Copy/transfer Instructions

Mnemonic MOV Description Move Accumulator to memory Memory to accumulator Register to register Memory to register Register to memory Immediate to register Immediate to memory Register to SS, DS or ES Memory to SS, DS or ES Segment register to register Segment register to memory Push word onto stack Register Segment register Memory Pop word off stack Register Segment register SS, DS, or Memory Exchange Register with accumulator Register with memory Register with register Input from I/O port Fixed port Variable port Output to I/O port Fixed port Variable port Clock Cycles 10 10 2 8+AM 9+AM 4 10+AM 2 8+AM 2 9+AM 11 10 16+AM 8 ES 8 17+AM 3 17+AM 4 10 8 10 8 Number of bytes 3 3 2 24 24 23 36 2 24 2 24 1 1 24 1 1 24 1 24 2 2 1 2 1 O D I T Flags S Z A P C

PUSH

POP

XCHG

IN

OUT

636 Advanced Microprocessors and Peripherals

Mnemonic Description Clock Cycles 11 2+AM 16+AM 4 4 10 8 Number of bytes 1 24 24 1 1 1 1 Flags T S Z

XLAT/ XLATB T r a n s l a t e LEA Load effective address LDS/LES Load pointer using DS/ES LAHF Load AH from flags SAHF Store AH in to flags P U S H F Push flags onto stack POPF Pop flags from stack

r r

r r

r r

r r

r r

Table A.2 Arithmetic Instructions

Mnemonic ADD Description Addition Register to register Memory to register Register to memory Immediate to register Immediate to memory Immediate to accumulator Add with carry Register to register Memory to register Register to memory Immediate to register Immediate to memory Immediate to accumulator Increment by 1 16-bit register 8-bit register Memory Decrement by 1 16-bit register 8-bit register Memory Subtraction Register from register Memory from register Register form memory Immediate from accumulator Immediate from register Immediate from memory Subtract with borrow Register from register Memory from register Register form memory Immediate from accumulator Clock Cycles 3 9+AM 16+AM 4 17+AM 4 3 9+AM 16+AM 4 17+AM 4 2 3 15+AM 2 3 15+AM 3 9+AM 16+AM 4 4 17+AM 3 9+AM 16+AM 4 Number of bytes 2 24 24 34 36 23 m 2 24 24 34 36 23 m 1 2 24 m 1 2 24 m 2 24 24 23 34 36 m 2 24 24 23 m m m m m m m m m m m m m m m m m m m m m m m O m D I T Flags S Z m m A m P m C m

ADC

INC

DEC

SUB

SUB

SBB

Appendix A Mnemonic Description Clock Cycles Number of bytes 34 36 m 2 24 24 34 36 23 1 1 2 2 1 1 2 24 m 2 2 24 24 m 2 2 24 24 1 1 2 2 24 24 d 2 2 24 24 d d d d d d d d d d d d m m m m Flags S Z

637

CMP

AAA AAS AAM AAD DAA DAS NEG

MUL

IMUL

IMUL CBW CWD DIV

IDIV

Immediate from register 4 Immediate from memory 17+AM Compare Register to register 3 Memory to register 9+AM Register to memory 16+AM Immediate to register 4 Immediate to memory 4 Immediate to accumulator 17+AM ASCII adjust after addition 4 ASCII adjust after subtraction 4 ASCII adjust after multiplication 83 ASCII adjust after division 60 Decimal adjust accumulator 4 Decimal adjust subtraction 4 Negate Register 3 Memory 16+AM Unsigned multiplication 8-bit register 7077 16-bit register 118133 8-bit memory (7683)+AM 16-bit memory (124139)+AM Integer multiplication 8-bit register 8098 16-bit register 128154 8-bit memory (86104)+AM 16-bit memory (134160)+AM Convert byte to word 2 Convert word to double word 5 Unsigned division 8-bit register 8090 16-bit register 144162 8-bit memory (8696)+AM 16-bit memory (150168)+AM Integer division 8-bit register 101112 16-bit register 165184 8-bit memory (107118)+AM 16-bit memory (171190)+AM

d d d d d d m

d d m m m m m

d d m m m m m

m m d d m m m

d d m m m m m

m m d d m m m

Table A.3 Logical Instructions

Mnemonic AND Description Logical AND Register to register Clock Cycles 3 Number of bytes 2 O 0 D I Flags T S Z m m A d P m C 0

638 Advanced Microprocessors and Peripherals

Mnemonic Description Memory to register Register to memory Immediate to register Immediate to memory Immediate to accumulator Logical OR Register to register Memory to register Register to memory Immediate to accumulator Immediate to register Immediate to memory Logical NOT Register Memory Logical exclusive OR Register with register Memory with register Register with memory Immediate with accumulator Immediate with register Immediate with memory TEST Register with register Memory with register Immediate with accumulator Immediate with register Immediate with memory Clock Cycles 9+AM 16+AM 4 17+AM 4 3 9+AM 16+AM 4 4 17+AM 3 16+AM 3 9+AM 16+AM 4 4 17+AM 3 9+AM 4 5 11+AM Number of bytes 24 24 34 36 23 2 24 24 23 34 36 2 24 0 2 24 24 23 34 36 0 2 24 23 34 36 m m d m 0 m m d m 0 Flags S Z

OR

m m

NOT

XOR

TEST

Table A.4 Branching Instructions

Mnemonic CALL Description Call a procedure Intrasegment direct Intrasegment indirect through register Intrasegment indirect through memory Intrasegment direct Intrasegment indirect Return from a procedure Intrasegment Intrasegment with constant Intersegment Intersegment with constant Clock Cycles 19 16 21+AM 28 37+AM 8 12 18 17 Number of bytes 3 2 24 5 24 1 3 1 3 O D I Flags T S Z A P C

RET

Appendix A Mnemonic INT N Description Clock Cycles Number of bytes 1 2 0 0 Flags S Z

639

I 0

T 0

Interrupt Type = 3 52 Type 3 51 INTO Interrupt if overflow Interrupt if taken 53 Interrupt if not taken 4 JMP Jump Intrasegment direct short 15 Intrasegment direct 15 Intersegment direct 15 Intrasegment indirect 18+AM through memory Intrasegment indirect 11 through register Intersegment indirect 24+AM IRET Return from Interrupt 24 JZ/JE Jump if not zero/ 16/4 Jump if not equal JNX/ Jumps if not zero/ 16.4 JNE Jumps if not equal JS Jump if sign 16/4 JNS Jump if not sign 16/4 JO Jump of overflow 16/4 JNO Jump if not overflow 16/4 J P / J P E Jump if parity/ 16/4 Jump if parity even J N P / J P O Jump if not parity/Jump 16/4 if parity odd JB/ J N A E / J C Jump if below/Jump if not 16/4 above or equal/Jump if carry JNB/ J A E / J N C Jump if not below/Jump if 16/4 above or equal/Jump if not carry J B E / J N A Jump if below or equal/ 16/4 Junp if not above J N B E / J A Jump if not below or equal/ 16/4 Jump if above JL/ JNGE Jump if less/ 16/4 Jump if not greater or equal J N L / J G E Jump if not less/ 16/4 Jump if greater or equal J L E / J N G Jump if less or equal/ 16/4 Jump if not greater J N L E / J G Jump if not less or equal/ 16/4 Jump if greater JCXZ Jump if CX is zero 18/6

2 3 5 24 2 24 1 2 2 2 2 2 2 2 2

2 2 2

2 2 2 2 2

640 Advanced Microprocessors and Peripherals Table A.5 LOOP Instructions

Mnemonic LOOP Loop LOOPE/ Loop LOOPZ Loop LOOPNZ/ Loop L O O P N E Loop Description Clock Cycles 17/5 18/6 Number of bytes 2 2 O D I T Flags S Z A P C

if equal/ if zero if not zero/ if not equal

19/5

Table A.6 Machine Control Instructions

Mnemonic NOP HLT WAIT LOCK ESC Description No operation Halt Wait while TE ST pin not asserted Lock Bus Escape Register Memory Clock Cycles 3 2 3+5n 2 2 8+AM Number of bytes 1 1 1 1 2 24 O D I T Flags S Z A P C

Table A.7 Flag Manipulation Instruction

Mnemonic CLC CMC STC CLD STD CLI STI Description Clear carry flag Complement carry flag Set carry flag Clear direction flag Set direction flag Clear interrupt flag Set interrupt flag Clock Cycles 2 2 2 2 2 2 2 Number of bytes 1 1 1 1 1 1 1 O D 0 1 I 0 1 T Flags S Z A P C 0 m 1

Table A.8 Shift and Rotate Instruction

Mnemonic Description Clock Cycles Number of bytes O m D I T Flags S Z m m A d P m C m

SHL/SAL Shift Logical Left/ Shift arithmetic Left Register with single shift 2 2 Register with variable shift 8+4/bit 2 Memory with single shift 15+AM 24 Memory with variable shift(20+AM)+4/bit 24 SHR Shift logical right Register with single shift 2 2 Register with variable shift 8 + 4/bit 2

m m

Appendix A Mnemonic Description Clock Cycles Number of bytes 24 24 m 2 2 24 24 m 2 2 24 24 m 2 2 24 24 m 2 2 24 24 m 2 2 24 24 m m d m Flags T S Z

641

SAR

ROR

RO L

RCR

RCL

Memory with single shift 15+AM Memory with variable shift(20+AM)+4/bit Shift arithmetic right Register with single shift 2 Register with variable shift 8 + 4/bit Memory with single shift 15+AM Memory with variable shift(20+AM)+4/bit Rotate right without carry Register with single shift 2 Register with variable shift 8 + 4 bit Memory with single shift 15+AM Memory with variable shift(20+AM)+4/bit Rotate left Register with single shift 2 Register with variable shift 8 + 4/bit Memory with single shift 15+AM Memory with variable shift(20+AM)+4/bit Rotate right through carry Register with single shift 2 Register with variable shift 8 + 4/bit Memory with single shift 15+AM Memory with variable shift(20+AM)+4/bit Rotate left through carry Register with single shift 2 Register with variable shift 8 + 4/bit Memory with single shift 15+AM Memory with variable shift(20+AM)+4/bit

Table A.9 String Instruction

Mnemonic Description Clock Cycles Number of bytes 1 O m D I T Flags S Z m m A m P m C m

CMPS/ Compare string/compare CMPSB byte string/compare word CMPSW s t r i n g Not repeated Repeated MOVS/ Move string/move MOVSB/ byte string/move MOVSW Word string Not repeated Repeated LODS/ Load string/Load LODSB/ String byte/Load LODSW String word Not repeated Repeated

22 9+22/rep 1

18 9+17/rep 1

12 9+13/rep

642 Advanced Microprocessors and Peripherals

Mnemonic Description Clock Cycles Number of bytes 1 Flags S Z

SCAS/ Scan string/ SCASB/ Scan byte string/ SCASW Scan word string Not repeated Repeated STOS/ Store string/ STOSB/ Store byte string/ STOSW Store word string Not repeated Repeated

15 9+15/rep 1

m m

11 9+10/rep

You might also like

- AVR Assembly-AVR Command Set - AVR Assembler Command SetNo ratings yetAVR Assembly-AVR Command Set - AVR Assembler Command Set8 pages

- GPON OLT Quick Configuration User Manual: About Product100% (1)GPON OLT Quick Configuration User Manual: About Product56 pages

- 6881009Y05-O Vol 1 Understanding Your Astro 25100% (1)6881009Y05-O Vol 1 Understanding Your Astro 25615 pages

- I I 1 I I: Instruction Set Reference DataNo ratings yetI I 1 I I: Instruction Set Reference Data18 pages

- ARM Organization and Implementation: Aleksandar Milenkovic100% (2)ARM Organization and Implementation: Aleksandar Milenkovic37 pages

- Forward Time Division Multiplex: Transmit Power Transmit Power Maximum Power Maximum PowerNo ratings yetForward Time Division Multiplex: Transmit Power Transmit Power Maximum Power Maximum Power39 pages

- Compaq - 8085 Microprocessor - (443940)No ratings yetCompaq - 8085 Microprocessor - (443940)46 pages

- FT-8800R Tech Documentation: From Interlock Rochester WikiNo ratings yetFT-8800R Tech Documentation: From Interlock Rochester Wiki5 pages

- EK-8A002-MM-002 PDP-8A Miniprocessor Users Manual Dec76No ratings yetEK-8A002-MM-002 PDP-8A Miniprocessor Users Manual Dec76602 pages

- Dynamic Binary Translation and Optimization: Erik R. Altman Kemal Ebcio GluNo ratings yetDynamic Binary Translation and Optimization: Erik R. Altman Kemal Ebcio Glu124 pages

- MOD 4-I Simple Computer - Bottom Up ImplementationNo ratings yetMOD 4-I Simple Computer - Bottom Up Implementation11 pages

- Exp 12) Prbs Generator and Shift RegisterNo ratings yetExp 12) Prbs Generator and Shift Register5 pages

- Block I Apollo Guidance Computer (AGC) : How To Build One in Your BasementNo ratings yetBlock I Apollo Guidance Computer (AGC) : How To Build One in Your Basement52 pages

- Array Processors: SIMD Computer Organization100% (1)Array Processors: SIMD Computer Organization45 pages

- Voyager 9520/40 Voyager GS9590 Eclipse 5145: Quick Start GuideNo ratings yetVoyager 9520/40 Voyager GS9590 Eclipse 5145: Quick Start Guide16 pages

- .CLP Delta - DVP-ES2 - EX2 - SS2 - SA2 - SX2 - SE&TP-Program - O - EN - 20130222 EDITADONo ratings yet.CLP Delta - DVP-ES2 - EX2 - SS2 - SA2 - SX2 - SE&TP-Program - O - EN - 20130222 EDITADO782 pages

- Introduction to Computer Organization: An Under the Hood Look at Hardware and x86-64 AssemblyFrom EverandIntroduction to Computer Organization: An Under the Hood Look at Hardware and x86-64 AssemblyNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic Circuits5/5 (1)

- Introduction To Cmos Vlsi Design: MIPS Processor ExampleNo ratings yetIntroduction To Cmos Vlsi Design: MIPS Processor Example43 pages

- Event Prediction in An IoT Environment Using Naïve Bayesian ModelsNo ratings yetEvent Prediction in An IoT Environment Using Naïve Bayesian Models7 pages

- Qterm A7 Terminal Windows Embedded Ce ManualNo ratings yetQterm A7 Terminal Windows Embedded Ce Manual62 pages

- Symantec Netbackup 7.5 For Unix: Manage and Administer (Appendixes)No ratings yetSymantec Netbackup 7.5 For Unix: Manage and Administer (Appendixes)474 pages

- Dense Passage Retrieval For Open-Domain Question AnsweringNo ratings yetDense Passage Retrieval For Open-Domain Question Answering13 pages

- Digital Electronics and Computer Architecture ELEC40003 SOLUTIONSNo ratings yetDigital Electronics and Computer Architecture ELEC40003 SOLUTIONS10 pages

- Annex05 WeLink Video Conference Operation Guide For Invigilator)No ratings yetAnnex05 WeLink Video Conference Operation Guide For Invigilator)10 pages

- EMPLOYEE MANAGEMENT SYSTEM-A DOCUMENTATION, CREATED BY Durga Prasad Mahato, Dip in C.S.ENo ratings yetEMPLOYEE MANAGEMENT SYSTEM-A DOCUMENTATION, CREATED BY Durga Prasad Mahato, Dip in C.S.E42 pages

- s7252 Jayadharini Jaiganesh Efficient Connected ComponentsNo ratings yets7252 Jayadharini Jaiganesh Efficient Connected Components43 pages

- AVR Assembly-AVR Command Set - AVR Assembler Command SetAVR Assembly-AVR Command Set - AVR Assembler Command Set

- GPON OLT Quick Configuration User Manual: About ProductGPON OLT Quick Configuration User Manual: About Product

- ARM Organization and Implementation: Aleksandar MilenkovicARM Organization and Implementation: Aleksandar Milenkovic

- Forward Time Division Multiplex: Transmit Power Transmit Power Maximum Power Maximum PowerForward Time Division Multiplex: Transmit Power Transmit Power Maximum Power Maximum Power

- FT-8800R Tech Documentation: From Interlock Rochester WikiFT-8800R Tech Documentation: From Interlock Rochester Wiki

- EK-8A002-MM-002 PDP-8A Miniprocessor Users Manual Dec76EK-8A002-MM-002 PDP-8A Miniprocessor Users Manual Dec76

- Dynamic Binary Translation and Optimization: Erik R. Altman Kemal Ebcio GluDynamic Binary Translation and Optimization: Erik R. Altman Kemal Ebcio Glu

- MOD 4-I Simple Computer - Bottom Up ImplementationMOD 4-I Simple Computer - Bottom Up Implementation

- Block I Apollo Guidance Computer (AGC) : How To Build One in Your BasementBlock I Apollo Guidance Computer (AGC) : How To Build One in Your Basement

- Voyager 9520/40 Voyager GS9590 Eclipse 5145: Quick Start GuideVoyager 9520/40 Voyager GS9590 Eclipse 5145: Quick Start Guide

- .CLP Delta - DVP-ES2 - EX2 - SS2 - SA2 - SX2 - SE&TP-Program - O - EN - 20130222 EDITADO.CLP Delta - DVP-ES2 - EX2 - SS2 - SA2 - SX2 - SE&TP-Program - O - EN - 20130222 EDITADO

- Introduction to Computer Organization: An Under the Hood Look at Hardware and x86-64 AssemblyFrom EverandIntroduction to Computer Organization: An Under the Hood Look at Hardware and x86-64 Assembly

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic Circuits

- IBM System 360 RPG Debugging Template and Keypunch CardFrom EverandIBM System 360 RPG Debugging Template and Keypunch Card

- Introduction To Cmos Vlsi Design: MIPS Processor ExampleIntroduction To Cmos Vlsi Design: MIPS Processor Example

- Event Prediction in An IoT Environment Using Naïve Bayesian ModelsEvent Prediction in An IoT Environment Using Naïve Bayesian Models

- Symantec Netbackup 7.5 For Unix: Manage and Administer (Appendixes)Symantec Netbackup 7.5 For Unix: Manage and Administer (Appendixes)

- Dense Passage Retrieval For Open-Domain Question AnsweringDense Passage Retrieval For Open-Domain Question Answering

- Digital Electronics and Computer Architecture ELEC40003 SOLUTIONSDigital Electronics and Computer Architecture ELEC40003 SOLUTIONS

- Annex05 WeLink Video Conference Operation Guide For Invigilator)Annex05 WeLink Video Conference Operation Guide For Invigilator)

- EMPLOYEE MANAGEMENT SYSTEM-A DOCUMENTATION, CREATED BY Durga Prasad Mahato, Dip in C.S.EEMPLOYEE MANAGEMENT SYSTEM-A DOCUMENTATION, CREATED BY Durga Prasad Mahato, Dip in C.S.E

- s7252 Jayadharini Jaiganesh Efficient Connected Componentss7252 Jayadharini Jaiganesh Efficient Connected Components