Switched Capacitor Band-Pass Filter 0.1 Object: C 3 DB BP

Switched Capacitor Band-Pass Filter 0.1 Object: C 3 DB BP

Uploaded by

mohamedCopyright:

Available Formats

Switched Capacitor Band-Pass Filter 0.1 Object: C 3 DB BP

Switched Capacitor Band-Pass Filter 0.1 Object: C 3 DB BP

Uploaded by

mohamedOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Switched Capacitor Band-Pass Filter 0.1 Object: C 3 DB BP

Switched Capacitor Band-Pass Filter 0.1 Object: C 3 DB BP

Uploaded by

mohamedCopyright:

Available Formats

Switched Capacitor Band-Pass Filter

0.1 Object

The object of this experiment is to design and implement a fourth-order Chebyshev band-pass

lter using a switched-capacitor realization. The specications of the lter are: passband

ripple 1.8 dB, center frequency f

C

= 4 kHz, 3 dB bandwidth f

3 dB

= 2 kHz, gain at the

center frequency H

BP

= 1. The transfer function is to be realized as the product of a

second-order high-pass lter in cascade with a second-order low-pass lter.

To obtain the transfer function for the lter, see page 13 of the Filter Potpourri. Follow

the example for the 8th order band-pass lter to solve for the required value of x and B in the

frequency transformation from a low-pass lter function to a band-pass lter function. The

frequency transformation for the band-pass lter is given on page 6 of the Filter Potpourri.

Use it to solve for the transfer function.

After you obtain the band-pass transfer function, use Mathcad or any math program to

plot the dB gain versus frequency for the function. If you use Mathcad, be sure to use a range

variable for the frequency that gives equal x-axis spacings on a log scale. Check to see if the

center frequency and the 3 dB bandwidth are correct. If they are correct, use Mathcad to

factor the denominator of the transfer function into the product of two second-order transfer

functions.

Rewrite the factored transfer function as the product of a high-pass lter function and

a low-pass lter function. Realize the two lter functions using the methods and hardware

described below. The parts will be supplied by our laboratory support sta. The information

below is from the lab manual for ECE 3042. It describes the devices available and how to

use them. Other that that, it contains more information than is needed for this experiment.

0.2 Switched Capacitor Theory

Active lter design with op amps is a robust mature discipline. All of the classical lter types

that were implemented in bygone eras with resistors, capacitors, and inductors may now be

implemented solely with resistors, capacitors, and op amps. The accuracy of these lters is

limited by only the precision of the components and the properties of the physical op amps

employed. If discrete resistors and capacitors are used, variations within the manufacturers

stated tolerance may produce unacceptable error in the design unless extremely expensive

components are employed.

The resistors and capacitors required for lter design may be fabricated on monolithic

integrated circuits along with the op amps but they usually require a large amount of area and

are subject to temperature drift and other annoying eects such as parasitic capacitance.

Resistors fabricated on integrated circuits are usually restricted to values less than 10 k

OBJECT 1

while the upper limit for capacitors is approximately 100 pF. Also, it is quite dicult to

obtain precise values of passive components fabricated on integrated circuits. Such dedicated

analog lter integrated circuits are available but they are rather expensive.

The problem of component variation may be overcome with switched capacitor lters.

These use small integrated circuit capacitors whose terminals are switched by a high fre-

quency clock signal using MOSFET switches to simulate large values of resistance. The

MOSFETs are fabricated on the same integrated circuit while the clock may be external or

also resident on the integrated circuit.

Switched capacitor lters are not a panacea. They are digital circuits and are, therefore,

subject to aliasing. The Nyquist criterion requires that the waveform be sampled at a rate

at least twice its bandwidth to prevent aliasing. Normally the clock frequency is picked to

be large compared to the critical frequencies of the lter (50 to 100 times larger) to prevent

aliasing. Also, the output is a discrete rather than continuous waveform. To minimize both

of these defects it is customary to precede the digital switched capacitor lter with an anti-

aliasing analog low-pass lter to limit the bandwidth and to follow the digital lter with an

analog deglitching lter. The break frequencies of these analog lters are not crucial so this

use of analog lters at the input and output is not a major impediment.

0.2.1 Switched Capacitor Integrator

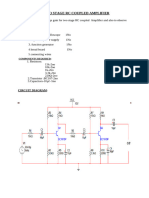

Figure 0-1 Switched capacitor integrator.

A switched capacitor integrator is shown in Fig. 0-1. The clock signal c(t) with frequency

f

c

and period T

c

= 1/f

c

is applied to both the gate input of MOSFET M

1

and the digital

2

INVERTER. The signal applied to the gate of MOSFET M

2

is the complement of the clock.

Hence, excepts for the switching transient, one MOSFET is on while the other is o.

When the clock is high MOSFET M

1

is on and M

2

is o. Capacitor C

1

has a charge

q = C

1

v

i

placed on it by the input to the lter. If the clock frequency is large compared to

the bandwidth of v

i

the input may be considered to be constant during the sampling interval

T

c

/2. During the next clock half cycle M

1

is o and M

2

is on which places the top node of

the capacitor C

1

at the virtual ground of the op amp which causes the charge on it to be

transferred to C

F

. The average current owing into capacitor C

1

is

i(t) =

q

T

c

=

C

1

T

c

v

i

= C

1

f

c

v

i

(1)

which means that it is equivalent to a resistor R

eq

= 1/C

1

f

c

. The output of the op amp is

then given by

v

o

=

1

C

F

Z

t

i(u) du =

C

1

f

c

C

F

Z

t

v

i

(u) du =

1

C

F

R

eq

Z

t

v

i

(u) du (2)

which makes this circuit an integrator. Integrators are the heart of the state variable lter

which means that any of the classical lters may be realized with this switched capacitor

arrangement. Other more elaborate topologies are also employed in switched capacitor lters

but the circuit in Fig. 0-1 illustrates the basic principle.

Because charge is transferred in spurts from capacitor C

1

to capacitor C

F

this makes

the output voltage discrete rather than continuous. The voltage increments are reduced to

acceptable values by picking the clock frequency to be large which is also required to prevent

aliasing. A deglitching analog low-pass lter cascaded with the output may also be used to

smooth the output voltage.

Since the output of the switched capacitor integrator depends on the ratio of two capac-

itances, this can easily be fabricated on an integrated circuit. Although precise values of

components are dicult to control, maintaining ratios is relatively simple.

Anent the equivalent resistance being set as R

eq

= 1/C

1

f

c

, this makes controlling the

critical frequencies of the lter elementary. The system clock sets the critical frequencies.

Therefore, such lters may be easily electronically tuned.

When a MOSFET is on the drain to source resistance is not zero but has a certain value

know as the on-resistance R

on

which is normally several hundred ohms. This means that

the charging and discharging of capacitor C

1

is not instantaneous but limited by an RC

time constant

on

= R

on

C

1

. This sets the upper limit for the system clock. Proper operation

requires that the period of the system clock be large compared to the charging time constant.

With current MOS technology this makes operation of switched capacitor lters above a few

hundred kilo-hertz impossible.

0.2.2 Second Order Filter Categories

Because switched capacitor lters are digital circuits, the appropriate mathematical artice

to analyze them is the z transform. However, classical frequency domain analysis is su-

ciently accurate and more amendable to a mathematical tractable analysis. This discussion

SWITCHED CAPACITOR THEORY 3

will be limited to second order lters because that is what is implemented in the device that

will be ultimately employed in this experiment.

Low-Pass Filter

Figure 0-2 Second-order low-pass lter.

The complex transfer function for a second-order low-pass lter is

T(s) = K

1

2

+

1

Q

+ 1

(3)

where K is the DC gain of the lter, Q is the quality factor, and

0

is the resonant frequency

of the lter. The magnitude of the complex transfer function is plotted in Fig. 0-2. The

3 dB or half-power cuto frequency f

c

is the frequency at which the gain is reduced to

K/

2 and is given by

f

c

= f

0

v

u

u

t

1

1

2Q

2

+

s

1

1

2Q

2

2

+ 1 (4)

which is a frequency larger than f

0

. The maximum value of the magnitude of the complex

transfer function A occurs at the frequency f

max

where

A =

K

1

Q

r

1

1

4Q

2

(5)

4

and

f

max

= f

0

r

1

1

2Q

2

(6)

which is a frequency smaller than f

0

.

The proper selection of Q will produce any of the classical lter congurations such as

Butterworth, Chebyshev, and Bessel. The choice of Q is given in Table 1.

Filter Type Pass-Band Ripple Q f

c

/f

0

Bessel 0.577 0.786

Butterworth 0.707 1.000

Chebyshev 0.1 dB 0.767 1.078

Chebyshev 0.2 dB 0.797 1.111

Chebyshev 0.3 dB 0.821 1.136

Chebyshev 0.5 dB 0.864 1.176

Chebyshev 1 dB 0.957 1.246

Chebyshev 2 dB 1.129 1.333

Chebyshev 3 dB 1.305 1.389

Table 1 Second-Order Low-Pass Filter Parameters

High-Pass Filter

Figure 0-3 Second-order high-pass lter.

SWITCHED CAPACITOR THEORY 5

The complex transfer function for a second-order high-pass lter is

T(s) = K

2

+

1

Q

+ 1

(7)

where K is the high-frequency gain of the lter, Q is the quality factor, and

0

is the resonant

frequency of the lter. The magnitude of the complex transfer function is plotted in Fig.

0-3. The minus 3 dB, half-power, critical, or cuto frequency f

c

is the frequency at which

the gain is reduced to K/

2 and is given by

f

c

=

f

0

v

u

u

t

1

1

2Q

2

+

s

1

1

2Q

2

2

+ 1

(8)

which is a frequency smaller than f

0

. The maximum value of the magnitude of the complex

transfer function A occurs at the frequency f

max

where

A =

K

1

Q

r

1

1

4Q

2

(9)

and

f

max

=

f

0

r

1

1

2Q

2

(10)

which is a frequency larger than f

0

.

Band-Pass Filter

The complex transfer function for the second-order band-pass lter is

T(s) = K

1

Q

2

+

1

Q

+ 1

(11)

where f

0

is the resonant frequency and also the center frequency, Q is the quality factor, and

K is the gain at the center frequency. The plot of the magnitude of the complex transfer

function as a function of frequency is shown in Fig. 0-4. This circuit has both an upper, f

U

,

and lower, f

L

, half-power frequencies given by

f

U

= f

0

_

_

1

2Q

+

s

1

2Q

2

+ 1

_

_

(12)

6

Figure 0-4 Band-pass lter.

SWITCHED CAPACITOR THEORY 7

and

f

L

= f

0

_

_

1

2Q

+

s

1

2Q

2

+ 1

_

_

(13)

The dierence between these two half-power frequencies is known as the half-power band-

width, f, which is given by

f = f

U

f

L

=

f

0

Q

(14)

which reveals that

Q =

f

0

f

(15)

which is the reason why Q is called the quality factor, i.e. the larger Q is the sharper the

peak in the lter becomes. The center frequency is also the geometric mean of the half-power

frequencies, i.e.

f

0

=

p

f

U

f

L

(16)

Notch Filter

The complex transfer function of the second order notch lter is given by

T(s) = K

2

+ 1

2

+

1

Q

+ 1

(17)

where

0

is the notch frequency in radians/sec, Q is the quality factor, and K is both the

high and low frequency gain. A plot of the magnitude of the complex transfer function for

the notch lter is shown in Fig. 0-5.

All of the equations for the upper and lower half-power frequencies as well as the quality

factor for the band-pass lter are equally applicable for the notch lter. This is because the

transfer function of the notch lter, T

N

(s), is related to that of the band-pass lter, T

B

(s),

by

T

N

(s) = K T

B

(s) (18)

Thus, either lter may be obtained by summing the other with a gain constant.

All-Pass Filter

The transfer function of the second-order all-pass lter is given by

8

Figure 0-5 Notch lter.

SWITCHED CAPACITOR THEORY 9

T(s) = K

1

Q

+ 1

2

+

1

Q

+ 1

(19)

which has a constant amplitude and a phase that varies with frequency. The magnitude

of the complex transfer function is K at all frequencies whereas the angle of the complex

transfer function is given by

(j) =

6

T(s)|

s=j

= 2 arctan

_

_

1

Q

0

1

2

_

_

(20)

Biquadratic Filter

The second order biquadratic lter has the complex transfer function

T(s) = K

2

+

1

Q

z

+ 1

2

+

1

Q

p

+ 1

(21)

which has a DC gain of K and a high frequency gain of K (

p

/

z

)

2

. A special case of the

biquadratic lter is obtained by letting the quality factor for the numerator become innite

(which puts the zeroes on the imaginary axis as is the case for the notch lter)these are

known as elliptic lters. If

p

>

z

it is a high-pass elliptic lter and if

p

<

z

it is a

low-pass elliptic lter (and, of course, if

p

=

z

it is a notch lter). Elliptic lters feature

the fastest transition from the pass to the stop band but, unlike the garden variety high-

and low-pass lters, do not have a gain that is a monotonic function of frequency.

0.3 Devices

A plethora of switched capacitor devices are available as o-the-shelf integrated circuits from

a variety of manufacturers. Prominent among these are the devices from Motorola which

are primarily intended for telecommunications applications such as the MC145432 which

features a six pole notch lter operated by a highly stable crystal oscillator internal clock

or the MC145414 which is a fth-order elliptic lter. Some lters are totally digital in that

both the clock frequency and the lter parameters are directly set by input digital codes.

The device that will be employed in this experiment in the MF10 Universal Monolithic

Dual Switched Capacitor Filter because it is the cheapest switched capacitor device available

and it oers a degree of exibility to the user. A functional block diagram is shown in Fig.

10

Figure 0-6 MF10 switched capacitor lter.

DEVICES 11

0-6. The square symbols indicate that these are pin numbers on the integrated circuit. It

has two identical lters known and A and B. Separate clocks are provided for each of the

two lters. The circuit components shown in this gure are internal to the integrated circuit.

Each of the symbols show as a triangle with an integral symbol inside are switched capacitor

integrators of the type discussed in 0.2.1. Because there are two integrators and op amp

summers, this makes this a second order state variable lter.

The symbol with a one plus and two minus signs in a circle with an X is a summer with

two inverting and one non-inverting inputs. One of the inverting inputs is a pin on the IC

while the other is controlled by the S

AB

input on pin 6; the position of this switch determines

whether the feedback is closed around the input op amp or the triple input summer.

The level shift input on pin 9 determines the type of clock being used. This pin is

grounded for TTL clock signals or 5 V CMOS clock signals. The same type of clock must

be applied to both lter A and B but dierent frequency clocks may be used at the two

inputs. The 50/100/CL input on pin 12 determines whether the critical frequencies are

obtained as the clock frequency divided by 50 or 100 or whether the lter is turned o; if

this pin is connected to the positive power supply the clock frequency is divided by 50, if

it is grounded the clock frequency is divided by 100, and if it is connected to the negative

supply ltration is inhibited.

Figure 0-7 Pinouts for MF10

The pinouts for the MF10 are given in Fig. 0-7. A more complete description of this

device is given in the manufacturers data sheet in the appendix to this experiment. The

notation used in the manufacturers data sheet diers slightly from that used in this exper-

iment.

The manufacturer denes several modes or circuit topologies for the MF10. The one that

12

Figure 0-8 Mode 3A for MF10

DEVICES 13

will be used in this experiment is Mode 3a shown in Fig. 0-8. The resistors R1, R2, R3, and

R4 are external resistors that are connected to the pins shown. There are three outputs low-,

high-, and band-pass at pins 1, 3, and 2 respectively. One external op amp summer with

resistors R

L

, R

U

,and R

g

is used to sum the high- and low-pass outputs to produce a notch

output. The input is v

i

.

The resonant frequency f

0

is given by

f

0

=

f

CLK

100

r

R2

R4

or

f

CLK

50

r

R2

R4

(22)

depending on whether the clock is being divided by 100 or 50; this is center frequency of

both the band-pass and notch lter. The quality factor is given by

Q =

r

R2

R4

R3

R2

(23)

The DC gain of the low-pass lter is

K

LP

=

R4

R1

(24)

The high-frequency gain of the high-pass lter is

K

HP

=

R2

R1

(25)

The gain at the center frequency of the band-pass lter is

K

BP

=

R3

R1

(26)

The gain of the notch lter at the notch frequency f

0

is given by

A

n

=

R

g

R

L

K

LP

R

g

R

H

K

HP

(27)

which would normally be picked to be zero. The gain of the notch lter at DC is

K

N

=

R

g

R

L

K

LP

(28)

while the gain at the frequency which is half of the clock frequency is

KCLK

2

=

R

g

R

H

K

HP

(29)

14

0.4 Experimental Procedures

0.4.1 Preparation

Prepare the electronic breadboard to provide buses for the positive and negative power supply

rails and the circuit ground. Three power supplies will be used in this experiment: +5 V, and

5 V. Each power supply rail should be decoupled with a 100 , 25 V (or greater) capacitor.

The resistors are connected in series with the external power supply leads and the capacitors

are connected from the power supply rails to ground on the circuit side of the resistor. The

capacitor must be installed with the proper polarity to prevent reverse polarity breakdown.

0.4.2 Clock

Figure 0-9 555/MC1555 Timer

EXPERIMENTAL PROCEDURES 15

The clock that will be used for the experiment in the MC1555/555 timer shown in Fig.

0-9. The power supply voltage for this IC will be + 5 V so that it will produce a TTL clock.

The clock frequency is

f

CLK

=

1.44

(R

1

+ 2R

2

) C

T

(30)

and the duty cycle is

Duty Cycle =

R

1

+R

2

R

1

+ 2R

2

(31)

Design the timer so that the clock frequency is either f

0

100 or f

0

50. Pick the duty

cycle to be close to 50%. The lower of the two frequencies is the most judicious choice;

although the higher clock frequency would produces fewer glitches in the output of the lter,

if the timer were operated at this high frequency on an untidy breadboard, the waveform

might be distorted and degrade the performance of the lter.

0.4.3 Second-Order Filter

Assemble the second-order state variable lter shown in Fig. 0-8 using the component values

computed in the preliminary calculations section with the power o. This is the mode of the

lter labeled 3a by the manufacturer.

Pins 5, 9, and 15 should be connected to ground.

Pins 7, 8, and 12 should be connected to the positive power supply, +5 V. (Connecting

pin 12 to the positive power supply sets the lter to the f

CLK

/50 mode. If the f

CLK

/100

mode is desired, pin 12 should be grounded.)

Pins 6, 13, and 14 should be connected to the negative power supply, 5 V.

Standard connections should be made for the external op amp. An LF351 would be a

better choice than a 741 since the 741 requires power supply voltages of at least 8 V which

would incinerate the MF10.

The clock input is pin 3 of the MC1555 timer which is connected to pin 10 of the MF10

for lter A.

Turn the power on and measure the frequency response of the lter. Data should be

taken of the four outputs as the frequency of the input is varied one decade above and below

f

0

.

Increase the frequency of the input until it is approximately equal to the clock frequency.

Explain why the low- and band-pass outputs are nonzero in the laboratory report.

0.4.4 Fourth-Order Filter

Assemble the fourth-order lter with the characteristics specied by the laboratory instruc-

tor. This is obtained by cascading the two second-order lters found in the MF10. Repeat

the measurement of the frequency response.

16

You might also like

- Ultra-Low Power Phase-Locked LoopDocument4 pagesUltra-Low Power Phase-Locked Loophawking1122No ratings yet

- Implementation of Second Order Switched Capacitors Filters With Feedback SignalDocument3 pagesImplementation of Second Order Switched Capacitors Filters With Feedback SignalInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- Lab 3Document5 pagesLab 3معتصم الكاملNo ratings yet

- Bmen3120 Project1 Frequency Selective Circuit 1Document12 pagesBmen3120 Project1 Frequency Selective Circuit 1api-3139933760% (2)

- Digitally Controlled Oscillator ReportDocument18 pagesDigitally Controlled Oscillator ReportVinidhra ShivakumarNo ratings yet

- RC Phase Shift Oscillator and RC Coupled Ce Amplifier - Lab ExperimentDocument8 pagesRC Phase Shift Oscillator and RC Coupled Ce Amplifier - Lab ExperimentMani Bharathi100% (1)

- A Low Power, and Low Signal 5-Bit 25msamples/s Pipelined ADC For Monolithic Active PixelsDocument5 pagesA Low Power, and Low Signal 5-Bit 25msamples/s Pipelined ADC For Monolithic Active Pixelstajmjcet_123No ratings yet

- An 1162Document36 pagesAn 1162naniknanikNo ratings yet

- DeDocument7 pagesDeSudhakar SpartanNo ratings yet

- Capacimetre FemtoDocument30 pagesCapacimetre FemtoJean-Marie ChaputNo ratings yet

- Team Members: Name USN Roll NumberDocument10 pagesTeam Members: Name USN Roll Number01fe20bec113No ratings yet

- Regular Correspondence: Compact High-Frequency Output Buffer For Testing of Analog CMOS VLSI CircuitsDocument3 pagesRegular Correspondence: Compact High-Frequency Output Buffer For Testing of Analog CMOS VLSI CircuitsSaranya ChakrabortyNo ratings yet

- Ultra-Low-Power 2.4 GHZ Colpitts Oscillator Based On Double Feedback TechniqueDocument4 pagesUltra-Low-Power 2.4 GHZ Colpitts Oscillator Based On Double Feedback TechniqueCamila DamascenoNo ratings yet

- Aec Lab ManualDocument17 pagesAec Lab ManualprofharishjoshiNo ratings yet

- ECE3204 D2013 Lab2Document9 pagesECE3204 D2013 Lab2Khalil2097No ratings yet

- RC OscillatorDocument8 pagesRC OscillatorRavi TejaNo ratings yet

- Interpretation Spectre SCDocument13 pagesInterpretation Spectre SCFrederic DelmarcheNo ratings yet

- 09 Chapter 3Document44 pages09 Chapter 3Amisha kambleNo ratings yet

- EE680Lab Experiment6-7Document21 pagesEE680Lab Experiment6-7Amro AbusailNo ratings yet

- Understanding Attenuators and Compensation: R R V R V R R R V VDocument7 pagesUnderstanding Attenuators and Compensation: R R V R V R R R V Vnithinjose4uNo ratings yet

- Synchronization MethodsDocument7 pagesSynchronization MethodsAmit KumarNo ratings yet

- Measuring Output Ripple An-1144Document8 pagesMeasuring Output Ripple An-1144anon_444314615No ratings yet

- Direct RF Sampling Mixer With Recursive Filtering in Charge DomainDocument4 pagesDirect RF Sampling Mixer With Recursive Filtering in Charge DomainBinod AdhikariNo ratings yet

- Amplitude Modulation and DemodulationDocument3 pagesAmplitude Modulation and DemodulationRaj Mehra Mehar100% (1)

- EEE 54 DP1 Documentation - Mendoza - SorianoDocument2 pagesEEE 54 DP1 Documentation - Mendoza - SorianoDarl John MendozaNo ratings yet

- Monty B Bode Plots and First Order Filters ReportDocument11 pagesMonty B Bode Plots and First Order Filters ReportMonts 42No ratings yet

- Circuits Lab Program Manual (1-6 Exp)Document46 pagesCircuits Lab Program Manual (1-6 Exp)727722euec122No ratings yet

- Unusual Filter CktsDocument46 pagesUnusual Filter Cktsraineymj100% (1)

- Roychan's Sem 1 ReportDocument13 pagesRoychan's Sem 1 Reportroychan1012No ratings yet

- 2 Ask, PSK, FSKDocument15 pages2 Ask, PSK, FSKI AM A PROGRAMMERNo ratings yet

- The Radio ReportDocument11 pagesThe Radio Reportxavier bourret sicotteNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Application Note ANP 16: Loop Compensation of Voltage-Mode Buck ConvertersDocument9 pagesApplication Note ANP 16: Loop Compensation of Voltage-Mode Buck ConvertersNguyen Thanh TuanNo ratings yet

- Band-Pass Filtered, Inverting - 40 DB Attenuator, 10 HZ - 100 KHZ, 0.1 DB ErrorDocument20 pagesBand-Pass Filtered, Inverting - 40 DB Attenuator, 10 HZ - 100 KHZ, 0.1 DB ErrorSalman ZafarNo ratings yet

- (AMW0003) Design of A Simple Tunable Switchable Bandpass FilterDocument5 pages(AMW0003) Design of A Simple Tunable Switchable Bandpass FilterSamer Ehab Ibrahim YounisNo ratings yet

- Morse Code Astable OscillatorDocument2 pagesMorse Code Astable OscillatorFeher Catalin100% (1)

- Daniel Proj 1997 Transcond AmpDocument15 pagesDaniel Proj 1997 Transcond AmpIbrahim MuhammedNo ratings yet

- Three Bit Phase Shifter: MMIC Project Final Report EE525.787 Fall 2007Document16 pagesThree Bit Phase Shifter: MMIC Project Final Report EE525.787 Fall 2007eesharifNo ratings yet

- Impact of The Layout Components and FiltersDocument21 pagesImpact of The Layout Components and Filtersnexy bNo ratings yet

- Passive Low Pass RC FiltersDocument8 pagesPassive Low Pass RC FiltersSayuri CastellanosNo ratings yet

- 5 KHZ Cut-Off Frequency: F Vin F VoutDocument7 pages5 KHZ Cut-Off Frequency: F Vin F VoutLukman MuhammadNo ratings yet

- Ring OscillatorDocument12 pagesRing OscillatorCmeLiv InmyHart NpaynoRentNo ratings yet

- 8 ModulationDocument8 pages8 ModulationAhmadAkhbariNo ratings yet

- Demonstration of A Switched Resonator Concept in A Dual-Band Monolithic CMOS LC-nned VCODocument4 pagesDemonstration of A Switched Resonator Concept in A Dual-Band Monolithic CMOS LC-nned VCOJeong-geun KimNo ratings yet

- AN1207 For MC145170Document6 pagesAN1207 For MC145170ftbenji123No ratings yet

- Some Aspects of The Design of Balanced Rectifier Modulators For Precision ApplicationsDocument12 pagesSome Aspects of The Design of Balanced Rectifier Modulators For Precision ApplicationsshirtquittersNo ratings yet

- Experiment Number 7 Phase Locked Loop (PLL) : The Lock RangeDocument4 pagesExperiment Number 7 Phase Locked Loop (PLL) : The Lock RangeNikita KanchanNo ratings yet

- Electronic Lab ManualDocument22 pagesElectronic Lab ManualnssgdcyellanduNo ratings yet

- Ecad Lab ManualDocument83 pagesEcad Lab ManualJacklyn Untalan100% (1)

- High Pass FilterDocument5 pagesHigh Pass FilterGilberto ManhattanNo ratings yet

- Fermin Energy LevelDocument13 pagesFermin Energy LevelSemiu AdelekeNo ratings yet

- Figure 2. Voltage Mode Amplifier CircuitDocument2 pagesFigure 2. Voltage Mode Amplifier CircuitHadi KhanmohammadiNo ratings yet

- Lm331 AppnoteDocument8 pagesLm331 AppnoteEward KenNo ratings yet

- A New Control Structure For Grid-Connected LCLDocument7 pagesA New Control Structure For Grid-Connected LCLpmih1No ratings yet

- L211 Series Resonance and TimeFrequency Response of Passive Networks PDFDocument25 pagesL211 Series Resonance and TimeFrequency Response of Passive Networks PDFglenlcy100% (1)

- Subwoofer Active Low Pass FilterDocument11 pagesSubwoofer Active Low Pass FilterFrank De Leon VailNo ratings yet

- Filter DesignDocument6 pagesFilter Designnaga7389No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Analysis and Design of Multicell DC/DC Converters Using Vectorized ModelsFrom EverandAnalysis and Design of Multicell DC/DC Converters Using Vectorized ModelsNo ratings yet

- High-Speed PCB Design GuideDocument115 pagesHigh-Speed PCB Design GuideJonathan100% (4)

- RAM Job Interview Questions and AnswersDocument8 pagesRAM Job Interview Questions and AnswersmohamedNo ratings yet

- 8Gb DDR3L-1284459Document206 pages8Gb DDR3L-1284459mohamedNo ratings yet

- What Do You Mean by Pure Virtual Functions? 5. What Does Extern Mean in A Function Declaration?Document1 pageWhat Do You Mean by Pure Virtual Functions? 5. What Does Extern Mean in A Function Declaration?mohamedNo ratings yet

- Dimensions: (MM) Recommended Land Pattern: (MM) Electrical PropertiesDocument8 pagesDimensions: (MM) Recommended Land Pattern: (MM) Electrical PropertiesmohamedNo ratings yet

- Computer Networks 2 MarksDocument17 pagesComputer Networks 2 MarksmohamedNo ratings yet

- Floating Point Representation ExamplesDocument2 pagesFloating Point Representation ExamplesmohamedNo ratings yet

- Computer Networks 2 MarksDocument17 pagesComputer Networks 2 MarksmohamedNo ratings yet

- Quad, 14-Bit, High-Accuracy, 16V Output, Serial Input Digital-To-Analog ConverterDocument42 pagesQuad, 14-Bit, High-Accuracy, 16V Output, Serial Input Digital-To-Analog ConvertermohamedNo ratings yet

- Antamount: Vishay SpragueDocument22 pagesAntamount: Vishay SpraguemohamedNo ratings yet

- Parallel AES Encryption EnginesDocument12 pagesParallel AES Encryption EnginesmohamedNo ratings yet

- ProtocolsDocument8 pagesProtocolscaje_mac6960No ratings yet

- Form 31: Application For Transfer of Ownership in The Name of The Person Succeeding To The Possession of The VehicleDocument2 pagesForm 31: Application For Transfer of Ownership in The Name of The Person Succeeding To The Possession of The VehiclemohamedNo ratings yet

- SVTB TutorialDocument70 pagesSVTB TutorialmohamedNo ratings yet

- DT Processing of Conti - Signals MITRA PDFDocument54 pagesDT Processing of Conti - Signals MITRA PDFNarasimhamNo ratings yet

- MF10-N Universal Monolithic Dual Switched Capacitor Filter: Features DescriptionDocument35 pagesMF10-N Universal Monolithic Dual Switched Capacitor Filter: Features DescriptionAlbeiro Yr TrancerNo ratings yet

- FirDocument27 pagesFirvirat sharmaNo ratings yet

- Signals and Systems Using Matlab Chapter 7 - Fourier Analysis in Communications and FilteringDocument21 pagesSignals and Systems Using Matlab Chapter 7 - Fourier Analysis in Communications and FilteringDiluNo ratings yet

- Finals DSP WithMinimalErrors PDFDocument64 pagesFinals DSP WithMinimalErrors PDFanembam putobungbongNo ratings yet

- Materi Workshop MATLAB+WSDocument87 pagesMateri Workshop MATLAB+WSDinda Dwi SeptianiNo ratings yet

- Lec 9Document108 pagesLec 9Trần Nhật DươngNo ratings yet

- Microwave Filters-Applications and TechnologyDocument12 pagesMicrowave Filters-Applications and Technologyalokcena007No ratings yet

- Lab Ex 5Document7 pagesLab Ex 5bvlinh041No ratings yet

- Digital Signal Processing-SubhaDocument18 pagesDigital Signal Processing-SubhaNagammaieieNo ratings yet

- Vasil o Poulos 2006Document12 pagesVasil o Poulos 2006Tanjiro NadivaNo ratings yet

- Digital Filter DesignDocument360 pagesDigital Filter DesignLakshmi Doravari100% (3)

- EC3492 - DIGITAL SIGNAL PROCESSING-923183941-question Bank DSP 21 RegDocument17 pagesEC3492 - DIGITAL SIGNAL PROCESSING-923183941-question Bank DSP 21 Reggunasekaran kNo ratings yet

- Chapter 4Document24 pagesChapter 4422h0049No ratings yet

- Project Assignment: R. Nassif, ECE Department, AUB EECE 491-691, Digital Signal ProcessingDocument3 pagesProject Assignment: R. Nassif, ECE Department, AUB EECE 491-691, Digital Signal ProcessingHussein BayramNo ratings yet

- EIE3510Assignment 3 - FinalDocument2 pagesEIE3510Assignment 3 - FinalYabin CHENGNo ratings yet

- Application of The Chebyshev Polynomials To Approximation and Construction of Map ProjectionsDocument10 pagesApplication of The Chebyshev Polynomials To Approximation and Construction of Map ProjectionsEdinson Figueroa FernandezNo ratings yet

- Features Applications: High-Pass Out R Band-Pass Out Low-Pass OutDocument6 pagesFeatures Applications: High-Pass Out R Band-Pass Out Low-Pass OutAnonymous Uk3JxlHANo ratings yet

- 3 Design of RF and Microwave FiltersDocument44 pages3 Design of RF and Microwave FiltersAkmal Nurhakim100% (1)

- Butterworth Filter DesignDocument23 pagesButterworth Filter Designbriannguyen.eteNo ratings yet

- DSP Manual HamdardDocument52 pagesDSP Manual HamdardMuhammad IrfanNo ratings yet

- D 119Document35 pagesD 119Mohammad Ayatullah MaktoomNo ratings yet

- Labview Digital Filter Design Toolkit Api Reference 2024-04-19-01-39-07Document149 pagesLabview Digital Filter Design Toolkit Api Reference 2024-04-19-01-39-07ridwankayode55No ratings yet

- Unit 5Document105 pagesUnit 5Senthilkumar PandianNo ratings yet

- Signal Processing: Design of IIR FiltersDocument94 pagesSignal Processing: Design of IIR FiltersTrần Nhật DươngNo ratings yet

- Aim and Objective of The Course:: Course Structure Analysis Subject WiseDocument10 pagesAim and Objective of The Course:: Course Structure Analysis Subject WisepriyakanthrNo ratings yet

- Optimizing Arduino and The AD9851 DDS Signal GeneratorDocument8 pagesOptimizing Arduino and The AD9851 DDS Signal GeneratorDAvid DavidsonNo ratings yet

- Exp 10 DSPDocument6 pagesExp 10 DSPKAUSALYA R (RA2011052010013)No ratings yet

- Lab 5. FIR & IIR Filters in Matlab: Filter DesignDocument12 pagesLab 5. FIR & IIR Filters in Matlab: Filter DesignDrakshayaniMurgodNo ratings yet

- 10.chebyshev FilterDocument6 pages10.chebyshev FilterNARENDRANo ratings yet