Chip Multicore Processors - Tutorial 8: Task 8.1: Performance of Snooping-Based Cache Coherency

Uploaded by

Bobby BeamanChip Multicore Processors - Tutorial 8: Task 8.1: Performance of Snooping-Based Cache Coherency

Uploaded by

Bobby BeamanMUNCHEN TECHNISCHE UNIVERSITAT Lehrstuhl f ur Integrierte Systeme

Chip Multicore Processors Tutorial 8

June 19, 2013

Task 8.1: Performance of Snooping-based Cache Coherency

In this task the performance of snooping-based cache coherency is evaluated. The starting state of a system with three processor cores and their caches is depicted. Each cache entry is the state of the coherency protocol, the tag und two data words. All addresses are hexadecimal and the tag is depicted simpleed as the cahe lines base address of the cache line. Data is also simpleed. You also nd the start state of the memory. As discussed in the previous tutorial, the timing behavior and the performance depend on the coherency implementation. The given implementation for mobile systems is optimized towards power eciency, so that accesses to the external memory should be minimized. The system has the following properties: In case of a hit, no extra stall cycles are required. In case of a miss, Nmem = 40 cycles are required when the block is loaded from memory. In case another cache holds the cache block currrently, it can provide the data within Ncache = 16 to other caches. An invalidation delays the execution by Ninv = 4 cycles. A write back delays the execution by Nwb = 40 cycles. Given is following operation sequence: sequence 1: (P1) read 410 (P2) read 410 (P0) read 430 sequence 2: (P0) write 420, 42 (P2) read 424 (P2) write 424, 23 sequence 3: (P0) write 408, 7 (P2) read 408 (P0) write 408, 9

1: 2: 3:

nomenclature: (CPU) read address and (CPU) write addresse, value. a) Give the changes of the cache entries of each sequence (separately) according to the MSI protocol. Use the following tables for the changes after each operation. Furthermore, give the delay of the whole sequence on execution.

2 sequence 1 Op CPU

Index

State

Tag

Data

sequence 2 Op CPU

Index

State

Tag

Data

sequence 3 Op CPU

Index

State

Tag

Data

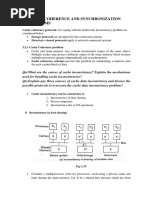

b) To optimize the external accesses an owner state (O) is added to the cache coherency protocol. On a write, all other cache entries should be invalidated (write-invalidate). Instead of the memory the current owner will give the data on a read access of another cache. Sketch the modied diagramm of the MOSI protocol.

Invalid

Shared

Modified

Owner

3 c) Perform the same procedure as in part a for the MOSI protocol in the following tables.

sequence 1 Op CPU

Index

State

Tag

Data

sequence 2 Op CPU

Index

State

Tag

Data

sequence 3 Op CPU

Index

State

Tag

Data

Task 8.2: Cache Coherency Example: Intel Nehalem

Read the article Memory Performance and Cache Coherency Eects on an Intel Nehalem Multiprocessor System, Daniel Molka et al., PACT 2009. Shortly describe the investigated architecture? What is decribed by the term ccNUMA? How do the information in the level 3 cache relate to the other levels and how precise is it? Shortly describe the executed benchmarks and central ndings of the article.

You might also like

- Yan Solihin - Fundamentals of Parallel Computer Architecture100% (2)Yan Solihin - Fundamentals of Parallel Computer Architecture547 pages

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Muge - Snoop Based Multiprocessor DesignNo ratings yetMuge - Snoop Based Multiprocessor Design32 pages

- Chip Multicore Processors - Tutorial 7: Task 7.1: Memory Overhead of Cache CoherencyNo ratings yetChip Multicore Processors - Tutorial 7: Task 7.1: Memory Overhead of Cache Coherency2 pages

- Shared Memory Architecture Concepts and Performance Issues: OutlineNo ratings yetShared Memory Architecture Concepts and Performance Issues: Outline7 pages

- L39 - Centralized Shared Memory ArchitecturesNo ratings yetL39 - Centralized Shared Memory Architectures31 pages

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- PlayStation 2 Architecture: Architecture of Consoles: A Practical Analysis, #12From EverandPlayStation 2 Architecture: Architecture of Consoles: A Practical Analysis, #12No ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Cache Coherence Protocols: Evaluation Using A Multiprocessor Simulation ModelNo ratings yetCache Coherence Protocols: Evaluation Using A Multiprocessor Simulation Model26 pages

- Dcos: Cache Embedded Switch Architecture For Distributed Shared Memory Multiprocessor SocsNo ratings yetDcos: Cache Embedded Switch Architecture For Distributed Shared Memory Multiprocessor Socs4 pages

- CS 523 Advanced Computer Architecture: Introduction To Cache Coherence ProtocolsNo ratings yetCS 523 Advanced Computer Architecture: Introduction To Cache Coherence Protocols24 pages

- Computer Architecture: Multiprocessors Shared Memory Architectures Prof. Jerry Breecher CSCI 240 Fall 2003No ratings yetComputer Architecture: Multiprocessors Shared Memory Architectures Prof. Jerry Breecher CSCI 240 Fall 200324 pages

- LPIC-3 Exam 306-300 Mastery: 500 Practice Questions on High Availability & Storage ClustersFrom EverandLPIC-3 Exam 306-300 Mastery: 500 Practice Questions on High Availability & Storage ClustersNo ratings yet

- Cache Coherency in Multiprocessors (MPS) / Multi-Cores: Topic 9No ratings yetCache Coherency in Multiprocessors (MPS) / Multi-Cores: Topic 979 pages

- Cache Coherence: - According To Webster's DictionaryNo ratings yetCache Coherence: - According To Webster's Dictionary15 pages

- Memory Hierarchy: Haresh Dagale Dept of ESENo ratings yetMemory Hierarchy: Haresh Dagale Dept of ESE32 pages

- Nintendo 64 Architecture: Architecture of Consoles: A Practical Analysis, #8From EverandNintendo 64 Architecture: Architecture of Consoles: A Practical Analysis, #8No ratings yet

- Cache Coherence: CSE 661 - Parallel and Vector ArchitecturesNo ratings yetCache Coherence: CSE 661 - Parallel and Vector Architectures37 pages

- Pattern Based Cache Coherency ArchitectuNo ratings yetPattern Based Cache Coherency Architectu13 pages

- Shared-Memory Architectures: Adapted From A Lecture by Ian Watson, University of MachesterNo ratings yetShared-Memory Architectures: Adapted From A Lecture by Ian Watson, University of Machester33 pages

- Cache Coherence: Write-Invalidate Snooping Protocol For Write-BackNo ratings yetCache Coherence: Write-Invalidate Snooping Protocol For Write-Back21 pages

- Electronic Structure Calculations on Graphics Processing Units: From Quantum Chemistry to Condensed Matter PhysicsFrom EverandElectronic Structure Calculations on Graphics Processing Units: From Quantum Chemistry to Condensed Matter PhysicsRoss C. WalkerNo ratings yet

- Cache Coherence: Computer Science & Artificial Intelligence LabNo ratings yetCache Coherence: Computer Science & Artificial Intelligence Lab36 pages

- A Survey of Cache Coherence Mechanisms in Shared MNo ratings yetA Survey of Cache Coherence Mechanisms in Shared M27 pages

- Cache Coherence: Part I: CMU 15-418: Parallel Computer Architecture and Programming (Spring 2012)No ratings yetCache Coherence: Part I: CMU 15-418: Parallel Computer Architecture and Programming (Spring 2012)31 pages

- Mehmet Senvar - Cache Coherence ProtocolsNo ratings yetMehmet Senvar - Cache Coherence Protocols30 pages

- CSA Mod 3-Part 2 Notes (Cache Coherence)No ratings yetCSA Mod 3-Part 2 Notes (Cache Coherence)19 pages

- 1.symmetric and Distributed Shared Memory Architectures79% (19)1.symmetric and Distributed Shared Memory Architectures29 pages

- Cache Coherence and Synchronization - TutorialspointNo ratings yetCache Coherence and Synchronization - Tutorialspoint7 pages

- Multiprocessing: Flynn's Classification (1966)No ratings yetMultiprocessing: Flynn's Classification (1966)8 pages

- Chip Multicore Processors - Tutorial 11: Task 11.1: RoutingNo ratings yetChip Multicore Processors - Tutorial 11: Task 11.1: Routing2 pages

- Chip Multicore Processors - Tutorial 10: Task 10.1: Why On-Chip Coherence Is Here To StayNo ratings yetChip Multicore Processors - Tutorial 10: Task 10.1: Why On-Chip Coherence Is Here To Stay2 pages

- Chip Multicore Processors - Tutorial 6: Task 6.1: Cache MissesNo ratings yetChip Multicore Processors - Tutorial 6: Task 6.1: Cache Misses1 page

- Chip Multicore Processors - Tutorial 5: Task 5.1: SemaphoresNo ratings yetChip Multicore Processors - Tutorial 5: Task 5.1: Semaphores1 page

- Chip Multicore Processors - Tutorial 4: Task 4.1: Counter ImplementationNo ratings yetChip Multicore Processors - Tutorial 4: Task 4.1: Counter Implementation1 page

- Chip Multicore Processors - Tutorial 2: 2.1: Frequency and Voltage Scaling, Amdahl's LawNo ratings yetChip Multicore Processors - Tutorial 2: 2.1: Frequency and Voltage Scaling, Amdahl's Law2 pages

- Chip Multicore Processors - Tutorial 3: 3.1: 3-Thread LockNo ratings yetChip Multicore Processors - Tutorial 3: 3.1: 3-Thread Lock2 pages

- Final Exam System On Chip Solutions in Networking SS 2010No ratings yetFinal Exam System On Chip Solutions in Networking SS 201012 pages

- 2008 FinalExam SoCN Final Master SolutionNo ratings yet2008 FinalExam SoCN Final Master Solution10 pages

- Final Exam System On Chip Solutions in Networking SS 2007No ratings yetFinal Exam System On Chip Solutions in Networking SS 200710 pages

- ECE 6100 Project 3: Implementation of Cache Coherence ProtocolsNo ratings yetECE 6100 Project 3: Implementation of Cache Coherence Protocols6 pages

- Chip Multicore Processors - Tutorial 8: Task 8.1: Performance of Snooping-Based Cache CoherencyNo ratings yetChip Multicore Processors - Tutorial 8: Task 8.1: Performance of Snooping-Based Cache Coherency3 pages

- Verification and Computer Architecture Important LinksNo ratings yetVerification and Computer Architecture Important Links22 pages

- Parallel Computing Pastpaper Solve by Noman TariqNo ratings yetParallel Computing Pastpaper Solve by Noman Tariq30 pages