Data Sheet: HEF4013B Flip-Flops Dual D-Type Flip-Flop

Data Sheet: HEF4013B Flip-Flops Dual D-Type Flip-Flop

Uploaded by

PedroZevallosCopyright:

Available Formats

Data Sheet: HEF4013B Flip-Flops Dual D-Type Flip-Flop

Data Sheet: HEF4013B Flip-Flops Dual D-Type Flip-Flop

Uploaded by

PedroZevallosOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Data Sheet: HEF4013B Flip-Flops Dual D-Type Flip-Flop

Data Sheet: HEF4013B Flip-Flops Dual D-Type Flip-Flop

Uploaded by

PedroZevallosCopyright:

Available Formats

INTEGRATED CIRCUITS

DATA SHEET

For a complete data sheet, please also download:

The IC04 LOCMOS HE4000B Logic

Family Specifications HEF, HEC

The IC04 LOCMOS HE4000B Logic

Package Outlines/Information HEF, HEC

HEF4013B

flip-flops

Dual D-type flip-flop

Product specification

File under Integrated Circuits, IC04

January 1995

Philips Semiconductors

Product specification

HEF4013B

flip-flops

Dual D-type flip-flop

DESCRIPTION

FUNCTION TABLES

The HEF4013B is a dual D-type flip-flop which features

independent set direct (SD), clear direct (CD), clock inputs (CP)

and outputs (O, O). Data is accepted when CP is LOW and

transferred to the output on the positive-going edge of the

clock. The active HIGH asynchronous

clear-direct (CD) and set-direct (SD) are independent and

override the D or CP inputs. The outputs are buffered for best

system performance. Schmitt-trigger action in the clock input

makes the circuit highly tolerant to slower clock rise and fall

times.

INPUTS

OUTPUTS

SD

CD

CP

INPUTS

OUTPUTS

D

On 1

On1

SD

CD

L

L

CP

Notes

1. H = HIGH state (the more positive voltage)

L=LOW state (the less positive voltage)

X=state is immaterial

= positive-going transition

On 1 = state after clock positive transition

PINNING

D

data inputs

CP

clock input (L to H edge-triggered)

SD

asynchronous set-direct input (active HIGH) CD

asynchronous clear-direct input (active HIGH) O

true

output

O

Fig.1 Functional diagram.

complement output

HEF4013BP(N):

14-lead DIL; plastic

(SOT27-1)

HEF4013BD(F):

14-lead DIL; ceramic (cerdip)

HEF4013BT(D):

14-lead SO; plastic

(SOT73)

(SOT108-1)

( ): Package Designator North America

FAMILY DATA, I DD LIMITS category FLIP-FLOPS See

Fig.2 Pinning diagram.

January 1995

Family Specifications

Philips Semiconductors

Product specification

HEF4013B

flip-flops

Dual D-type flip-flop

January 1995

Philips Semiconductors

Product specification

HEF4013B

flip-flops

Dual D-type flip-flop

AC CHARACTERISTICS

VSS = 0 V; Tamb = 25

C; CL = 50 pF; input transition times 20 ns

VDD

V

SYMBOL

MIN.

TYPICAL EXTRAPOLATION

FORMULA

TYP.

MAX.

110

220

ns

83 ns

(0,55 ns/pF) CL

Propagation delays

CP O, O

HIGH to LOW

LOW to HIGH

SD O

HIGH to LOW

SD O

LOW to HIGH

45

90

ns

34 ns

(0,23 ns/pF) CL

15

30

60

ns

22 ns

(0,16 ns/pF) CL

95

190

ns

68 ns

(0,55 ns/pF) CL

10

tPHL

40

80

ns

29 ns

(0,23 ns/pF) CL

15

30

60

ns

22 ns

(0,16 ns/pF) CL

5

10

100

40

200

80

ns

ns

73 ns

29 ns

(0,55 ns/pF) CL

(0,23 ns/pF) CL

15

30

60

ns

22 ns

(0,16 ns/pF) CL

5

10

75

35

150

70

ns

ns

48 ns

24 ns

(0,55 ns/pF) CL

(0,23 ns/pF) CL

25

50

ns

17 ns

(0,16 ns/pF) CL

100

40

200

80

ns

ns

73 ns

29 ns

(0,55 ns/pF) CL

(0,23 ns/pF) CL

30

60

ns

22 ns

(0,16 ns/pF) CL

60

30

120

60

ns

ns

33 ns

19 ns

(0,55 ns/pF) CL

(0,23 ns/pF) CL

15

20

40

ns

12 ns

(0,16 ns/pF) CL

60

120

ns

10 ns

(1,0 ns/pF) CL

10

tPLH

tPHL

tPLH

15

CD O

HIGH to LOW

5

10

tPHL

15

CD O

LOW to HIGH

Output transition times

HIGH to LOW

LOW to HIGH

5

10

tPLH

30

60

ns

9 ns

(0,42 ns/pF) CL

15

20

40

ns

6 ns

(0,28 ns/pF) CL

60

120

ns

10 ns

30

60

ns

9 ns

(0,42 ns/pF) CL

20

40

ns

6 ns

(0,28 ns/pF) CL

10

10

tTHL

tTLH

15

January 1995

(1,0 ns/pF) CL

Philips Semiconductors

Product specification

HEF4013B

flip-flops

Dual D-type flip-flop

AC CHARACTERISTI CS

VSS = 0 V; Tamb = 25C; CL

= 50 pF; input transition times 20

VDD

V

Set-up time

D CP

10

Hold time

D CP

Minimum clock

pulse width; LOW

Minimum SD pulse

width; HIGH

Minimum CD pulse

width; HIGH

Recovery time

for SD

Recovery time

for CD

Maximum clock

pulse frequency

SYMBOL

MIN.

ns

TYP.

40

20

ns

25

10

ns

15

15

ns

20

ns

10

20

ns

15

15

ns

60

30

ns

10

30

15

ns

15

20

10

ns

50

25

ns

24

12

ns

15

20

10

ns

50

25

ns

10

10

tsu

thold

tWCPL

tWSDH

24

12

ns

15

20

10

ns

15

ns

10

tWCDH

15

ns

15

15

ns

40

25

ns

10

tRSD

25

10

ns

25

10

ns

14

MHz

14

28

MHz

20

40

MHz

10

VDD

V

tRCD

see also waveforms

Figs 4 and 5

15

15

fmax

TYPICAL FORMULA FOR P (W)

850 fi (foCL) VDD 2

dissipation per

10

3 600 fi (foCL) VDD 2

package (P)

15

9 000 fi (foCL) VDD 2

Dynamic power

MAX.

where

fi = input freq. (MHz)

fo = output freq. (MHz)

CL = total load cap. (pF)

(foCL) = sum of outputs

VDD = supply voltage (V)

January 1995

Philips Semiconductors

Product specification

HEF4013B

flip-flops

Dual D-type flip-flop

Fig.4

Waveforms showing set-up times, hold times and minimum clock pulse width. Set-up and hold times are

shown as positive values but may be specified as negative values.

Fig.5 Waveforms showing recovery times for SD and CD; minimum SD and CD pulse widths.

January 1995

Philips Semiconductors

Product specification

HEF4013B

flip-flops

Dual D-type flip-flop

APPLICATION INFORMATION

Some examples of applications for the HEF4013B are:

Counters/dividers

Registers

Toggle flip-flops

Fig.6 Typical application of the HEF4013B in an n-stage shift register.

Fig.7 Typical application of the HEF4013B in a binary ripple up-counter; divide-by-2n.

Fig.8 Typical application of the HEF4013B in a modified ring counter; divide-by-(n + 1).

January 1995

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

You might also like

- Data Sheet: HEF4013B Flip-FlopsDocument7 pagesData Sheet: HEF4013B Flip-Flopsanon_95251911No ratings yet

- Data Sheet: HEF4511B MSIDocument11 pagesData Sheet: HEF4511B MSIBruno SouzaNo ratings yet

- DatasheetDocument7 pagesDatasheetRon de CañaNo ratings yet

- Data Sheet: HEF4093B GatesDocument7 pagesData Sheet: HEF4093B GatesEvelyn Soledad Perez PerezNo ratings yet

- 40193Document9 pages40193Merényi OszkárNo ratings yet

- Hef 4093BDocument6 pagesHef 4093BCristiano BruschiniNo ratings yet

- Hef 4049 BDocument4 pagesHef 4049 BBrzata PticaNo ratings yet

- Hef 4069Document7 pagesHef 4069makkasiNo ratings yet

- Data Sheet: HEF40174B MSIDocument6 pagesData Sheet: HEF40174B MSIPedroZevallosNo ratings yet

- Data Sheet: HEF40195B MSIDocument9 pagesData Sheet: HEF40195B MSIPedroZevallosNo ratings yet

- Data Sheet: HEF4070B GatesDocument3 pagesData Sheet: HEF4070B GatesBrzata PticaNo ratings yet

- 40174Document5 pages40174Merényi OszkárNo ratings yet

- Hef 4011Document3 pagesHef 4011TC Tekin ErcanNo ratings yet

- Data Sheet: HEF40175B MSIDocument5 pagesData Sheet: HEF40175B MSIcataclgNo ratings yet

- Data Sheet: HEF4543B MSIDocument9 pagesData Sheet: HEF4543B MSIPaulo RomeuNo ratings yet

- Hef 4093B PDFDocument6 pagesHef 4093B PDFCristiano BruschiniNo ratings yet

- Hef 4071 BDocument3 pagesHef 4071 BBrzata PticaNo ratings yet

- Data Sheet: HEF4070B GatesDocument4 pagesData Sheet: HEF4070B GatesDouglas FariasNo ratings yet

- Data Sheet: HEF4081B GatesDocument3 pagesData Sheet: HEF4081B Gatesvladyonutz91No ratings yet

- 4081Document3 pages4081Halyson GomesNo ratings yet

- Hcf4017 Data Sheet 2Document8 pagesHcf4017 Data Sheet 2Filipe CoimbraNo ratings yet

- Datasheet IC 4017Document8 pagesDatasheet IC 4017Tri KusbiantoNo ratings yet

- Data Sheet: HEF4068B GatesDocument3 pagesData Sheet: HEF4068B GatesBrzata PticaNo ratings yet

- 4538B Data SheetDocument10 pages4538B Data SheetpandaypiraNo ratings yet

- HEF4075B GatesDocument3 pagesHEF4075B GatesBerk TekerNo ratings yet

- Data Sheet: 74HC/HCT74Document13 pagesData Sheet: 74HC/HCT74Anubhav YadavNo ratings yet

- Data Sheet: HEF4073B GatesDocument3 pagesData Sheet: HEF4073B GatesBrzata PticaNo ratings yet

- Hef 4001 Quadruple InputDocument3 pagesHef 4001 Quadruple Inputwlen2012No ratings yet

- 74HC4543Document12 pages74HC4543Anung PriyantoNo ratings yet

- Data Sheet: HEF4014B MSIDocument7 pagesData Sheet: HEF4014B MSIPedroZevallosNo ratings yet

- Datasheet HFE4069 UBPDocument7 pagesDatasheet HFE4069 UBPMarcos SouzaNo ratings yet

- 4731BDocument3 pages4731BRaul Sedano LauNo ratings yet

- HEF4013B: 1. General DescriptionDocument15 pagesHEF4013B: 1. General DescriptionMuhammad Iqbal RasyidiNo ratings yet

- 74HC HCT574 CNV 2Document8 pages74HC HCT574 CNV 2thinh040No ratings yet

- 4518Document7 pages4518Brzata PticaNo ratings yet

- Data Sheet: HEF40193B MSIDocument10 pagesData Sheet: HEF40193B MSIPedroZevallosNo ratings yet

- 74F175, 74F175A Quad D Flip-Flop: Integrated CircuitsDocument11 pages74F175, 74F175A Quad D Flip-Flop: Integrated CircuitsroozbehxoxNo ratings yet

- 4052Document9 pages4052Brzata PticaNo ratings yet

- Integrated CircuitsDocument3 pagesIntegrated CircuitsharfecNo ratings yet

- Dual D-Type Flip-Flop: Integrated CircuitsDocument8 pagesDual D-Type Flip-Flop: Integrated CircuitsRakesh Kumar DNo ratings yet

- Hef 4508Document10 pagesHef 4508jcvoscribNo ratings yet

- Hef4082b PDFDocument3 pagesHef4082b PDFGoodLookingPirateNo ratings yet

- Hef4068b PDFDocument3 pagesHef4068b PDFGoodLookingPirateNo ratings yet

- 74HC HCT151 CNV 2Document8 pages74HC HCT151 CNV 2jomebaNo ratings yet

- CD54HC08, CD74HC08, CD54HCT08, CD74HCT08: Features DescriptionDocument13 pagesCD54HC08, CD74HC08, CD54HCT08, CD74HCT08: Features DescriptionWissam NawfalNo ratings yet

- Hef4025b PDFDocument3 pagesHef4025b PDFGoodLookingPirateNo ratings yet

- SP481E/SP485E Enhanced Low Power Half-Duplex RS-485 TransceiversDocument11 pagesSP481E/SP485E Enhanced Low Power Half-Duplex RS-485 TransceiverselecompinnNo ratings yet

- Data Sheet: 74HC/HCT173Document11 pagesData Sheet: 74HC/HCT173Bryan Bethke IIINo ratings yet

- Data Sheet: 74HC/HCT125Document6 pagesData Sheet: 74HC/HCT125Andes IndrayantoNo ratings yet

- HEF4007UBFDocument9 pagesHEF4007UBFJonathan NavaNo ratings yet

- Integrated CircuitsDocument3 pagesIntegrated CircuitsjgaranNo ratings yet

- 74 HC 4067Document15 pages74 HC 4067김경원No ratings yet

- Hef4081b PDFDocument3 pagesHef4081b PDFGoodLookingPirateNo ratings yet

- Hef 4069Document7 pagesHef 4069rharjaniNo ratings yet

- The Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsFrom EverandThe Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsSylvain ClercNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Data Sheet: HEF40174B MSIDocument6 pagesData Sheet: HEF40174B MSIPedroZevallosNo ratings yet

- Data Sheet: HEF40193B MSIDocument10 pagesData Sheet: HEF40193B MSIPedroZevallosNo ratings yet

- Data Sheet: HEF40194B MSIDocument9 pagesData Sheet: HEF40194B MSIPedroZevallosNo ratings yet

- Data Sheet: HEF40195B MSIDocument9 pagesData Sheet: HEF40195B MSIPedroZevallosNo ratings yet

- Data Sheet: HEF4014B MSIDocument7 pagesData Sheet: HEF4014B MSIPedroZevallosNo ratings yet

- Dual 4-Stage Static Shift Register: High-Voltage Silicon-Gate CMOSDocument6 pagesDual 4-Stage Static Shift Register: High-Voltage Silicon-Gate CMOSPedroZevallosNo ratings yet

- MC14018B Presettable Divide by N Counter: PDIP 16 P Suffix CASE 648Document9 pagesMC14018B Presettable Divide by N Counter: PDIP 16 P Suffix CASE 648PedroZevallosNo ratings yet

- XX01 CH-012 Manual Version2.1 A - 3-4Document2 pagesXX01 CH-012 Manual Version2.1 A - 3-4Arturo Yanez S.G.No ratings yet

- M 168Document376 pagesM 168long_address_shortNo ratings yet

- CS302 2005 2010 Midterm - Solved - MEGA FILEDocument91 pagesCS302 2005 2010 Midterm - Solved - MEGA FILEAli QureshiNo ratings yet

- Microcontroller and Interfacing LabDocument49 pagesMicrocontroller and Interfacing LabAkshat MishraNo ratings yet

- Prep Guide Adnan IITDDocument6 pagesPrep Guide Adnan IITDh20230162No ratings yet

- Large List of Intel Interview QuestionsDocument4 pagesLarge List of Intel Interview QuestionsvaghelamiralNo ratings yet

- PIC16C7X: 8-Bit CMOS Microcontrollers With A/D ConverterDocument34 pagesPIC16C7X: 8-Bit CMOS Microcontrollers With A/D ConvertersureshNo ratings yet

- VHDL Word FileDocument231 pagesVHDL Word FileAmit JangraNo ratings yet

- MIL-STD-806B Graphical Symbols For Logic Diagrams 19620226Document26 pagesMIL-STD-806B Graphical Symbols For Logic Diagrams 19620226bibliografia digitalesNo ratings yet

- EE 533 Lab #10: Convertible First-In First-Out (SRAM) MemoryDocument1 pageEE 533 Lab #10: Convertible First-In First-Out (SRAM) MemoryPokemonponponNo ratings yet

- Memory Address DecodingDocument31 pagesMemory Address DecodingMehulJainNo ratings yet

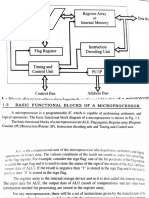

- The 8085 Microprocessor ArchitectureDocument26 pagesThe 8085 Microprocessor ArchitecturesantoshobraNo ratings yet

- Comparison of CMOS XOR and XNOR Gate DesignDocument104 pagesComparison of CMOS XOR and XNOR Gate Designksreddy2002No ratings yet

- Design of SPI (Serial Peripheral Interface) Protocol With DO-254 ComplianceDocument4 pagesDesign of SPI (Serial Peripheral Interface) Protocol With DO-254 ComplianceEditor IJRITCC100% (1)

- Module 8 Memory TestingDocument65 pagesModule 8 Memory Testinggangavinodc123No ratings yet

- Single Cycle Processor PPT by SvnitDocument88 pagesSingle Cycle Processor PPT by SvnitViren KathiriyaNo ratings yet

- Practical Work 3 - CMOS + Rubric PDFDocument25 pagesPractical Work 3 - CMOS + Rubric PDFRiki SmithNo ratings yet

- Functional BLK Diagram 8085Document3 pagesFunctional BLK Diagram 8085Clash JNo ratings yet

- Electronic Trainer Kit For The Basic Understanding of Electronic Circuits.Document85 pagesElectronic Trainer Kit For The Basic Understanding of Electronic Circuits.Syed Inam Ullah ShahNo ratings yet

- Programmable Logic ArraysDocument5 pagesProgrammable Logic ArraysSitotaw NigussieNo ratings yet

- 2014 Set BDocument19 pages2014 Set Bokay45486No ratings yet

- Embedded Systems Design UCS614: Assignment 1-4Document12 pagesEmbedded Systems Design UCS614: Assignment 1-4Pankaj GuptaNo ratings yet

- Basic Circuit For 8051Document54 pagesBasic Circuit For 8051uatulkarNo ratings yet

- Switching Theory and Logic DesignDocument8 pagesSwitching Theory and Logic DesignSubrahmanyam VjsNo ratings yet

- Assist Techniques For Radiation Hardened SRAM in Space ApplicationsDocument4 pagesAssist Techniques For Radiation Hardened SRAM in Space ApplicationsDr. M V GANESWARA RAONo ratings yet

- Lecture 16: Basic CPU Design: Today's Topics: Single-Cycle CPU Multi-Cycle CPUDocument12 pagesLecture 16: Basic CPU Design: Today's Topics: Single-Cycle CPU Multi-Cycle CPUgiga moviesNo ratings yet

- CS1104 - Computer Organization: Aaron Tan Tuck ChoyDocument30 pagesCS1104 - Computer Organization: Aaron Tan Tuck ChoyTaye ToluNo ratings yet

- Digital Design of A Digital CombinationDocument6 pagesDigital Design of A Digital CombinationemreNo ratings yet

- PIC16F84 Datasheet PDFDocument124 pagesPIC16F84 Datasheet PDFFuh ValleryNo ratings yet

- MOSFET - TutorialspointDocument3 pagesMOSFET - Tutorialspointgunasekaran k100% (1)