Professional Documents

Culture Documents

Tsmc018 Info

Tsmc018 Info

Uploaded by

Sure AvinashOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Tsmc018 Info

Tsmc018 Info

Uploaded by

Sure AvinashCopyright:

Available Formats

MOSIS WAFER ACCEPTANCE TESTS

RUN: T68B (MM_NON-EPI) VENDOR: TSMC

TECHNOLOGY: SCN018 FEATURE SIZE: 0.18 microns

Run type: SKD

INTRODUCTION: This report contains the lot average results obtained by MOSIS

from measurements of MOSIS test structures on each wafer of

this fabrication lot. SPICE parameters obtained from similar

measurements on a selected wafer are also attached.

COMMENTS: DSCN6M018_TSMC

TRANSISTOR PARAMETERS W/L N-CHANNEL P-CHANNEL UNITS

MINIMUM 0.27/0.18

Vth 0.50 -0.51 volts

SHORT 20.0/0.18

Idss 547 -250 uA/um

Vth 0.51 -0.51 volts

Vpt 4.8 -5.6 volts

WIDE 20.0/0.18

Ids0 14.4 -4.7 pA/um

LARGE 50/50

Vth 0.43 -0.42 volts

Vjbkd 3.1 -4.3 volts

Ijlk <50.0 <50.0 pA

K' (Uo*Cox/2) 175.4 -35.6 uA/V^2

Low-field Mobility 416.52 84.54 cm^2/V*s

COMMENTS: Poly bias varies with design technology. To account for mask

bias use the appropriate value for the parameters XL and XW

in your SPICE model card.

Design Technology XL (um) XW (um)

----------------- ------- ------

SCN6M_DEEP (lambda=0.09) 0.00 -0.01

thick oxide 0.00 -0.01

SCN6M_SUBM (lambda=0.10) -0.02 0.00

thick oxide -0.02 0.00

FOX TRANSISTORS GATE N+ACTIVE P+ACTIVE UNITS

Vth Poly >6.6 <-6.6 volts

PROCESS PARAMETERS N+ P+ POLY N+BLK PLY+BLK M1 M2 UNITS

Sheet Resistance 6.7 7.8 8.0 59.7 313.6 0.08 0.08 ohms/sq

Contact Resistance 10.6 11.0 10.0 4.79 ohms

Gate Oxide Thickness 41 angstrom

PROCESS PARAMETERS M3 POLY_HRI M4 M5 M6 N_W UNITS

Sheet Resistance 0.08 0.08 0.08 0.03 930 ohms/sq

Contact Resistance 9.24 14.05 18.39 20.69 ohms

COMMENTS: BLK is silicide block.

CAPACITANCE PARAMETERS N+ P+ POLY M1 M2 M3 M4 M5 M6 R_W D_N_W M5P N_W UNITS

Area (substrate) 942 1163 106 34 14 9 6 5 3 123 125 aF/um^2

Area (N+active) 8484 55 20 13 11 9 8 aF/um^2

Area (P+active) 8232 aF/um^2

Area (poly) 66 17 10 7 5 4 aF/um^2

Area (metal1) 37 14 9 6 5 aF/um^2

Area (metal2) 35 14 9 6 aF/um^2

Area (metal3) 37 14 9 aF/um^2

Area (metal4) 36 14 aF/um^2

Area (metal5) 34 984 aF/um^2

Area (r well) 920 aF/um^2

Area (d well) 582 aF/um^2

Area (no well) 137 aF/um^2

Fringe (substrate) 212 235 41 35 29 21 14 aF/um

Fringe (poly) 70 39 29 23 20 17 aF/um

Fringe (metal1) 52 34 22 19 aF/um

Fringe (metal2) 48 35 27 22 aF/um

Fringe (metal3) 53 34 27 aF/um

Fringe (metal4) 58 35 aF/um

Fringe (metal5) 55 aF/um

Overlap (N+active) 895 aF/um

Overlap (P+active) 737 aF/um

CIRCUIT PARAMETERS UNITS

Inverters K

Vinv 1.0 0.74 volts

Vinv 1.5 0.78 volts

Vol (100 uA) 2.0 0.08 volts

Voh (100 uA) 2.0 1.63 volts

Vinv 2.0 0.82 volts

Gain 2.0 -23.72

Ring Oscillator Freq.

D1024_THK (31-stg,3.3V) 300.36 MHz

DIV1024 (31-stg,1.8V) 363.77 MHz

Ring Oscillator Power

D1024_THK (31-stg,3.3V) 0.07 uW/MHz/gate

DIV1024 (31-stg,1.8V) 0.02 uW/MHz/gate

You might also like

- CD 4538Document10 pagesCD 4538Geraldo PereiraNo ratings yet

- BSIM4 4.8.1 Technical ManualDocument185 pagesBSIM4 4.8.1 Technical ManualdeancjenningsNo ratings yet

- Lab 3 Adventure GameDocument7 pagesLab 3 Adventure Gamevirjog100% (1)

- Some Solutions of Chapter 2 of Antenna Theory Analysis and Design of BalanisDocument14 pagesSome Solutions of Chapter 2 of Antenna Theory Analysis and Design of BalanisProttoy KadirNo ratings yet

- Boss BR-1180 Service NotesDocument35 pagesBoss BR-1180 Service NotesFernando Gómez67% (3)

- Robotics Chapter 4: Manipulator Kinematic: Phd. Nguyễn Hoàng GiápDocument31 pagesRobotics Chapter 4: Manipulator Kinematic: Phd. Nguyễn Hoàng GiápNguyễn Xuân TrườngNo ratings yet

- Source Follower: (Common-Drain Amplifier)Document40 pagesSource Follower: (Common-Drain Amplifier)Benj MendozaNo ratings yet

- DE2 115 Pin AssignmentDocument4 pagesDE2 115 Pin AssignmentKamal HaydarNo ratings yet

- 5- CH 5 Arithmetic and Logic Instructions - ١٢٢٠١٩Document44 pages5- CH 5 Arithmetic and Logic Instructions - ١٢٢٠١٩Boy azNo ratings yet

- Địa Chỉ Các Bit Trong Các Thanh Ghi Của PIC16F877A PDFDocument4 pagesĐịa Chỉ Các Bit Trong Các Thanh Ghi Của PIC16F877A PDFDanh_IS4No ratings yet

- Buck ConverterDocument13 pagesBuck ConverterDinesh MahtoNo ratings yet

- BJT Model From DatasheetDocument14 pagesBJT Model From DatasheetAngel Pérez SantiagoNo ratings yet

- Chapter 9 Microprocessor 8086Document57 pagesChapter 9 Microprocessor 8086shubhankar palNo ratings yet

- Cumulative 4-Bit AdderDocument2 pagesCumulative 4-Bit AdderSidhartha Sankar RoutNo ratings yet

- Frequency MeterDocument5 pagesFrequency Meterlaithnatour0% (1)

- Problems 3 (Chapter 4)Document3 pagesProblems 3 (Chapter 4)Thịnh NguyễnNo ratings yet

- TSMC 180 NMDocument5 pagesTSMC 180 NMtsmc12345No ratings yet

- BT19ECE067 Assignment 03Document11 pagesBT19ECE067 Assignment 03BT19ECE067 MiteshNo ratings yet

- TGSL - 101 - Part1Document25 pagesTGSL - 101 - Part1sorinn1987No ratings yet

- Timer LPC2148Document5 pagesTimer LPC2148yuvarajnarayanasamyNo ratings yet

- Robotic Arm Project PPT12Document13 pagesRobotic Arm Project PPT12Deepti Chaudhary0% (1)

- Robot Technology: Ch.7 Trajectory Planning of RobotsDocument53 pagesRobot Technology: Ch.7 Trajectory Planning of RobotsmubarakNo ratings yet

- VLSI Testing QuestionDocument5 pagesVLSI Testing QuestionAMIT VERMANo ratings yet

- AN-1525 Single Supply Operation of The DAC0800 and DAC0802: Application ReportDocument6 pagesAN-1525 Single Supply Operation of The DAC0800 and DAC0802: Application ReportYasin ArslanNo ratings yet

- Gpdk090 DRM PDFDocument128 pagesGpdk090 DRM PDFShobhit GargNo ratings yet

- Dac 0800 & Dac 0802 (An 1525)Document4 pagesDac 0800 & Dac 0802 (An 1525)HARICH90No ratings yet

- 5V Power Supply Using 7805 Voltage Regulator Ic AIMDocument2 pages5V Power Supply Using 7805 Voltage Regulator Ic AIMPrajith VbNo ratings yet

- Transistor As A Switch: Electronics and Communication Circuits Lab. Experiment #6Document5 pagesTransistor As A Switch: Electronics and Communication Circuits Lab. Experiment #6Eng. Ahmad ELsamakNo ratings yet

- Nand, Nor Gates, Circuit Minimization and Karnaugh Maps: Prof. Sin-Min Lee Department of Computer ScienceDocument62 pagesNand, Nor Gates, Circuit Minimization and Karnaugh Maps: Prof. Sin-Min Lee Department of Computer ScienceYONIWO EDWARD TSEMINo ratings yet

- Analog Guide Raja ReddyDocument30 pagesAnalog Guide Raja ReddySobir AliNo ratings yet

- PIC Instruction SetDocument64 pagesPIC Instruction SetHiru Purushothaman Hirudayanathan100% (2)

- Chapter 81Document30 pagesChapter 81Adnan KarimNo ratings yet

- HW Ông VinhDocument8 pagesHW Ông VinhQuốc Thắng NguyễnNo ratings yet

- Fx5u Pid Control Function PDFDocument38 pagesFx5u Pid Control Function PDFNutchaiSaengsurathamNo ratings yet

- AND GATE (7408) : A Y B Truth TableDocument14 pagesAND GATE (7408) : A Y B Truth TablepankajmadhuNo ratings yet

- Huffman Encoder and Decoder Using VerilogDocument3 pagesHuffman Encoder and Decoder Using VerilogInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- The Silicon Laboratories C8051F020Document89 pagesThe Silicon Laboratories C8051F020hani1986yeNo ratings yet

- Mos Field-Effect Transistors (Mosfets) : Section 5.1: Device Structure and Physical OperationDocument16 pagesMos Field-Effect Transistors (Mosfets) : Section 5.1: Device Structure and Physical OperationJohn Paul Alcantara Nidoy100% (1)

- Module WIFI TYWE3S User ManualDocument13 pagesModule WIFI TYWE3S User ManualPen TranNo ratings yet

- VLSI Notes 1 PDFDocument305 pagesVLSI Notes 1 PDFKishore KumarNo ratings yet

- DE2 Pin AssignmentsDocument8 pagesDE2 Pin Assignmentstuandt5No ratings yet

- TC 300 Uc InglesDocument62 pagesTC 300 Uc InglesTamo Activo MusicNo ratings yet

- Homework2 Soln DevDocument18 pagesHomework2 Soln DevDevaraj SubrmanayamNo ratings yet

- List of 8051 Microcontroller Special Function RegistersDocument10 pagesList of 8051 Microcontroller Special Function RegistersMamta JainNo ratings yet

- EE322 LAB3 ReportDocument6 pagesEE322 LAB3 ReportkynguyenNo ratings yet

- Stepper MotorDocument6 pagesStepper MotorSiddharth MishraNo ratings yet

- Pages by Bose-DigitalDocument15 pagesPages by Bose-DigitalJenny VarelaNo ratings yet

- SPWM CircuitDocument13 pagesSPWM Circuitchinnathambij100% (1)

- Design Rules-VlsiDocument9 pagesDesign Rules-VlsiPrabhat KumarNo ratings yet

- RTL Engineer ResumeDocument2 pagesRTL Engineer Resumekowsalya100% (2)

- Bipolar IC ProcessDocument5 pagesBipolar IC Processlachuns123No ratings yet

- Introduction To Cmos Vlsi Design: Silicon-on-Insulator (SOI)Document27 pagesIntroduction To Cmos Vlsi Design: Silicon-on-Insulator (SOI)TygerYashanshuNo ratings yet

- Lab 7 (Cascaded Amplifier Design) - Sept 20Document8 pagesLab 7 (Cascaded Amplifier Design) - Sept 20WilfredNo ratings yet

- VLSI Design Mid 2Document3 pagesVLSI Design Mid 2mohanNo ratings yet

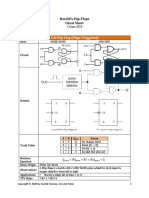

- Harolds Discrete Math Flip Flops Cheat Sheet 2020Document6 pagesHarolds Discrete Math Flip Flops Cheat Sheet 2020Nandini JayakumarNo ratings yet

- DBEC DATA Sheet Final - FAR PDFDocument1 pageDBEC DATA Sheet Final - FAR PDFMohd FarhanNo ratings yet

- Arduino IDE Geiger Counter DIY Kit RH K GK 1 LDocument24 pagesArduino IDE Geiger Counter DIY Kit RH K GK 1 LMissoft wares100% (1)

- VLSI 100 QuestionsDocument4 pagesVLSI 100 Questionsapi-3824368No ratings yet

- Modelvalues 250 NMDocument4 pagesModelvalues 250 NMraghuvlsiNo ratings yet

- Specifications: Component MeasurementsDocument4 pagesSpecifications: Component MeasurementsChristian BedoyaNo ratings yet

- Three-Phase LLC Converter Loss Input Parameter Parameter Value UnitDocument40 pagesThree-Phase LLC Converter Loss Input Parameter Parameter Value UnitVũ Hùng TrángNo ratings yet

- Unisonic Technologies Co., LTD: 4A, 600V N-Channel Power MosfetDocument9 pagesUnisonic Technologies Co., LTD: 4A, 600V N-Channel Power MosfetEmerson FerreiraNo ratings yet

- IO Ring Design PDFDocument20 pagesIO Ring Design PDFSure AvinashNo ratings yet

- EE 5341 MOS Device Modeling: Assignment 1: MOS Capacitor / JunctionDocument1 pageEE 5341 MOS Device Modeling: Assignment 1: MOS Capacitor / JunctionSure AvinashNo ratings yet

- Assignment 3Document19 pagesAssignment 3Sure AvinashNo ratings yet

- EC5311 - Digital IC Design: Assignment - 4Document6 pagesEC5311 - Digital IC Design: Assignment - 4Sure AvinashNo ratings yet

- Ee5311 Module 1 TransistorDocument41 pagesEe5311 Module 1 TransistorSure AvinashNo ratings yet

- Academic Calendar For 1st SemDocument1 pageAcademic Calendar For 1st SemSure AvinashNo ratings yet

- MOSFET QuestionsDocument23 pagesMOSFET QuestionsSure Avinash100% (2)

- Chap 1 Que SemiconductorPhysicsDocument7 pagesChap 1 Que SemiconductorPhysicsSure AvinashNo ratings yet

- How To Design A Step Up and Step Down Auto Transformer - MepitsDocument6 pagesHow To Design A Step Up and Step Down Auto Transformer - MepitsBASEER AHMADNo ratings yet

- Vitalograph ALPHA - Driver Installation GuideDocument8 pagesVitalograph ALPHA - Driver Installation GuideHenrri CanaviriNo ratings yet

- Ept Lab 15Document4 pagesEpt Lab 15Rasool Bux RajarNo ratings yet

- 00fk788 PDFDocument160 pages00fk788 PDFmihociuliNo ratings yet

- 35w LCD Monitor Power Supply SCHDocument2 pages35w LCD Monitor Power Supply SCHmiltoncgNo ratings yet

- Versions Available:: Aeterna Programming and UpdateDocument10 pagesVersions Available:: Aeterna Programming and UpdateBogicevic DejanNo ratings yet

- Epson Stylus Color 460 Service ManualDocument10 pagesEpson Stylus Color 460 Service ManualLuis GonzalezNo ratings yet

- Conference PaperDocument3 pagesConference PaperAngelica SutharNo ratings yet

- Physical Handout NotesDocument121 pagesPhysical Handout NotesJimmy MachariaNo ratings yet

- Conexión Piasini RF8. Mazda 6 2009 Tnx.Document4 pagesConexión Piasini RF8. Mazda 6 2009 Tnx.Maikel GonzálezNo ratings yet

- Toshiba Photocouplers and Photo RelaysDocument77 pagesToshiba Photocouplers and Photo RelaysEhab Anwar ElnagdyNo ratings yet

- Sa5532 PDFDocument22 pagesSa5532 PDFsimoel_itnNo ratings yet

- CSIT211 Computer ArchitectureDocument1 pageCSIT211 Computer Architectureभुपेन्द्र बोहराNo ratings yet

- SR - A Device Replication Installation Tariel KapanadzeDocument7 pagesSR - A Device Replication Installation Tariel KapanadzeSilviu Corcan100% (1)

- MTS46# G2WD-21Document2 pagesMTS46# G2WD-21NataliaNo ratings yet

- INTRO MOD 8-Protection Rev2016Document103 pagesINTRO MOD 8-Protection Rev2016Wang MariusNo ratings yet

- An Introduction To Software Defined Radio: November 2015Document5 pagesAn Introduction To Software Defined Radio: November 2015MarcosZelayaNo ratings yet

- TXNR 509Document105 pagesTXNR 509perico1962No ratings yet

- Meanwell SMPS CATLOGUE.Document1 pageMeanwell SMPS CATLOGUE.rajstarNo ratings yet

- Unit 3 DSDDocument107 pagesUnit 3 DSDGuru VelmathiNo ratings yet

- Interfacing The MSP430 and TMP100 Temperature SensorDocument7 pagesInterfacing The MSP430 and TMP100 Temperature SensorJohnny Di SantoNo ratings yet

- Basic Signal Communication MS-1Document16 pagesBasic Signal Communication MS-1Audrey RodrigoNo ratings yet

- RM3 TR1Document4 pagesRM3 TR1Sayak BoseNo ratings yet

- Gige Vision Camera Series (Poe) & (Poehs)Document32 pagesGige Vision Camera Series (Poe) & (Poehs)khiem nguyenNo ratings yet

- Bugging, Tapping and Listening In: Federal LawDocument5 pagesBugging, Tapping and Listening In: Federal Lawg_02No ratings yet

- 2SC3133Document464 pages2SC3133Pravin Mevada0% (1)

- 1mechanical Experiment Semiconductor Diode Biasing PracticalDocument17 pages1mechanical Experiment Semiconductor Diode Biasing PracticalJeferson RosalesNo ratings yet

- 24GHz RADAR Chip 107 WebDocument2 pages24GHz RADAR Chip 107 WebZhu LanNo ratings yet