MCQ Unit 2

MCQ Unit 2

Uploaded by

Darshana KodamCopyright:

Available Formats

MCQ Unit 2

MCQ Unit 2

Uploaded by

Darshana KodamOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

MCQ Unit 2

MCQ Unit 2

Uploaded by

Darshana KodamCopyright:

Available Formats

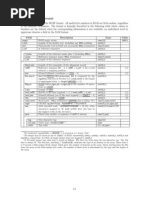

MCQ COMPUTER ORGANIZATION

Unit 2 & 3 7. Which register keeps the track of instruction

1. The load instruction is mostly used to designate stored in memory.

a transfer from memory to a processor register is A. AR (Address register)

known as B. XR (Index register)

A. Instruction register C. PC (Program counter)

B. Program counter D. AC (Accumulator)

C. Accumulator ANSWER: C

D. Memory address register

ANSWER: C 8. Load is a type of

A. Data transfer instruction

2. Intel i360,SPARC,IBM Rs. 16,000 are the B. Data processing instruction

examples of C. Program counter instruction

A. CISC processor D. None

B. RISC processor ANSWER: A

C. IBM processor

D. Intel processor 9. Assembler syntax for index addressing mode is

ANSWER: B A. Ri B. (Ri)

C. X(Ri) D. Ri+

3. A stack computer evaliates arithmatic and ANSWER: D

other expressions using a format known as

A. Stack notation 10. Intel i860,motorola M88100 and AMD 29000

B. Polish notation are example of

C. Either A or B A. CISC architecture B. RISC architecture

D. None of these C. Both A and B D. None

ANSWER: B ANSWER: B

4. Control unit design based on sequential logic 11. Width of fraction bit in case of IEEE standard

circuit is called as of single precision is

A. Microprogrammed control unit A. 8 bit B. 11 bit

B. Hardwired control unit C. 52 bit D. 23 bit

C. GCD processor ANSWER: D

D. None of these

ANSWER: B 12. The delay elements are used in

A. State table method

5. NDRO means B. Sequence counter method

A. The method of reading the memory destroys C. Both A and B

stored information D. Delay element method

B. The method of reading the memory does not effect ANSWER: D

the stored data

C. Both A & B 13. Characteristics of CISC are

D. None of these A. More addressing mode, large set of instruction,

ANSWER: B few GPR's

B. Less addressing mode, large set of instruction, few

6. Byte addresses can be assigned across words GPR's

according to lower byte addresses are used for the C. More addressing mode, few set of instruction, few

more significant bytes of the word called as GPR's

A. Little-endian B. Big-endian D. Less addressing mode, few set of instruction, more

C. Neither A nor B D. Can't say GPR's

ANSWER: B ANSWER: A

Mr. Ritesh S. Dayama

MCQ COMPUTER ORGANIZATION

14. Instruction cache and data cache are not 21. Addressing mode is

splited in case of A. Specification of opcode

A. CISC architecture B. Specification of operand

B. RISC architecture C. Specification of function

C. Both A and B D. All the above

D. None ANSWER: B

ANSWER: A

22. If the effective address is EA= [Ri] then he

15. Store is a type of type of addressing mode is

A. Data transfer instruction A. Immediate

B. Data processing instruction B. Index

C. Program counter instruction C. Direct

D. None D. Indirect

ANSWER: A ANSWER: D

16. In move M, R instruction, M is the memory 23. Hardware control unit design method is

and R is the register. The type of addressing mode A. Stae table method

is B. Delay element method

A. Absolute B. Indirect C. Sequence counter method

C. Register D. Index D. All of above

ANSWER: C ANSWER: D

17. Instruction format is variable in case of 24. Bitwise AND operation is a type of

A. CISC architecture A. Data transfer instruction

B. RISC architecture B. Data processing instruction

C. Both A and B C. Program counter instruction

D. None D. None

ANSWER: A ANSWER: D

18. Width of exponent field in case of IEEE 25. The assembler syntax for register based

standard for double precision is indirect addressing mode is

A. 11 bit B. 8 bit A. (Ri)

C. 52 bit D. 23 bit B. X (Ri)

ANSWER: A C. Ri

D. (Ri)+

19. The design method, which makes use of ANSWER: A

sequential cirsuit design is called

A. Delay element method 26. Intel i486, Motorola MC 68040 and NS 32532

B. Sequence counter method are examples of

C. State table method A. CISC architecture

D. All B. RISC architecture

ANSWER: C C. Both A and B

D. None

20. Assembly language format LDX is ANSWER: A

A. Data transfer instruction

B. Data processing instruction

C. Program control instruction

D. Logical instruction

ANSWER: A

Mr. Ritesh S. Dayama

MCQ COMPUTER ORGANIZATION

27. Width of exponent field in case of IEEE 34. According to what address generated by

standard for single precision is program tends to be localized and can be

A. 11 bit predictable

B. 8 bit A. Locality of reference

C. 52 bit B. Spatial locality

D. 23 bit C. Temperal locality

ANSWER: B D. All of above

ANSWER: D

28. Design approach used in hardwired control is

A. State table method 35. Which unit issue control single to datapath

B. Delay element method A. Datapath unit

C. Sequence counter method B. Control unit

D. All C. ALU

ANSWER: D D. None of these

ANSWER: B

29. Instruction cache and data cache are splited in

case of

A. CISC architecture

B. RISC architecture

C. Both A and B

D. None

ANSWER: B

30. Function of I/O control instruction is

A. Moves data from one location to another

B. For performing arithmatic operation

C. For performaing logical operations

D. Move data from CPU to I/O devices

ANSWER: D

31. How many instructions are executed per

machine cycle in RISC

A. 1 B. 2

C. 3 D. 4

ANSWER: A

32. How many bits are there in product if n is

number of bits input in Booth's algo-

multiplication.

A. n B. 2n

C. 3n D. n*n

ANSWER: A

33. How many bits are there in single precision

format of floating point number?

A. 30

B. 64

C. 32

D. 33

ANSWER: C

Mr. Ritesh S. Dayama

You might also like

- Test Bank Ninth EditionDocument59 pagesTest Bank Ninth Editionhamed50% (2)

- Microstream Capnography Exercises Physio-Control Lifepak® 12 and Lifepak 15 Monitor/DefibrillatorsDocument2 pagesMicrostream Capnography Exercises Physio-Control Lifepak® 12 and Lifepak 15 Monitor/DefibrillatorsLexipol_Media_GroupNo ratings yet

- Management Information System Solved MCQs (Set-1)Document5 pagesManagement Information System Solved MCQs (Set-1)Saksham YadavNo ratings yet

- Ee8551-Microprocessors and MicrocontrollersDocument8 pagesEe8551-Microprocessors and MicrocontrollersImportantNo ratings yet

- DIP Unit 3 MCQDocument5 pagesDIP Unit 3 MCQsumit singhNo ratings yet

- Microprocessor & AlpDocument43 pagesMicroprocessor & AlpKunwar Gajendra Singh TanwarNo ratings yet

- Mpi MCQDocument83 pagesMpi MCQAKSHAY DagareNo ratings yet

- TRB Answer KeyDocument70 pagesTRB Answer KeyVskm Nagarajan Muthuragavan100% (1)

- 8086: Microprocessor: Multiple Choice Question & AnswersDocument34 pages8086: Microprocessor: Multiple Choice Question & AnswersJos BatlarNo ratings yet

- MCQ For Second YearDocument22 pagesMCQ For Second YearVaishNo ratings yet

- Computer Exit Exam quesitions with AnaswerDocument14 pagesComputer Exit Exam quesitions with Anaswershiferachala778100% (1)

- Theory of Computation (Chapter - Unit 4) Solved MCQs (Set-1)Document6 pagesTheory of Computation (Chapter - Unit 4) Solved MCQs (Set-1)YatiNo ratings yet

- B. To Reduce The Size of Data To Save SpaceDocument25 pagesB. To Reduce The Size of Data To Save SpaceAashi Neha100% (1)

- Question Bank - EC-208 - Programming ConceptsDocument20 pagesQuestion Bank - EC-208 - Programming ConceptsPiyush CharanNo ratings yet

- Memory Hierarchy and Cache Quiz AnswersDocument3 pagesMemory Hierarchy and Cache Quiz AnswersNeha SharmaNo ratings yet

- Computer 9th MCQS) PDFDocument4 pagesComputer 9th MCQS) PDFAbdul RehmanNo ratings yet

- CMCQDocument18 pagesCMCQYesudasNo ratings yet

- AaDocument15 pagesAaSofonias MenberuNo ratings yet

- MCQ of Computer Organization Architecture 3340705Document26 pagesMCQ of Computer Organization Architecture 334070530. Suraj IngaleNo ratings yet

- Computer Graphics MCQ - BDocument6 pagesComputer Graphics MCQ - BAmbika JaiswalNo ratings yet

- Computer Organization and ArchitectureDocument20 pagesComputer Organization and ArchitecturePoovarasanNo ratings yet

- DLF 2 Mark Question BanksDocument5 pagesDLF 2 Mark Question Banksmeenakshisankar2013100% (1)

- PC Repairing (MCQS)Document26 pagesPC Repairing (MCQS)Noman AsifNo ratings yet

- DAA - Questions BANKDocument8 pagesDAA - Questions BANKkillerpreet003No ratings yet

- Q&ADocument89 pagesQ&AAjay Tomar100% (1)

- CG MCQDocument38 pagesCG MCQsuraj rautNo ratings yet

- COA MCQ 1Document21 pagesCOA MCQ 1Nayan Ranjan Paul100% (1)

- Typical Questions & AnswersDocument82 pagesTypical Questions & AnswersSudip PaulNo ratings yet

- Web Technology MCQDocument9 pagesWeb Technology MCQmuruganv84No ratings yet

- Ca Q&aDocument129 pagesCa Q&aRavi TejaNo ratings yet

- Rev MidtermDocument17 pagesRev MidtermraqibappNo ratings yet

- Programming in C++ Msuniv QuestionDocument6 pagesProgramming in C++ Msuniv QuestionAngel PriyaNo ratings yet

- Awp MCQ 100Document16 pagesAwp MCQ 100SaurabhNo ratings yet

- DBMS Gate2010Document10 pagesDBMS Gate2010Devang Bagora100% (1)

- Design and Analysis of Algorithms Solved MCQs (Set-11)Document7 pagesDesign and Analysis of Algorithms Solved MCQs (Set-11)Aamir ShaheenNo ratings yet

- Programming Languages MCQsDocument7 pagesProgramming Languages MCQsAmmara HussainNo ratings yet

- Question Text: Fill in The Blanks: Write The Missing Word To Complete The SentenceDocument39 pagesQuestion Text: Fill in The Blanks: Write The Missing Word To Complete The Sentencemoncarla lagon100% (1)

- AP PGECET CS and IT (CS-2015) Question Paper & Answer Key. Download All Previous Years Computer Science & Information Technology Sample & Model Question Papers.Document16 pagesAP PGECET CS and IT (CS-2015) Question Paper & Answer Key. Download All Previous Years Computer Science & Information Technology Sample & Model Question Papers.pavani100% (2)

- Chapter 6: Output: Multiple ChoiceDocument30 pagesChapter 6: Output: Multiple ChoiceRonnel BrusasNo ratings yet

- AI MCQ QUESTION 100 MCQDocument13 pagesAI MCQ QUESTION 100 MCQdrphysics256No ratings yet

- RCS 087 - DATA COMPRESSION 300+ MCQsDocument50 pagesRCS 087 - DATA COMPRESSION 300+ MCQsNihal SharmaNo ratings yet

- Final Answer Key HSST Computer ScienceDocument19 pagesFinal Answer Key HSST Computer Scienceresmimr100% (1)

- 1Document16 pages1Velmurugan JeyavelNo ratings yet

- Design and Analysis of Algorithms Solved MCQs (Set-1) PDFDocument7 pagesDesign and Analysis of Algorithms Solved MCQs (Set-1) PDFkantipucappa 19No ratings yet

- Chapter 6 AJAXDocument9 pagesChapter 6 AJAXOz GNo ratings yet

- Module 1Document79 pagesModule 1Remya RaveendranNo ratings yet

- Database Systems Questions and AnswersDocument14 pagesDatabase Systems Questions and AnswersTongai Dune100% (1)

- DSA MCQ Unit 1 PDFDocument41 pagesDSA MCQ Unit 1 PDFSamruddhi PatilNo ratings yet

- Compiler Mcqs Last Updated Solved CompleteDocument57 pagesCompiler Mcqs Last Updated Solved Completesaeed khanNo ratings yet

- Unit 2 MCQDocument11 pagesUnit 2 MCQShubhangi GiraseNo ratings yet

- AI Final Exam For 6kilo.Document4 pagesAI Final Exam For 6kilo.Beki TubeNo ratings yet

- Human Computer Interaction (COMS4041, COMS7054) Class Test: University of The Witwatersrand, JohannesburgDocument2 pagesHuman Computer Interaction (COMS4041, COMS7054) Class Test: University of The Witwatersrand, JohannesburgNim DNo ratings yet

- Algorithm Question SetDocument26 pagesAlgorithm Question Setlokenders80175% (4)

- HCI TestDocument2 pagesHCI TestAura M M CelestinoNo ratings yet

- Coa Unit 4,5 MCQDocument26 pagesCoa Unit 4,5 MCQManish Singh RajputNo ratings yet

- MCQ On Chapters 5 & 6Document8 pagesMCQ On Chapters 5 & 6Renz Ronnie TarromaNo ratings yet

- Lower Sixth Science, 2 Sequence Test. Computer Science November 2014, Time 2hoursDocument2 pagesLower Sixth Science, 2 Sequence Test. Computer Science November 2014, Time 2hoursFerdinand NgumNo ratings yet

- Multiple Choice Questions For Computer OperatorDocument5 pagesMultiple Choice Questions For Computer OperatorRikesh DewanganNo ratings yet

- COA ExamDocument7 pagesCOA ExamsomsonengdaNo ratings yet

- McqDocument8 pagesMcqstavinadsouzaNo ratings yet

- Co 2020Document12 pagesCo 2020Sinley PatelNo ratings yet

- Bluestar Brand EMI Offer - Dec 24Document16 pagesBluestar Brand EMI Offer - Dec 24orock91No ratings yet

- TB-M0.005 - Mechanical - SchedulesDocument1 pageTB-M0.005 - Mechanical - Schedulesdns.ssaietNo ratings yet

- Adm-860c Manual - 041408Document70 pagesAdm-860c Manual - 041408Hansen Henry D'souza100% (1)

- Electrical Notes For VIVA VOCEDocument5 pagesElectrical Notes For VIVA VOCE8ke0472xre4lzzw72r8No ratings yet

- VSP Architecture Overview V2 2Document25 pagesVSP Architecture Overview V2 2Vignesh Babu100% (1)

- Nodemcu: An Open Source IOT PlatformDocument13 pagesNodemcu: An Open Source IOT PlatformmohitNo ratings yet

- Panasonic Kxtg1070 Service ManualDocument41 pagesPanasonic Kxtg1070 Service ManualGuillermo SeguraNo ratings yet

- 4100ES Fire Alarm System Operator's Manual (579-197)Document62 pages4100ES Fire Alarm System Operator's Manual (579-197)Mostafa AbdelhadiNo ratings yet

- BTS Commissioning: Prepared & Presented By: Thushara KarunarathnaDocument75 pagesBTS Commissioning: Prepared & Presented By: Thushara KarunarathnaErangaNo ratings yet

- Automatic Transfer Switch CatalogueDocument11 pagesAutomatic Transfer Switch CatalogueSuper Whipped0% (1)

- Mesotech MS1000 PDFDocument2 pagesMesotech MS1000 PDFArnoldo López MéndezNo ratings yet

- Manual WilsonDocument12 pagesManual WilsonRuben BongioanniNo ratings yet

- Analysis of Response Variables in Ecm of Aluminium Metal Matrix Composite (Al, Sic) Using Doe and Gra MethodDocument8 pagesAnalysis of Response Variables in Ecm of Aluminium Metal Matrix Composite (Al, Sic) Using Doe and Gra MethodSandeep KumarNo ratings yet

- Stereo Power Amplifier Amplificador: Operating Instructions Mode D'emploi Manual de InstruccionesDocument2 pagesStereo Power Amplifier Amplificador: Operating Instructions Mode D'emploi Manual de InstruccionesJuan Carlos LizarazoNo ratings yet

- Spare Parts For Control PainelsDocument9 pagesSpare Parts For Control PainelsMarcos CarvalhoNo ratings yet

- Nexon Ev BrochureDocument37 pagesNexon Ev BrochurefirefoxbrowseraNo ratings yet

- Presentation StruxureWare DCODocument30 pagesPresentation StruxureWare DCOGaniza Long0% (1)

- Performance Comparison Between Various Tuning Strategies: Ciancone, Cohen Coon & Ziegler-Nicholas Tuning MethodsDocument9 pagesPerformance Comparison Between Various Tuning Strategies: Ciancone, Cohen Coon & Ziegler-Nicholas Tuning MethodsDeriSuryadiNo ratings yet

- 4.2 The BAM Format: List of Reference Information (N N Ref)Document1 page4.2 The BAM Format: List of Reference Information (N N Ref)antidemosNo ratings yet

- BS en 1714-98 - Ultrasonic Examination of Weld JointDocument26 pagesBS en 1714-98 - Ultrasonic Examination of Weld Jointsortancil100% (4)

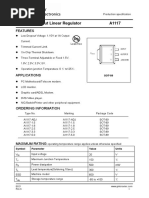

- 1A Low Dropout Linear Regulator A1117: FeaturesDocument5 pages1A Low Dropout Linear Regulator A1117: FeaturesStênio FirminoNo ratings yet

- Traffic Light ControllerDocument4 pagesTraffic Light ControllerpaijozzNo ratings yet

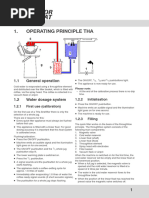

- Bravilor Bonamat Operating Principle THA (After 2009) GBDocument4 pagesBravilor Bonamat Operating Principle THA (After 2009) GBAntonNo ratings yet

- Grounding Tutorial Substation Ground System Design & Standard IEEE 80Document103 pagesGrounding Tutorial Substation Ground System Design & Standard IEEE 80DINESHNo ratings yet

- Exp - Meth - in - RF DesDocument501 pagesExp - Meth - in - RF DesMila IosifNo ratings yet

- CCNA 2 Exploration ERouting Final Exam Form3 V 4.0Document20 pagesCCNA 2 Exploration ERouting Final Exam Form3 V 4.0sEcZxNo ratings yet

- SyllabusDocument2 pagesSyllabusvamshiNo ratings yet

- Report LI - Nur SabihaDocument43 pagesReport LI - Nur SabihaafiqahNo ratings yet

- P3-16TD1 Output 12-24 VDCDocument6 pagesP3-16TD1 Output 12-24 VDCAlejandroNo ratings yet