DCMP-lab1 Handout

DCMP-lab1 Handout

Uploaded by

AKANSH AGRAWALCopyright:

Available Formats

DCMP-lab1 Handout

DCMP-lab1 Handout

Uploaded by

AKANSH AGRAWALOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

DCMP-lab1 Handout

DCMP-lab1 Handout

Uploaded by

AKANSH AGRAWALCopyright:

Available Formats

EE 381A: EE LABORATORIES (DIGITAL CIRCUITS AND MICROPROCESSORS)

2021-2022/II

EXPERIMENT 1: SYNCHRONOUS & RIPPLE COUNTERS

PART 1: SYNCHRONOUS COUNTERS

Design a divide-by-SIX synchronous counter using 74LS76 Dual J-K negative edge-triggered flip-

flops. The sequence of states of the counter should be (QCQBQA): 000, 100, 010, 011, 111, 101,

000 ….. . Ensure that if state 001 occurs the next state is 111 and if state 110 occurs then the next

state is 000. The ICs given to you are: 74LS76 – 2 nos., 7400 (Quad 2-i/p NAND) – 3 nos.

1.1 Lab Preparation

1. Design the above counter making use of appropriate transition tables and K-maps. Verify your

design using a suitable table.

2. Draw the complete circuit diagram (functional diagram with all the required pin numbers).

1.2 Experiment

1. Show your design to your tutor before you start.

2. Test the flip-flops of 74LS76 using either manual clock or the Function Generator and CRO.

3. Wire the circuit. Use manual clock (circuit of Fig. 1) and the LEDs (circuit of Fig. 2 with

value of R chosen such that LED current = 20 mA) to verify that your counter follows the

specified sequence. Set the unused states as well and ensure that the next states obtained are as

specified.

4. Use TTL clock from the FG as the clock instead of the manual clock. Observe and sketch the

QC, QB, and QA outputs with respect to the clock.

5. Increase the frequency of the TTL clock to several megahertz (say 5 MHz). Measure the

propagation delay of the flip-flop.

PART 2: RIPPLE COUNTERS

Design a divide-by-EIGHT asynchronous DOWN counter using 74LS74 Dual D-flip flops. Use no

other ICs.

2.1 Lab Preparation

1. Design the above counter.

2. Draw the complete circuit diagram (functional diagram with all the required pin numbers).

2.2 Experiment

1. Test the circuit using manual clock and verify that it is working as per design.

2. Use TTL clock from the FG instead of the manual clock. Observe and sketch the QC, QB, and

QA outputs with respect to the clock.

3. Using the FG measure the delay between the QC, QB, and QA outputs.

PART 3: PROGRAMMABLE SYNCHRONOUS COUNTER

Design (i) a divide-by-NINE and (ii) a divide-by-THIRTEEN synchronous UP counters using

74LS163 (Synchronous binary counter with synchronous Clear) and ONE 3-input NAND gate (7410)

in each case. Use no other ICs.

3.1 Lab Preparation and Experiment

1. Design the above counter and draw the complete circuit diagram.

2. Test the circuit using manual clock and verify that it is working as per design.

3. Use TTL clock from the FG instead of the manual clock. Observe and sketch the O0, O1, O2

and O3 outputs with respect to the clock.

PART4: DIVIDE-BY-256 SYNCHRONOUS COUNTER (Optional if time permits)

Design a divide-by-256 synchronous counter using two 74LS163 ICs. (Note: To do this experiment

you need to understand the roles of the CET, CEP inputs and the TC output of 74LS163).

+ 5V + 5V + 5V + 5V

Push R

NC

Button + 5V

Switch NO R

Fig. 1 Manual Clock Circuit Fig. 2 LED Probes

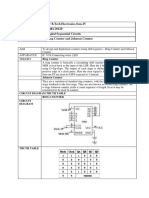

IC PIN Details

74163

4-bit

binary

counter

Pin Description and Mode Select Table for 74163

You might also like

- Digital StopwatchDocument13 pagesDigital StopwatchAtharva Inamdar100% (3)

- Experiment 7.docxDocument5 pagesExperiment 7.docxsriramrajasekar1396No ratings yet

- Pre-Lab 2 (2)Document3 pagesPre-Lab 2 (2)SILENT KILLER GAMINGNo ratings yet

- Digital LabDocument51 pagesDigital LabBala SubramanianNo ratings yet

- Laboratory Activity 8 Counter Sequential CircuitsDocument4 pagesLaboratory Activity 8 Counter Sequential CircuitsAdrianne MarianoNo ratings yet

- Asynchronous and Synchronous CounterDocument10 pagesAsynchronous and Synchronous CounterNurul Fatihah ArdanNo ratings yet

- Experiment 8 Basic Combinatorial CircuitsDocument4 pagesExperiment 8 Basic Combinatorial CircuitsPk KumarNo ratings yet

- DLD Exp05Document7 pagesDLD Exp05Dr-Eng Imad ShaheenNo ratings yet

- Ic Lab AllDocument45 pagesIc Lab AllRaghu KasulaNo ratings yet

- ECE 28 FDS CounterDocument8 pagesECE 28 FDS CounterJeara MuyongNo ratings yet

- Qjsnksjdbxnclamd'bdDocument2 pagesQjsnksjdbxnclamd'bdkdmmoh001No ratings yet

- Data Sheet: 74HC/HCT393Document7 pagesData Sheet: 74HC/HCT393MUHAMMAD SISWANTORONo ratings yet

- All-In-One PLC: KV Nano Application Guide Vol. 7Document12 pagesAll-In-One PLC: KV Nano Application Guide Vol. 7Phạm Thế HiệpNo ratings yet

- EE103 Exp9 TOSHIT - 2101CB59Document5 pagesEE103 Exp9 TOSHIT - 2101CB59Rahul PalNo ratings yet

- Experiment No. 2: Abstract-In This Experiment, The StudentsDocument6 pagesExperiment No. 2: Abstract-In This Experiment, The StudentsShania SarmientoNo ratings yet

- Digital Logic Design Lab Manual FinalDocument30 pagesDigital Logic Design Lab Manual Finalsenthil kumarNo ratings yet

- Exp 12) Prbs Generator and Shift RegisterDocument5 pagesExp 12) Prbs Generator and Shift RegisterMani BharathiNo ratings yet

- 18c Lab18 Divided by N Counters-335bDocument2 pages18c Lab18 Divided by N Counters-335bsaraj71205No ratings yet

- Laboratory Manual Course Code:Ece 201Document41 pagesLaboratory Manual Course Code:Ece 201Er Sacchu SrivastavaNo ratings yet

- EXP 10-11 MergedDocument20 pagesEXP 10-11 MergedNitesh KumarNo ratings yet

- Rotary EncoderDocument6 pagesRotary EncoderalesysNo ratings yet

- Rajalakshmi Engineering College THANDALAM - 602 105Document70 pagesRajalakshmi Engineering College THANDALAM - 602 105swathianandaraoNo ratings yet

- Rajalakshmi Engineering College THANDALAM - 602 105Document70 pagesRajalakshmi Engineering College THANDALAM - 602 105Vajith RaghmanNo ratings yet

- COE117L Expt 6 SabDocument1 pageCOE117L Expt 6 Sabcreatorpurpose12345No ratings yet

- 13 Counters and Oscillators: 13.1 Binary CounterDocument5 pages13 Counters and Oscillators: 13.1 Binary CountermhofuNo ratings yet

- De Lab ManualDocument20 pagesDe Lab ManualVishesh ShrivastavaNo ratings yet

- Ee 381A: Digital Circuits and Microprocessors 2021-2022/II Experiment 2 Prbs & Sequence Generators Using Shift RegistersDocument2 pagesEe 381A: Digital Circuits and Microprocessors 2021-2022/II Experiment 2 Prbs & Sequence Generators Using Shift RegistersAKANSH AGRAWALNo ratings yet

- Project - Group 8Document7 pagesProject - Group 8Việt BảoNo ratings yet

- Ece Ade Manual 500 CopiesDocument79 pagesEce Ade Manual 500 CopiesRajkumarNo ratings yet

- Acrel dtsd1352 ManualDocument28 pagesAcrel dtsd1352 ManualShare4U VBANo ratings yet

- Digital Electronics Circuits: Experiment: 9Document4 pagesDigital Electronics Circuits: Experiment: 9movabNo ratings yet

- Integrated Circuits Laboratory: SyllabusDocument70 pagesIntegrated Circuits Laboratory: Syllabusdeena10No ratings yet

- Experiment No-7 Design and Implementation of 4-Bit Ripple Counter and Mod-10 Counters Using Flip Flop and Gates ObjectDocument3 pagesExperiment No-7 Design and Implementation of 4-Bit Ripple Counter and Mod-10 Counters Using Flip Flop and Gates ObjectMohini Mohan BeheraNo ratings yet

- EXPT. No. 8 Generation of TTL Level SignalsDocument2 pagesEXPT. No. 8 Generation of TTL Level SignalsHritik KumarNo ratings yet

- ETU 07322 - Digital Electronic Lab ManualDocument33 pagesETU 07322 - Digital Electronic Lab ManualFrancis LubangoNo ratings yet

- Two Digit CounterDocument12 pagesTwo Digit Counter22je0766No ratings yet

- Ade Lab ManualDocument79 pagesAde Lab ManualVinod KannaNo ratings yet

- Expt 2Document2 pagesExpt 2Ankit KhandelwalNo ratings yet

- DLD Lab ManualDocument41 pagesDLD Lab ManualCreative Study by CZNo ratings yet

- Astable and Monostable Multivibrator Trainer NV6507Document10 pagesAstable and Monostable Multivibrator Trainer NV6507Himadri MandalNo ratings yet

- KNL 1253 Digital Electronics: CountersDocument44 pagesKNL 1253 Digital Electronics: CountersjuzsuicideNo ratings yet

- Meter MultiDocument28 pagesMeter Multibatzorig valyaNo ratings yet

- DLC LAB - 07 - Student - ManualDocument6 pagesDLC LAB - 07 - Student - Manualrk refatNo ratings yet

- Laboratory Manual Course Code:Ece 201Document41 pagesLaboratory Manual Course Code:Ece 201Atul SainiNo ratings yet

- MultivibratorDocument6 pagesMultivibratorrajivNo ratings yet

- Digital_Electronics_-_Unit_1_Activity_1.2.4_Sept_2024Document5 pagesDigital_Electronics_-_Unit_1_Activity_1.2.4_Sept_2024ace.x16.xdNo ratings yet

- Lab Report 1 EE32200 - Ronny VintimillaDocument16 pagesLab Report 1 EE32200 - Ronny VintimillaRonny VintimillaNo ratings yet

- Data SheetDocument7 pagesData SheetmegmanojsterNo ratings yet

- MP Lab Manual PDFDocument62 pagesMP Lab Manual PDFअंकित अनुरागNo ratings yet

- Ic Lab Planer 8-7-13Document55 pagesIc Lab Planer 8-7-13NaveenkNo ratings yet

- Ring and Johnson CounterDocument5 pagesRing and Johnson CounterHarry StylesNo ratings yet

- De Lab PDFDocument36 pagesDe Lab PDFNaveen Yallapu100% (1)

- BM8411Document142 pagesBM8411Gayathri M100% (1)

- Lecture3 Chapter6 - Counters With Unused StatesDocument17 pagesLecture3 Chapter6 - Counters With Unused StatesAhsan BilalNo ratings yet

- KNR 1063 Digital Electronics: CountersDocument33 pagesKNR 1063 Digital Electronics: CountersCyprian Mikael CorgedoNo ratings yet

- FLIP - FLOPS Lab-Sheet-Digital-ElectronicsDocument5 pagesFLIP - FLOPS Lab-Sheet-Digital-Electronicswakala manaseNo ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Design of Electrical Circuits using Engineering Software ToolsFrom EverandDesign of Electrical Circuits using Engineering Software ToolsNo ratings yet

- Analog Dialogue, Volume 48, Number 1: Analog Dialogue, #13From EverandAnalog Dialogue, Volume 48, Number 1: Analog Dialogue, #13Rating: 4 out of 5 stars4/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Telex PH-81 PH-85 Technical Data SheetDocument2 pagesTelex PH-81 PH-85 Technical Data SheetGerardo L. SilvaNo ratings yet

- TransistorsDocument21 pagesTransistorsAhmad AzriNo ratings yet

- High Efficiency DC-DC Boost Converter Design For LED DrivesDocument10 pagesHigh Efficiency DC-DC Boost Converter Design For LED DriveskowsalyaNo ratings yet

- TRx3218 PDFDocument2 pagesTRx3218 PDFJonatan Cari OjedaNo ratings yet

- Electronics DC Plugs & JacksDocument2 pagesElectronics DC Plugs & JacksWaseem ArshadNo ratings yet

- ESDM Courses Syllabi - 150316 PDFDocument431 pagesESDM Courses Syllabi - 150316 PDFBuddhadebSiNo ratings yet

- BEEE Assignment 1 (2024-2025)Document2 pagesBEEE Assignment 1 (2024-2025)aryankondekar15No ratings yet

- Introduction, Methology and Front Page Lab Report Sem2Document3 pagesIntroduction, Methology and Front Page Lab Report Sem2ammar tajuddinNo ratings yet

- To Identify A Diode, An LED, A Transistor, An IC, A Resistor & A Capacitor From A Mixed Collection of Such ItemsDocument3 pagesTo Identify A Diode, An LED, A Transistor, An IC, A Resistor & A Capacitor From A Mixed Collection of Such ItemsHarsh Patidar75% (4)

- North-1 Carkit For 3G+2G+LTE+HuaweiDocument14 pagesNorth-1 Carkit For 3G+2G+LTE+HuaweiAijaz khanNo ratings yet

- Manual CNT Asl51Document4 pagesManual CNT Asl51Jhoompieer VFNo ratings yet

- Code Cause Operation Reset ProcedureDocument3 pagesCode Cause Operation Reset ProcedureAdi M100% (1)

- Total Seats Vacant in Govt./GIA Institutes & IITRAM BE After Round - 03Document3 pagesTotal Seats Vacant in Govt./GIA Institutes & IITRAM BE After Round - 03Darshak ParikhNo ratings yet

- SPWMDocument16 pagesSPWMSatyanarayana GurramNo ratings yet

- Sensorless Field Oriented Control (FOC) of An AC Inductive MotorDocument34 pagesSensorless Field Oriented Control (FOC) of An AC Inductive MotorpaaraibNo ratings yet

- Generation (1G, 2G, 3G, 4G, 5G) Throughput /: Users On A Single Channel Via Multiplexing - DuringDocument4 pagesGeneration (1G, 2G, 3G, 4G, 5G) Throughput /: Users On A Single Channel Via Multiplexing - DuringArindam GangopadhyayNo ratings yet

- Good For Gaming and PisonetDocument3 pagesGood For Gaming and PisonetRobertson Prado De SolaNo ratings yet

- Nokia 202 RM-834 Schematics v1.0Document7 pagesNokia 202 RM-834 Schematics v1.0ssssNo ratings yet

- Inm MTL4000Document44 pagesInm MTL4000Nestor CalaNo ratings yet

- IR Drop Reduction Via Via AdditionDocument4 pagesIR Drop Reduction Via Via AdditionSeema JainNo ratings yet

- Crash Dump Analysis: Jakub Jermář Martin DěckýDocument47 pagesCrash Dump Analysis: Jakub Jermář Martin Děckýachilles7No ratings yet

- Risk AnalysisDocument8 pagesRisk Analysiscarlitos8022No ratings yet

- 1MRK505265-BEN - en Product Guide Busbar Protection REB650 IECDocument61 pages1MRK505265-BEN - en Product Guide Busbar Protection REB650 IECRobert RocafuerteNo ratings yet

- POWER SUPPLY - Extra High Voltage - 6000V.DC.: Instruction SheetDocument2 pagesPOWER SUPPLY - Extra High Voltage - 6000V.DC.: Instruction SheetlamchunyienNo ratings yet

- Arduino The Ultimate Beginner's Guide by Lee MaxwellDocument48 pagesArduino The Ultimate Beginner's Guide by Lee MaxwellJacob MelladoNo ratings yet

- Gateway I IFC User ManualDocument30 pagesGateway I IFC User ManualSuraj KumarNo ratings yet

- Video Controller VX4 Series User Manual-V1.0.0Document30 pagesVideo Controller VX4 Series User Manual-V1.0.0anyuserNo ratings yet

- Data FormatDocument1 pageData Formatshezi23No ratings yet

- Incisive Verification Ip For The Arm Amba Protocol Family: Capabilities Key FeaturesDocument4 pagesIncisive Verification Ip For The Arm Amba Protocol Family: Capabilities Key FeaturesGiri DharNo ratings yet

- Toshiba Photocouplers and Photo RelaysDocument77 pagesToshiba Photocouplers and Photo RelaysEhab Anwar ElnagdyNo ratings yet