Ec3352 - Digital Systems Design Set I - Iat2

Uploaded by

venki08Copyright:

Available Formats

Ec3352 - Digital Systems Design Set I - Iat2

Uploaded by

venki08Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Ec3352 - Digital Systems Design Set I - Iat2

Uploaded by

venki08Copyright:

Available Formats

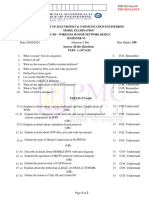

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

INTERNAL ASSESMENT TEST –II (SET I)

SUBJECT CODE/NAME : EC3352 DIGITAL SYSTEMS DESIGN DATE :

BRANCH / SEMESTER : II ECE / III TIME :

ACADEMIC YEAR : 2023-24 MARK : 50

CO2: Design various combinational digital circuits using logic gates.

CO3: Analyse and design asynchronous sequential circuits.

BLOOM'S TAXONOMY

Remembering Applying Evaluating

Understanding Analyzing Creating

PART A (5 x 2 = 10 marks)

CO2 R 1. Define Combinational Circuits? (2)

CO2 U 2. What is a Full Adder? (2)

CO2 R 3. List out the various applications of Multiplexer? (2)

CO3 U 4. Differentiate Flipflop & Latches (2)

CO3 C 5. Write down the characteristic’s equation for JK & T Flipflop. (2)

PART B (2 x 13= 26 marks)

CO2 a) What is Multiplexer? With a neat Logic diagram explain in detail function of 8:1

Multiplexer? (OR)

U

6. (13)

CO3 R b) Define Register & explain the working principle of SISO?

CO2 U a) Explain in detail about the function of Parity Generator / Parity Checker. (OR)

7. (13)

CO2 U b) What is Encoder? Explain the function of Priority Encoder.

PART C (1x 14 = 14 marks)

CO2 U a) With a neat diagram explain in detail about the working principle of a 4-bit

look ahead carry adder. (OR)

(14)

CO2 U b) Explain in detail about the working principle of Seven Segment Display

8. Decoder.

Prepared by Verified by Approved by

You might also like

- Ec3352 - Digital Systems Design Set Ii - Iat2No ratings yetEc3352 - Digital Systems Design Set Ii - Iat21 page

- Part A: (Government Aided Autonomous Institution)No ratings yetPart A: (Government Aided Autonomous Institution)2 pages

- Solution_COA_KCS-302__Special Theory ExaminationNo ratings yetSolution_COA_KCS-302__Special Theory Examination20 pages

- VTU exam Question Paper with Solution of BCS302 Digital Design and Computer Organization April-2024-Dr.Ciyamala Kushbu SNo ratings yetVTU exam Question Paper with Solution of BCS302 Digital Design and Computer Organization April-2024-Dr.Ciyamala Kushbu S4 pages

- Copy of 20pespc103 Design of Embedded SystemsNo ratings yetCopy of 20pespc103 Design of Embedded Systems2 pages

- Salem-Campus, Attur Main Road, Minnampalli, Salem - 636 106.: Mahendra College of EngineeringNo ratings yetSalem-Campus, Attur Main Road, Minnampalli, Salem - 636 106.: Mahendra College of Engineering2 pages

- Bethlahem Institute of Engineering: KARUNGAL - 629 157No ratings yetBethlahem Institute of Engineering: KARUNGAL - 629 1574 pages

- Salem-Campus, Attur Main Road, Minnampalli, Salem - 636 106.: Mahendra College of EngineeringNo ratings yetSalem-Campus, Attur Main Road, Minnampalli, Salem - 636 106.: Mahendra College of Engineering2 pages

- Dhanalakshmi Srinivasan: College of EngineeringNo ratings yetDhanalakshmi Srinivasan: College of Engineering3 pages

- Automobile Engineering Internal Exam Question PaperNo ratings yetAutomobile Engineering Internal Exam Question Paper10 pages

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNo ratings yet

- Class Wise Timetable ODD SEM 24-25 ECE II YEARNo ratings yetClass Wise Timetable ODD SEM 24-25 ECE II YEAR1 page

- Role of Artificial Intelligence in The Internet of Things (IoT) CNo ratings yetRole of Artificial Intelligence in The Internet of Things (IoT) C13 pages

- Solutions To Real Analysis 2nd Edition, G.B.Folland Chapter 1. Measures (Part 2)No ratings yetSolutions To Real Analysis 2nd Edition, G.B.Folland Chapter 1. Measures (Part 2)6 pages

- Shaarira Sthaana: Dr. M. Gautham Asst. Professor. Samhita & Siddhanta. Raja Rajeshwari Ayurvedic College, HumnabadNo ratings yetShaarira Sthaana: Dr. M. Gautham Asst. Professor. Samhita & Siddhanta. Raja Rajeshwari Ayurvedic College, Humnabad55 pages

- List of 7400 Series Integrated CircuitsNo ratings yetList of 7400 Series Integrated Circuits41 pages

- Couchsurfing - A Different Kind of Travel Experience: 22.01.2021 NameNo ratings yetCouchsurfing - A Different Kind of Travel Experience: 22.01.2021 Name6 pages

- Business Writing: at The End of This Module, You Should Be Able ToNo ratings yetBusiness Writing: at The End of This Module, You Should Be Able To6 pages

- Ancient Macedonian Language According To Modern Sources100% (1)Ancient Macedonian Language According To Modern Sources8 pages

- AfsaruddinonBauerBSOASGender Hierarchy in The QuranNo ratings yetAfsaruddinonBauerBSOASGender Hierarchy in The Quran3 pages

- God Has A Plan For Your Life - Your New Life - Morris CerulloNo ratings yetGod Has A Plan For Your Life - Your New Life - Morris Cerullo50 pages

- Analog/Mixed Signal IC Design Senior Engineer EngineerNo ratings yetAnalog/Mixed Signal IC Design Senior Engineer Engineer4 pages