EM2710 Datasheet

EM2710 Datasheet

Uploaded by

gm799763Copyright:

Available Formats

EM2710 Datasheet

EM2710 Datasheet

Uploaded by

gm799763Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

EM2710 Datasheet

EM2710 Datasheet

Uploaded by

gm799763Copyright:

Available Formats

eMPIA Technology

EM2710 USB PC CAM Device

Hardware Specification

EMPIA Technology Proprietary and Confidential

2/01/2004

EM2710

ADVANCED INFORMATION

DISCLAIMER

EMPIA Technology reserves the right to make changes in the device data identified in this publication without further notice. EMPIA Technology advises its customers to obtain the latest version of all device data to verify that any information being relied upon by the customer is current and accurate. EMPIA Technology does not assume any liability arising out of or associated with the application or use of any product or integrated circuit or component described herein. EMPIA Technology does not convey any license under its patent rights or the patent rights of others described herein. In the absence of a written or prior stated agreement to the contrary, the terms and conditions stated on the back of the EMPIA Technology order acknowledgment obtain. EMPIA Technology makes no warranty of any kind with regard to this material, including, but not limited to the implied warranties of merchantability and fitness for a particular purpose. EMPIA Technology products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any nuclear facility application, or for any other application in which the failure of the EMPIA Technology product(s) could create a situation where personal injury or death may occur. EMPIA Technology will not knowingly sell its products for use in such applications, and the buyer shall indemnify and hold harm-less EMPIA Technology and its officers, employees, subsidiaries, affiliates, representatives, and distributors against all claims, costs, damages, expenses, tort, and attorney fees arising out of directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that EMPIA Technology was negligent regarding the design or manufacture of the part.

EMPIA Technology Proprietary and Confidential

2/1/2004

EM2710

ADVANCED INFORMATION

Features

No external memory required Flexible Video Input Port

8-bit video input port

Programmable Video Timing Generator

Generate clock, H-sync and V-sync for CMOS sensor

Bayer RGB Color Processor

Black clamping Gamma correction Bayer pattern filtering Gain and offset adjustment in RGB space Support for auto exposure and white balance Defect pixel compensation

Compressing Engine

Proprietary, high-quality compression Programmable compression rate

Audio Interface

Support AC97 CODEC Software direct access to AC97 CODEC registers Support audio sample rates of 48K, 44.1K, 32K, 22.05K, and 8K.

USB Port

Integrated USB 2.0 PHY with High-Speed and Full-Speed Transceivers Second generation USB 2.0 PHY with reduced power USB 2.0 and 1.1 compliant Support Iso-chronous audio pipe up to 0.2 MB/sec Support Iso-chronous video pipe up to 24 MB/sec Support Bulk video pipe

EEPROM Interface

Support 128-byte or 256-byte 2-wire serial EEPROM Use EEPROM to store chip configurations and USB descriptors Customized Vendor ID and Product ID Customized Vendor String, Product String, and Serial Number String Software may use EEPROM to store board configurations Software may use EEPROM to store defect pixel coordinates

Miscellaneous

2-wire serial bus to program front-end video/audio devices

EMPIA Technology Proprietary and Confidential

2/1/2004

EM2710

ADVANCED INFORMATION

Power-down control to front-end video/audio devices 8 General-Purposed I/O ports Snap shot button input LED control output 0.25 micron, 2.5V Core, 3.3V I/O CMOS process 64-pin LQFP package

EMPIA Technology Proprietary and Confidential

2/1/2004

EM2710

ADVANCED INFORMATION

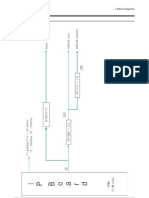

Functional Block Diagram

USB

EM2710

USB 2.0 PHY

Serial Interface

Video Source

SIE

Video Interface

Video Pipeline Stream Buffer

Audio Source

Audio Interface

EMPIA Technology Proprietary and Confidential

2/1/2004

EM2710

ADVANCED INFORMATION

General Description

EM2710 USB Video Capture Device (UVCD) is a highly integrated VLSI that provides a cost-effective solution for video capture applications on USB 2.0. Typical applications of this device are: CMOS PC-Camera As illustrated in the functional block diagram, an USB video subsystem consists of the UVCD, a video source, and optionally an audio source. The audio source can be an AC97 codec. The USB host configures (programs) the video/audio source via the 2-wire serial bus or the AC97-link. Source video stream is transferred to the UVCD via the 8-bit video bus. Source audio stream is transferred to the UVCD via the AC97-link. As shown in the functional block diagram, the UVCD consists of 7 main blocks. Video Interface Video Pipeline Audio Interface Stream Buffer Serial Interface Engine USB 2.0 PHY 2-Wire Serial Interface

Video Interface

The Video Interface Block receives video data from external video source. Video clock (VCLK) and reference signals (VREF, HREF) from the video source are used to strobe incoming video data. CCIR-656 with embedded FID, VREF and HREF is also supported. From the incoming video, a rectangular video sub-block is selected for feeding the next block, Video Pipeline. The Video Interface Block also includes a video timing generator that generates HREF and VREF for slavemode CMOS sensor.

Video Pipeline

The Video Pipeline Block performs the following operations. Black Clamping Gamma Correction RGB Gain and Offset Defect Pixel Compensation Up-Sampling 8-bit Bayer to 24-bit RGB, Color Space Conversion to YUV, Pixel Accumulation for AE and AWB Down Scaling Sharpness Enhancement Contrast, Brightness, and Saturation Adjustments UV Offset Adjustments Output Formatting Image Compression

EMPIA Technology Proprietary and Confidential

2/1/2004

EM2710

ADVANCED INFORMATION

After the above operations, the compressed video is stored into the Stream Buffer.

Audio Interface

The Audio Interface Block contains an AC97 controller. Enabled by configuration settings in EEPROM or CFG3. The AC97 controller interfaces with an external AC97 codec via 4-wire AC97-link. Supported audio sample rates are 48K, 44.1K, 32K, 22.05K, and 8K. The Audio Interface Block converts the serial audio input to PCM16 format and stores into the Stream Buffer.

Stream Buffer

The Stream Buffer stores the final audio and video data and delivers the data to the SIE upon request. The Stream Buffer is designed to sustain 24 MB/sec iso-chronous video transfer and 0.2 MB/sec iso-chronous audio transfer.

Serial Interface Engine

The Serial Interface Engine can be divided into 2 sub-blocks: the SIE Controller on the front end and the Endpoint Logic on the back end. The SIE Controller manages USB packets and transactions. The Endpoint Logic implements endpoint specific logic required for video capture application. The SIE communicates with the USB 2.0 PHY via UTMI bus. The UVCD complies with USB power management standard. When the USB bus stays idle for 3 mini seconds, the chip enters suspend mode and shuts down all internal clocks. The chip also sends out a power-down signal to external devices.

USB 2.0 PHY

The USB 2.0 PHY includes 12-MHz Full-Speed transceivers, 480-MHz High-Speed transceivers, a PLL, and an UTMI controller. The transceivers are compliant to the USB 2.0 electrical specification. The PLL supplies clocks to the entire chip. The UTMI controller communicates with the SIE. The PHY has been optimized for low power. Furthermore, the PHY can be suspended by the SIE to conserve power.

Serial Port and General I/O Port

The UVCD uses a two-wire serial bus to communicate with CMOS sensor or NTSC decoder. The serial port consists of SCL (clock) and SDA (data). Both are open-collector bi-directional ports. External pull-up resistors are required on both lines. There are 8 general I/O ports. All general I/O ports are open-collector bi-directional pins. If a port is intended for output, it must be tied to external pull-up resistors.

EMPIA Technology Proprietary and Confidential

2/1/2004

EM2710

ADVANCED INFORMATION

Pin Assignments

GND WSEL TESTMODE EXTPHY VCC3 CLKINT UCLKI VCC2 GND XSCI XSCO VCC3 AGND RREF DM DP

49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64

48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33

PW_DOWN LED SNAP RN FID PIO7 VCC2 PIO6 GND PIO5 GND PIO4 SDO SYNC BCLK GND

eMPIA

EM2710

32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17

VCC3 SDI PIO3 PIO2 PIO1 PIO0 GND SDA SCL VREF HREF XCLK VCLK VID7 VCC3 VID6

EMPIA Technology Proprietary and Confidential

AGND RPU DMRS DPRS AVCC3 AGND AVCC3 GND VID0 VCC2 VID1 VID2 VID3 GND VID4 VID5

01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16

2/1/2004

EM2710

ADVANCED INFORMATION

Pin Descriptions

Video Interface

Symbol XCLK VCLK VREF HREF FID VID7 VID6 VID5 VID4 VID3 VID2 VID1 VID0 Pin No. 21 20 23 22 44 19 17 16 15 13 12 11 9 Type O I B B I I I I I I I I I Description Video synchronous clock output Video reference clock from video source Vertical reference (sync) signal from video source in input mode. Video timing generator vertical reference output in output mode. Horizontal reference (sync) signal from video source in input mode. Video timing generator horizontal reference output in output mode. Field ID from video source Video input data, bit 7 Video input data, bit 6 Video input data, bit 5 Video input data, bit 4 Video input data, bit 3 Video input data, bit 2 Video input data, bit 1 Video input data, bit 0

Audio Interface

Symbol BCLK SDI SYNC SDO WSEL Pin No. 34 31 35 36 50 Type I I O O I Description AC97 bit clock AC97 serial data input AC97 48 KHz fixed rate sample sync AC97 serial data output Reserve

USB Interface

Symbol DP DM DPRS DMRS RREF RPU XSCI XSCO Pin No. 64 63 4 3 62 2 58 59 Type B B B B

Analog Analog Analog Analog

Description USB High-Speed differential data positive USB High-Speed differential data negative USB Full-Speed differential data positive, connected to external serial resistor (39 Ohm, 1%). USB Full-Speed differential data negative, connected to external serial resistor (39 Ohm, 1%). Connect external reference resistor (12.1 Kohm, 1%) to Analog Ground Connect external resistor (1.5 Kohm, 1%) to 3.3V Analog Power Crystal oscillator input 12 MHz Crystal oscillator output 12 MHz

EMPIA Technology Proprietary and Confidential

2/1/2004

EM2710

ADVANCED INFORMATION

Serial Bus and Programmable I/O

Symbol SCL SDA PIO7 PIO6 PIO5 PIO4 PIO3 PIO2 PIO1 PIO0 Pin No. 24 25 43 41 39 37 30 29 28 27 Typ B B B B B B B B B B Description Serial bus clock, open-drain, require external pull-up resistor. Serial data, open-drain, require external pull-up resistor. General I/O port 0, require external pull-up resistor in output mode. General I/O port 1, require external pull-up resistor in output mode. General I/O port 2, require external pull-up resistor in output mode. General I/O port 3, require external pull-up resistor in output mode. General I/O port 4, require external pull-up resistor in output mode. General I/O port 5, require external pull-up resistor in output mode. General I/O port 6, require external pull-up resistor in output mode. General I/O port 7, require external pull-up resistor in output mode.

Miscellaneous

Symbol RN SNAP LED PW_DOW TESTMO EXTPHY CLKINT UCLKI Pin No. 45 46 47 48 51 52 54 55 Typ I I O O I I I I Description Chip reset input. Active low. Connect to power-up RC circuit. Connect to snapshot button Connect to LED Power down external devices. Put the chip in test mode. Normally tie to GND Select and use external PHY. Normally tie to GND Select and use internal PLL. Normally tie to 3.3V VCC Chip clock input when CLKINT=0. Normally tie to GND

Power and Ground

Symbol AVCC3 AGND VCC3 VCC2 GND Pin No. 5,7 1, 6, 61 18, 32, 53, 60 10, 42, 56 8, 14,26,33 38,40,49,57 Type

Power Ground Power

Description 3.3V Analog Power Analog Ground 3.3V Digital Power 2.5V Digital Power Digital Ground

Power Ground

EMPIA Technology Proprietary and Confidential

10

2/1/2004

EM2710

ADVANCED INFORMATION

EEPROM Data Structure

EEPROM contains hardware configuration information. After reset by RN, the UVCD reads the EEPROM and uses the information to configure the chip. The first four bytes of the EEPROM are Key to the EEPROM. If the EEPROM is absent or the Key is invalid, the UVCD is configured with a set of default values.

Addr. 00H 01H 02H 03H 04H 05H 06H 07H 08H Data Definition Key Byte 0 = 1AH Key Byte 1 = EBH Key Byte 2 = 67H Key Byte 3 = 95H USB Vendor ID Low Byte USB Vendor ID High Byte USB Product ID Low Byte USB Product ID High Byte Chip Configuration Low Byte D[7:6] Reserved. Set to 0. D[5:4] Audio Configuration 00 No audio on board. 01 AC97 audio on board with 5 sample rates: 48K, 44.1K, 32K, 22.05K, and 8K. 10 Reserved. 11 Reserved. D[3] USB Remote Wakeup Capable when set to 1 D[2] USB Self Power Capable when set to 1. If the chip is configured to be Self Power Capable, PIO7 becomes self power status input. D[1:0] USB Max Power Select 00 USB Max Power 500 mA 01 USB Max Power 400 mA 10 USB Max Power 300 mA 11 USB Max Power 200 mA Chip Configuration High Byte Reserved. Set to 0. Board Configuration Low Byte To be defined by Software Architect Board Configuration High Byte To be defined by Software Architect String 1 Descriptor Pointer Starting address of String 1 Descriptor in the EEPROM String 1 Descriptor Length Number of bytes of String 1 Descriptor in the EEPROM String 2 Descriptor Pointer Starting address of String 2 Descriptor in the EEPROM String 2 Descriptor Length Number of bytes of String 2 Descriptor in the EEPROM String 3 Descriptor Pointer Starting address of String 3 Descriptor in the EEPROM String 3 Descriptor Length Number of bytes of String 3 Descriptor in the EEPROM String Index Table D[7:6] Reserved. Set to 0. D[5:4] Serial Number String Descriptor Index D[3:2] Product String Descriptor Index D[1:0] Vendor String Descriptor Index Default 1AH EBH * * **

09H 0AH 0BH 0CH 0DH 0EH 0FH 10H 11H 12H

00H 00H 00H 00H 00H 00H 00H 00H 00H 00H

EMPIA Technology Proprietary and Confidential

11

2/1/2004

EM2710

ADVANCED INFORMATION

Note:

* Default Product ID is listed below: Chip Type EM2710 Product ID (w.o. audio) 2710H Product ID (w. audio) 2711H

**

Default Chip Configuration Low Byte = 00H if PIO7 is pulled down with a resistor. Default Chip Configuration Low Byte = 10H if PIO7 is pulled up with a resistor.

EMPIA Technology Proprietary and Confidential

12

2/1/2004

EM2710

ADVANCED INFORMATION

Electrical Specifications

Absolute Maximum Ratings

Parameter

Power Supply Voltage Voltage on any input Operating Temperature (Ambient) Storage Temperature

Min

-0.3 -0.3 0 -40

Max

VCC+0.3 5.5 70 150

Unit

V V

o o

C C

Note: 1. Stress beyond those listed may cause permanent damage to the device. 2. Input pins are 5V tolerant.

DC Characteristics

Symbol Parameter

VCC2 VCC3 VCCA VIH VIL VOH VOL ICC ICCS CIN COUT Core Supply Voltage I/O Supply Voltage Analog Supply Voltage Input High Voltage Input Low Voltage Output High Voltage Output Low Voltage Operating Supply Current Suspend Supply Current Input Capacitance Output Capacitance 3.5 3.5 Vcc3 = 3.3V Vcc3 = 3.3V 2.4 0.4 120 250

Conditions

Min

2.25 3.0 3.0 2.0

Typ

2.5 3.3 3.3

Max

2.75 3.6 3.6

Unit

V V V V

0.8

V V V mA A pF pF

AC Characteristics

Symbol Parameter

fXTAL Crystal Frequency at XSCI, XSCO

Min

Typ

12

Max

Unit

MHz

EMPIA Technology Proprietary and Confidential

13

2/1/2004

EM2710

ADVANCED INFORMATION

Serial Bus Timing

Conditions: 100 KHz SCL; 4.7 Kohm pull up; 100 pF load;

Symbol Parameter

fSCL tSCL_LOW tSCL_HIGH tOSC tOSD tSDA_OD tSDA_SU tSDA_HD SCL Frequency SCL Low Pulse Width SCL High Pulse Width SDA to SCL Output Delay at START and STOP SCL to SDA Output Delay at START and STOP SDA Output Delay SDA Input Setup Time SDA Input Hold Time

Min

4.7 4.0 4.0 4.0 4.0 0 100

Typ

100

Max

Unit

KHz s s s s s ns ns

7.0 7.0 7.0

tSCL_LOW

tSCL_HIGH

SCL

tSDA_HD tSDA_SU

SDA in

tOSC

tSDA_OD

tOSD

SDA out

START STOP

WRITE

START

STOP

Serial Write Cycle

Device Address

One or More Register Addr

One or More Write Data

SDA

LSB ACK ACK ACK MSB START

START

WRITE

READ

STOP

Serial Read Cycle

Device Address

One or More Register Addr

Device Address

One or More Read Data

SDA

MSB MSB LSB ACK ACK LSB ACK ACK or NACK NACK the last read data and ACK all others

EMPIA Technology Proprietary and Confidential

14

2/1/2004

EM2710

ADVANCED INFORMATION

Video Interface Timing

Conditions: 50 pF load

Symbol Parameter

fVCLK tVC_LOW tVC_HIGH tV_OD tV_SU tV_HD VCLK Frequency VCLK Low Pulse Width VCLK High Pulse Width Video Output Delay Video Input Setup Time Video Input Hold Time

Min

15 15 0 10 10

Typ

Max

29

Unit

MHz ns ns

10

ns ns ns

tVC_LOW

tVC_HIGH

VCLK

tV_SU tV_HD

VID[7:0], FID VREF in HREF in

tV_OD

VREF out HREF out

EMPIA Technology Proprietary and Confidential

15

2/1/2004

EM2710

ADVANCED INFORMATION

AC97-Link Timing

Conditions: 50 pF load

Symbol Parameter

fBCLK fSYNC tBC_LOW tBC_HIGH tA_OD tA_SU tA_HD BCLK Frequency SYNC Frequency BCLK Low Pulse Width BCLK High Pulse Width AC97 Data Output Delay AC97 Data Input Setup Time AC97 Data Input Hold Time

Min

Typ

12.288 48

Max

Unit

MHz KHz

36 36 0 10 10

45 45 15

ns ns ns ns ns

tBC_LOW

tBC_HIGH

BCLK

tA_SU tA_HD

SDI

tA_OD

SYNC, SDO

EMPIA Technology Proprietary and Confidential

16

2/1/2004

EM2710

ADVANCED INFORMATION

Packaging Information

64-pin LQFP Mechanical Drawing

EMPIA Technology Proprietary and Confidential

17

2/1/2004

You might also like

- PLC Programming from Novice to Professional: Learn PLC Programming with Training VideosFrom EverandPLC Programming from Novice to Professional: Learn PLC Programming with Training VideosRating: 5 out of 5 stars5/5 (1)

- Em 2820Document18 pagesEm 2820fusse722No ratings yet

- Sony Hcd-Shake33 Hcd-Shake77 Ver1.0 SMDocument120 pagesSony Hcd-Shake33 Hcd-Shake77 Ver1.0 SMElectronica Leon Espinoza100% (3)

- Manual TimexDocument50 pagesManual Timexgm799763No ratings yet

- M871G Motherboard Manual ECS / PCChips 871G (1.5) - EngDocument46 pagesM871G Motherboard Manual ECS / PCChips 871G (1.5) - Enggm79976380% (5)

- Av36d303 SchematicDocument30 pagesAv36d303 SchematicLuis MorenoNo ratings yet

- EMPIA DatasheetDocument17 pagesEMPIA Datasheetgm799763No ratings yet

- STV0672 Datasheet PDFDocument2 pagesSTV0672 Datasheet PDFRicky CoxNo ratings yet

- EM2770 - 2775 Basic Family Description SheetDocument2 pagesEM2770 - 2775 Basic Family Description SheetBluff FlersNo ratings yet

- SAA7131E: 1. General DescriptionDocument66 pagesSAA7131E: 1. General DescriptionsaleanddekiNo ratings yet

- AS2204 DatasheetDocument2 pagesAS2204 DatasheetferchllNo ratings yet

- Voice Recording ISD1790 PR17B DDDocument9 pagesVoice Recording ISD1790 PR17B DDKesalan TerasaNo ratings yet

- DVD 4682Document6 pagesDVD 4682jgrisi065757No ratings yet

- Confidential For Digikits Technologies Internal Use Only: HDMI 1.4 3-In 1-Out Repeater/Switch/MCU Combo EP92A2EDocument21 pagesConfidential For Digikits Technologies Internal Use Only: HDMI 1.4 3-In 1-Out Repeater/Switch/MCU Combo EP92A2ESakthivel SNo ratings yet

- CM109 USB I/O Controller DataSheetDocument36 pagesCM109 USB I/O Controller DataSheetkurionNo ratings yet

- Acorn Electron Service ManualDocument54 pagesAcorn Electron Service ManualJohn Shalroth CheseldineNo ratings yet

- System Integration Guide 2014Document52 pagesSystem Integration Guide 2014catalin_chirilovNo ratings yet

- iWRAP A2DP Application NoteDocument20 pagesiWRAP A2DP Application Notergraczyk1No ratings yet

- Wireless Audio Link ICDocument4 pagesWireless Audio Link ICmotngaymoibatdau1986No ratings yet

- Service Manual M HCP HCP HCP HCP Lta-22n686hcpDocument31 pagesService Manual M HCP HCP HCP HCP Lta-22n686hcpCristina NistorNo ratings yet

- CPN103 Manual V1.1Document31 pagesCPN103 Manual V1.1alfee_ayajidNo ratings yet

- Dvtel Encoder AbbDocument2 pagesDvtel Encoder AbbGerardo AlcalaNo ratings yet

- Harmonic DS ViBE CP6000Document3 pagesHarmonic DS ViBE CP6000Ghufranaka Aldrien NanangNo ratings yet

- Sony - EX-2K Training ManualDocument27 pagesSony - EX-2K Training Manualmazterryble100% (1)

- Datasheet: C P V 5 3 7 5 Compactpci Host Slot Processor BoardDocument5 pagesDatasheet: C P V 5 3 7 5 Compactpci Host Slot Processor BoardprimaryrateNo ratings yet

- DVD s100ppDocument85 pagesDVD s100ppMarco RamosNo ratings yet

- Date Tehnice Bosch CCTVDocument27 pagesDate Tehnice Bosch CCTVCornelCiorcanNo ratings yet

- L32HP01E L32HP01U: Service Manual Manuel D'Entretien WartungshandbuchDocument78 pagesL32HP01E L32HP01U: Service Manual Manuel D'Entretien Wartungshandbuchsm14jNo ratings yet

- Features: 【 AVS-200D 】DecoderDocument2 pagesFeatures: 【 AVS-200D 】DecodermaecassiopeiaNo ratings yet

- Hitachi L26 L32A01ADocument68 pagesHitachi L26 L32A01ACarlos A. TorresNo ratings yet

- Hitachi LCD - Ls01 DVBT Service ManualDocument65 pagesHitachi LCD - Ls01 DVBT Service ManualMauro MangialavoriNo ratings yet

- Avc4000 HW A00Document23 pagesAvc4000 HW A00Cristian DumitrescuNo ratings yet

- Audio and Video BoqDocument8 pagesAudio and Video BoqmooorthuNo ratings yet

- User Guide: 10-Bit Multicodec EncoderDocument63 pagesUser Guide: 10-Bit Multicodec EncoderHami CostaNo ratings yet

- AML 8613 A/V Processor User's Guide: Amlogic, IncDocument25 pagesAML 8613 A/V Processor User's Guide: Amlogic, IncStefanMiticNo ratings yet

- EDGE Product ManualDocument95 pagesEDGE Product ManualPallab DasguptaNo ratings yet

- Flexwatch 3170Document10 pagesFlexwatch 3170opinadordeopiniaoNo ratings yet

- Changhong Chassis Ls03Document30 pagesChanghong Chassis Ls03Luděk Csiba100% (1)

- Enutv-3 Spec enDocument3 pagesEnutv-3 Spec enMarianoNo ratings yet

- CCTV Bosh Datasheet - Data - Sheet - enUS - 24097715595Document6 pagesCCTV Bosh Datasheet - Data - Sheet - enUS - 24097715595Dwitunggal EnergiNo ratings yet

- Ateme Kyrion Encoder Release Note AS2204 FW3.0.5-ev1.1 (3.0.5.4)Document14 pagesAteme Kyrion Encoder Release Note AS2204 FW3.0.5-ev1.1 (3.0.5.4)Techne PhobosNo ratings yet

- Service ManualDocument33 pagesService Manualmiguel angel jaramillo100% (2)

- Disclaimer: H81H3-M4 User ManualDocument30 pagesDisclaimer: H81H3-M4 User Manualmbj100000No ratings yet

- Vestel 17MB21-1Document50 pagesVestel 17MB21-1Bruno Mono0% (1)

- iAM VIDEO 2 - DDocument2 pagesiAM VIDEO 2 - DWildan SofyanNo ratings yet

- 13 - Video Chain in A Typical Doordarshan Studio - InductionDocument11 pages13 - Video Chain in A Typical Doordarshan Studio - InductionHISHIKESH PhukanNo ratings yet

- Data Sheet ST HDMI ControllerDocument7 pagesData Sheet ST HDMI Controlleralex20192No ratings yet

- DatasheetDocument52 pagesDatasheetMarek DabrowskiNo ratings yet

- MVP300Manual 2022.09Document12 pagesMVP300Manual 2022.09l23211506No ratings yet

- Section 16781 CCTV System: King Faisal University Al-Ahsa 16781-1 CCTV System Library BuildingDocument10 pagesSection 16781 CCTV System: King Faisal University Al-Ahsa 16781-1 CCTV System Library Buildingnadeem UddinNo ratings yet

- DVD 860Document30 pagesDVD 860lagreta55No ratings yet

- Chip Philips Toucam ProII Saa8116hlDocument20 pagesChip Philips Toucam ProII Saa8116hlEduardo AlamillaNo ratings yet

- NVR616R-64 128-4KS2 A e 20230922115701Document5 pagesNVR616R-64 128-4KS2 A e 20230922115701Tecnicos ConectNo ratings yet

- EN-200 ManualDocument67 pagesEN-200 ManualTony PerezNo ratings yet

- FA Mainboard CV512H-B42Document53 pagesFA Mainboard CV512H-B42Salomon ChiquilloNo ratings yet

- VLSI Design for Video Coding: H.264/AVC Encoding from Standard Specification to ChipFrom EverandVLSI Design for Video Coding: H.264/AVC Encoding from Standard Specification to ChipNo ratings yet

- Colour Banding: Exploring the Depths of Computer Vision: Unraveling the Mystery of Colour BandingFrom EverandColour Banding: Exploring the Depths of Computer Vision: Unraveling the Mystery of Colour BandingNo ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- BICSI RCDD Registered Communications Distribution Designer Exam Prep And Dumps RCDD-001 Exam Guidebook Updated QuestionsFrom EverandBICSI RCDD Registered Communications Distribution Designer Exam Prep And Dumps RCDD-001 Exam Guidebook Updated QuestionsNo ratings yet

- Manual Notebook H12YDocument38 pagesManual Notebook H12Ygm799763100% (2)

- M963G Motherboard Manual ECS / PCChips M963G (3.0B) EnglishDocument41 pagesM963G Motherboard Manual ECS / PCChips M963G (3.0B) Englishgm79976380% (5)

- M960GV Motherboard Manual ECS / PCChips 960GV (V3.0a)Document38 pagesM960GV Motherboard Manual ECS / PCChips 960GV (V3.0a)gm799763No ratings yet

- Manual Notebook H12YDocument38 pagesManual Notebook H12Ygm799763100% (2)

- Compaq PDFDocument198 pagesCompaq PDFfranjosssNo ratings yet

- Helicopter Rescue Sshrh2262010 A4 28672600Document2 pagesHelicopter Rescue Sshrh2262010 A4 28672600gm799763No ratings yet

- Hark New Version 05272011Document2 pagesHark New Version 05272011gm799763No ratings yet

- M863 AG Motherboard Manual ECS / PCChips 863AG - G (v5.1B) - EngDocument33 pagesM863 AG Motherboard Manual ECS / PCChips 863AG - G (v5.1B) - Enggm79976350% (2)

- Asus A7N266-VM Motherboard ManualDocument116 pagesAsus A7N266-VM Motherboard Manualgm799763No ratings yet

- M863G Motherboard Manual ECS / PCChips 863G (v5.1C) - EngDocument32 pagesM863G Motherboard Manual ECS / PCChips 863G (v5.1C) - Enggm799763100% (2)

- Xcom TFTD ManualDocument89 pagesXcom TFTD ManualEduardo Hein SotoNo ratings yet

- Motherboard ECS K7SEM V3.0Document38 pagesMotherboard ECS K7SEM V3.0gm7997630% (1)

- 4 Troubleshooting: 4-1 No PowerDocument4 pages4 Troubleshooting: 4-1 No Powergm799763No ratings yet

- 11 Disassembly and ReassemblyDocument10 pages11 Disassembly and ReassemblynoevidalNo ratings yet

- XCom UFO Defense ManualDocument134 pagesXCom UFO Defense ManualNewMaxx100% (1)

- 12 PCB LayoutDocument2 pages12 PCB Layoutgm799763No ratings yet

- 2 Product Specifications: 2-1 Fashion FeatureDocument4 pages2 Product Specifications: 2-1 Fashion Featuregm799763No ratings yet

- 6 partslist-LS17PENSF XAZDocument6 pages6 partslist-LS17PENSF XAZgm799763No ratings yet

- 8 Diagram WiringDocument2 pages8 Diagram Wiringgm799763No ratings yet

- 7 Block Diagram: 7-1 Power TreeDocument4 pages7 Block Diagram: 7-1 Power Treegm799763No ratings yet

- Unit 2Document15 pagesUnit 2Priyanka.T MBANo ratings yet

- BadmintonDocument7 pagesBadmintonAVEGAIL SALUDONo ratings yet

- BW Octnov08 TocDocument2 pagesBW Octnov08 TocInterweave40% (5)

- Design BDR For Load PebDocument4 pagesDesign BDR For Load Pebknight1729No ratings yet

- The Resistance (Rules Summary)Document1 pageThe Resistance (Rules Summary)Ethan DickinsonNo ratings yet

- Rephrasing TestDocument80 pagesRephrasing TestemmagutizNo ratings yet

- Pride and PrejudiceDocument2 pagesPride and PrejudiceLina TaehyungNo ratings yet

- Art Appre - Reflection Paper EuropeDocument1 pageArt Appre - Reflection Paper EuropegclaudenejoyNo ratings yet

- Hum 001 SyllabusDocument3 pagesHum 001 SyllabusHiro Jemmima RenoudNo ratings yet

- Asus Zenfone 4 ZE554KL - Full Phone SpecificationsDocument2 pagesAsus Zenfone 4 ZE554KL - Full Phone SpecificationsRally CautiverioNo ratings yet

- Service Manual: Sewing Machine Model 385, 15358Document32 pagesService Manual: Sewing Machine Model 385, 15358Theunis KokNo ratings yet

- Songs of BR AmitkDocument17 pagesSongs of BR AmitkJoel DsouzaNo ratings yet

- Infotech Institute College of Arts and Sciences Midterm Exam in World LiteratureDocument3 pagesInfotech Institute College of Arts and Sciences Midterm Exam in World LiteratureMichael Anthony EnajeNo ratings yet

- Pcratb PDFDocument1 pagePcratb PDFPablo RagoNo ratings yet

- Snow White PlayscriptDocument6 pagesSnow White PlayscriptNoreen's Del Fierro BOngoNo ratings yet

- JS API MAG200 (Rev 1.20) PDFDocument143 pagesJS API MAG200 (Rev 1.20) PDFGerson MayerNo ratings yet

- OngyoDocument1 pageOngyochrisNo ratings yet

- Je's AssignmentDocument5 pagesJe's Assignmentseyla sokNo ratings yet

- Downbeat 201002Document84 pagesDownbeat 201002Jonathan100% (1)

- Electric Counterpoint FULL REVISION NOTES PDFDocument2 pagesElectric Counterpoint FULL REVISION NOTES PDFMacca McNeneyNo ratings yet

- Kunci UkpDocument20 pagesKunci UkpFerdiNo ratings yet

- The Significance of USB Type C PCBDocument4 pagesThe Significance of USB Type C PCBjackNo ratings yet

- 2022 Suggested UASA Year 4Document7 pages2022 Suggested UASA Year 4g-39009559No ratings yet

- Cornerstone Alive in Us: G C9 D em D C9 D G C G em CDocument6 pagesCornerstone Alive in Us: G C9 D em D C9 D G C G em CNisha HernandezNo ratings yet

- Legit Applications For Iphone & Ipod Touch Only (Non-Jailbroken)Document105 pagesLegit Applications For Iphone & Ipod Touch Only (Non-Jailbroken)jiroyanNo ratings yet

- Left Hand Piano Accompaniment Styles - The Alberti BassDocument14 pagesLeft Hand Piano Accompaniment Styles - The Alberti BassLouis Migliore100% (1)

- Seduction Strategy 29 (NSFW)Document5 pagesSeduction Strategy 29 (NSFW)namjoonleftoenailNo ratings yet

- AbcdegdgDocument1 pageAbcdegdgShahid IlyasNo ratings yet

- The Purpose of LifeDocument33 pagesThe Purpose of LifeNandi Gnana Prakash Babu100% (1)