SMD 357

SMD 357

Uploaded by

Marcoantonio AntonioCopyright:

Available Formats

SMD 357

SMD 357

Uploaded by

Marcoantonio AntonioOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

SMD 357

SMD 357

Uploaded by

Marcoantonio AntonioCopyright:

Available Formats

April 1997

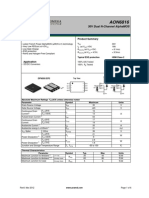

NDS351AN N-Channel Logic Level Enhancement Mode Field Effect Transistor

General Description

These N-Channel logic level enhancement mode power field effect transistors are produced using Fairchild's proprietary, high cell density, DMOS technology. This very high density process is especially tailored to minimize on-state resistance. These devices are particularly suited for low voltage applications in notebook computers, portable phones, PCMCIA cards, and other battery powered circuits where fast switching, and low in-line power loss are needed in a very small outline surface mount package.

Features

1.2A, 30 V. RDS(ON) = 0.25 @ VGS = 4.5 V RDS(ON) = 0.16 @ VGS = 10 V. Industry standard outline SOT-23 surface mount package using proprietary SuperSOTTM-3 design for superior thermal and electrical capabilities. High density cell design for extremely low RDS(ON). Exceptional on-resistance and maximum DC current capability. Compact industry standard SOT-23 surface mount

_________________________________________________________________________________

Absolute Maximum Ratings

Symbol VDSS VGSS ID PD TJ,TSTG Parameter Drain-Source Voltage

T A = 25C unless otherwise noted

NDS351AN 30 20

(Note 1a)

Units V V A

Gate-Source Voltage - Continuous Maximum Drain Current - Continuous - Pulsed Maximum Power Dissipation

(Note 1a) (Note 1b)

1.2 10 0.5 0.46 -55 to 150

Operating and Storage Temperature Range

THERMAL CHARACTERISTICS RJA RJC Thermal Resistance, Junction-to-Ambient Thermal Resistance, Junction-to-Case

(Note 1a) (Note 1)

250 75

C/W C/W

1997 Fairchild Semiconductor Corporation

NDS351AN Rev. C

Electrical Characteristics (TA = 25C unless otherwise noted)

Symbol Parameter Conditions Min Typ Max Units OFF CHARACTERISTICS BVDSS IDSS IGSSF IGSSR VGS(th) RDS(ON) Drain-Source Breakdown Voltage Zero Gate Voltage Drain Current VGS = 0 V, ID = 250 A VDS = 24 V, VGS = 0 V TJ =125C Gate - Body Leakage, Forward Gate - Body Leakage, Reverse VGS = 20 VDS = 0 V VGS = -20 V, VDS = 0 V VDS = VGS, ID = 250 A TJ =125C Static Drain-Source On-Resistance VGS = 4.5 V, ID = 1.2 A TJ =125C VGS = 10 V, ID = 1.4 A ID(ON) gFS Ciss Coss Crss td(on) tr td(off) tf Qg Q gs Q gd On-State Drain Current Forward Transconductance VGS = 4.5 V, VDS = 5 V VDS = 5 V, ID= 1.2 A, VDS = 10 V, VGS = 0 V, f = 1.0 MHz 3.5 1.8 0.8 0.5 1.7 1.3 0.19 0.28 0.125 30 1 10 100 -100 V A A nA nA

ON CHARACTERISTICS (Note 2) Gate Threshold Voltage 2 1.5 0.25 0.37 0.16 A S V

DYNAMIC CHARACTERISTICS Input Capacitance Output Capacitance Reverse Transfer Capacitance

(Note 2)

125 100 90

pF pF pF

SWITCHING CHARACTERISTICS Turn - On Delay Time Turn - On Rise Time Turn - Off Delay Time Turn - Off Fall Time Total Gate Charge Gate-Source Charge Gate-Drain Charge

VDD = 10 V, ID = 1 A, VGS = 10 V, RGEN = 50

6 15 14 18

15 30 30 40 2.7

ns ns ns ns nC nC nC

VDS = 10 V, ID = 1.2 A, VGS = 4.5 V

1.9 0.5 0.9

NDS351AN Rev. C

Electrical Characteristics (TA = 25C unless otherwise noted)

Symbol Parameter Conditions Min Typ Max Units DRAIN-SOURCE DIODE CHARACTERISTICS AND MAXIMUM RATINGS IS ISM VSD

Notes: 1. RJA is the sum of the junction-to-case and case-to-ambient thermal resistance where the case thermal reference is defined as the solder mounting surface of guaranteed by design while RCA is determined by the user's board design. the drain pins. RJC is

Maximum Continuous Drain-Source Diode Forward Current Maximum Pulsed Drain-Source Diode Forward Current Drain-Source Diode Forward Voltage VGS = 0 V, IS = 1.2 A (Note 2) 0.8

0.42 5 1.2

A A V

P D (t ) =

R JA(t )

T J TA

TJ

TA

R JC+RCA(t )

= I 2 (t ) RDS(ON ) D

TJ

Typical RJA using the board layouts shown below on 4.5"x5" FR-4 PCB in a still air environment: a. 250oC/W when mounted on a 0.02 in2 pad of 2oz copper. b. 270oC/W when mounted on a 0.001 in2 pad of 2oz copper.

1a

1b

Scale 1 : 1 on letter size paper 2. Pulse Test: Pulse Width < 300s, Duty Cycle < 2.0%.

NDS351AN Rev. C

Typical Electrical Characteristics

5 1.8

V GS =10V

I D , DRAIN-SOURCE CURRENT (A)

4

6.0

R DS(on ) , NORMALIZED DRAIN-SOURCE ON-RESISTANCE

5.0 4.5 4.0

1.6 1.4 1.2 1 0.8 0.6 0.4

VGS = 3.5V

3.5

2

4.0 4.5 5.0 6.0 7.0 10

3.0

1

0 0 V

DS

, DRAIN-SOURCE VOLTAGE (V)

2 I D , DRAIN CURRENT (A)

Figure 1. On-Region Characteristics.

Figure 2. On-Resistance Variation with Drain Current and Gate Voltage.

1.8

1.8 DRAIN-SOURCE ON-RESISTANCE I D = 1.2A 1.6 1.4 1.2 1 0.8 0.6 0.4

DRAIN-SOURCE ON-RESISTANCE

1.6

VGS = 4.5 V

R DS(ON), NORMALIZED

V GS = 4.5V

TJ = 125C

1.4

RDS(on) , NORMALIZED

1.2

25C -55C

0.8

0.6 -50

-25

0 25 50 75 100 T , JUNCTION TEMPERATURE (C) J

125

150

2 I D, DRAIN CURRENT (A)

Figure 3. On-Resistance Variation with Temperature.

Figure 4. On-Resistance Variation with Drain Current and Temperature.

V DS = 5.0V

4

25C

Vth , NORMALIZED GATE-SOURCE THRESHOLD VOLTAGE

T = -55C J

1.2 1.1 1 0.9 0.8 0.7 0.6 -50

I D , DRAIN CURRENT (A)

125C

3

V DS= V GS I D = 250A

0 0.5

1.5 V

GS

2.5

3.5

4.5

-25

, GATE TO SOURCE VOLTAGE (V)

0 25 50 75 100 TJ , JUNCTION TEMPERATURE (C)

125

150

Figure 5. Transfer Characteristics.

Figure 6. Gate Threshold Variation with Temperature.

NDS351AN Rev. C

Typical Electrical Characteristics (continued)

1.12

DRAIN-SOURCE BREAKDOWN VOLTAGE

I , REVERSE DRAIN CURRENT (A)

I D = 250A

1.08

V GS = 0V

1

BV DSS , NORMALIZED

TJ = 125C

0.1

25C -55C

1.04

0.01

0.96

0.001

0.92 -50

-25

0 T

J

25

50

75

100

125

150

0.0001 0 0.2 0.4 0.6 0.8 1 V SD , BODY DIODE FORWARD VOLTAGE (V) 1.2

, JUNCTION TEMPERATURE (C)

Figure 7. Breakdown Voltage Variation with Temperature.

Figure 8. Body Diode Forward Voltage Variation with Source Current and Temperature.

400 , GATE-SOURCE VOLTAGE (V) 300 CAPACITANCE (pF)

10

I D = 1.2A

8

VDS = 5V

10V 15V

200 150

C iss

100 80

C oss f = 1 MHz V GS = 0V C rss

50 0.1

V 0.2 V 0.5

DS

GS

10

20

30

, DRAIN TO SOURCE VOLTAGE (V)

2 Q g , GATE CHARGE (nC)

Figure 9. Capacitance Characteristics.

Figure 10. Gate Charge Characteristics.

VDD

t d(on)

t on

t off tr

90%

t d(off)

90%

tf

V IN

D

RL V OUT

VOUT

10%

VGS

R GEN

10%

INVERTED

DUT 90% S

V IN

10%

50%

50%

PULSE WIDTH

Figure 11. Switching Test Circuit.

Figure 12. Switching Waveforms.

NDS351AN Rev. C

Typical Electrical Characteristics (continued)

, TRANSCONDUCTANCE (SIEMENS) 5 20

VDS = 5.0V

I D , DRAIN CURRENT (A) 4

10

1m s

N) S(O RD IT LIM

T J = -55C 25C

5 3 1 0.3 0.1 0.03 0.01 0.1

10m 100 1s ms

125C

V GS = 4.5V SINGLE PULSE R JA =See Note1b T = 25C A

0.2 0.5 V

DS

10s DC

FS

2 3 I , DRAIN CURRENT (A)

D

10

20 30

50

, DRAI N-SOURCE VOLTAGE (V)

Figure 13. Transconductance Variation with Drain Current and Temperature.

Figure 14. Maximum Safe Operating Area.

STEADY-STATE POWER DISSIPATION (W)

1

I , STEADY-STATE DRAIN CURRENT (A)

1.6

0.8

1.4

0.6

1b

1a

1.2

1a

0.4

1b

4.5"x5" FR-4 Board TA = 2 5 C Still Air VG S = 4 . 5 V

o

0.2

4.5"x5" FR-4 Board TA = 25 oC Still Air

0.8 0 0.1 0.2 0.3 2oz COPPER MOUNTING PAD AREA (in 2 ) 0.4

0.1 0.2 0.3 2oz COPPER MOUNTING PAD AREA (in 2 )

0.4

Figue 15. SuperSOTTM _ 3 Maximum Steady-State Power Dissipation versus Copper Mounting Pad Area.

Figure 16. Maximum Steady-State Drain Current versus Copper Mounting Pad Area.

1

r(t), NORMALIZED EFFECTIVE TRANSIENT THERMAL RESISTANCE

0.5 0.2 0.1 0.05 0.02 0.01 0.005 0.002 0.001 0.0001

D = 0.5 0.2 0.1 0.05 0.02 0.01 Single Pulse

R JA (t) = r(t) * R JA R JA = See Note 1b

P(pk)

t1

t2

TJ - TA = P * R JA (t) Duty Cycle, D = t1 /t2

0.001

0.01

0.1 t 1 , TIME (sec)

10

100

300

Figure 17. Transient Thermal Response Curve.

Note : Characterization performed using the conditions described in note 1b. Transient thermal response will change depending on the circuit board design.

NDS351AN Rev. C

You might also like

- Irfp 260 NDocument9 pagesIrfp 260 NJolaine MojicaNo ratings yet

- Irfb4020Pbf: Digital Audio MosfetDocument8 pagesIrfb4020Pbf: Digital Audio Mosfetto_netiksNo ratings yet

- Fdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MDocument11 pagesFdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MKevin TateNo ratings yet

- Fdms0308Cs: N-Channel Powertrench SyncfetDocument8 pagesFdms0308Cs: N-Channel Powertrench Syncfetdreyes3773No ratings yet

- IRFP360LCDocument8 pagesIRFP360LCΗρακλης ΖερκελιδηςNo ratings yet

- Irlz 24 NDocument9 pagesIrlz 24 NRobson PontinNo ratings yet

- IRF540NDocument7 pagesIRF540Nmichaelliu123456No ratings yet

- Irf1405 DatasheetDocument9 pagesIrf1405 DatasheetE Alejandro G. BenavidesNo ratings yet

- FQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETDocument9 pagesFQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETsoweloNo ratings yet

- Irfz46n PDFDocument9 pagesIrfz46n PDFYunier FernandezNo ratings yet

- IRF830A: Smps MosfetDocument8 pagesIRF830A: Smps MosfetRICHIHOTS2No ratings yet

- N-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Document11 pagesN-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Kevin TateNo ratings yet

- Fds6982S: Dual Notebook Power Supply N-Channel Powertrench SyncfetDocument12 pagesFds6982S: Dual Notebook Power Supply N-Channel Powertrench SyncfetAlejandro DelgadoNo ratings yet

- International Rectifier IRFP2907Document9 pagesInternational Rectifier IRFP2907scribd20110526No ratings yet

- Irf 730 ADocument9 pagesIrf 730 Ajose_mamani_51No ratings yet

- IRFZ34N Datasheet - KDocument8 pagesIRFZ34N Datasheet - KNairo FilhoNo ratings yet

- AO4800 Dual N-Channel Enhancement Mode Field Effect TransistorDocument6 pagesAO4800 Dual N-Channel Enhancement Mode Field Effect Transistordreyes3773No ratings yet

- NTD78N03 Power MOSFET: 25 V, 78 A, Single N Channel, DPAKDocument7 pagesNTD78N03 Power MOSFET: 25 V, 78 A, Single N Channel, DPAKfercikeNo ratings yet

- Irfp2907Pbf: Typical ApplicationsDocument9 pagesIrfp2907Pbf: Typical Applicationsrajeev_kumar_1231852No ratings yet

- FET 75N75 TransistorDocument8 pagesFET 75N75 Transistorshahid iqbalNo ratings yet

- Dual N-Channel Enhancement Mode Phn210T Trenchmos TransistorDocument8 pagesDual N-Channel Enhancement Mode Phn210T Trenchmos TransistorCristian ViolaNo ratings yet

- Irl 530 NDocument9 pagesIrl 530 NEric Lenin Marin MoncadaNo ratings yet

- Generation V Technology Ultra Low On-Resistance Complimentary Half Bridge Surface Mount Fully Avalanche RatedDocument10 pagesGeneration V Technology Ultra Low On-Resistance Complimentary Half Bridge Surface Mount Fully Avalanche RatedFidel ArroyoNo ratings yet

- FDS4435BZDocument6 pagesFDS4435BZCornel PislaruNo ratings yet

- FDP 8896Document11 pagesFDP 8896condejhonnyNo ratings yet

- FQB8N60C / FQI8N60C: 600V N-Channel MOSFETDocument9 pagesFQB8N60C / FQI8N60C: 600V N-Channel MOSFETemelchor57No ratings yet

- FQD30N06L / FQU30N06L: 60V LOGIC N-Channel MOSFETDocument10 pagesFQD30N06L / FQU30N06L: 60V LOGIC N-Channel MOSFETJavier Ayerdis NarváezNo ratings yet

- Radiation Hardened Power Mosfet THRU-HOLE (T0-204AE) I R H 9 1 5 0 100V, P-CHANNELDocument8 pagesRadiation Hardened Power Mosfet THRU-HOLE (T0-204AE) I R H 9 1 5 0 100V, P-CHANNELDeepa DevarajNo ratings yet

- Data Sheet IRFB42N20DDocument8 pagesData Sheet IRFB42N20DvalubaNo ratings yet

- NDP6051 / NDB6051 N-Channel Enhancement Mode Field Effect TransistorDocument6 pagesNDP6051 / NDB6051 N-Channel Enhancement Mode Field Effect TransistorHoàng Ngọc QuyềnNo ratings yet

- 2N60Document8 pages2N60vdăduicăNo ratings yet

- FDMS3604SDocument12 pagesFDMS3604Sg_alinNo ratings yet

- IRF740B/IRFS740B: 400V N-Channel MOSFETDocument11 pagesIRF740B/IRFS740B: 400V N-Channel MOSFETMistery of the souldNo ratings yet

- Irlhs 6242 PBFDocument9 pagesIrlhs 6242 PBFSergiu HălăucăNo ratings yet

- Irfr3707Zpbf Irfu3707Zpbf: V R Max QGDocument11 pagesIrfr3707Zpbf Irfu3707Zpbf: V R Max QGJared RobisonNo ratings yet

- IRFB4227Document8 pagesIRFB4227Fco. Jefferson Ferreira de SáNo ratings yet

- Dual N-Channel, Notebook Power Supply MOSFET: June 1999Document9 pagesDual N-Channel, Notebook Power Supply MOSFET: June 1999dreyes3773No ratings yet

- IRF650B / IRFS650B: 200V N-Channel MOSFETDocument10 pagesIRF650B / IRFS650B: 200V N-Channel MOSFETbinoelNo ratings yet

- Irfp 460 ADocument8 pagesIrfp 460 AKasun Darshana PeirisNo ratings yet

- 13N60 Series: N-Channel Power MOSFET 13A, 600volts DescriptionDocument8 pages13N60 Series: N-Channel Power MOSFET 13A, 600volts DescriptionAndres AlegriaNo ratings yet

- IRF9540NDocument8 pagesIRF9540Nhardik_patel182000No ratings yet

- N 308 ApDocument11 pagesN 308 Apdragon-red0816No ratings yet

- N Mosfet Fdv303nDocument4 pagesN Mosfet Fdv303nxlam99No ratings yet

- Irfp 90 N 20 DDocument9 pagesIrfp 90 N 20 DAndré Frota PaivaNo ratings yet

- Fdb045An08A0: N-Channel Powertrench MosfetDocument12 pagesFdb045An08A0: N-Channel Powertrench MosfetRocio HernandezNo ratings yet

- Irfps 3810 PBFDocument8 pagesIrfps 3810 PBFCrisan Radu-HoreaNo ratings yet

- IRF3710Document8 pagesIRF3710Andrés MorochoNo ratings yet

- Advanced Power Electronics Corp.: AP4525GEMDocument7 pagesAdvanced Power Electronics Corp.: AP4525GEMsontuyet82No ratings yet

- Data SSMPS MOSFETheetDocument8 pagesData SSMPS MOSFETheetwaqasmirNo ratings yet

- Irfz 34 NLDocument10 pagesIrfz 34 NLguerrero_27No ratings yet

- Radiation Hardened IRHNA57163SE Power Mosfet Surface Mount (Smd-2) 130V, N-CHANNELDocument8 pagesRadiation Hardened IRHNA57163SE Power Mosfet Surface Mount (Smd-2) 130V, N-CHANNELbmmostefaNo ratings yet

- MosfetDocument6 pagesMosfetfilibertooNo ratings yet

- IRL540NDocument8 pagesIRL540Nmestek123No ratings yet

- Irfz 48 VDocument8 pagesIrfz 48 VZoltán HalászNo ratings yet

- General Description Product Summary: 30V Dual N-Channel AlphamosDocument6 pagesGeneral Description Product Summary: 30V Dual N-Channel AlphamosMateus RossiniNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Electricity in Fish Research and Management: Theory and PracticeFrom EverandElectricity in Fish Research and Management: Theory and PracticeNo ratings yet

- Eston's Prediction of Body Fat and Fat Free Mass Index From SkinfoldsDocument5 pagesEston's Prediction of Body Fat and Fat Free Mass Index From SkinfoldsHuy Tuan LyNo ratings yet

- DC MachineDocument30 pagesDC MachineAzza FaiadNo ratings yet

- Rizal Module 4 EndtermDocument8 pagesRizal Module 4 EndtermGerose TubianosaNo ratings yet

- Natural Science Weekly PlannerDocument50 pagesNatural Science Weekly Plannererikalee942No ratings yet

- Iso 20345 2021Document14 pagesIso 20345 2021Flaviano CavalcantiNo ratings yet

- Types of Ships Tramp ShipsDocument3 pagesTypes of Ships Tramp ShipsDurao SebastiaoNo ratings yet

- Hydralazine Drug StudyDocument1 pageHydralazine Drug StudySabrina MascardoNo ratings yet

- Business PlanDocument20 pagesBusiness PlanRachel Anne MasangcayNo ratings yet

- There To Be Explanation and ExercisesDocument4 pagesThere To Be Explanation and ExercisesmiteacherNo ratings yet

- Bhrugu Bindu Theory - (Bhrugu Chakra Paddhati) - 1-3Document36 pagesBhrugu Bindu Theory - (Bhrugu Chakra Paddhati) - 1-3Sampath Kumar99% (86)

- Native American Creation Stories From The Southwestern United StatesDocument9 pagesNative American Creation Stories From The Southwestern United StatesKent HuffmanNo ratings yet

- 2021 Ninja 650 Abs en Us Spec SheetDocument1 page2021 Ninja 650 Abs en Us Spec SheetlensfortNo ratings yet

- Contributions Realistic/Research-based Evidence/s in Our Society 1. CompassDocument3 pagesContributions Realistic/Research-based Evidence/s in Our Society 1. CompassJerickson Mauricio100% (1)

- 2003 Chemistry Higher Finalised Marking InstructionsDocument23 pages2003 Chemistry Higher Finalised Marking InstructionsrussellmackayNo ratings yet

- Prop ReportDocument51 pagesProp ReportEmmanuel Delos SantosNo ratings yet

- DNV-RU-INV Pt.1 Ch.1Document27 pagesDNV-RU-INV Pt.1 Ch.1TumulNo ratings yet

- Isolated Footing Design (ACI 318-11) - Metric: ElevationDocument12 pagesIsolated Footing Design (ACI 318-11) - Metric: ElevationOsas Asemota-OsagieNo ratings yet

- Invalco Brochure PDFDocument20 pagesInvalco Brochure PDFMargaret DaughertyNo ratings yet

- Traditional BankingDocument7 pagesTraditional BankingYulius PurnamaNo ratings yet

- r2015 07 AllDocument64 pagesr2015 07 AllRezhaNo ratings yet

- Pre-Cast Concrete SystemDocument24 pagesPre-Cast Concrete SystemAnonymous 5kOS4t100% (1)

- 2016 Nutrient Specifications Manual - Metric - 9-21-16 PDFDocument62 pages2016 Nutrient Specifications Manual - Metric - 9-21-16 PDFAnna Clarissa Concepcion Villanueva100% (1)

- Steve's Handy Guide To Orbits: by Steven M. Schultheis, P.E. Houston, Texas U.S.ADocument25 pagesSteve's Handy Guide To Orbits: by Steven M. Schultheis, P.E. Houston, Texas U.S.AMuhammad HaroonNo ratings yet

- Pro Line 21™ Integrated Avionics Upgrades Collins AerospaceDocument1 pagePro Line 21™ Integrated Avionics Upgrades Collins AerospaceSahan RathnayakeNo ratings yet

- Jesus The Bread of HeavenDocument3 pagesJesus The Bread of HeavenNeli MirandaNo ratings yet

- Types of MicroorganismDocument20 pagesTypes of MicroorganismFrances Audrey TagupaNo ratings yet

- Mech ErectionDocument2 pagesMech ErectionMohammed Mostafa El HaddadNo ratings yet

- World of Legends Reading Comprehension Exercises - 118219Document2 pagesWorld of Legends Reading Comprehension Exercises - 118219wisepupilNo ratings yet

- Crepes On Gaskill: The Canowindra PhoenixDocument4 pagesCrepes On Gaskill: The Canowindra PhoenixCanowindra PhoenixNo ratings yet

- 16 CFR 1500.44Document2 pages16 CFR 1500.44Milagros WieczorekNo ratings yet