OpAmp - LF451

OpAmp - LF451

Uploaded by

Ludwig SchmidtCopyright:

Available Formats

OpAmp - LF451

OpAmp - LF451

Uploaded by

Ludwig SchmidtOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

OpAmp - LF451

OpAmp - LF451

Uploaded by

Ludwig SchmidtCopyright:

Available Formats

TLH9660

L

F

4

5

1

W

i

d

e

-

B

a

n

d

w

i

d

t

h

J

F

E

T

-

I

n

p

u

t

O

p

e

r

a

t

i

o

n

a

l

A

m

p

l

i

f

i

e

r

December 1995

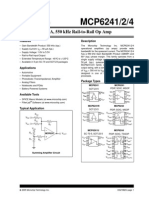

LF451 Wide-Bandwidth

JFET-Input Operational Amplifier

General Description

The LF451 is a low-cost high-speed JFET-input operational

amplifier with an internally trimmed input offset voltage (BI-

FET II

TM

technology) The device requires a low supply cur-

rent and yet maintains a large gain bandwidth product and a

fast slew rate In addition well matched high voltage JFET

input devices provide very low input bias and offset cur-

rents The LF451 is pin compatible with the standard

LM741 allowing designers to upgrade the overall perform-

ance of existing designs

The LF451 may be used in such applications as high-speed

integrators fast DA converters sample-and-hold circuits

and many other circuits requiring low input bias current high

input impedance high slew rate and wide bandwidth

Features

Y

Internally trimmed offset voltage 50 mV (max)

Y

Low input bias current 50 pA (typ)

Y

Low input noise current 001 pA0Hz (typ)

Y

Wide gain bandwidth 4 MHz (typ)

Y

High slew rate 13 Vms (typ)

Y

Low supply current 34 mA (max)

Y

High input impedance 10

12

X (typ)

Y

Low total harmonic distortion A

V

e 10

k

002% (typ)

R

L

e 10k V

O

e 20 V

pp

f e 20 Hz20 kHz

Y

Low 1f noise corner 50 Hz (typ)

Y

Fast settling time to 001% 2 ms (typ)

Connection Diagram

SO Package

TLH96602

Top View

Order Number LF451CM

See NS Package Number M08A

Typical Connection

TLH96601

Simplified Schematic

TLH96603

BI-FETTM is a trademark of National Semiconductor Corporation

C1995 National Semiconductor Corporation RRD-B30M125Printed in U S A

Absolute Maximum Ratings (Note 1)

If MilitaryAerospace specified devices are required

please contact the National Semiconductor Sales

OfficeDistributors for availability and specifications

Supply Voltage (V

a

bV

b

) 36V

Input Voltage Range V

b

s

V

IN

s

Va

Differential Input Voltage (Note 2) g30V

Junction Temperature (T

J

MAX) 150C

Output Short Circuit Duration Continuous

Power Dissipation (Note 3) 500 mW

ESD Tolerance TBD

Soldering Information (Note 5)

SO Package Vapor Phase (60 sec) 215C

Infrared (15 sec) 220C

Operating Ratings (Note 1)

Temperature Range T

MIN

s

T

A

s

T

MAX

LF451CM 0C

s

T

A

s a70C

Junction Temperature (T

J max

) 125C

Supply Voltage (V

a

bV

b

) 10V to 32V

DC Electrical Characteristics The following specifications apply for V

a

e a15V and V

b

e b15V Bold-

face limits apply for T

MIN

to T

MAX

all other limits T

A

e T

J

e 25C

LF451CM

Symbol Parameter Conditions Typical

Tested Design

Units

(Note 6)

Limit Limit

(Note 7) (Note 8)

V

OS

Maximum Input Offset Voltage R

S

e 10 kX (Note 10) 03 5 mV

I

OS

Maximum Input Offset Current (Notes 9 10) T

J

e 25C 25 100 pA

T

J

e 70C 2 nA

I

B

Maximum Input Bias Current (Notes 9 10) T

J

e 25C 50 200 pA

T

J

e 70C 4 nA

R

IN

Input Resistance T

J

e 25C 10

12

X

AVOL Minimum Large Signal V

O

e g10V R

L

e 2 kX

200 50 25 VmV

Voltage Gain (Note 10)

V

O

Minimum Output Voltage Swing R

L

e 10k g135 g12 g12 V

V

CM

Minimum Input Common Mode a145 a11 a11 V

Voltage Range b115 b11 b11 V

CMRR Minimum Common-Mode R

S

s

10 kX

100 80 80 dB

Rejection Ratio

PSRR Minimum Supply Voltage (Note 11)

100 80 80 dB

Rejection Ratio

I

S

Maximum Supply Current 34 34 mA

AC Electrical Characteristics The following specifications apply for V

a

e a15V and V

b

e b15V Bold-

face limits apply for T

MIN

to T

MAX

all other limits T

A

e T

J

e 25C

LF451CM

Symbol Parameter Conditions Typical

Tested Design

Units

(Note 6)

Limit Limit

(Note 7) (Note 8)

SR Slew Rate A

V

e a1 13 8 Vms

GBW Minimum Gain-Bandwidth Product f e 100 kHz 4 27 MHz

e

n

Equivalent Input Noise Voltage R

S

e 100X f e 1 kHz 25 nV0Hz

i

n

Equivalent Input Noise Current R

S

e 100X f e 1 kHz 001 pA0Hz

Note 1 Absolute Maximum Ratings indicate limits beyond which damage to the device may occur DC and AC electrical specifications do not apply when operating

the device beyond its specified operating ratings

Note 2 When the input voltage exceeds the power supplies the current should be limited to 1 mA

Note 3 The maximum power dissipation must be derated at elevated temperatures and is dictated by T

J

MAX i

JA

and the ambient temperature T

A

The maximum

allowable power dissipation at any temperature is P

D

e (T

J

MAX b T

A

)i

JA

or the number given in the Absolute Maximum Ratings whichever is lower For

guaranteed operation T

J max

e 125C The typical thermal resistance (i

JA

) of the LF451CM when board-mounted is 170CW

Note 5 See AN-450 Surface Mounting Methods and Their Effect on Product Reliability (Appendix D) for other methods of soldering surface mount devices

Note 6 Typicals are at T

J

e 25C and represent most likely parametric norm

2

Note 7 Tested limits are guaranteed to Nationals AOQL (Average Outgoing Quality Level)

Note 8 Design limits are guaranteed to Nationals AOQL but not 100% tested

Note 9 The input bias currents are junction leakage currents which approximately double for every 10C increase in the junction temperature T

J

Due to limited

production test time the input bias currents are correlated to junction temperature In normal operation the junction temperature rises above the ambient

temperature as a result of internal power dissipation P

D

T

J

e T

A

a i

JA

P

D

where i

JA

is the thermal resistance from junction to ambient

Note 10 V

OS

I

B

AVOL and I

OS

are measured at V

CM

e 0V

Note 11 Supply voltage rejection ratio is measured for both supply magnitudes increasing or decreasing simultaneously in accordance with common practice

Typical Performance Characteristics

Distortion vs Frequency Voltage Swing

Undistorted Output

Response

Open Loop Frequency

Rejection Ratio

Common-Mode

Rejection Ratio

Power Supply

Noise Voltage

Equivalent Input

Gain (VV)

Open Loop Voltage

Output Impedance Inverter Settling Time

TLH96605

3

Typical Performance Characteristics (Continued)

Input Bias Current Input Bias Current Supply Current

Input Voltage Limit

Positive Common-Mode

Input Voltage Limit

Negative Common-Mode

Positive Current Limit

Negative Current Limit Voltage Swing Output Voltage Swing

Gain Bandwidth Bode Plot Slew Rate

TLH96604

4

Pulse Response

Small Signal Inverting

TLH96606

Small Signal Non-Inverting

TLH96607

Large Signal Inverting

TLH96608

Large Signal Non-Inverting

TLH96609

Current Limit (R

L

e 100X)

TLH966010

Application Hints

The LF451CM is an op amp with an internally trimmed input

offset voltage and JFET input devices (BI-FET II) These

JFETs have large reverse breakdown voltages from gate to

source and drain eliminating the need for clamps across the

inputs Therefore large differential input voltages can easily

be accommodated without a large increase in input current

The maximum differential input voltage is independent of

the supply voltages However neither of the input voltages

should be allowed to exceed the negative supply as this will

cause large currents to flow which can result in a destroyed

unit

Exceeding the negative common-mode limit with the non-in-

verting input or with both inputs will force the output to a

high state potentially causing a reversal of phase to the

output

In neither case does a latch occur since raising the input

back within the common-mode range again puts the input

stage and thus the amplifier in a normal operating mode

5

Application Hints (Continued)

Exceeding the positive common-mode limit on a single input

will not change the phase of the output however if both

inputs exceed the limit the output of the amplifier will be

forced to a high state

The amplifier will operate with a common-mode input volt-

age equal to the positive supply however the gain band-

width and slew rate may be decreased in this condition

When the negative common-mode voltage swings to within

3V of the negative supply an increase in input offset voltage

may occur

The LF451 is biased by a zener reference which allows nor-

mal circuit operation on g4V power supplies Supply volt-

ages less than these may result in lower gain bandwidth and

slew rate

The LF451 will drive a 2 kX load resistance to g10V over

the full temperature range of 0C to a70C If the amplifier

is forced to drive heavier load currents however an in-

crease in input offset voltage may occur on the negative

voltage swing and finally reach an active current limit on

both positive and negative swings

Precautions should be taken to ensure that the power sup-

ply for the integrated circuit never becomes reversed in po-

larity or that the unit is not inadvertently installed backwards

in a socket as an unlimited current surge through the result-

ing forward diode within the IC could cause fusing of the

internal conductors and result in a destroyed unit

As with most amplifiers care should be taken with lead

dress component placement and supply decoupling in or-

der to ensure stability For example resistors from the out-

put to an input should be placed with the body close to the

input to minimize pick-up and maximize the frequency of

the feedback pole by minimizing the capacitance from the

input to ground

A feedback pole is created when the feedback around any

amplifier is resistive The parallel resistance and capaci-

tance from the input of the device (usually the inverting in-

put) to AC ground set the frequency of the pole In many

instances the frequency of this pole is much greater than

the expected 3 dB frequency of the closed loop gain and

consequently there is negligible effect on stability margin

However if the feedback pole is less than approximately 6

times the expected 3 dB frequency a lead capacitor should

be placed from the output to the input of the op amp The

value of the added capacitor should be such that the RC

time constant of this capacitor and the resistance it parallels

is greater than or equal to the original feedback pole time

constant

The benefit of the SO package results from its very small

size It follows however that the die inside the SO pack-

age is less protected from external physical forces than a

die in a standard DIP would be because there is so much

less plastic in the SO Therefore not following certain pre-

cautions when board mounting the LF451CM can put me-

chanical stress on the die lead frame andor bond wires

This can cause shifts in the LF451CMs parameters even

causing them to exceed limits specified in the Electrical

Characteristics For recommended practices in LF451CM

surface mounting refer to Application Note AN-450 Sur-

face Mounting Methods and Their Effect on Product Reli-

ability and to Section 6 Surface Mount found in any

Rev 1 Linear Databook volume

Detailed Schematic

TLH966011

6

7

L

F

4

5

1

W

i

d

e

-

B

a

n

d

w

i

d

t

h

J

F

E

T

-

I

n

p

u

t

O

p

e

r

a

t

i

o

n

a

l

A

m

p

l

i

f

i

e

r

Physical Dimensions inches (millimeters) Lit 106161

Small Outline Package (M)

Order Number LF451CM

NS Package Number M08A

LIFE SUPPORT POLICY

NATIONALS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL

SEMICONDUCTOR CORPORATION As used herein

1 Life support devices or systems are devices or 2 A critical component is any component of a life

systems which (a) are intended for surgical implant support device or system whose failure to perform can

into the body or (b) support or sustain life and whose be reasonably expected to cause the failure of the life

failure to perform when properly used in accordance support device or system or to affect its safety or

with instructions for use provided in the labeling can effectiveness

be reasonably expected to result in a significant injury

to the user

National Semiconductor National Semiconductor National Semiconductor National Semiconductor

Corporation Europe Hong Kong Ltd Japan Ltd

1111 West Bardin Road Fax (a49) 0-180-530 85 86 13th Floor Straight Block Tel 81-043-299-2309

Arlington TX 76017 Email cnjwgetevm2nsccom Ocean Centre 5 Canton Rd Fax 81-043-299-2408

Tel 1(800) 272-9959 Deutsch Tel (a49) 0-180-530 85 85 Tsimshatsui Kowloon

Fax 1(800) 737-7018 English Tel (a49) 0-180-532 78 32 Hong Kong

Franais Tel (a49) 0-180-532 93 58 Tel (852) 2737-1600

Italiano Tel (a49) 0-180-534 16 80 Fax (852) 2736-9960

National does not assume any responsibility for use of any circuitry described no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications

You might also like

- A Guide to Electronic Maintenance and RepairsFrom EverandA Guide to Electronic Maintenance and RepairsRating: 4.5 out of 5 stars4.5/5 (7)

- SpaceLabs Qube 91390 Service ManualDocument160 pagesSpaceLabs Qube 91390 Service ManualGandy Torres TorresNo ratings yet

- Implementation of Uart On An FpgaDocument31 pagesImplementation of Uart On An FpgaNishanth KrishnappaNo ratings yet

- TL081Document9 pagesTL081Vero PorrasNo ratings yet

- LF351NDocument11 pagesLF351NAndres CampoNo ratings yet

- LF353Document13 pagesLF353cromus_9000No ratings yet

- LF444 Quad Low Power JFET Input Operational Amplifier: General Description FeaturesDocument11 pagesLF444 Quad Low Power JFET Input Operational Amplifier: General Description FeaturesJohn PachecoNo ratings yet

- tl082cp DatasheetDocument15 pagestl082cp DatasheetHeriberto Flores AmpieNo ratings yet

- Tl082cp Datasheet de National Semiconductor para Sustituir Ci de Etapa Pre Amplificador Bunker Mx2400 2Document12 pagesTl082cp Datasheet de National Semiconductor para Sustituir Ci de Etapa Pre Amplificador Bunker Mx2400 2Jess AJNo ratings yet

- tl082 Op Amp DatasheetDocument23 pagestl082 Op Amp DatasheetnurburgNo ratings yet

- TL082 EqualizerDocument16 pagesTL082 EqualizerMecabot DzibNo ratings yet

- Unisonic Technologies Co., LTD: Low Noise Quad J-Fet Operational AmplifierDocument5 pagesUnisonic Technologies Co., LTD: Low Noise Quad J-Fet Operational Amplifiergaldos08No ratings yet

- TL082Document14 pagesTL082radioscribdNo ratings yet

- LF442Document14 pagesLF442atavachronNo ratings yet

- Boost Controller With Power Factor CorrectionDocument14 pagesBoost Controller With Power Factor CorrectionChiseledPrawnNo ratings yet

- Datasheet LF412CNDocument14 pagesDatasheet LF412CNJose Fernando Perdomo BolañosNo ratings yet

- LF442CNDocument13 pagesLF442CNFSNo ratings yet

- LF 351Document14 pagesLF 351Ivan PetrovicNo ratings yet

- Datasheet LF 353Document14 pagesDatasheet LF 353Anggridho MeilandanuNo ratings yet

- Lm386 DatasheetDocument7 pagesLm386 DatasheetJM Carrasco HottmanNo ratings yet

- Data SheetDocument10 pagesData SheetselocaNo ratings yet

- LM397MF Comparador 6 Pines PDFDocument8 pagesLM397MF Comparador 6 Pines PDFAndres AlegriaNo ratings yet

- Opamp - Lf155 Lf156 Lf157 - NatsemDocument19 pagesOpamp - Lf155 Lf156 Lf157 - NatsemLudwig SchmidtNo ratings yet

- LF347n PDFDocument13 pagesLF347n PDFDiego PeñuelaNo ratings yet

- Constant Current Led DriverDocument27 pagesConstant Current Led DriverJubin JainNo ratings yet

- Ncl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsDocument10 pagesNcl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsKhúc Hành QuânNo ratings yet

- AOZ1031AIDocument15 pagesAOZ1031AIrachnologistNo ratings yet

- LM3900Document20 pagesLM3900Wilfredo MarquezNo ratings yet

- LM324 OpampDocument9 pagesLM324 OpampYuvarajaNo ratings yet

- TE CH: Features General DescriptionDocument10 pagesTE CH: Features General DescriptionJuan VillanuevaNo ratings yet

- Voltage Comperator3 LM397Document10 pagesVoltage Comperator3 LM397ΠΑΝΑΓΙΩΤΗΣΠΑΝΑΓΟΣNo ratings yet

- LM3478 High Efficiency Low-Side N-Channel Controller For Switching RegulatorDocument22 pagesLM3478 High Efficiency Low-Side N-Channel Controller For Switching RegulatorVinoth Kumar RajendranNo ratings yet

- Ca3140, Ca3140A: 4.5Mhz, Bimos Operational Amplifier With Mosfet Input/Bipolar Output FeaturesDocument22 pagesCa3140, Ca3140A: 4.5Mhz, Bimos Operational Amplifier With Mosfet Input/Bipolar Output FeaturesfcabreraibanezNo ratings yet

- LM108A/LM208A/LM308A Operational Amplifiers: General DescriptionDocument8 pagesLM108A/LM208A/LM308A Operational Amplifiers: General DescriptioncrizerNo ratings yet

- LF155Document24 pagesLF155Brzata PticaNo ratings yet

- LM138, LM338 5-Amp Adjustable Regulators: General DescriptionDocument14 pagesLM138, LM338 5-Amp Adjustable Regulators: General DescriptionrrebollarNo ratings yet

- Xl6009e1 Switch Mode IcDocument7 pagesXl6009e1 Switch Mode IctamaramarcuNo ratings yet

- LM759/LM77000 Power Operational Amplifiers: General Description FeaturesDocument15 pagesLM759/LM77000 Power Operational Amplifiers: General Description FeaturesgustavoblimaNo ratings yet

- 1.5A Power Switching Regulator: DescriptionDocument16 pages1.5A Power Switching Regulator: DescriptionPravin MevadaNo ratings yet

- LM 1875Document13 pagesLM 1875pblhnrqNo ratings yet

- Act 4065Document9 pagesAct 4065bob75No ratings yet

- LM2907 LM2917 Conversor F - VDocument18 pagesLM2907 LM2917 Conversor F - VAlejandra Vasquez GiraldoNo ratings yet

- LM78S40 Universal Switching Regulator Subsystem: General Description FeaturesDocument9 pagesLM78S40 Universal Switching Regulator Subsystem: General Description FeaturesgusguicorNo ratings yet

- General Purpose JFET Quad Operational Amplifiers: FeaturesDocument20 pagesGeneral Purpose JFET Quad Operational Amplifiers: FeaturesBruno NascimentoNo ratings yet

- LF351Document10 pagesLF351Benjamin JonesNo ratings yet

- LM358 PDFDocument14 pagesLM358 PDFChetan KotwalNo ratings yet

- AOZ1021AIDocument15 pagesAOZ1021AIJohnny La Mesa100% (1)

- TD1501Document18 pagesTD1501Hernando GamaNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Analog Dialogue Volume 46, Number 1: Analog Dialogue, #5From EverandAnalog Dialogue Volume 46, Number 1: Analog Dialogue, #5Rating: 5 out of 5 stars5/5 (1)

- Analog Dialogue, Volume 48, Number 1: Analog Dialogue, #13From EverandAnalog Dialogue, Volume 48, Number 1: Analog Dialogue, #13Rating: 4 out of 5 stars4/5 (1)

- A Guide to Vintage Audio Equipment for the Hobbyist and AudiophileFrom EverandA Guide to Vintage Audio Equipment for the Hobbyist and AudiophileNo ratings yet

- Influence of System Parameters Using Fuse Protection of Regenerative DC DrivesFrom EverandInfluence of System Parameters Using Fuse Protection of Regenerative DC DrivesNo ratings yet

- T BJT - Tip41 - Tip42 (Met Pinout)Document4 pagesT BJT - Tip41 - Tip42 (Met Pinout)Ludwig SchmidtNo ratings yet

- SOUND CARD - Sblive24 Sound Blaster Live! 24-Bit ExternalDocument2 pagesSOUND CARD - Sblive24 Sound Blaster Live! 24-Bit ExternalLudwig SchmidtNo ratings yet

- T Fet N - Bf245a-B-c - 2 - PhilipsDocument12 pagesT Fet N - Bf245a-B-c - 2 - PhilipsLudwig SchmidtNo ratings yet

- Reg - LM2931Document18 pagesReg - LM2931Ludwig SchmidtNo ratings yet

- R POT - Insulated Shaft Potentiometer RK09K+RK09D Series - 0900766b80f4c571Document7 pagesR POT - Insulated Shaft Potentiometer RK09K+RK09D Series - 0900766b80f4c571Ludwig SchmidtNo ratings yet

- Router Wlan Gbit Tl-wr1043nd - v1 - DatasheetDocument3 pagesRouter Wlan Gbit Tl-wr1043nd - v1 - DatasheetLudwig SchmidtNo ratings yet

- OpAmp - MCP6244Document38 pagesOpAmp - MCP6244Ludwig SchmidtNo ratings yet

- OpAmp - LM308AN - National Semiconductor - 49173 - DSDocument9 pagesOpAmp - LM308AN - National Semiconductor - 49173 - DSLudwig SchmidtNo ratings yet

- OpAmp - MCP6241Document28 pagesOpAmp - MCP6241Ludwig SchmidtNo ratings yet

- OpAmp - LM308AN - MotorolaDocument9 pagesOpAmp - LM308AN - MotorolaLudwig SchmidtNo ratings yet

- Opamp - Lf155 Lf156 Lf157 - NatsemDocument19 pagesOpamp - Lf155 Lf156 Lf157 - NatsemLudwig SchmidtNo ratings yet

- Mcu - r8c27 - Renesas r8c26 r8c27 - HW Manual - 16-Bit Single-Chip Mcu - m16c Family r8c Tiny SeriesDocument482 pagesMcu - r8c27 - Renesas r8c26 r8c27 - HW Manual - 16-Bit Single-Chip Mcu - m16c Family r8c Tiny SeriesLudwig SchmidtNo ratings yet

- Mcu - r8c27 - Renesas r8c26 r8c27 - Software Manual Rej09b0001 - r8csmDocument298 pagesMcu - r8c27 - Renesas r8c26 r8c27 - Software Manual Rej09b0001 - r8csmLudwig SchmidtNo ratings yet

- Vektor Ablerex-800L - 1000L-TearsheetDocument1 pageVektor Ablerex-800L - 1000L-TearsheetJhonSitanalaNo ratings yet

- Sliding Mode ControlDocument12 pagesSliding Mode ControlakhilvjNo ratings yet

- A 19.8 MW Eddy Current Displacement Sensor Interface With Sub Nanometer ResolutionDocument13 pagesA 19.8 MW Eddy Current Displacement Sensor Interface With Sub Nanometer ResolutionSiphesihle NkosiNo ratings yet

- Wxpvm70mna0001e 01 7 RecorderDocument116 pagesWxpvm70mna0001e 01 7 RecorderSandro SammoriNo ratings yet

- EE8701 Unit1-Two MarkDocument7 pagesEE8701 Unit1-Two Marksaikarthick023No ratings yet

- Electrical TheoryDocument32 pagesElectrical TheoryFRANCES ANN ESPONILLANo ratings yet

- Submittal AM072BXVGJHAADocument2 pagesSubmittal AM072BXVGJHAASaul AguilarNo ratings yet

- CSE DEPT LIBRARY Total Book List Until January2014 PDFDocument24 pagesCSE DEPT LIBRARY Total Book List Until January2014 PDFasdfhh0% (1)

- AIM Tech-Sheet: Solder Paste Handling GuidelinesDocument4 pagesAIM Tech-Sheet: Solder Paste Handling GuidelinesDaniel I. AlcantaraNo ratings yet

- PCDocument25 pagesPCPrasun BiswasNo ratings yet

- MAE 334 - Introduction To Computers and Instrumentation. Lec 1 IntroductionDocument13 pagesMAE 334 - Introduction To Computers and Instrumentation. Lec 1 IntroductionKhoa Ngo NhuNo ratings yet

- Software Linearization of An RTD SensorDocument6 pagesSoftware Linearization of An RTD SensorgrbavithraNo ratings yet

- DPG409Document3 pagesDPG409samuelNo ratings yet

- Logic 1 and Is Historically Referred To As "Marking." Similarly, A High Level (+3V To +15V) Is Defined As Logic 0 and Is Referred To As "Spacing."Document4 pagesLogic 1 and Is Historically Referred To As "Marking." Similarly, A High Level (+3V To +15V) Is Defined As Logic 0 and Is Referred To As "Spacing."Mohammad NadimNo ratings yet

- Machine Condition Tester T30: Instruction ManualDocument85 pagesMachine Condition Tester T30: Instruction ManualDaniel ArbeláezNo ratings yet

- Vitrafix Accessories Brochure V2Document7 pagesVitrafix Accessories Brochure V2Nooong NooongNo ratings yet

- Matz 1Document30 pagesMatz 1Ritesh Jaiswal100% (1)

- Folder 3 - Publikasi - SAY - IMA1IFDocument5 pagesFolder 3 - Publikasi - SAY - IMA1IFrin taNo ratings yet

- DVR Dahua Dvr5104h enDocument3 pagesDVR Dahua Dvr5104h enBuliga FlorinNo ratings yet

- Trans 4v DensitometerDocument4 pagesTrans 4v DensitometerTapan NayakNo ratings yet

- C30733EH-1 DatasheetDocument7 pagesC30733EH-1 DatasheetnicknaydehoclaptrinhNo ratings yet

- Controlador 320BDocument12 pagesControlador 320BJuank Jacales100% (4)

- Hirschmann NEW 9000K CatalogDocument24 pagesHirschmann NEW 9000K CatalogAllan Nalla100% (1)

- Letter WritingDocument14 pagesLetter Writingharpal_161No ratings yet

- Physics 2 - Midterm ReflectionDocument6 pagesPhysics 2 - Midterm ReflectionBalane, Ellezer Jay A.No ratings yet

- Design and Development of A Heart Rate Measuring Device Using FingertipDocument6 pagesDesign and Development of A Heart Rate Measuring Device Using FingertipKazandra Cassidy GarciaNo ratings yet

- Gold Chemistry 2Document189 pagesGold Chemistry 2Radulescu Eugen100% (3)