Ps 11034

Ps 11034

Uploaded by

Tanvon MalikCopyright:

Available Formats

Ps 11034

Ps 11034

Uploaded by

Tanvon MalikOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Ps 11034

Ps 11034

Uploaded by

Tanvon MalikCopyright:

Available Formats

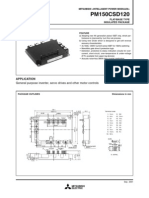

MITSUBISHI

MITSUBISHI

SEMICONDUCTOR

SEMICONDUCTOR

<Application

<Application

Specific

Specific

Intelligent

Intelligent

Power

Power

Module>

Module>

PS11034

PS11034

FLAT-BASE

FLAT-BASE

TYPE

TYPE

INSULATED

INSULATED

TYPE

TYPE

PS11034

INTEGRATED FUNCTIONS AND FEATURES

Converter bridge for 3 phase AC-to-DC power conversion.

3 phase IGBT inverter bridge configured by the latest 3rd.

generation IGBT and diode technology.

Inverter output current capability I O (Note 1):

Type Name Motor Rating IO (100%) IO (150%; 60sec)

7.5Arms

PS11034 0.75 kW/200V AC 5.0Arms

(Note 1) : The inverter output current is assumed to be sinusoidal and the peak current value of each of the

2,

above loading cases is defined as : IOP = IO

TC < 100C

INTEGRATED DRIVE, PROTECTION AND SYSTEM CONTROL FUNCTIONS:

P-Side IGBTs : Drive circuit, high-level-shift circuit, bootstrap circuit supply scheme for Single Control-Power-Source drive, and under voltage (UV) protection.

N-Side IGBTs : Drive circuit, DC-Link current sense and amplifier circuits for overcurrent protection, control-supply under-voltage

protection (UV), and fault output (FO) signaling circuit.

Fault Output : N-side IGBT short circuit (SC), over-current (OC), and control supply under-voltage (UV).

Inverter Analog Current Sense : N-Side IGBT DC-Link Current Sense.

Input Interface : 5V CMOS/TTL compatible, Schmitt Trigger input, and Arm-Shoot-Through interlock protective function.

APPLICATION

Acoustic noise-less 0.75kW/200V AC Class 3 phase inverters, motor control applications,

and motors with built-in small size inverter package

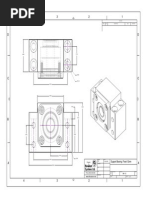

PACKAGE OUTLINES

741

60

16.50.5

Terminals Assignment :

56

7 8 9 10 12 14 16

11 13 15

2.2

50.70.8

4.5

25

15

631

2-R

250.5

4.5

1.2

5.08

30

0.6

21 22 23 24 25 26 27 28 29

30.5

0.6

2-R

40

34

(25.7)

12

0.4

36

1. CBU+

2. CBU

3. CBV+

4. CBV

5. CBW+

6. CBW

7. VD

8. UP

9. VP

10. WP

11. UN

12. VN

13. WN

14. FO

15. Vamp

16. GND

21. P1

22. R

23. S

24. T

25. N1

26. P2

27. U

28. V

29. W

30. N2

4-R3

45.72

8.50.5

(69)

55.5

16.50.5

3.5

Type name,LotNo.

(Fig. 1)

Jan. 2000

MITSUBISHI SEMICONDUCTOR <Application Specific Intelligent Power Module>

PS11034

FLAT-BASE TYPE

INSULATED TYPE

INTERNAL FUNCTIONS BLOCK DIAGRAM

P1

R

S

T

N1

P2

V(amp)

+

Drive circuit

V

W

Drive circuit

Fo Circuit

UV Protection

FO

OC/SC Protection

UP

VP

WP

UN

VN

WN

Input signal conditioning

(Interlock circuit)

VD

Level shifter

UV Protection

N2

GND

(Fig. 2)

MAXIMUM RATINGS (Tj = 25C)

INVERTER PART

Symbol

VCC

Item

Supply voltage

Condition

Applied between P2-N2

VCC(surge) Supply voltage (surge)

Applied between P2-N2, Surge-value

VP or VN Each output IGBT collector-emitter static voltage Applied between P2-U.V.W, U.V.W-N2

VP(S) or

VN(S)

Ic(Icp)

Each output IGBT collector-emitter

switching voltage

Each output IGBT collector current

Applied between P2-U.V.W, U.V.W-N2

TC = 25C, (

) means IC peak value

Ratings

450

Unit

V

500

600

V

V

600

15 (30)

Ratings

800

Unit

V

CONVERTER PART

Symbol

VRRM

Item

Condition

Ea

Repetitive peak reverse voltage

Recommended AC input voltage

220

Vrms

IO

IFSM

DC output current

Surge (non-repetitive) forward current

3 rectifying circuit

1 cycle at 60Hz, peak value non-repetitive

15

150

A

A

I2t

I2t for fusing

Value for one cycle of surge current

93

A 2s

CONTROL PART

Ratings

Unit

VD, VDB

VCIN

Symbol

Supply voltage

Input signal voltage

0.5 ~ 20

0.5 ~ +7.5

V

V

VFO

IFO

Fault output supply voltage

0.5 ~ +7.5

15

V

mA

mA

Iamp

Item

Fault output current

DC-Link IGBT current signal Amp output current

Jan. 2000

MITSUBISHI SEMICONDUCTOR <Application Specific Intelligent Power Module>

PS11034

FLAT-BASE TYPE

INSULATED TYPE

TOTAL SYSTEM

Symbol

Tj

Item

Junction temperature

Tstg

TC

Storage temperature

Module case operating temperature

VISO

Isolation voltage

Condition

Ratings

Unit

(Note 2)

20 ~ +125

(Fig. 3)

40 ~ +125

20 ~ +100

C

C

2500

Vrms

0.98 ~ 1.47

Nm

60 Hz sinusoidal AC applied between all terminals and

the base plate for 1 minute.

Mounting screw: M4

Mounting torque

(Note 2) : The indicated values are specified considering the safe operation of all the parts within the ASIPM. The max. ratings for the ASIPM

power chips (IGBT & FWDi) is Tj < 150.

CASE TEMPERATURE MEASUREMENT POINT

TC

(Fig. 3)

THERMAL RESISTANCE

Symbol

Rth(jc) Q

Rth(jc) F

Rth(jc) FR

Rth(cf)

Condition

Item

Junction to case Thermal

Resistance

Contact Thermal Resistance

Ratings

Unit

Inverter IGBT (1/6)

Min.

Typ.

Max.

2.8

C/W

Inverter FWDi (1/6)

Converter Di (1/6)

3.9

4.8

C/W

C/W

Case to fin thermal, grease applied (1 Module)

0.074

C/W

ELECTRICAL CHARACTERISTICS (Tj = 25C, VD = 15V, V DB = 15V unless otherwise noted)

Symbol

Item

Condition

Tj = 25C, Input = ON, Ic = 15A, VD = VDB = 15V

(Shunt voltage drop not included)

Tj = 25C, IC = 15A

VEC

Collector-emitter saturation

voltage

FWDi forward voltage

VFR

IRRM

Tj = 25C, IFR = 10A

Converter diode voltage

Converter diode reverse current VR = VRRM , Tj = 125C

VCE(sat)

ton

tc(on)

Switching times

toff

tc(off)

trr

FWDi reverse recovery time

1/2 Bridge inductive, Input = 5V 0V

VCC = 300V, IC = 15A, Tj = 125C

VD = 15V, VDB = 15V

Note: ton, toff include delay time of the internal control

circuit.

Short circuit endurance

@VCC 400V, Input = 5V 0V (One-Shot)

(Output, Arm, and Load Short Circuit Modes) 20C Tj (start) 125C, 13.5V VD = VDB 16.5V

Switching SOA

@VCC 400V, Input = 5V 0V, Tj 125C

IC < OC trip level, 13.5V VD = VDB 16.5V

Ratings

Unit

Min.

Typ.

Max.

2.9

2.9

1.5

8

V

mA

0.3

0.6

0.5

1.5

1.0

s

s

1.6

0.5

2.5

1.3

s

s

0.12

No destruction

FO output by protection operation

No destruction

No protecting operation

No FO output

Jan. 2000

MITSUBISHI SEMICONDUCTOR <Application Specific Intelligent Power Module>

PS11034

FLAT-BASE TYPE

INSULATED TYPE

ELECTRICAL CHARACTERISTICS (Tj = 25C, VD = 15V, V DB = 15V unless otherwise noted)

Symbol

Item

Condition

ID

IDB

Vth(on)

Vth(off)

Ri

fPWM

Circuit current (Average)

Circuit current (Average)

Input on threshold voltage

Input off threshold voltage

Input pull-up resistor

PWM input frequency

tdead

Arm shoot-through blocking time

tint

Vamp(100%)

Vamp(200%)

Vamp(250%)

Vamp(0)

OC

tOC

SC

tSC

UVD

UVDr

UVDB

UVDBr

tdV

tFO

IFo(H)

IFo(L)

Input interlock sensing

Inverter DC-Link IGBT current sense voltage

output signal

Inverter DC-Link IGBT current sense voltage

output limit

Over current trip level

Over current delay time

Short circuit trip level

Short circuit delay time

Trip level

Reset level

Supply circuit under

Trip level

voltage protection

Reset level

Delay time

Fault output pulse width

Tj = 25C, VD = 15V, Vin = 5V

Tj = 25C, VD = VDB = 15V, Vin = 5V

Fault output current

Applied between input terminal-inside power supply

T C 100C, Tj 125C

Relates to corresponding inputs

(Note 3)

T C = 20C ~ +100C

Relates to corresponding input (Fig. 6)

IC = IOP(100%)

VD = 15V

Tj = 25C (Fig. 4)

IC = IOP(200%)

VD = 15V

IC = IOP(250%)

(Fig. 4)

IC = 0A

Tj = 25C

(Fig. 5)

Tj = 25C

(Fig. 5)

Tj = 25C

(Fig. 5)

Tj = 25C

(Fig. 5)

T C = Tj = 25C

(Fig. 5)

Tj = 25C

(Note 4)

Open collector output

(Note 4)

Min.

0.8

2.5

Ratings

Typ.

1.4

3.0

50

Max.

50

5

2.0

4.0

15

2.2

1.5

3.0

5.0

14.2

11.0

11.5

10.1

10.6

1.0

100

2.0

4.0

50

17.7

10

30

2

12.0

12.5

10.8

11.3

10

1.8

2.5

5.0

100

25.0

13.0

13.5

11.6

12.1

1

15

ns

V

V

V

mV

A

s

A

s

V

V

V

V

s

ms

A

mA

Unit

mA

mA

V

V

k

kHz

(Note 3) : The dead-time has to be set externally by the CPU; it is not part of the ASIPM internal functions.

(Note 4) : Fault output signaling is given only when the internal OC, SC, & UV protection circuits are activated.

The OC, SC and UV protection (and fault output) operate for the lower arms only. The OC and SC protection Fault output is given

in a pulse format while that of UV protection is maintained throughout the duration of the under-voltage condition.

RECOMMENDED OPERATING CONDITIONS

Ratings

Symbol

Item

Condition

VCC

VD

VDB

VD, VDB

VCIN(ON)

VCIN(OFF)

tdead

TC

fPWM

tXX

Supply voltage

Supply voltage

Supply voltage

Supply voltage ripple

Input on voltage

Input off voltage

Arm shoot-through blocking time

Module case operating temperature

PWM Input frequency

Allowable minimum input on-pulse width

Applied across P2-N2 terminals

Applied between VD-GND

Applied between CBU+ & CBU, CBV+ & CBV, CBW+ & CBW

Applied between UP VP WP UN VN WN and

GND

Relates to corresponding inputs

TC 100C, Tj 125C

Typ.

300

15.0

15.0

Max.

400

16.5

16.5

+1

0.8

5.0

100

15

Unit

V

V

V

V/s

V

V

s

C

kHz

s

Vamp

INVERTER DC-LINK IGBT CURRENT ANALOGUE

SIGNALING OUTPUT (TYPICAL)

Min.

13.5

13.5

1

0

4.0

2.2

VD = 15V

Tj = 25C

Vamp (V)

Vamp (200%)

3

2

Vamp (100%)

1

(Fig. 4)

0

0

200

300

100

Actual Load Peak Current (%), (IC = IO 2)

Jan. 2000

MITSUBISHI SEMICONDUCTOR <Application Specific Intelligent Power Module>

PS11034

FLAT-BASE TYPE

INSULATED TYPE

CURRENT ABNORMALITY PROTECTIVE FUNCTIONS

Protection is achieved by monitoring and filtering the N-side

DC-Bus current. The over-current protection is activated (after allowing a filtering time of 10 s) when the line current reaches

250% of the rated load-current IO (rms). Similarly, the short circuit

protection is activated (after allowing a filtering time of 2 s) when

the line current reaches twice the rated collector-current (IC ).

When a current trip-level is exceeded (OC or SC), all the N-side

IGBTs are intercepted (turned OFF) and a fault-signal is output.

After the fault-signal output duration (1.8 ms - typ.), the interception is Reset at the following OFF input signal. However, since the

fault may be repetitive, it is recommended to stop the system after

the fault-signal is received and check the fault. The trip-level settings described above are summarized in the following figure:

Ic(A)

Short circuit trip level

SC

Over current trip level

OC

Collector current

0

2

10

tw (s)

(Fig. 5)

ARM-SHOOT-THROUGH INTER-LOCK PROTECTIVE FUNCTION

a1

P-Side Input Signal : VCIN(p) ON

b4

a4

N-Side Input Signal : VCIN(n) ON

b1

a3

b2

P-Side IGBT Gate : VGE(p)

0

N-Side IGBT Gate : VGE(n)

a2

b3

(Fig. 6)

Description:

(1) During the ON-State of either of the upper-arm or the lower-arm IGBT, the inter-lock protection circuit blocks any erroneous ON pulses (resulting from input noise) from triggering the other arm IGBT and thus it prevents the arm-shoot-through situation.

(2) When two ON-signals are received for both the upper and the lower arms, the signal received first will be passed to the IGBT and the second signal will be blocked. The second signal will be passed to its corresponding IGBT immediately after the first signal is OFF.

Note: This protective function provides no fault signaling output. The Dead-Time has to be set using the micro-controller (CPU).

Operation:

a1. P-side normal ON-signal P-side IGBT gate turns ON.

a2. N-side erroneous ON-signal N-side IGBT gate remains OFF.

a3. While P-side ON-signal remains P-side IGBT gate remains ON.

a4. N-side normal ON-signal N-side IGBT gate turns ON.

RECOMMENDED I/O INTERFACE CIRCUIT

b1.

b2.

b3.

b4.

N-side normal ON-signal N-side IGBT gate turns ON.

Simultaneous ON-signals P-side IGBT gate remains OFF.

N-side receives OFF-signal N-side IGBT gate turns OFF.

Immediately after (b3) P-side IGBT gate turns ON.

5V

5V

VD(15V)

ASIPM

5.1k

R

CPU

UP,VP,WP,UN,VN,WN

Fo

10k

V(amp)

0.1nF

0.1nF

GND(Logic)

(Fig. 7)

Jan. 2000

You might also like

- DM 103vaDocument2 pagesDM 103vaTanvon Malik100% (1)

- PT6A-42A Wash ProcedureDocument17 pagesPT6A-42A Wash ProcedureLoki Wartooth100% (1)

- Dyonics 25Document4 pagesDyonics 25api-19808945No ratings yet

- Ps22a78 eDocument10 pagesPs22a78 evishwa_001No ratings yet

- Leaflet Delem Profile-W enDocument2 pagesLeaflet Delem Profile-W enTanvon MalikNo ratings yet

- Basic Electrical SafetyDocument25 pagesBasic Electrical Safetyperezes100% (2)

- Turbines, Compressors and Fans - S. M. YahyaDocument170 pagesTurbines, Compressors and Fans - S. M. YahyaGt Varadharajan100% (1)

- Ps 21245Document9 pagesPs 21245pukymottoNo ratings yet

- Air Acond Ps21246 OnduladorDocument10 pagesAir Acond Ps21246 OnduladorJ CorreoNo ratings yet

- PM 150 CSD 120Document7 pagesPM 150 CSD 120elecompinnNo ratings yet

- BTS5215LDocument14 pagesBTS5215LVanny Is AresNo ratings yet

- Ps 21 A 79Document10 pagesPs 21 A 79Omar LeonNo ratings yet

- 04 Spec Sheet PWM Controller ChipDocument16 pages04 Spec Sheet PWM Controller Chipxuanhiendk2No ratings yet

- Mitsubishi Semiconductor Mitsubishi SemiconductorDocument8 pagesMitsubishi Semiconductor Mitsubishi Semiconductoramired2No ratings yet

- Iramx 16 Up 60 ADocument17 pagesIramx 16 Up 60 AJandfor Tansfg ErrottNo ratings yet

- PM20CSJ060Document6 pagesPM20CSJ060Dany Carrasco Ysus TecladosNo ratings yet

- Double Channel High Side Solid State Relay: VND600SPDocument17 pagesDouble Channel High Side Solid State Relay: VND600SPDan EsentherNo ratings yet

- IRAMX16UP60ADocument18 pagesIRAMX16UP60Atheylor1990No ratings yet

- FSBB20CH60: Smart Power ModuleDocument16 pagesFSBB20CH60: Smart Power ModuleDhaka AsasaNo ratings yet

- Transition-Mode PFC Controller: 1 FeaturesDocument17 pagesTransition-Mode PFC Controller: 1 Featuresadriancho66No ratings yet

- Double Channel High Side Solid State RelayDocument18 pagesDouble Channel High Side Solid State RelayDan EsentherNo ratings yet

- VND830MSP: Double Channel High Side DriverDocument18 pagesVND830MSP: Double Channel High Side DriverDan EsentherNo ratings yet

- Irams 06 Up 60 ADocument18 pagesIrams 06 Up 60 AAndré Roberto EvangelistaNo ratings yet

- BTS 410 F2Document15 pagesBTS 410 F2roozbehxoxNo ratings yet

- L 6565Document17 pagesL 6565tatatabuchoNo ratings yet

- 78 S 40Document9 pages78 S 40Luis AlbertoNo ratings yet

- MC 34152Document12 pagesMC 34152dcastrelos2000No ratings yet

- Unisonic Technologies Co., LTD: 30 Amps, 60 Volts N-Channel Power MosfetDocument8 pagesUnisonic Technologies Co., LTD: 30 Amps, 60 Volts N-Channel Power Mosfetperro sNo ratings yet

- VND810MSP: Double Channel High Side DriverDocument18 pagesVND810MSP: Double Channel High Side DriverDan EsentherNo ratings yet

- Pm100cva120 - e IGBT PDFDocument6 pagesPm100cva120 - e IGBT PDFDoDuyBacNo ratings yet

- Infineon BTS6143D DS v01 00 enDocument18 pagesInfineon BTS6143D DS v01 00 enNacer MezghicheNo ratings yet

- L6565Document18 pagesL6565Sergio Daniel BarretoNo ratings yet

- 7378Document19 pages7378Dan EsentherNo ratings yet

- Circuito Integrado TL072 CNDocument16 pagesCircuito Integrado TL072 CNSalvador Francisco Tello OrtízNo ratings yet

- PS21245 eDocument9 pagesPS21245 eTol SirtNo ratings yet

- VN800S VN800PT: High Side DriverDocument21 pagesVN800S VN800PT: High Side DriverDan EsentherNo ratings yet

- LM350 DatasheetDocument12 pagesLM350 DatasheetOmarVelasquezC.No ratings yet

- Three-Terminal Positive Fixed Voltage Regulators: Semiconductor Technical DataDocument16 pagesThree-Terminal Positive Fixed Voltage Regulators: Semiconductor Technical DataBetancur AlejandroNo ratings yet

- Mitsubishi SemiconductorDocument8 pagesMitsubishi Semiconductoredgardo2004No ratings yet

- 7MBR100SD060: PIM/Built-in Converter With Thyristor and Brake (S Series) 600V / 100A / PIMDocument7 pages7MBR100SD060: PIM/Built-in Converter With Thyristor and Brake (S Series) 600V / 100A / PIMPhong PhongNo ratings yet

- Infineon BTS740S2Document15 pagesInfineon BTS740S2dasho1No ratings yet

- M XQSZVDocument10 pagesM XQSZVRoozbeh BahmanyarNo ratings yet

- Mitsubishi Igbt CSTBT Pm150rl1a120 E2Document9 pagesMitsubishi Igbt CSTBT Pm150rl1a120 E2Damiano ZitoNo ratings yet

- 7MBP150RA060: IGBT-IPM R SeriesDocument8 pages7MBP150RA060: IGBT-IPM R SeriesDiego Boczylo JardimNo ratings yet

- TL062, TL062A, TL062B: Low-Power JFET Dual Operational AmplifiersDocument16 pagesTL062, TL062A, TL062B: Low-Power JFET Dual Operational AmplifierswojtektmNo ratings yet

- Quad Smart Power Solid State Relay For Complete H Bridge ConfigurationsDocument20 pagesQuad Smart Power Solid State Relay For Complete H Bridge ConfigurationsDan EsentherNo ratings yet

- Viper 53Document24 pagesViper 53Cadena CesarNo ratings yet

- Uc3842b 3843BDocument10 pagesUc3842b 3843Bbob75No ratings yet

- Double Channel High Side Driver: Type R I VDocument19 pagesDouble Channel High Side Driver: Type R I VDan EsentherNo ratings yet

- 428L2 PDFDocument13 pages428L2 PDFesquisofNo ratings yet

- LTC 1625Document24 pagesLTC 1625Sakura KunNo ratings yet

- Thb7128 InstructionsDocument9 pagesThb7128 InstructionsanhxcoNo ratings yet

- 7MBR35SD120: PIM/Built-in Converter With Thyristor and Brake (S Series) 1200V / 35A / PIMDocument7 pages7MBR35SD120: PIM/Built-in Converter With Thyristor and Brake (S Series) 1200V / 35A / PIMLuis TorresNo ratings yet

- 5V-0.5A Very Low Drop Regulator With Reset: DescriptionDocument6 pages5V-0.5A Very Low Drop Regulator With Reset: DescriptionDan EsentherNo ratings yet

- Fixed Frequency Current Mode PWM Controller: Description Pin ConfigurationDocument11 pagesFixed Frequency Current Mode PWM Controller: Description Pin ConfigurationDong Ho JinNo ratings yet

- Driver Bobina de Encendido VB326SPDocument9 pagesDriver Bobina de Encendido VB326SPteroplasNo ratings yet

- 8205Document16 pages8205sonytinNo ratings yet

- C324G Low Power Quad OpAmpDocument12 pagesC324G Low Power Quad OpAmpwhynot05No ratings yet

- Auips 7111 SDocument15 pagesAuips 7111 SPham LongNo ratings yet

- IGBT MODUL Data Sheet 6MBI 15GS-060Document4 pagesIGBT MODUL Data Sheet 6MBI 15GS-060Anonymous LJ1HbbNo ratings yet

- Aplicacion Note UC3843Document11 pagesAplicacion Note UC3843Luis PapaNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Exercises in Electronics: Operational Amplifier CircuitsFrom EverandExercises in Electronics: Operational Amplifier CircuitsRating: 3 out of 5 stars3/5 (1)

- Micromo Magnetic Encoders: Integral Encoder Series Ie2-512Document2 pagesMicromo Magnetic Encoders: Integral Encoder Series Ie2-512Tanvon MalikNo ratings yet

- Venture Depliants Macchines For Industry - EngDocument9 pagesVenture Depliants Macchines For Industry - EngTanvon MalikNo ratings yet

- Tulip FANRAM 11Manual-CompleteDocument7 pagesTulip FANRAM 11Manual-CompleteTanvon MalikNo ratings yet

- Novakon Novakon Novakon Novakon Systems Ltd. Systems Ltd. Systems Ltd. Systems LTDDocument1 pageNovakon Novakon Novakon Novakon Systems Ltd. Systems Ltd. Systems Ltd. Systems LTDTanvon MalikNo ratings yet

- Novakon Novakon Novakon Novakon Systems Ltd. Systems Ltd. Systems Ltd. Systems LTDDocument1 pageNovakon Novakon Novakon Novakon Systems Ltd. Systems Ltd. Systems Ltd. Systems LTDTanvon MalikNo ratings yet

- G 201 ManualDocument6 pagesG 201 ManualTanvon MalikNo ratings yet

- Novakon Novakon Novakon Novakon Systems Ltd. Systems Ltd. Systems Ltd. Systems LTDDocument1 pageNovakon Novakon Novakon Novakon Systems Ltd. Systems Ltd. Systems Ltd. Systems LTDTanvon MalikNo ratings yet

- Rs23 OverviewDocument2 pagesRs23 OverviewTanvon MalikNo ratings yet

- NEMA 34 RHT Series Stepper MotorsDocument1 pageNEMA 34 RHT Series Stepper MotorsTanvon MalikNo ratings yet

- Novakon Novakon Novakon Novakon Systems Ltd. Systems Ltd. Systems Ltd. Systems LTDDocument1 pageNovakon Novakon Novakon Novakon Systems Ltd. Systems Ltd. Systems Ltd. Systems LTDTanvon MalikNo ratings yet

- rht34 740dDocument1 pagerht34 740dTanvon MalikNo ratings yet

- Delem: Modularity SolutionsDocument2 pagesDelem: Modularity SolutionsTanvon MalikNo ratings yet

- Installing and Configuring The SmoothStepperDocument16 pagesInstalling and Configuring The SmoothStepperTanvon MalikNo ratings yet

- EZ-G540 Installation GuideDocument2 pagesEZ-G540 Installation GuideTanvon MalikNo ratings yet

- Care & Feeding of MachinesDocument36 pagesCare & Feeding of MachinesTanvon MalikNo ratings yet

- ANSI MV Fusesaver Flyer EN PDFDocument2 pagesANSI MV Fusesaver Flyer EN PDFNorng VibolNo ratings yet

- Instruction & Safety Manual: Read Carefully Before Using This FirearmDocument33 pagesInstruction & Safety Manual: Read Carefully Before Using This FirearmSV100% (2)

- Curionics - Brochure A4 - Page WiseDocument4 pagesCurionics - Brochure A4 - Page WiseBalaKrishna BadimelaNo ratings yet

- labVIEW Lab ManualDocument41 pageslabVIEW Lab ManualvertikaNo ratings yet

- PIC32MZDocument718 pagesPIC32MZalecsionNo ratings yet

- Backing Up and Restoring A Hyperion Essbase DatabaseDocument11 pagesBacking Up and Restoring A Hyperion Essbase DatabaseSreedhar ThatipallyNo ratings yet

- Sti DatasheetDocument10 pagesSti DatasheetamrezzatNo ratings yet

- MM 105 001Document18 pagesMM 105 001anshuyadav1223334444No ratings yet

- Ingal Eps Utility Poles Brochure PDFDocument16 pagesIngal Eps Utility Poles Brochure PDFJosue HasbunNo ratings yet

- Anti-Agglomerant Hydrate Inhibitors For Prevention of Hydrate Plugs in Deepwater SystemsDocument7 pagesAnti-Agglomerant Hydrate Inhibitors For Prevention of Hydrate Plugs in Deepwater SystemsThevaruban RagunathanNo ratings yet

- Titan 60maindeckloaderDocument606 pagesTitan 60maindeckloaderdustdevil9916No ratings yet

- ADC Basic ConceptsDocument15 pagesADC Basic ConceptssibNo ratings yet

- Pneudri Maxi & MaxiplusDocument8 pagesPneudri Maxi & Maxiplusantonio timboNo ratings yet

- GTDSMath SpecDocument710 pagesGTDSMath SpecShaneNo ratings yet

- Boiler Energy Audit ManualDocument29 pagesBoiler Energy Audit ManualAnubhav100% (11)

- NJ 5Document3 pagesNJ 5ahmeddamakNo ratings yet

- Applied Termo 122424Document4 pagesApplied Termo 122424rjrahul25No ratings yet

- Secification GeneraleDocument14 pagesSecification GeneraleNic Ric100% (1)

- Manual Bomba Maxbloc - HDDocument9 pagesManual Bomba Maxbloc - HDAnonymous jW9BkgbQmENo ratings yet

- dwf750 Manualul Mașinii de Spălat DaewooDocument50 pagesdwf750 Manualul Mașinii de Spălat DaewooCătălin MatacheNo ratings yet

- UL100-12 UltracellDocument2 pagesUL100-12 UltracellyusufshabanNo ratings yet

- The Effect of Giving To Much Home Work To High School StudentDocument4 pagesThe Effect of Giving To Much Home Work To High School StudentNuk UttagosolNo ratings yet

- Mid Year Form 3 2022Document4 pagesMid Year Form 3 2022HASMUNI BINTI HASSAN MoeNo ratings yet

- Silver Stacie - Q88 PDFDocument9 pagesSilver Stacie - Q88 PDFAks MarinerNo ratings yet

- Stud Details: K.P.Mondal & SonsDocument1 pageStud Details: K.P.Mondal & SonsTanmoy DuttaNo ratings yet

- Elementary Analysis of Two Vehicles in CollisionDocument4 pagesElementary Analysis of Two Vehicles in CollisionVinz Hexon BalangueNo ratings yet