C8051F350

C8051F350

Uploaded by

gigiCopyright:

Available Formats

C8051F350

C8051F350

Uploaded by

gigiCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

C8051F350

C8051F350

Uploaded by

gigiCopyright:

Available Formats

C8051F350

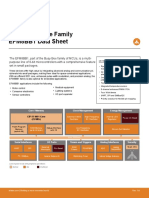

50 MIPS, 8 kB Flash, 24-Bit ADC, 32-Pin Mixed-Signal MCU

Analog Peripherals High-Speed 8051 µC Core

24-Bit ADC - Pipelined instruction architecture; executes 70% of instructions in 1 or 2

- 0.0015% nonlinearity system clocks

- Programmable throughput up to 1 ksps - Up to 50 MIPS throughput with 50 MHz clock

- 8 external inputs; programmable as single-ended or differential - Expanded interrupt handler

- Programmable amplifier gain: 128, 64, 32, 16, 8, 4, 2, 1 Memory

- Data-dependent windowed interrupt generator - 768 bytes data RAM

- Built-in temperature sensor (±3 °C) - 8 kB Flash; in-system programmable in 512 byte sectors (512 bytes are

Two 8-Bit Current DACs reserved)

Comparator Digital Peripherals

- 16 Programmable hysteresis values and response time

- 17 port I/O; all 5 V tolerant

- Configurable to generate interrupts or reset

- Hardware SMBus™ (I2C™ compatible), SPI™, and UART serial ports

- Low current (0.4 µA) available concurrently

Internal Voltage Reference - 16-bit programmable counter array with three capture/compare modules,

VDD Monitor/Brown-out Detector WDT

On-Chip Debug

- 4 general-purpose 16-bit counter/timers

- Realtime clock mode using PCA or timer and external clock source

- On-chip debug circuitry facilitates full speed, non-intrusive in-system

debug (no emulator required) Clock Sources

- Provides breakpoints, single stepping, watchpoints - Internal oscillator: 24.5 MHz, 2% accuracy supports UART operation

- Inspect/modify memory, registers, and stack - External oscillator: Crystal, RC, C, or clock (1 or 2 pin modes)

- Superior performance to emulation systems using ICE-chips, target - 2x clock multiplier to achieve 50 MHz internal clock

pods, and sockets

- Can switch between clock sources on-the-fly

Supply Voltage: 2.7 to 3.6 V

Package

- Typical operating current: 17 mA at 50 MHz

- 32-pin LQFP (lead-free package)

16 µA at 32 kHz

- Typical stop mode current: <0.1 µA Ordering Part Numbers

Temperature Range: –40 to +85 °C - C8051F350-GQ

Digital Power

VDD

GND

Analog 8 kB P0.0

AV+ Power 8 FLASH

AGND

C2D

Debug HW

P0.1

0 256 Byte P P0.2/XTAL1

Port 0

RST/C2CK

Reset 5 SRAM

Latch

0

P0.3/XTAL2

Brown-

1 512 Byte UART D P0.4/TX

POR XRAM r

Out v P0.5/RX

Timer 0,

External

C 1, 2, 3 P0.6/CNVSTR

XTAL1

XTAL2

Oscillator o SFR Bus 3-Chnl

X

B

P0.7

Circuit System PCA/

Clock r WDT

A

CP0 +

CP0+

24.5 MHz 2% R

Internal

Clock

Multiplier

e SMBus CP0A - CP0-

Oscillator

SPI Bus

VREF+

VREF- P1.0

Port 1

VREF Latch

P1.1

P P1.2

1

AIN0 P1.3

AIN1 Offset D P1.4/CP0A

DAC r

AIN2 v P1.5/CP0

A 24-bit 8-bit

AIN3 M Buffer

+

PGA

IDAC0

P1.6/IDAC0

+ ADC0

AIN4 U P1.7/IDAC1

X

AIN5 8-bit

IDAC1

AIN6 Temp C2D

AIN7 Sensor Port 2

P2.0/C2D

Latch

Precision Mixed Signal Copyright © 2005 by Silicon Laboratories 5.5.2005

C8051F350

50 MIPS, 8 kB Flash, 24-Bit ADC, 32-Pin Mixed-Signal MCU

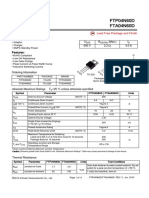

Selected Electrical Specifications

(TA = –40 to +85 C°, VDD = AV+ = 3.0 V, VREF = 2.5 V External, PGA Gain = 1x, MDCLK = 2.4567 MHz,

Decimation Ratio = 1920 unless otherwise specified)

PARAMETER CONDITIONS MIN TYP MAX UNITS

GLOBAL CHARACTERISTICS

Supply Voltage 2.7 3.6 V

Supply Current Clock = 50 MHz 17 mA

(CPU active) Clock = 1 MHz 0.5 mA

Clock = 32 kHz; VDD Monitor Enabled 16 µA

Supply Current Oscillator not running; VDD Monitor 0.1 µA

(shutdown) Disabled

Clock Frequency Range DC 50 MHz

24-BIT A/D CONVERTER

Resolution (no missing codes) 24 bits

Integral Nonlinearity Single-ended Mode ±15 ppm FS

Differential Mode

Offset Error ±5 ppm

Gain Error ±0.002 %

Common Mode Rejection 110 dB

Ratio (CMRR)

Power Supply Rejection, 80 dB

DC

Power Supply Current 230 µA

8-BIT CURRENT-MODE D/A CONVERTERS

Resolution 8 bits

Integral Nonlinearity ±0.5 LSB

Differential Nonlinearity Guaranteed Monotonic ±0.5 ±1 LSB

Package Information C8051F350DK Development Kit

D

D1 MIN NOM MAX

(mm) (mm) (mm)

A - - 1.60

A1 0.05 - 0.15

E1 E A2 1.35 1.40 1.45

b 0.30 0.37 0.45

32 D - 9.00 -

PIN 1 D1 - 7.00 -

IDENTIFIER

1

A2 e - 0.80 -

A E - 9.00 -

A1 E1 - 7.00 -

b e

Precision Mixed Signal Copyright © 2005 by Silicon Laboratories 5.5.2005

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc.

Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders

You might also like

- AEG PS431. Engl PDFDocument88 pagesAEG PS431. Engl PDFÍcaro Viana67% (3)

- Touch Technologies Tutorial Latest VersionDocument315 pagesTouch Technologies Tutorial Latest VersionRoze Galeska100% (1)

- LB 881Document26 pagesLB 881gigi100% (1)

- Principles of Data Conversion System DesignDocument5 pagesPrinciples of Data Conversion System Designbalodhi100% (1)

- C8051F360 ShortDocument2 pagesC8051F360 ShortMazlan Ab RahimNo ratings yet

- 8 K ISP Flash MCU Family: Analog Peripherals High Speed 8051 C CoreDocument234 pages8 K ISP Flash MCU Family: Analog Peripherals High Speed 8051 C Coremorcego151061No ratings yet

- Familia Mcu FlashDocument356 pagesFamilia Mcu FlashsergioNo ratings yet

- 2.0 V, 32/16 KB Flash, Smartclock, 12-Bit Adc: Analog Peripherals Digital I/ODocument270 pages2.0 V, 32/16 KB Flash, Smartclock, 12-Bit Adc: Analog Peripherals Digital I/Owalo91No ratings yet

- ADuC7019 7020 7021 7022 7024 7025 7026 7027 7028 7029Document96 pagesADuC7019 7020 7021 7022 7024 7025 7026 7027 7028 7029Suma SureshNo ratings yet

- C 8051 F 310/1/2/3/4/5/6/7Document228 pagesC 8051 F 310/1/2/3/4/5/6/7vivek2585No ratings yet

- For New Designs: C8051F70x/71xDocument307 pagesFor New Designs: C8051F70x/71xSarah Joy ManimtimNo ratings yet

- EFM8 Busy Bee Family EFM8BB1 Reference ManualDocument231 pagesEFM8 Busy Bee Family EFM8BB1 Reference ManualFrancesco MenichelliNo ratings yet

- Si1000 DatasheetDocument372 pagesSi1000 Datasheety lNo ratings yet

- C8051F38x Pages 1Document1 pageC8051F38x Pages 1lingeshtjNo ratings yet

- InfoI Tercer Parcial ResueltoDocument454 pagesInfoI Tercer Parcial ResueltoRodrigo DíazNo ratings yet

- Si 1000Document382 pagesSi 1000GunaNo ratings yet

- PIC24HJ128GP502Document390 pagesPIC24HJ128GP502Shaun Van HeerdenNo ratings yet

- Aduc7026: Preliminary Technical DataDocument16 pagesAduc7026: Preliminary Technical DataaishwaryaNo ratings yet

- Datasheet C8051FDocument170 pagesDatasheet C8051FEmmanuel Mariano GómezNo ratings yet

- PIC16 (L) F1526/7: 64-Pin Flash Microcontrollers With XLP TechnologyDocument373 pagesPIC16 (L) F1526/7: 64-Pin Flash Microcontrollers With XLP TechnologyCristian MentesanaNo ratings yet

- 70283k PDFDocument330 pages70283k PDFJose Daniel Rodriguez100% (1)

- C8051F12x 13x PDFDocument350 pagesC8051F12x 13x PDFNARENDRASINH DABHINo ratings yet

- PIC16F1713Document450 pagesPIC16F1713Динко КънчевNo ratings yet

- dspic33fj32gp204Document300 pagesdspic33fj32gp204ghadaabdelli2No ratings yet

- Pic12f1571 PDFDocument334 pagesPic12f1571 PDFazuanr830No ratings yet

- Vortex86DX A9121 Data Sheet V200 BF PDFDocument37 pagesVortex86DX A9121 Data Sheet V200 BF PDFXaoc KabataNo ratings yet

- PIC16F1717Document486 pagesPIC16F1717angel.fonsecaNo ratings yet

- PIC24F16KL402 Family Data Sheet DS30001037DDocument264 pagesPIC24F16KL402 Family Data Sheet DS30001037DDaniNo ratings yet

- Pic16f1717 Datasheet PDFDocument483 pagesPic16f1717 Datasheet PDFShyam Thillainathan0% (1)

- Pic16 (L) F15089 PDFDocument418 pagesPic16 (L) F15089 PDFWarr SteelNo ratings yet

- STM32FEBKC6T6Document67 pagesSTM32FEBKC6T6Mazhar SyedNo ratings yet

- MSPM 0 G 3507Document96 pagesMSPM 0 G 3507Saurav AvachatNo ratings yet

- LPC82XDocument85 pagesLPC82Xb06260626No ratings yet

- Silicon Labs C805CCXXX231 GQ DataDocument146 pagesSilicon Labs C805CCXXX231 GQ DatasikeshkkNo ratings yet

- Datasheet 16F1938 PDFDocument488 pagesDatasheet 16F1938 PDFAnonymous ZMx8heNo ratings yet

- PIC16F753/HV753: 14/16-Pin, Flash-Based 8-Bit CMOS MicrocontrollersDocument230 pagesPIC16F753/HV753: 14/16-Pin, Flash-Based 8-Bit CMOS MicrocontrollersjamorNo ratings yet

- Chip Data Sheet (Signal Generator)Document278 pagesChip Data Sheet (Signal Generator)lokesh charangNo ratings yet

- Samsung CMOS CardDocument2 pagesSamsung CMOS CardBudau RolandNo ratings yet

- ADuC845 7 8 - ADocument108 pagesADuC845 7 8 - Aapi-3736461No ratings yet

- PIC16F1788/9: 8-Bit Advanced Analog Flash MicrocontrollerDocument474 pagesPIC16F1788/9: 8-Bit Advanced Analog Flash MicrocontrollerProljece123No ratings yet

- LPC82XDocument82 pagesLPC82XAndrés VallejoNo ratings yet

- ADI ADuC7060 - 7061 Datasheet - Low-Power Precision Analog Microcontroller, Dual Sigma-Delta ADCs, Flash EE, ARM7TDDMIDocument108 pagesADI ADuC7060 - 7061 Datasheet - Low-Power Precision Analog Microcontroller, Dual Sigma-Delta ADCs, Flash EE, ARM7TDDMIJim GunterNo ratings yet

- Aduc7060 7061 7062Document100 pagesAduc7060 7061 7062Aaron TeterNo ratings yet

- LPC11U6XDocument97 pagesLPC11U6XDenes MarschalkoNo ratings yet

- Efm8lb1 DatasheetDocument77 pagesEfm8lb1 DatasheetJakieNo ratings yet

- Single-Chip 8-Bit Microcontroller: Integrated CircuitsDocument24 pagesSingle-Chip 8-Bit Microcontroller: Integrated CircuitsJuan Carlos CrespoNo ratings yet

- Atmel 6500 32 Bit Cortex M3 Microcontroller SAM3S4 SAM3S2 SAM3S1 DatasheetDocument1,113 pagesAtmel 6500 32 Bit Cortex M3 Microcontroller SAM3S4 SAM3S2 SAM3S1 DatasheetJorge Luis Pantoja HoyosNo ratings yet

- 1729 Psoc 3 Cy8c38 Programmable System-On-Chip DatasheetDocument141 pages1729 Psoc 3 Cy8c38 Programmable System-On-Chip DatasheetKamal MehraNo ratings yet

- Silicon Labs Efm8ub20f64g B QFP48R - C2053313Document57 pagesSilicon Labs Efm8ub20f64g B QFP48R - C2053313TNo ratings yet

- VRC 4172 PBDocument2 pagesVRC 4172 PBAndrej RadulovicNo ratings yet

- DSPIC DatasheetDocument386 pagesDSPIC DatasheetRojan BhattaraiNo ratings yet

- PIC16F1509Document401 pagesPIC16F1509avefenix586No ratings yet

- Data Sheet Pic32mx250f128bDocument328 pagesData Sheet Pic32mx250f128bMarlet MeléndezNo ratings yet

- Keyboard and Embedded Controller For Notebook PC: Product FeaturesDocument10 pagesKeyboard and Embedded Controller For Notebook PC: Product FeaturesgercoralNo ratings yet

- Pic32cm Mc00 Family Data Sheet Ds60001638dDocument990 pagesPic32cm Mc00 Family Data Sheet Ds60001638dDanny VillanuevaNo ratings yet

- PIC16F145x PDFDocument404 pagesPIC16F145x PDFArsalan88No ratings yet

- ADuC845 847 848Document108 pagesADuC845 847 848Tim BeckNo ratings yet

- C8051F99x PDFDocument325 pagesC8051F99x PDFPu DuanNo ratings yet

- Aduc845 847 848Document109 pagesAduc845 847 848clkent2022No ratings yet

- Efm8lb1 RMDocument394 pagesEfm8lb1 RMlingNo ratings yet

- Efm8bb1 DatasheetDocument57 pagesEfm8bb1 DatasheetManuel Jesus Delgado LaraNo ratings yet

- Efm8bb10f8g-A-Qfn20r - 3 - 1Document3 pagesEfm8bb10f8g-A-Qfn20r - 3 - 1iet mitNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- Condensatoare MLCC-1837944Document130 pagesCondensatoare MLCC-1837944gigiNo ratings yet

- Leaflet TSU9600 EU A4 PDFDocument2 pagesLeaflet TSU9600 EU A4 PDFgigiNo ratings yet

- Level 2 Module A Advanced ProntoEdit1Document51 pagesLevel 2 Module A Advanced ProntoEdit1gigiNo ratings yet

- Phase Detector PatentDocument11 pagesPhase Detector PatentgigiNo ratings yet

- HOME Product Information SMPS SMPS For LCD TV: Input ConditionDocument3 pagesHOME Product Information SMPS SMPS For LCD TV: Input ConditiongigiNo ratings yet

- 1 Freq Effects in AmplifiersDocument8 pages1 Freq Effects in AmplifiersgigiNo ratings yet

- Audiaflex Digital Audio Platform: FeaturesDocument2 pagesAudiaflex Digital Audio Platform: FeaturesgigiNo ratings yet

- D3000 92000 PDFDocument2 pagesD3000 92000 PDFgigiNo ratings yet

- FTP04N60D Fta04n60dDocument9 pagesFTP04N60D Fta04n60dgigiNo ratings yet

- Carte Tehnica UPS-uri Powertronix Mizar enDocument13 pagesCarte Tehnica UPS-uri Powertronix Mizar engigiNo ratings yet

- 4CW30000ADocument9 pages4CW30000AgigiNo ratings yet

- Um Inv222 enDocument21 pagesUm Inv222 enŽarko MočnikNo ratings yet

- 6103 Service Manual PDFDocument65 pages6103 Service Manual PDFJorgeLuisUriarteNo ratings yet

- Shunt-Based, 200-A Peak Current Measurement Reference Design Using Reinforced Isolation AmplifierDocument27 pagesShunt-Based, 200-A Peak Current Measurement Reference Design Using Reinforced Isolation AmplifiergofererNo ratings yet

- M64894FP/GP: Mitsubishi Ic (TV)Document9 pagesM64894FP/GP: Mitsubishi Ic (TV)Julio Rafael GamboaNo ratings yet

- Jaes V52 3 All PDFDocument220 pagesJaes V52 3 All PDFtimosp1973No ratings yet

- Is SCC 2024 Advance ProgramDocument79 pagesIs SCC 2024 Advance ProgramIrvingNo ratings yet

- Module 1 StudentsDocument59 pagesModule 1 StudentsMahesh M P NairNo ratings yet

- Microconverter, Multichannel 12-Bit Adc With Embedded Flash McuDocument57 pagesMicroconverter, Multichannel 12-Bit Adc With Embedded Flash McubtanmayNo ratings yet

- Instant download Circuits Signals and Systems for Bioengineers 3rd Edition John Semmlow pdf all chapterDocument55 pagesInstant download Circuits Signals and Systems for Bioengineers 3rd Edition John Semmlow pdf all chapteramusodowenct100% (1)

- Chapter 12 - ADC TestingDocument87 pagesChapter 12 - ADC TestingMonal Bhoyar100% (1)

- CT 3477saDocument2 pagesCT 3477sasudipta_kolNo ratings yet

- Differential/Single-Ended Input, Dual 2 MSPS, 12-Bit, 3-Channel SAR ADC AD7266Document28 pagesDifferential/Single-Ended Input, Dual 2 MSPS, 12-Bit, 3-Channel SAR ADC AD7266Leonel LizamaNo ratings yet

- MI0802 Datasheet v1.0.1Document16 pagesMI0802 Datasheet v1.0.1tffzeldarNo ratings yet

- Wheel Speed SensorsDocument7 pagesWheel Speed SensorsJude MakobaNo ratings yet

- A Brief History of Digital ShakersDocument5 pagesA Brief History of Digital ShakersCharles HyndmanNo ratings yet

- MLX90360 Datasheet MelexisDocument35 pagesMLX90360 Datasheet MelexissdfsdfNo ratings yet

- Analog Sensor Conditioning Circuits - An Overview AN990Document16 pagesAnalog Sensor Conditioning Circuits - An Overview AN990thietdaucongNo ratings yet

- EHTC O&M-edn PDFDocument24 pagesEHTC O&M-edn PDFprasanta_bbsr100% (1)

- F MC-16F MB90220 Series: 16-Bit Proprietary MicrocontrollerDocument105 pagesF MC-16F MB90220 Series: 16-Bit Proprietary MicrocontrollerTriman TelaumbanuaNo ratings yet

- SpecLab ManualDocument113 pagesSpecLab ManualJim CorinnaNo ratings yet

- ATJ2135Document111 pagesATJ2135souravsonar1997No ratings yet

- 1997-04 HP JournalDocument112 pages1997-04 HP JournalElizabeth WilliamsNo ratings yet

- Instruction Manual 2301E Speed Controller Simulator KitDocument24 pagesInstruction Manual 2301E Speed Controller Simulator Kityityizhen22No ratings yet

- ES8388 User GuideDocument28 pagesES8388 User Guidetl072cNo ratings yet

- Lesson 7 Pulse ModulationDocument38 pagesLesson 7 Pulse Modulationnelsonnats91No ratings yet

- 24-Bit, 4-Channel Simultaneous Sampling 1.5 MSPS Precision Alias Free ADCDocument86 pages24-Bit, 4-Channel Simultaneous Sampling 1.5 MSPS Precision Alias Free ADCAndres Alejandro JaraNo ratings yet

- B 115 BDocument121 pagesB 115 BPetrica Dan DinuNo ratings yet