Vlsi Syllabus

Uploaded by

rekhayadavVlsi Syllabus

Uploaded by

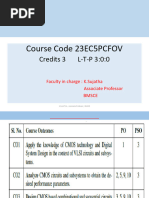

rekhayadavECE407B VLSI DESIGN

B. Tech Semester –VII (ECE, AEI, EEE)

L T P Credits Class Work : 25 Marks

3 1 - 4 Theory : 75 Marks

Total : 100 Marks

Duration of Exam. : 3 Hrs.

COURSE OBJECTIVES:

To understand the steps involved in IC fabrication

To study basic electrical properties of MOS &BIOS circuits.

To understand VLSI circuit design processes representations of stick diagram &layout diagram.

UNIT I

INTRODUCTION:

Evolution of VLSI, Moore’s Law, MOS transistor theory – MOS structure, enhancement & depletion transistor, Threshold voltage, MOS device

design equations, Body Effect, Channel length modulation, Mos Transistor Trans conductance and output conductance.

MOS FABRICATION:

Crystal Growth, wafer preparation, epitaxy, oxidation, lithography, etching, diffusion, deposition, ion-implantation, metallization, Fabrication

Process: nMOS, CMOS (n-well, p-well, twin-tub, silicon on insulator, 3-D CMOS, MOS capacitance dynamic behavior, sub-micron MOS

transistors- related effects.

UNIT II

MOS INVERTER:

Introduction, nMOS inverter: resisive load, enhancement load, depletion load, determination of pull-up to pull-down ratio for an nMOS inverter

driven by another nMOS inverter. CMOS inverter: DC characteristics, circuit model, latch up.

CMOS DESIGN:

Gate Logic: inverter, nand gate, nor gate. Ratioed logic, pseudo NMOS logic, DCVSL Logic, Switch Logic: pass transistor and transmission

gate, dynamic logic, charge sharing logic, domino logic. Combination logic: Parity generator, multiplexer. Sequential logic: two phase clocking,

memory-latches and registers, setup and hold time violations, causes ,effects and remedies.

UNIT III

MOS circuit Design :

MOS layer, stick diagram: nMOS Design style, CMOS design style, design rules and layout: lambda based design rule, layer representation,

contact cuts, double metal MOS process rules, CMOS lambda based design rules.

SCALING OF MOS CIRCUITS:

Scaling models and scaling factors for device parameters, limitations of scaling: substrate doping, limits of miniaturization, limit of interconnect

and contact resistance.

UNIT IV

CIRCUIT CHARACTERIZATION AND PERFORMANCE ESTIMATION:

Sheet resistance, resistance estimation, capacitance estimation, inductance, switching characteristic, propagation delays, CMOS gate

transistor sizing, power dissipation: static and dynamics.

SUB-DESIGN PROCESS:

Design of an ALU subsystem: 4-bit shifter, barrel shifters, logarithmic shifters.Adders – ripple carry, Manchester carry, carry bypass, carry

select linear, carry select square root, carry look ahead, tree and domino adder .Multiplier – binary , array, carry save, Wallace

tree,Programmable logic array, random access memory, binary counter.

Text Books :

1. D.A.Pucknell and K. Eshraghian, “Basic VLSI Design”

2. Weste and Eshrighian, “Principle of CMOS VLSI Design” Pearson Education, 2001

Reference Books:

1. S. M. Kang, Y. Lebiebici, “CMOS digital integrated circuits analysis & design” TMH, 3rd Edition.

2. Rabaey, “Introduction of digital integration circuit”.

COURSE OUTCOMES:

Ability to calculate electrical properties of MOS circuits

Ability to design various gates, adders, Multipliers, Memories, using stick diagrams, layouts.

NOTE: In the Semester examination, the examiner will set 08 questions in all selecting two from each unit. The candidates will be required to

attempt five questions in all, atleast one from each unit. All questions carry equal marks.

You might also like

- VOLVO EC220D LR EC220DLR EXCAVATOR Service Repair Manual PDFNo ratings yetVOLVO EC220D LR EC220DLR EXCAVATOR Service Repair Manual PDF17 pages

- Fundamentals of CMOS VLSI (Complete Notes) PDFNo ratings yetFundamentals of CMOS VLSI (Complete Notes) PDF214 pages

- ME - Detailed Syllabus - 2016-17 OnwardsNo ratings yetME - Detailed Syllabus - 2016-17 Onwards24 pages

- HICET - Department of Electronics and Communication EngineeringNo ratings yetHICET - Department of Electronics and Communication Engineering1 page

- EC8095-VLSI Design - 01 - by WWW - LearnEngineering.inNo ratings yetEC8095-VLSI Design - 01 - by WWW - LearnEngineering.in134 pages

- VTU - MTECH - VLSI Design& Embedded Systems Syllabus - RevisedNo ratings yetVTU - MTECH - VLSI Design& Embedded Systems Syllabus - Revised37 pages

- Sri Ramakrishna Engineering College: 20ec214 & Digital Cmos Vlsi CircuitsNo ratings yetSri Ramakrishna Engineering College: 20ec214 & Digital Cmos Vlsi Circuits122 pages

- Analog & Digital VLSI Design Handout - RevisedNo ratings yetAnalog & Digital VLSI Design Handout - Revised3 pages

- School of Electronics Devi Ahilya University, Indore: Course PlanNo ratings yetSchool of Electronics Devi Ahilya University, Indore: Course Plan3 pages

- Ece-V-fundamentals of Cmos Vlsi (10ec56) - Notes0% (1)Ece-V-fundamentals of Cmos Vlsi (10ec56) - Notes214 pages

- Cmos Vlsi Design - 2019 Syllabus, Course OutcomesNo ratings yetCmos Vlsi Design - 2019 Syllabus, Course Outcomes1 page

- Semester 1: 1. Course Structure and Scheme of Evaluation (Semester-Wise, Along With Curriculum Details)No ratings yetSemester 1: 1. Course Structure and Scheme of Evaluation (Semester-Wise, Along With Curriculum Details)19 pages

- Ece5015 Digital-Ic-Design Eth 1.0 40 Ece5015No ratings yetEce5015 Digital-Ic-Design Eth 1.0 40 Ece50152 pages

- FALL WIN SEM (2023-24) ECE5003 ETH AP2023243000139 Reference Material I 08-Sep-2023 ECE5003 CMOS Digital IC Design 1No ratings yetFALL WIN SEM (2023-24) ECE5003 ETH AP2023243000139 Reference Material I 08-Sep-2023 ECE5003 CMOS Digital IC Design 12 pages

- Bece303l Vlsi-system-Design TH 1.0 0 Bece303l-2No ratings yetBece303l Vlsi-system-Design TH 1.0 0 Bece303l-23 pages

- Damage Mechanics in Metal Forming: Advanced Modeling and Numerical SimulationFrom EverandDamage Mechanics in Metal Forming: Advanced Modeling and Numerical Simulation4/5 (1)

- IOM - Operating Procedure For Ball and Tube MillNo ratings yetIOM - Operating Procedure For Ball and Tube Mill5 pages

- Commercial Operation of 282 MW Pakpattan Hydropower Plant in Punjab PakistanNo ratings yetCommercial Operation of 282 MW Pakpattan Hydropower Plant in Punjab Pakistan4 pages

- Make The Smartpic Serial Programmer: Feature Article100% (1)Make The Smartpic Serial Programmer: Feature Article5 pages

- Critikon Dinamap Compact - Service Manual 2No ratings yetCritikon Dinamap Compact - Service Manual 278 pages

- 370 ZXM6-NHLD120 166 - 1755×1038 (30×20) - 350-370W - 350mm - ENo ratings yet370 ZXM6-NHLD120 166 - 1755×1038 (30×20) - 350-370W - 350mm - E2 pages

- Design and Construction of An Electric Arc WeldingNo ratings yetDesign and Construction of An Electric Arc Welding7 pages

- Acm Interface Tst6621: Acm Interface For Tkt66Xxc Central Battery UnitsNo ratings yetAcm Interface Tst6621: Acm Interface For Tkt66Xxc Central Battery Units3 pages