Schematic Diagram VC-910

Schematic Diagram VC-910

Uploaded by

api-3702225Copyright:

Available Formats

Schematic Diagram VC-910

Schematic Diagram VC-910

Uploaded by

api-3702225Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Schematic Diagram VC-910

Schematic Diagram VC-910

Uploaded by

api-3702225Copyright:

Available Formats

5 4 3 2 1

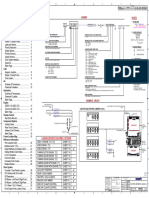

Teco_V862 Version Document

--------------------------------------------------------------------

Main Features:

D D

1. System: ZR36862+16M SDRAM + 8M FLASH

2. Audio: 2ch Audio DAC CS4334 for 2ch out only

3. Motor Driver: AM5888S/AT5669

4. Supported OPUs: SANYO DV342/502W

C Notes: C

1.Assembly Note (See comments in every schematics page, and also see the

implementation field for each component)

B B

TECOBEST TECHNOLOGY

A

TB_V862 A

Title

Version Document

Size Document Number Rev

V1.2

Date: Saturday, May 28, 2005 Sheet 1 of 6

5 4 3 2 1

PDF created with pdfFactory Pro trial version www.pdffactory.com

5 4 3 2 1

Notes:

1. Pin105 to pin203 of ZR36862/8 is 5V & 3.3V tolerant both.

2. ZR36868 is used for 6 or 8 CH audio out application.

ZR36862 is used for 2 CH audio out application, and pin111/112 could be used as GPCIO.

SPDL_SENS+

SPDL_SENS-

MD_DVD

DVD_LD

MD_CD

CD_LD

RFD

RFC

RFE

RFB

RFA

RFF

VC

R102 FB101 220Z

TRACK_S R128 51K 0R DSPVCC33

TRACK_S

SLED_S SLED_S R105 30K SLED_PWM R115 100K

D SPINDLE_S SPINDLE_S R104 15K SPINDLE_PWM + D

FOCUS_S FOCUS_S R127 43K FOCUS_PWM R101 C121 C122

[51K] 20K 1% 0.1uF 100uF/16V C113 L102

C103 VDDAFE

0.1uF

C104 C105 C101 C102 NM NM

HOMESW

1nF 1nF 27nF 22nF [220pF] [2.7uH] R113

VDDPWM FB102 220Z C114 OSCIN

CLOSE

OPEN

22pF

CD/DVD

OUTSW

75R

DRVSB

INSW

TP1 DUPRD0 +

RD0

for DOWN_LOAD TP1 DUPTD0 1nF C110 C119 C120 Y101 R112

TD0 VDDPWM

0.1uF 220uF/10V 27.000MHz 220K

CLOSE

TP1 DUPRD1 Assemble C113&L102

OPEN

RD1

RFD

RFC

RFB

RFA

TP1 DUPTD1

TD1 when Y101 assemble

CD/DVD

1nF C109

OUTSW

DRVSB

RF

RFINN

Third overtone Crystal

RFINP

IRRCV

INSW

for HYPER_TERMINAL IRRCV

FPC_CLK R129

FPC_CLK FPC_DOUT 75R

FPC_DOUT

DSPVCC18

VDDDAC FB106 220Z C115

DSPVCC33 DSPVCC33

OSCOUT

22pF

+ C124

208

207

206

205

204

203

202

201

200

199

198

197

196

195

194

193

192

191

190

189

188

187

186

185

184

183

182

181

180

179

178

177

176

175

174

173

172

171

170

169

168

167

166

165

164

163

162

161

160

159

158

157

C123 100uF/16V 1 PH1

.

U101A 0.1uF

VDDPWM

GNDPWM

AGNDREF

RESOUT

F

GPCIO[47]/SSCCLK

IDGPCIO[7]/SPINDLEPULSE

IDGPCIO[6]/SLEDPULSE

VDD-IP

GNDP

VDDP

VBGAP

K

E

RFP

GPCIO[16]/SSCTXD

GNDC

VDDC

DVD_LD

CD_LD

DVD_MD

CD_MD

VC

AGND

D

H

C

AVDD

SVDD

RFN

J

G

GPCIO[38]/DUPTD1

GPCIO[37]/DUPRD1

GPCIO[36]/DUPTD0

GPCIO[35]/DUPRD0

GPCIO[41]/PWMCO[0]

IDGPCIO[4]/PWMCO[6]

GPCIO[46]/PWMCO[5]

GPCIO[45]/PWMCO[4]

GPCIO[44]/PWMCO[3]

GPCIO[43]/PWMCO[2]

ICGPCIO[7]

ICGPCIO[6]

IDGPCIO[3]

ICGPCIO[5]

ICGPCIO[4]

GPCIO[32]

AGND1

AVDD1

MARK5

.

Use it to connect the shell of the crystal to ground.

FB103 220Z

DSPVCC18

1

C178 C116 + C117

0.1uF 1nF 100uF/16V

FPC_STB 1 156

FPC_STB SSCRXD/GPCIO[17] GNDDACBS2 R106 392R 1%

2 155

MEMCS#[1]/GPCIO[18] GNDDACP

3 154

MEMAD15 4 VDDP RSET 153

MEMAD16 MEMAD[15] C/B/U C_B_U

5 152

MEMAD14 MEMAD[16] VDDDAC

6 151

MEMAD13 MEMAD[14] Y/R/V Y_R_V

7 150

C MEMAD12 MEMAD[13] CVBS/C CVBS_C C

8 149

MEMDA15 9 MEMAD[12]/PLLCFGA

MEMDA[15]

ZR36862 VDDDAC

CVBS/G/Y

148

CVBS_G_Y

MEMAD11 10 147

MEMDA7 MEMAD[11]/PLLCFGP Y/C DSPVCC33

11 146

MEMDA[7] GNDDACD

12 145

MEMAD10 GNDP GNDDACD OSCIN R111 R110 R109 R108

13 144

MEMDA14 14 MEMAD[10] GCLK 143 OSCOUT VGND 75R 1% 75R 1% 75R 1% 75R 1%

MEMAD9 MEMDA[14] XO VDDA

15 142

MEMDA6 MEMAD[9] VDDA RESET R120

16 141

MEMAD8 MEMDA[6] RESET# 10K

17 140

MEMDA13 MEMAD[8] GNDA C108

18 139 +

MEMDA[13] GNDP

MEMDA5 19 138 10uF/16V VGND

MEMDA[5] VDD RESET

20 137 RESET

MEMAD[20]/GPCIO[19]/MEMCS#[2] IDGPCIO[2]

21 136 R114

3

MEMDA12 VDDP GPCIO[31] 100

22 135

MEMDA[12] DJTCK/ICGPCIO[3]/VID[0]

MEMWR- 23 134 Q101 1

MEMWR- MEMDA4 24 MEMWR# DJTDO/GPCIO[30]/VID[1] 133 MUTEC 9014

2

MEMDA[4] DJTDI/GPCIO[29]/VID[2]

25 132

VDDC DJTMS/GPCIO[28]/VID[3]

2

MEMDA11 26 131 C125 D101 R116

MEMDA3 MEMDA[11] VDDC 0.1uF LL4148 10K

27 130

MEMAD19 MEMDA[3] GNDC FS3

28 129

29 MEMAD[19]/PLLSEL DJTCK2/ICETCK/GPCIO[27]/VID[4] 128 FS2 FS3

MEMDA10 GNDC DJTDO2/ICETDO/IDGPCIO[1]/VID[5] FS1 FS2

1

30 127

MEMAD18 MEMDA[10] DJTDI2/ICETDI/ICGPCIO[2]/VID[6] FS1

31 126

MEMAD[18] DJTMS2/ICETMS/GPCIO[26]/VID[7]

32 125

MEMDA2 GNDP VDDP

33

MEMDA[2] COSYNC/CJTMS/ICGPCIO[1]/VCLKx2

124 TBR Huang fu kuan 2005/05/24

RAMDAT10

RAMDAT12

RAMDAT13

RAMDAT15

RAMADD4

RAMADD6

RAMADD7

RAMADD8

RAMADD9

MEMAD17 34 123

RAMDAT8

RAMDAT9

RAMDQM

RAMDAT11

RAMDAT14

RAMADD5

MEMDA9 MEMAD[17] GNDP HSYNC U102

35 122

MEMAD7 MEMDA[9] CJTDO/GPCIO[25]/HSYNC VSYNC HSYNC

36 121

PCLK

MEMDA1 MEMAD[7] CJTDI/GPCIO[24]/VSYNC VSYNC

37 120

MEMAD6 MEMDA[1] CJTCK/GPCIO[23]/AIN

38 119

MEMDA8 39 MEMAD[6] VDDP-A2 118 IAMCLK R117 33R AMCLK

MEMAD5 MEMDA[8] AMCLK AMCLK

40 117

MEMAD[5] GNDP-A2 IABCLK R118 33R ABCLK

41 116

MEMDA0 VDDP ABCLK R103 33R ALRCLK ABCLK

42 115

MEMDA[15:0] MEMDA[0] ALRCLK ALRCLK

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

MEMAD4 43 114

MEMRD- 44 MEMAD[4] GPAIO 113 IAOUT0 R190 33R AOUT0

MEMRD- MEMAD3 MEMRD# AOUT[0] AOUT0

45 112

UDQM

VSS

CKE

CLK

VSS

NC

NC

VDDQ

VSSQ

VDDQ

VSSQ

A4

A5

A6

A7

A8

A9

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

MEMAD2 MEMAD[3] GPCIO[22]/AOUT[1]

46 111

MEMCS0- MEMAD[2] GPCIO[21]/AOUT[2] SPDIF

47 110

MEMCS0- MEMCS#[0] SPDIF SPDIF

MEMAD1 48 109 SDRAM speed <=7ns

B MEMAD[1]/BOOTSEL2 IDGPCIO[0] B

MEMAD[19:0]

MEMAD0 49

MEMAD[0]/BOOTSEL1 ICGPCIO[0]

108 K4S161622C-TC/L70

50 107

GNDP GNDP

A10/AP

51 106

LDQM

VDDQ

VDDQ

VSSQ

VSSQ

VDD-IP CPUNMI/GPCIO[20]

RAMCS#[0]/RAMBA1

52 105

VDD

VDD

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

RAS

CAS

VDDP VDDP

WE

CS

BA

A3

A2

A1

A0

DSPVCC33

RAMADD[10]

RAMADD[11]

RAMDAT[10]

RAMDAT[11]

RAMDAT[12]

RAMDAT[13]

RAMDAT[14]

RAMDAT[15]

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

RAMADD[4]

RAMADD[3]

RAMADD[5]

RAMADD[2]

RAMADD[6]

RAMADD[1]

RAMADD[7]

RAMADD[0]

RAMADD[8]

RAMADD[9]

RAMCS#[1]

RAMDAT[8]

RAMDAT[7]

RAMDAT[9]

RAMDAT[6]

RAMDAT[5]

RAMDAT[4]

RAMDAT[3]

RAMDAT[2]

RAMDAT[1]

RAMDAT[0]

9

8

7

6

5

4

3

2

1

R122

GNDPCLK

RAMRAS#

RAMCAS#

VDDPCLK

RAMBA[0]

RAMDQM

RAMWE#

NM

[1K] MARK6

GNDC

GNDC

GNDP

GNDP

GNDP

GNDP

GNDP

VDDC

VDDC

VDDP

VDDP

VDDP

VDDP

VDDP

PCLK

RAMADD10

1

RAMADD3

RAMADD1

RAMADD0

RAMDAT7

RAMDAT6

RAMDAT5

RAMDAT3

RAMDAT2

RAMDAT0

RAMDQM

RAMADD2

RAMRAS-

RAMCAS-

RAMDAT4

RAMDAT1

RAMCS0-

RAMWE-

100

101

102

103

104

1

2

RAMBA

53

54

55

56

57

58

59

60

61

62

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

R125 R126

4.7K 4.7K

JP102

NM

[BOOTSEL1]

DSPVCC33

RAMADD10

RAMDAT10

RAMDAT11

RAMDAT12

RAMDAT13

RAMDAT14

RAMDAT15

RAMADD4

RAMADD3

RAMADD5

RAMADD2

RAMADD1

RAMADD7

RAMADD0

RAMADD8

RAMDAT7

RAMDAT9

RAMDAT6

RAMDAT5

RAMDAT3

RAMDAT2

RAMDAT0

RAMDQM

RAMADD6

RAMADD9

RAMCS0-

RAMDAT8

RAMDAT4

RAMDAT1

C152 C153 C154

IPCLK

RAMWE-

RAMRAS-

RAMCAS-

RAMBA

NMI + C158 0.1uF 0.1uF 0.1uF

MODE: Play Download 47uF/16V

JP102: Open Short R119

4.7K

R123

PCLK

56R

C106

NM

[5pF]

DSPVCC33 DSPVCC33

A C130 C131 C133 C134 C135 C136 C137 C138 C139 C140 A

10nF 10nF 10nF 10nF 10nF 10nF 10nF 10nF 10nF 10nF

PCB layout guy: please put these bypass capacitors close to main chip

DSPVCC18

DSPVCC18

TECOBEST TECHNOLOGY

C146 C147 C148 C149

10nF 10nF 10nF 10nF

TB_V862

Title

ZR36862 & SDRAM

Size Document Number Rev

V1.2

Date: Saturday, May 28, 2005 Sheet 2 of 6

5 4 3 2 1

PDF created with pdfFactory Pro trial version www.pdffactory.com

5 4 3 2 1

OPUs Option:

SUPPORT OPUS:SANYO DV342/502W

D D

DV342(default) 502W

R221,R224=10R R221,R224=2.2R

R294,R295=0R R294,R295=91R

R202=2KR R202=0R

R127=43K R127=51K

R205=10K R205=3.3K

R207=2.2K R207=3.3K

C C

B B

TECOBEST TECHNOLOGY

A A

TB_V862

Title

ZR36862 & SDRAM

Size Document Number Rev

V1.2

Date: Saturday, May 28, 2005 Sheet 2 of 6

5 4 3 2 1

PDF created with pdfFactory Pro trial version www.pdffactory.com

5 4 3 2 1

Flash speed <= 70 nS.

If plan to use 90ns

Flash, it needs to be

MEMDA[15:0]

MEMDA[15:0] verified by s/w.

MEMAD[19:0]

D MEMAD[19:0] D

When using INTEL FLASH: TSOP_VCC

TSOP_VCC R166

R161=0 ohm, R160=NC U106 1R

DSPVCC33

When using SST FLASH: MEMAD19 [NM]

MEMAD15 1 48 MEMAD16

R160=0 ohm, R161=NC MEMAD14 2

A15 A16

47 R167

A14 BYTE# VCCQ

Default is SST mode. MEMAD13 3 A13 GND 46 NM

D5V

MEMAD12 4 45 MEMDA15 [1R]

MEMAD11 A12 DQ15 MEMDA7

5 A11 DQ7 44

MEMAD10 6 43 MEMDA14

MEMAD9 A10 DQ14 MEMDA6 C162 C541

7 A9 DQ6 42

C TSOP_VCC MEMAD8 8 41 MEMDA13 0.1uF 0.1uF C

R160 0R A8 DQ13 MEMDA5

9 NC A19 DQ5 40

[NM] 10 39 MEMDA12

MEMWR- A20 DQ12 MEMDA4

11 WE# DQ4 38

RESET 12 37

RESET RP# VCC MEMDA11

13 VPP NC DQ11 36

14 35 MEMDA3

WP# NC DQ3

R161 NM 15 34 MEMDA10

A19 RY/BY# DQ10

[0R] MEMAD18 16 33 MEMDA2

MEMAD17 A18 DQ2 MEMDA9

17 A17 DQ9 32

TSOP_VCC MEMAD7 18 31 MEMDA1

MEMAD6 A7 DQ1 MEMDA8

MEMAD5

19

20

A6 DQ8 30

29 MEMDA0

Close to Pin37 & Pin47 of U106

MEMAD4 A5 DQ0 MEMRD-

21 A4 OE# 28

MEMAD3 22 27

R168 MEMAD2 A3 GND FLASHCS-

23 A2 CE# 26

4.7K MEMAD1 24 25 MEMAD0

A1 A0

MEMWR-

MEMWR- SST39VF800

B B

MEMRD-

MEMRD-

MEMCS0-

MEMCS0-

TECOBEST TECHNOLOGY

A A

TB_V862

Title

FLASH & EEPROM

Size Document Number Rev

Custom V1.2

Date: Saturday, May 28, 2005 Sheet 3 of 6

5 4 3 2 1

PDF created with pdfFactory Pro trial version www.pdffactory.com

5 4 3 2 1

RF33V RF33V

RFA5V

2

Q202 R200

C231 + BT2907 1 10K

0.1uF C205 R221 DRVSB

+ 100uF/16V 10R C228

C201 C202 [2.2R] 47uF/16V

3

D 100uF/16V 0.1uF D

2

R202 R222

2K Q204 1 220R

DVD_LD

[0R] BT2907

RF33V

3

C212

1nF

OPU_HFM

2

R224 Q203 R201

10R + BT2907 1 10K

C207 C208 [2.2R]

CN201 0.1uF 0.1uF C229

24Pin OPU connector 47uF/16V

3

2

24 Q205 1 R223 220R

GND-LD DVDLD CD_LD

23 BT2907

DVD-LD 22

NC 21 3

HFM 20

MD 19 CDLD

CD-LD 18 PW5V

VR-DVD 17

1

VR-CD 16

NC 15 RFE RFE

1

E 14 D203

VCC 13 VREF R217 33R VC 2.1V 1N4001 D205

VC(VREF) VC VR_CD

12 R209 0R MD_DVD 1N4001

GND/PD 11 RFF

2

F RFF

10 RFB VR_DVD R210 0R MD_CD

B 9

22

RFA

2

A 8 RF Q210 Q211

RF RF

7 PDIC_SEL 3V3_DRV 1 S8550 DSPVCC33 1V8_DRV1 S8550 R553

CD/DVD_SW 6 DSPVCC18 0R

D RFD RF33V

C 5 RFC R294 R295 S8050/S8550 R551 0R C

C 4 TACT- 0R 0R DSPVCC33

3

T- DSPVCC33

3 TACT+ [91R] [91R]

T+ 2 FACT+

F+ RFA5V RF33V DSPVCC18

1 FACT- R552

2

F- 0R

GND

GND

Close to OPU Q212 1 Q213 1 R219 + R220

BT3904 BT3904 20K 1% C276 4.3K 1%

[0R] 220uF/10V

26

25

R207 R206

2E

C204 R208 R204 2.2K 4.7K 3V3_FB 1V8_FB

1B

3C

+

0.1uF C209 3.3K 470R [3.3K] [NM] +

47uF/16V C275

R218 R238 220uF/10V

12K 1% 10K 1%

PDIC_SEL R235 NM [NM]

CD/DVD

Not assemble for HOP1250/SPU3153/DPD20428

OPUs, and assemble for other OPUs PDIC_SEL: CD_DVD :

CD=HIGH R205 CD=LOW

Default=SANYO HD62 []=502W DVD=LOW 10K DVD=HIGH FOR AM5888S, DEFAULT

3

[3.3K]

Q201 1

FOR AT5669,R219=0R,R218=NM

BT3904

2

R278 24K

CN504 P+12V

Close to Motor driver

R264

PW5V

VDDPWM R505 0R M5V

B 1 B

U202 DRVSB 1K 1% 1K 1% M5V

2

AM5888S/AT5669 DRVSB 3 P+5V1FB501 220Z R506 0R RFA5V

RF33V R243 R292 1K RFA5V

4

FOCUS_S 0R 1 28 R265 5 P+5V2FB502 220Z R507 0R D5V

FOCUS_S VINFC STBY D5V

3V3_DRV 2 27

R236 R237 CFCERR1(OP2IN-) BIAS C246 0.1uF HEADER 5 +

1V8_FB 3 26 R268 + C501

10K 10K R246 CFCERR2(OP2IN+) VINTK 0R TRACK_S C504 220uF/16V

CN204 SLED_S 0R 4 25 1V8_DRV

+5V: +5V(+-2.5%) 100uF/16V

SLED_S VINSL+ CTKERR1(OP1IN+)

1 LOAD-

2 LOAD+ 3V3_FB 5 24

VINSL-(OP2OUT) CTKERR2(OP1IN-)

3

OUTSW CLOSE

4 6 23 R269

CLOSE VOSL(CLOSE) VINLD SPINDLE_S

5 0R

INSW OPEN 7 22

OPEN VNFFC(OPEN) PREGND

TRAY M5V M5V

8 21 MARK1

VCC PVCC2

.

LOAD- 9 20

PVCC1(LOAD-) VNFTK(OP1OUT)

1

C244 C245 LOAD+ 10 19 H1 H2 MARK2

RF33V 100uF/16V 0.1uF PGND(LOAD+) PGND(VCC2)

.

3 4 3 4

SLED- MOT_SPDL- RF33V 3 4 3 4

11 18 2 5 2 5

VOSL- VOLD- 2 5 2 5

1 1

1

SLED+ MOT_SPDL+ 1 1 MARK3

12 17

VOSL+ VOLD+

9

8

7

6

9

8

7

6

CN203 R254

.

FACT- 13 16 TACT- H1 H2

SLED+ 10K VOFC- VOTK- R276 R277 R279

6

9

8

7

6

9

8

7

6

1

5 SLED- FACT+ 14 15 TACT+ 1K 1K 39R MARK4

VOFC+ VOTK+

GND1

.

4

GND

HOMESW R299

3

2 MOT_SPDL+ C251 2K

1

MOT_SPDL- 22nF SPDL_SENS-

1

29

30

A A

SPDL_SENS+

SLED & SPINDLE

C274

1 2 R203 0.1uF

D207 LL4148 120R

2 1 TECOBEST TECHNOLOGY

D206 LL4148

TB_V862

Title

OPU Connector & DRIVER & POWER

Size Document Number Rev

V1.2

Date: Saturday, May 28, 2005 Sheet 4 of 6

5 4 3 2 1

PDF created with pdfFactory Pro trial version www.pdffactory.com

5 4 3 2 1

R322

Defult:CS4334 DSPVCC33 20K A-LMAIN

U301 R304 R309 D5V

C322

4

D D

CS4334 56R NC C320 R320 R323 120pF

A_LOUT 3.9K 2 - C323 R324

CEI2711 NC 10R R304 R309 1 1K LMAIN-OUT

56R NC 10uF/16V 10K C321 LMAIN-OUT

3 +

[NC] [10R] MJM4558E

2

1nF U303A 10uF/16V R325

U301 OP_12V MUTE 2K Q312

8

1

AOUT0 1 8 BT3904

AOUT0 ABCLK SDATA AOUTL

2 7

ABCLK ALRCLK SCLK VA R332

3

3 6

ALRCLK AMCLK LRCK VGND 20K A-RMAIN

4 5

AMCLK MCLK AOUTR

CS4334

[CEI2711] C332

4

C330 R330 R333 120pF

A_ROUT 3.9K 6 - C333 R334

7 1K RMAIN-OUT

10uF/16V 10K OP_BIAS RMAIN-OUT

5 +

+ MJM4558E

2

C304 C303 U303B 10uF/16V R335

MUTE

8

0.1uF 47uF/16V C331 OP_12V 2K 1 Q313

1nF BT3904

C C

3

R308

P+12V H: Mute 4.7K

3

R307 R310 + C317

MUTEC 1 Q303 3.3K 10uF/16V

MUTEC BT3904

47K

2

R301

100R Q304 BT3906

P+12V D5V 2 3

OP_12V

R311 10K

1

R302 + R312 100K

10K C301 C302

47uF/25V 0.1uF D301 LL4148

B OP_BIAS 1 2 B

Q305 BT3906

2 3 MUTE

+

R303 C305 C306

10K 47uF/25V 0.1uF +

C318

1

2

VGND 220uF/10V

R313

D302 47K R314

LL4148 2K

1

C319

47uF/25V

A TECOBEST TECHNOLOGY A

TB_V862

Title

Audio

Size Document Number Rev

V1.2

Date: Saturday, May 28, 2005 Sheet 5 of 6

5 4 3 2 1

PDF created with pdfFactory Pro trial version www.pdffactory.com

5 4 3 2 1

JR501

AV-4-405A

Y_R_V 7

Y_R_V

3

P+12V

D502 9

FS1: H=RGB L=CVBS NM

[BAT54S]

R509 R513 COAX_SPDIF 8

D SCART/VGA PORT FS2 FS3 SCART CFG 2K 2K D

2

00 4:3 [NM] [NM]

VSYNC DSPVCC33

VGND

12 HSYNC VSYNC

01 TV AUDIO/TV/16:9

11 HSYNC

10

Video Status

Y_R_V 10 16:9 C_B_U 4

C_B_U

3

9 C_B_U R510

8 CVBS_G_Y 1K

7 SCART_SWITCH CVBS_G_Y [NM] D504 6

6 CVBS_OUT NM

5 AUDIO/TV/16:9 [BAT54S]

4

3

RMAIN-OUT 5

3 RMAIN-OUT

LMAIN-OUT 1 Q501

2

2 FS2

RMAIN-OUT BT3904

1 DSPVCC33

[NM] VGND

D5V

2

CN501

CVBS_G_Y 1

CVBS_G_Y

3

VGND

1 Q502 R514

FS3

BT3904 150R D503 3

[NM] [NM] NM

[BAT54S]

2

LMAIN-OUT 2

LMAIN-OUT

2

FS1 1 Q503

DSPVCC33

BT3904 VGND

[NM] VGND

SCART_SWITCH

2

RGB Status

R516

1K JR504

1

C C

[NM]

C520 11pF

1

SCART 8

8

CVBS_C L501 1.1uH CVBS_OUT 7 9

CVBS_C 7 9

1

C511 C521 Y_R_V 3

150pF 160pF D506 D505 3

LL4148 LL4148 C_B_U 4

4

2

DSPVCC33

2

DSPVCC33 VGND VGND

2

VGND

CVBS &

SVIDEO

R501 R502 R503 R504

10K 10K 10K 4.7K

CN503

D5V

1

2 R540 220R

IRRCV D5V

3

4 R541 220R

FPC_CLK

5 R542 220R

FPC_STB

6 R543 220R

FPC_DOUT R550

10R

VFD_PORT C542

C535

NM JR505

B B

+

[100pF] 3

GND

100uF/16V 2

R548 68R VCC

OPT_SPDIF 1

IN

KEY D5V

OPTI

3

R549 33R

SPDIF 1 Q505 C509

SPDIF

0.1uF

BT3904

2

Close to Q505

R529

56R

C528

R544

COAX_SPDIF

R530 62R

0.1uF

39R C510

22pF

A A

TECOBEST TECHNOLOGY

TB_V862

Title

AV output

Size Document Number Rev

V1.2

Date: Saturday, May 28, 2005 Sheet 6 of 6

5 4 3 2 1

PDF created with pdfFactory Pro trial version www.pdffactory.com

You might also like

- RTL9210-VB-CG Demo V203 PDFDocument5 pagesRTL9210-VB-CG Demo V203 PDFCenusa MihaiNo ratings yet

- Tinysa RF Section V2 Per M0Wid Pinout: Sma SKT EdgeDocument1 pageTinysa RF Section V2 Per M0Wid Pinout: Sma SKT EdgePisu Miau Pisu Miau67% (9)

- Driver Led BN44-00523BDocument1 pageDriver Led BN44-00523Bies837100% (2)

- SCH Srm450v2 Schematics Amp (0029446-Xx Revh00)Document5 pagesSCH Srm450v2 Schematics Amp (0029446-Xx Revh00)John Casas50% (2)

- Ancient Greece Final ProjectDocument6 pagesAncient Greece Final Projectschmidtbrent100% (1)

- Ibanez Ds7 Distortion SchematicDocument1 pageIbanez Ds7 Distortion SchematicsubcomandantemarcosNo ratings yet

- Basic 400 Pst368eDocument8 pagesBasic 400 Pst368eMehran Azizi100% (1)

- Silica Gel Production Report PDFDocument8 pagesSilica Gel Production Report PDFChoice Organo0% (1)

- ESP32 S2 SAOLA 1 - V1.1 - SchematicsDocument2 pagesESP32 S2 SAOLA 1 - V1.1 - SchematicsN AbeyNo ratings yet

- Iphone6 SchematicDocument54 pagesIphone6 Schematicbullet884No ratings yet

- SM-T818V Esquematico Completo Anibal Garcia IrepairDocument8 pagesSM-T818V Esquematico Completo Anibal Garcia Irepairdavid.mrtinz.hdzNo ratings yet

- ILI9486Document19 pagesILI9486bthcall3No ratings yet

- Rev. Change Description Date Drawn: Notes 1. MUST MEET DELTA SPEC. 10000-0162 2. Eltek P/N: N/A 3. Eltek Doc No. N/ADocument4 pagesRev. Change Description Date Drawn: Notes 1. MUST MEET DELTA SPEC. 10000-0162 2. Eltek P/N: N/A 3. Eltek Doc No. N/AIsac ClaroNo ratings yet

- Generic Display Adapter V2.1Document2 pagesGeneric Display Adapter V2.1Fahri AyberkNo ratings yet

- Primare I21 Amplifier SM 2001Document11 pagesPrimare I21 Amplifier SM 2001rzysztof.warpechowskiNo ratings yet

- 10085-9-V13-ETP2-00018 Tap ChangerDocument10 pages10085-9-V13-ETP2-00018 Tap ChangerAbdelrahman RamadanNo ratings yet

- Power SupplyDocument1 pagePower SupplyEimantas TolisNo ratings yet

- Esquema EletricoDocument31 pagesEsquema EletricoJefferson AmbrosioNo ratings yet

- Esquema ALI M3329Document8 pagesEsquema ALI M3329DanielFontanive100% (3)

- Schematics Iphone 6+ Alpha2000Document57 pagesSchematics Iphone 6+ Alpha2000imayavenged sevenfoldismNo ratings yet

- IBE (Luminaria)Document5 pagesIBE (Luminaria)Jose CachonNo ratings yet

- SM-T818A Esquematico Completo Anibal Garcia IrepairDocument10 pagesSM-T818A Esquematico Completo Anibal Garcia IrepairFederico Héctor UsseglioNo ratings yet

- Smartsim340 Schematic v100Document1 pageSmartsim340 Schematic v100bruno magalhãesNo ratings yet

- AS3422 Eval Board V2.1Document6 pagesAS3422 Eval Board V2.1Alejandro CaceresNo ratings yet

- PLC MegaV2 - Slim PDFDocument1 pagePLC MegaV2 - Slim PDFfrancisco ibañezNo ratings yet

- Diagrama Elétrico - MXM202D-232DDocument36 pagesDiagrama Elétrico - MXM202D-232Dmarciotech99 moraesNo ratings yet

- Release Notice: PCB Outline DrawingDocument5 pagesRelease Notice: PCB Outline DrawingsunilbeedasseeNo ratings yet

- N/A W3002R Common Product: Product Name:: TendaDocument12 pagesN/A W3002R Common Product: Product Name:: TendaOlegNo ratings yet

- ClanSOFT - Diagrama Técnico Esquemático Completo SM-G531M MUDocument7 pagesClanSOFT - Diagrama Técnico Esquemático Completo SM-G531M MUJunior Souza JrNo ratings yet

- UENR62730001Document17 pagesUENR62730001Henry Sergio HuayhuaNo ratings yet

- Butterfly Valves: B. D. K. Engineering Industries LimitedDocument6 pagesButterfly Valves: B. D. K. Engineering Industries LimitedRajesh KanalaNo ratings yet

- 机型:KDL42XS715UN: Konka Dtv Sch DesignDocument14 pages机型:KDL42XS715UN: Konka Dtv Sch DesignAlexis FloresNo ratings yet

- CT844 17 RLT 28x12 T22.23x9.53 F - IFC - R1Document1 pageCT844 17 RLT 28x12 T22.23x9.53 F - IFC - R1admin qaqcNo ratings yet

- CC3200 SchematicDocument7 pagesCC3200 Schematic陈仁杰No ratings yet

- Renr8130 C12 PDFDocument2 pagesRenr8130 C12 PDFait mimouneNo ratings yet

- Cummins R20 ElectricalDocument7 pagesCummins R20 Electricaljean sanchezNo ratings yet

- Servicemanual Panasonic kv-s5055c s1Document11 pagesServicemanual Panasonic kv-s5055c s1Ralf KöhlerNo ratings yet

- BC 5300&5380 (1) FluidicDocument8 pagesBC 5300&5380 (1) FluidicCHARLIE BRICENo ratings yet

- Wiring Diagram GensetDocument7 pagesWiring Diagram Gensetali202258No ratings yet

- SM-T337A Esquematico Completo Anibal Garcia IrepairDocument12 pagesSM-T337A Esquematico Completo Anibal Garcia IrepairRenato Luiz TécnicoNo ratings yet

- Crest Old CA 12 Output SchematicDocument1 pageCrest Old CA 12 Output SchematicFederico Urquiza100% (2)

- Petra UMA Touch CSD Acer Aspire V5-531-V5-571-V5-431Document103 pagesPetra UMA Touch CSD Acer Aspire V5-531-V5-571-V5-431ady putraNo ratings yet

- Husk Petra NVidia None Touch CSD Acer Aspire V5-531-V5-571-V5-431Document103 pagesHusk Petra NVidia None Touch CSD Acer Aspire V5-531-V5-571-V5-431ady putraNo ratings yet

- SKYWORTH 37 Inch LCDTV PSU CircutsDocument1 pageSKYWORTH 37 Inch LCDTV PSU CircutsJhun CruzNo ratings yet

- Nokia n72 rm180 Schematics PDFDocument8 pagesNokia n72 rm180 Schematics PDFAbu Hanna MariamNo ratings yet

- Wating Area Elevations Sds LTC 015-23-007Document1 pageWating Area Elevations Sds LTC 015-23-007almamoura.eaNo ratings yet

- Default Switch/Jumper SettingsDocument16 pagesDefault Switch/Jumper SettingsRafael Avella100% (1)

- Ib MSOHDocument5 pagesIb MSOHGress AlmeydaNo ratings yet

- Abrfeviaturas, Diagrama de ConexionesDocument10 pagesAbrfeviaturas, Diagrama de ConexionesRicardo Diaz MorenoNo ratings yet

- 4283773-01-E Balde G2Document2 pages4283773-01-E Balde G2Robin carcamoNo ratings yet

- DVA T4 Amp Mid - High (Scheme)Document1 pageDVA T4 Amp Mid - High (Scheme)Sem ToughzaouiNo ratings yet

- ESP32 S3 Touch LCD 4.3 SCH 2Document3 pagesESP32 S3 Touch LCD 4.3 SCH 2laurencebarbasteNo ratings yet

- Gigabyte Gv-R67xtgaming Oc-12gd Rev 1.0Document42 pagesGigabyte Gv-R67xtgaming Oc-12gd Rev 1.0techgamebr85No ratings yet

- Esp32 c6 Devkitm 1 SchematicsDocument2 pagesEsp32 c6 Devkitm 1 SchematicsNguyễn Công DanhNo ratings yet

- Puntoapunto 306Document17 pagesPuntoapunto 306Carlos HernandezNo ratings yet

- QH MK A5000 LCM FPC SchematicDocument3 pagesQH MK A5000 LCM FPC SchematicNikolayNo ratings yet

- Bz26938gex-P Diagrama Placa PortÁtilDocument1 pageBz26938gex-P Diagrama Placa PortÁtilapi-3702225No ratings yet

- Bz26938gex-P Diagrama Placa PortÁtilDocument1 pageBz26938gex-P Diagrama Placa PortÁtilapi-3702225No ratings yet

- Pet-704 704PDocument38 pagesPet-704 704Papi-3702225100% (1)

- Deh 536 Deh636Document91 pagesDeh 536 Deh636api-3702225No ratings yet

- Schematic Diagram VC-910Document7 pagesSchematic Diagram VC-910api-3702225100% (2)

- Pet 708Document32 pagesPet 708api-3702225100% (1)

- Pet 320Document33 pagesPet 320api-3702225No ratings yet

- Pet 700Document26 pagesPet 700api-3702225No ratings yet

- BZ6938GEX-P Lista de PeçasDocument12 pagesBZ6938GEX-P Lista de Peçasapi-3702225No ratings yet

- Pet 705Document28 pagesPet 705api-3702225100% (3)

- Pet 702Document34 pagesPet 702api-3702225100% (3)

- Pet-821 824 825 V 1 6-Service ManualDocument28 pagesPet-821 824 825 V 1 6-Service Manualapi-3702225No ratings yet

- Service Manual: DVP-S325/S525D/S725DDocument31 pagesService Manual: DVP-S325/S525D/S725Dapi-3702225No ratings yet

- KX TG2559LBSDocument90 pagesKX TG2559LBSAnonymous Lfgk6vygNo ratings yet

- Manual de Servicio: Modelo: Dg-K23Document20 pagesManual de Servicio: Modelo: Dg-K23api-3702225No ratings yet

- Dpc-7600 8600 Daewoo DVD Portable PlayerDocument46 pagesDpc-7600 8600 Daewoo DVD Portable Playerapi-3702225No ratings yet

- DPC 7100 DVD DaewooDocument26 pagesDPC 7100 DVD Daewooapi-3702225100% (1)

- KX tc1005Document2 pagesKX tc1005api-3702225No ratings yet

- Compaq TFT8000 ControlDocument1 pageCompaq TFT8000 Controlapi-3702225No ratings yet

- KX TC1709LBBDocument75 pagesKX TC1709LBBapi-3702225100% (1)

- Compaq MB ServerDocument80 pagesCompaq MB Serverapi-3702225No ratings yet

- Dvd4500xscore EsquemaDocument9 pagesDvd4500xscore Esquemaapi-3702225100% (1)

- Compaq TFT8000 AdjustmentDocument1 pageCompaq TFT8000 Adjustmentapi-3702225No ratings yet

- Telefone+Toshiba+FT 8009Document23 pagesTelefone+Toshiba+FT 8009api-3702225100% (1)

- KX F700 Esquema CompletoDocument16 pagesKX F700 Esquema Completoapi-3702225100% (1)

- Service: Samsung FacsimileDocument23 pagesService: Samsung Facsimileapi-3702225No ratings yet

- DVD4500XB EsquemaDocument9 pagesDVD4500XB Esquemaapi-3702225No ratings yet

- Telefone+Toshiba+FT 8808Document56 pagesTelefone+Toshiba+FT 8808api-3702225No ratings yet

- Cordless Telephone: Service ManualDocument21 pagesCordless Telephone: Service Manualapi-3702225No ratings yet

- Sharp UX-500, 510, FO-1460 Service ManualDocument108 pagesSharp UX-500, 510, FO-1460 Service ManualjgerabmNo ratings yet

- Electrical SystemDocument368 pagesElectrical SystemAnonymous 28jRu2j100% (1)

- El3356 0010Document3 pagesEl3356 0010Krishnamurthy KulkarniNo ratings yet

- Sampel Active Filter BrocureDocument1 pageSampel Active Filter BrocureMario WiryaNo ratings yet

- Design For Test Scan TestDocument31 pagesDesign For Test Scan TestMani KandanNo ratings yet

- E 180 000 2 11 13Document408 pagesE 180 000 2 11 13spaszko54No ratings yet

- Air CondDocument50 pagesAir CondIzad Bin Idris100% (2)

- Back To The Roots SanyovaDocument60 pagesBack To The Roots SanyovabeaNo ratings yet

- VI Sem Major Trends in Historical Thought and Writing PDFDocument139 pagesVI Sem Major Trends in Historical Thought and Writing PDFShona Roy100% (1)

- Rak College of Nursing, Lajpat Nagar, NEW DELHI 110024Document17 pagesRak College of Nursing, Lajpat Nagar, NEW DELHI 110024Pankaj S R MehrotraNo ratings yet

- Materials Management Notes (1) 4321 (1) Wert343Document85 pagesMaterials Management Notes (1) 4321 (1) Wert343Mohammed AneesNo ratings yet

- Maths SyllabusDocument71 pagesMaths SyllabuswakiroivanNo ratings yet

- April CC - 19Document3 pagesApril CC - 19Er Rohit VermaNo ratings yet

- Manual de Reparacion QSK23Document944 pagesManual de Reparacion QSK23Suministros Mantenimiento100% (2)

- PRIYADocument9 pagesPRIYAswapnilNo ratings yet

- User Interface Design: (Lecture 7)Document22 pagesUser Interface Design: (Lecture 7)jatinderNo ratings yet

- Afra Corporation LTD.: Page 1 of 2Document2 pagesAfra Corporation LTD.: Page 1 of 2salimcivil12No ratings yet

- Dok TD MRD1 GeDocument56 pagesDok TD MRD1 GeheriberhuertaNo ratings yet

- Synonymy and PolysemyDocument2 pagesSynonymy and PolysemyOtmane ArabyNo ratings yet

- 1st Merit List 5th Semester BS Applied Psychology Group A Department of Applied Psychology RAHIM YAR KHAN RYK 5th Semester Fall 2022 Fall 2022Document3 pages1st Merit List 5th Semester BS Applied Psychology Group A Department of Applied Psychology RAHIM YAR KHAN RYK 5th Semester Fall 2022 Fall 2022Muhammad ShahidNo ratings yet

- Utilitarianism & DeontologyDocument12 pagesUtilitarianism & DeontologyJustin ViberNo ratings yet

- GROUP 4 (Phoneme, Allophones, Phonetic Analysis)Document13 pagesGROUP 4 (Phoneme, Allophones, Phonetic Analysis)Khansa Sweet7No ratings yet

- HVDC Control & ProtectionDocument31 pagesHVDC Control & ProtectionS Bharadwaj ReddyNo ratings yet

- Free M.phil Thesis in Computer ScienceDocument4 pagesFree M.phil Thesis in Computer Scienceaflnzefdqbrevm100% (2)

- FICHA TECNICA EHB04 - Tech - DatasheetDocument5 pagesFICHA TECNICA EHB04 - Tech - DatasheetLio LiverhNo ratings yet

- Turbo ChargerDocument7 pagesTurbo ChargerRachit Sharma100% (1)

- YgojDocument25 pagesYgojAnshul SainiNo ratings yet

- TH336, TH337, TH406, TH407, TH414, TH514, TH417 Hydraulic Schematic TH336, TH337, TH406, TH407Document2 pagesTH336, TH337, TH406, TH407, TH414, TH514, TH417 Hydraulic Schematic TH336, TH337, TH406, TH407مهدي شقرونNo ratings yet

- Development and Validation of Module inDocument271 pagesDevelopment and Validation of Module inKareen Joy ManglicmotNo ratings yet