Buk555 100a

Buk555 100a

Uploaded by

Diego AliasCopyright:

Available Formats

Buk555 100a

Buk555 100a

Uploaded by

Diego AliasOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Buk555 100a

Buk555 100a

Uploaded by

Diego AliasCopyright:

Available Formats

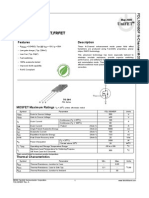

Philips Semiconductors

Product Specification

PowerMOS transistor Logic level FET

GENERAL DESCRIPTION

N-channel enhancement mode logic level field-effect power transistor in a plastic envelope. The device is intended for use in Switched Mode Power Supplies (SMPS), motor control, welding, DC/DC and AC/DC converters, and in automotive and general purpose switching applications.

BUK555-100A/B

QUICK REFERENCE DATA

SYMBOL VDS ID Ptot Tj RDS(ON) PARAMETER BUK555 Drain-source voltage Drain current (DC) Total power dissipation Junction temperature Drain-source on-state resistance; VGS = 5 V MAX. -100A 100 25 125 175 0.085 MAX. -100B 100 22 125 175 0.11 UNIT V A W C

PINNING - TO220AB

PIN 1 2 3 tab gate drain source drain DESCRIPTION

PIN CONFIGURATION

tab

SYMBOL

d

1 23

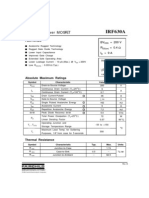

LIMITING VALUES

Limiting values in accordance with the Absolute Maximum System (IEC 134) SYMBOL VDS VDGR VGS VGSM ID ID IDM Ptot Tstg Tj PARAMETER Drain-source voltage Drain-gate voltage Gate-source voltage Non-repetitive gate-source voltage Drain current (DC) Drain current (DC) Drain current (pulse peak value) Total power dissipation Storage temperature Junction Temperature CONDITIONS RGS = 20 k tp 50 s Tmb = 25 C Tmb = 100 C Tmb = 25 C Tmb = 25 C MIN. - 55 -100A 25 18 100 125 175 175 MAX. 100 100 15 20 -100B 22 15 88 UNIT V V V V A A A W C C

THERMAL RESISTANCES

SYMBOL Rth j-mb Rth j-a PARAMETER Thermal resistance junction to mounting base Thermal resistance junction to ambient CONDITIONS MIN. TYP. 60 MAX. 1.2 UNIT K/W K/W

April 1993

Rev 1.100

Philips Semiconductors

Product Specification

PowerMOS transistor Logic level FET

STATIC CHARACTERISTICS

Tmb = 25 C unless otherwise specified SYMBOL V(BR)DSS VGS(TO) IDSS IDSS IGSS RDS(ON) PARAMETER Drain-source breakdown voltage Gate threshold voltage Zero gate voltage drain current Zero gate voltage drain current Gate source leakage current Drain-source on-state resistance CONDITIONS VGS = 0 V; ID = 0.25 mA VDS = VGS; ID = 1 mA VDS = 100 V; VGS = 0 V; Tj = 25 C VDS = 100 V; VGS = 0 V; Tj =125 C VGS = 10 V; VDS = 0 V VGS = 5 V; BUK555-100A BUK555-100B ID = 13 A MIN. 100 1.0 -

BUK555-100A/B

TYP. 1.5 1 0.1 10 0.075 0.09

MAX. 2.0 10 1.0 100 0.085 0.11

UNIT V V A mA nA

DYNAMIC CHARACTERISTICS

Tmb = 25 C unless otherwise specified SYMBOL gfs Ciss Coss Crss td on tr td off tf Ld Ld Ls PARAMETER Forward transconductance Input capacitance Output capacitance Feedback capacitance Turn-on delay time Turn-on rise time Turn-off delay time Turn-off fall time Internal drain inductance Internal drain inductance Internal source inductance CONDITIONS VDS = 25 V; ID = 13 A VGS = 0 V; VDS = 25 V; f = 1 MHz VDD = 30 V; ID = 3 A; VGS = 5 V; RGS = 50 ; Rgen = 50 Measured from contact screw on tab to centre of die Measured from drain lead 6 mm from package to centre of die Measured from source lead 6 mm from package to source bond pad MIN. 10 TYP. 13.5 1450 280 100 25 65 135 80 3.5 4.5 7.5 MAX. 1750 350 150 40 85 180 110 UNIT S pF pF pF ns ns ns ns nH nH nH

REVERSE DIODE LIMITING VALUES AND CHARACTERISTICS

Tmb = 25 C unless otherwise specified SYMBOL IDR IDRM VSD trr Qrr PARAMETER Continuous reverse drain current Pulsed reverse drain current Diode forward voltage Reverse recovery time Reverse recovery charge CONDITIONS IF = 25 A ; VGS = 0 V IF = 25 A; -dIF/dt = 100 A/s; VGS = 0 V; VR = 30 V MIN. TYP. 1.3 90 0.8 MAX. 25 100 1.7 UNIT A A V ns C

AVALANCHE LIMITING VALUE

Tmb = 25 C unless otherwise specified SYMBOL WDSS PARAMETER Drain-source non-repetitive unclamped inductive turn-off energy CONDITIONS ID = 25 A ; VDD 50 V ; VGS = 5 V ; RGS = 50 MIN. TYP. MAX. 140 UNIT mJ

April 1993

Rev 1.100

Philips Semiconductors

Product Specification

PowerMOS transistor Logic level FET

BUK555-100A/B

120 110 100 90 80 70 60 50 40 30 20 10 0

PD%

Normalised Power Derating

10

Zth j-mb / (K/W)

BUKx55-lv

D= 0.5 0.2 0.1 0.05 0.02 0 P D tp D= tp T t 1E+01

0.1

0.01

20

40

60

80 100 Tmb / C

120

140

160

180

0.001 1E-07

T 1E-05 1E-03 t/s 1E-01

Fig.1. Normalised power dissipation. PD% = 100PD/PD 25 C = f(Tmb)

ID% Normalised Current Derating

Fig.4. Transient thermal impedance. Zth j-mb = f(t); parameter D = tp/T

ID / A 10 7 40 30 20 3 10 0 VGS / V = 4 5 BUK555-100A

120 110 100 90 80 70 60 50 40 30 20 10 0

50

20

40

60

80 100 Tmb / C

120

140

160

180

4 VDS / V

10

Fig.2. Normalised continuous drain current. ID% = 100ID/ID 25 C = f(Tmb); conditions: VGS 5 V

ID / A BUK555-100A,B

Fig.5. Typical output characteristics, Tj = 25 C. ID = f(VDS); parameter VGS

RDS(ON) / Ohm VGS / V = 3 3.5 BUK555-100A

1000

0.5 0.4

2.5

100

RD O S( N)

=V

/ DS

ID

A B tp = 10 us 100 us

0.3 0.2 0.1

4 4.5 5 10

10 DC 1 ms 10 ms 100 ms 1 1 10 VDS / V 100 1000

20 ID / A

40

Fig.3. Safe operating area. Tmb = 25 C ID & IDM = f(VDS); IDM single pulse; parameter tp

Fig.6. Typical on-state resistance, Tj = 25 C. RDS(ON) = f(ID); parameter VGS

April 1993

Rev 1.100

Philips Semiconductors

Product Specification

PowerMOS transistor Logic level FET

BUK555-100A/B

50

ID / A Tj / C = 25 150

BUK555-100A

2

VGS(TO) / V max.

40

typ.

30

1 min.

20

10

0 0 2 4 VGS / V 6 8

0 -60 -20 20 60 Tj / C 100 140 180

Fig.7. Typical transfer characteristics. ID = f(VGS) ; conditions: VDS = 25 V; parameter Tj

gfs / S BUK555-100A

Fig.10. Gate threshold voltage. VGS(TO) = f(Tj); conditions: ID = 1 mA; VDS = VGS

ID / A SUB-THRESHOLD CONDUCTION

20

1E-01

1E-02

15

1E-03 2% typ 98 %

10

1E-04

1E-05

0 0 20 ID / A 40

1E-06 0 0.4 0.8 1.2 VGS / V 1.6 2 2.4

Fig.8. Typical transconductance, Tj = 25 C. gfs = f(ID); conditions: VDS = 25 V

a Normalised RDS(ON) = f(Tj)

Fig.11. Sub-threshold drain current. ID = f(VGS); conditions: Tj = 25 C; VDS = VGS

C / pF BUK5y5-100

2.4 2.2 2.0 1.8 1.6 1.4 1.2 1.0 0.8 0.6 0.4 0.2 0

10000

1000

Ciss

Coss 100 Crss

-60

-20

20

60 Tj / C

100

140

180

10 0 20 VDS / V 40

Fig.9. Normalised drain-source on-state resistance. a = RDS(ON)/RDS(ON)25 C = f(Tj); ID = 13 A; VGS = 5 V

Fig.12. Typical capacitances, Ciss, Coss, Crss. C = f(VDS); conditions: VGS = 0 V; f = 1 MHz

April 1993

Rev 1.100

Philips Semiconductors

Product Specification

PowerMOS transistor Logic level FET

BUK555-100A/B

12 10 8 6 4 2 0

VGS / V

BUK555-100 VDS / V =20

120 110 100 90 80 70 60 50 40 30 20 10 0

WDSS%

80

20 QG / nC

40

20

40

60

80

100 120 Tmb / C

140

160

180

Fig.13. Typical turn-on gate-charge characteristics. VGS = f(QG); conditions: ID = 25 A; parameter VDS

IF / A BUK555-100A

Fig.15. Normalised avalanche energy rating. WDSS% = f(Tmb); conditions: ID = 25 A

50

+

40

VDD

L VDS

30

VGS

20 Tj / C = 150 10 25

-ID/100 T.U.T. R 01 shunt

0 RGS

0 0 1 VSDS / V 2

Fig.14. Typical reverse diode current. IF = f(VSDS); conditions: VGS = 0 V; parameter Tj

Fig.16. Avalanche energy test circuit. 2 WDSS = 0.5 LID BVDSS /(BVDSS VDD )

April 1993

Rev 1.100

Philips Semiconductors

Product Specification

PowerMOS transistor Logic level FET

MECHANICAL DATA

Dimensions in mm Net Mass: 2 g

BUK555-100A/B

4,5 max 10,3 max

1,3

3,7 2,8

5,9 min

15,8 max

3,0 max not tinned

3,0

13,5 min

1,3 max 1 2 3 (2x)

2,54 2,54

0,9 max (3x)

0,6 2,4

Fig.17. TO220AB; pin 2 connected to mounting base.

Notes 1. Observe the general handling precautions for electrostatic-discharge sensitive devices (ESDs) to prevent damage to MOS gate oxide. 2. Refer to mounting instructions for TO220 envelopes. 3. Epoxy meets UL94 V0 at 1/8".

April 1993

Rev 1.100

Philips Semiconductors

Product Specification

PowerMOS transistor Logic level FET

DEFINITIONS

Data sheet status Objective specification Product specification Limiting values

BUK555-100A/B

This data sheet contains target or goal specifications for product development. This data sheet contains final product specifications.

Preliminary specification This data sheet contains preliminary data; supplementary data may be published later.

Limiting values are given in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of this specification is not implied. Exposure to limiting values for extended periods may affect device reliability. Application information Where application information is given, it is advisory and does not form part of the specification. Philips Electronics N.V. 1996 All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, it is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent or other industrial or intellectual property rights.

LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.

April 1993

Rev 1.100

This datasheet has been download from: www.datasheetcatalog.com Datasheets for electronics components.

You might also like

- Truck FormatDocument2 pagesTruck Formatemmanuel2024895% (19)

- Buk453 100aDocument7 pagesBuk453 100amicrowave440No ratings yet

- Buk455 200aDocument8 pagesBuk455 200athecrabforyouNo ratings yet

- Buk 456 60HDocument7 pagesBuk 456 60HkleephNo ratings yet

- Buk564-60h Powermos Transistor FetDocument7 pagesBuk564-60h Powermos Transistor FetOlga PlohotnichenkoNo ratings yet

- BUK436-200A PowerMOS TransistorDocument8 pagesBUK436-200A PowerMOS TransistorZxdIaminxXzlovewithzxXzyouzxNo ratings yet

- Datasheet BUK7508-55Document9 pagesDatasheet BUK7508-55Luis PerezNo ratings yet

- P-Channel Enhancement Mode BSH205 MOS Transistor: Features Symbol Quick Reference DataDocument7 pagesP-Channel Enhancement Mode BSH205 MOS Transistor: Features Symbol Quick Reference DataKumar Amit VermaNo ratings yet

- N-Channel Enhancement Mode Bsp100 Trenchmos Transistor: Features Symbol Quick Reference DataDocument9 pagesN-Channel Enhancement Mode Bsp100 Trenchmos Transistor: Features Symbol Quick Reference DataroozbehxoxNo ratings yet

- Qfet Qfet Qfet Qfet: FQP55N10Document8 pagesQfet Qfet Qfet Qfet: FQP55N10andreanuovoNo ratings yet

- Fqa5n90900v N-Channel MosfetDocument8 pagesFqa5n90900v N-Channel MosfetbmmostefaNo ratings yet

- N-Channel Trenchmos Transistor Irf540, Irf540S: Features Symbol Quick Reference DataDocument10 pagesN-Channel Trenchmos Transistor Irf540, Irf540S: Features Symbol Quick Reference DatathedrodNo ratings yet

- BTA151Document6 pagesBTA151Alejandro Borrego DominguezNo ratings yet

- N-Channel Trenchmos Transistor Irf630, Irf630S: Features Symbol Quick Reference DataDocument9 pagesN-Channel Trenchmos Transistor Irf630, Irf630S: Features Symbol Quick Reference Datalord mace tyrellNo ratings yet

- FDL100N50FDocument8 pagesFDL100N50FthanhluanbkNo ratings yet

- AO4912 Asymmetric Dual N-Channel Enhancement Mode Field Effect TransistorDocument8 pagesAO4912 Asymmetric Dual N-Channel Enhancement Mode Field Effect Transistordreyes3773No ratings yet

- IRFS830A: Advanced Power MOSFETDocument7 pagesIRFS830A: Advanced Power MOSFETtecjc1No ratings yet

- BUK7511-55A BUK7611-55A: 1. DescriptionDocument15 pagesBUK7511-55A BUK7611-55A: 1. DescriptionziminautaNo ratings yet

- IRFZ48 55V-64A 140W-N-channelenhancemenT PDFDocument8 pagesIRFZ48 55V-64A 140W-N-channelenhancemenT PDFZxdIaminxXzlovewithzxXzyouzxNo ratings yet

- IRF630A: Advanced Power MOSFETDocument7 pagesIRF630A: Advanced Power MOSFETdragon-red0816No ratings yet

- FQPF17P06: 60V P-Channel MOSFETDocument8 pagesFQPF17P06: 60V P-Channel MOSFETMahmoued YasinNo ratings yet

- Dual N-Channel Enhancement Mode Phn210T Trenchmos TransistorDocument8 pagesDual N-Channel Enhancement Mode Phn210T Trenchmos TransistorCristian ViolaNo ratings yet

- 01 Ufshsi 4 Pczuf 2 FKWKTC 7 PDG 1 PyDocument9 pages01 Ufshsi 4 Pczuf 2 FKWKTC 7 PDG 1 PyPuti Benny LakraNo ratings yet

- FDN335NDocument5 pagesFDN335NFernando YanoNo ratings yet

- Fqa6n70700v N-Channel MosfetDocument8 pagesFqa6n70700v N-Channel MosfetbmmostefaNo ratings yet

- Data Sheet: P-Channel Enhancement Mode Vertical D-MOS TransistorDocument12 pagesData Sheet: P-Channel Enhancement Mode Vertical D-MOS TransistorMiloud ChouguiNo ratings yet

- Irf640a PDFDocument7 pagesIrf640a PDFXavier CastilloNo ratings yet

- BUK951R6-30E: 1. Product ProfileDocument13 pagesBUK951R6-30E: 1. Product ProfileTom BeanNo ratings yet

- N-Channel Enhancement Mode Bsp100 Trenchmos Transistor: Features Symbol Quick Reference DataDocument9 pagesN-Channel Enhancement Mode Bsp100 Trenchmos Transistor: Features Symbol Quick Reference DataroozbehxoxNo ratings yet

- BUK7508-55A: 1. Product ProfileDocument14 pagesBUK7508-55A: 1. Product Profilejalvarez_385073No ratings yet

- Irf9540, Sihf9540: Vishay SiliconixDocument9 pagesIrf9540, Sihf9540: Vishay SiliconixraminakhanNo ratings yet

- IRFF420 JANTX2N6794 Hexfet Transistors JANTXV2N6794 THRU-HOLE (TO-205AF) REF:MIL-PRF-19500/555 500V, N-CHANNELDocument8 pagesIRFF420 JANTX2N6794 Hexfet Transistors JANTXV2N6794 THRU-HOLE (TO-205AF) REF:MIL-PRF-19500/555 500V, N-CHANNELppanagosNo ratings yet

- IRF450Document7 pagesIRF450Viet Hoang LeNo ratings yet

- FQP13N50: N-Channel QFET MosfetDocument8 pagesFQP13N50: N-Channel QFET MosfetaldoNo ratings yet

- Sss6n70a-Advanced Power MosfetDocument7 pagesSss6n70a-Advanced Power MosfetbmmostefaNo ratings yet

- IRF360Document7 pagesIRF360Miloud ChouguiNo ratings yet

- FTP05N50Document11 pagesFTP05N50Mustapha Maiz Hadj AhmedNo ratings yet

- RFP12N10LDocument6 pagesRFP12N10LSasi Kiran SNo ratings yet

- Fds 4435Document5 pagesFds 4435Rommel LoayzaNo ratings yet

- FD3055Document8 pagesFD3055maldomattNo ratings yet

- JANTX2N6768 Hexfet Transistors JANTXV2N6768 THRU-HOLE (TO-204AA/AE) (REF:MIL-PRF-19500/543) IRF350Document7 pagesJANTX2N6768 Hexfet Transistors JANTXV2N6768 THRU-HOLE (TO-204AA/AE) (REF:MIL-PRF-19500/543) IRF350Miloud ChouguiNo ratings yet

- JANTX2N6756 Hexfet Transistors JANTXV2N6756 THRU-HOLE (TO-204AA/AE) (REF:MIL-PRF-19500/542) IRF130Document7 pagesJANTX2N6756 Hexfet Transistors JANTXV2N6756 THRU-HOLE (TO-204AA/AE) (REF:MIL-PRF-19500/542) IRF130meroka2000No ratings yet

- Irfr3707Zpbf Irfu3707Zpbf: V R Max QGDocument11 pagesIrfr3707Zpbf Irfu3707Zpbf: V R Max QGJared RobisonNo ratings yet

- FQP6N60Document8 pagesFQP6N60achuthkumarNo ratings yet

- Fds 4488Document5 pagesFds 4488javierrincon800No ratings yet

- IRF650B / IRFS650B: 200V N-Channel MOSFETDocument11 pagesIRF650B / IRFS650B: 200V N-Channel MOSFETMiloud ChouguiNo ratings yet

- FET 75N75 TransistorDocument8 pagesFET 75N75 Transistorshahid iqbalNo ratings yet

- BT151 600RDocument6 pagesBT151 600RGiovanny DíazNo ratings yet

- N 308 ApDocument11 pagesN 308 Apdragon-red0816No ratings yet

- Fdw2503N: Dual N-Channel 2.5V Specified Powertrench MosfetDocument6 pagesFdw2503N: Dual N-Channel 2.5V Specified Powertrench MosfetUlises Juan Huancapaza MachucaNo ratings yet

- IRF740B/IRFS740B: 400V N-Channel MOSFETDocument11 pagesIRF740B/IRFS740B: 400V N-Channel MOSFETMistery of the souldNo ratings yet

- Power Mos V: APT10M25BVFRDocument4 pagesPower Mos V: APT10M25BVFRAlejandro Borrego DominguezNo ratings yet

- 7555 CNDocument9 pages7555 CNdsdsds4No ratings yet

- RF Power Mosfet: N - Channel Enhancement Mode 125V 750W 40MhzDocument4 pagesRF Power Mosfet: N - Channel Enhancement Mode 125V 750W 40MhzDurbha RaviNo ratings yet

- FQP6N60C/FQPF6N60C: 600V N-Channel MOSFETDocument10 pagesFQP6N60C/FQPF6N60C: 600V N-Channel MOSFETBiswajit SarkarNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Analog Dialogue Volume 46, Number 1: Analog Dialogue, #5From EverandAnalog Dialogue Volume 46, Number 1: Analog Dialogue, #5Rating: 5 out of 5 stars5/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- ELSSG12Document14 pagesELSSG12Ariel Anibal AparicioNo ratings yet

- TURNSTILES Full Height Turnstiles Operation & Maintenance GuideDocument25 pagesTURNSTILES Full Height Turnstiles Operation & Maintenance GuideJuan Pablo Diaz FabianNo ratings yet

- Transformer Phase DisplacementDocument5 pagesTransformer Phase Displacement10rodriguezNo ratings yet

- SENSOR Question 1Document7 pagesSENSOR Question 1Jemima ANo ratings yet

- Ch07EN CalibrationsDocument44 pagesCh07EN CalibrationsMounir AngadNo ratings yet

- PMS-DN 2000 MSB-DescriptionDocument8 pagesPMS-DN 2000 MSB-DescriptionTamNo ratings yet

- ArticleMortadi MATPR 2Document5 pagesArticleMortadi MATPR 2Youssef ChatirNo ratings yet

- Company CatalogueDocument10 pagesCompany CataloguePower Tech IndiaNo ratings yet

- Unit 4Document12 pagesUnit 4PrasanthNo ratings yet

- New Askir 23012V BR New Emivac enDocument1 pageNew Askir 23012V BR New Emivac enrafaelNo ratings yet

- Minor ProjDocument42 pagesMinor Projshiva prasadNo ratings yet

- Massage Gun Ebook PDFDocument7 pagesMassage Gun Ebook PDFhamza 4266No ratings yet

- Electrical Design & Implementation Engineer CV WordDocument6 pagesElectrical Design & Implementation Engineer CV WordAlamgeer Abdul RazzaqueNo ratings yet

- Active Currents Power Factor and Apparent Power FoDocument19 pagesActive Currents Power Factor and Apparent Power FoMulugeta AbrhaNo ratings yet

- Integrated Optics-An IntroductionDocument12 pagesIntegrated Optics-An IntroductionaliflailasurumiNo ratings yet

- Perkins 2800 Series Diagnostic ManualDocument10 pagesPerkins 2800 Series Diagnostic Manualkelly100% (63)

- Experiment 7 - Fault AnalysisDocument7 pagesExperiment 7 - Fault AnalysisArvind SriramNo ratings yet

- REN Isl95520 SDS 20150216Document2 pagesREN Isl95520 SDS 20150216jonathan hernandezNo ratings yet

- Northern Power Distribution Company of Telangana LimitedDocument8 pagesNorthern Power Distribution Company of Telangana LimitedMaruthi AilyNo ratings yet

- X Pro1smDocument132 pagesX Pro1smchristianNo ratings yet

- Electrical Technology Lab PracticeDocument2 pagesElectrical Technology Lab PracticeM B Hemanth KumarNo ratings yet

- ADGISDocument52 pagesADGISBlessy JoyNo ratings yet

- 275W Poly CrystallineDocument2 pages275W Poly CrystallineGael Noé TjombNo ratings yet

- Audibax Dallas 72 InstrucionesDocument2 pagesAudibax Dallas 72 InstrucionesFrancisco Martin BurgosNo ratings yet

- HVX Selection List PDFDocument44 pagesHVX Selection List PDFDorelBuzneaNo ratings yet

- DC3000 Series Solid State Lead/Lag Controller With DC Fan ControlDocument5 pagesDC3000 Series Solid State Lead/Lag Controller With DC Fan ControlarmandoNo ratings yet

- ELS 2202 Week 2 (1) .PPT - PpsDocument61 pagesELS 2202 Week 2 (1) .PPT - PpsYohana Crisma LimbongNo ratings yet

- Specifications For LCD Module: Customer Customer Part No. Ampire Part No. AG-12864C Approved by DateDocument18 pagesSpecifications For LCD Module: Customer Customer Part No. Ampire Part No. AG-12864C Approved by Datejose luisNo ratings yet

- Induction Heater Tutorial 10kw and 3kwDocument44 pagesInduction Heater Tutorial 10kw and 3kwSaeid Mir100% (3)