MP1006

MP1006

Uploaded by

luis perdigonCopyright:

Available Formats

MP1006

MP1006

Uploaded by

luis perdigonCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

MP1006

MP1006

Uploaded by

luis perdigonCopyright:

Available Formats

MP1006

OFF LINE CCFL/EEFL CONTROLLER

The Future of Analog IC Technology

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION –TCL USE ONLY

DESCRIPTION FEATURES

The MP1006 is a high performance off-line • 9V Enhanced Gate Driver, Can Directly Drive

CCFL/EEFL controller designed for powering the the Gate Driving Transformer

Cold Cathode Fluorescent Lamp (CCFL) and • Programmable Fixed Operating Frequency

External Electrode Fluorescent Lamp (EEFL), • Input Voltage Range from 9V to 30V

especially for multi-lamp Liquid Crystal Display • Lamp Current and Voltage Regulation

(LCD) backlighting applications. • Burst Mode Dimming Control

The MP1006 utilizes fixed operating frequency • Integrated Burst Mode Oscillator and Modulator

PWM control to the inverter. It outputs two 180 • Soft-On and Soft-Off Burst Envelope

degree phase shifted driving signals for various • Smart Fault Protection Interface

external power stages. Its enhanced 9V gate • Built-in fault management

driver provides adequate driving capability for • Dual Mode Fault Timer

the external MOSFETs. It is able to directly • Programmable Striking Frequency, Striking

drive the external gate driving transformer. The Time and Burst Dimming Frequency

inverter converts unregulated DC voltage to a • Unique Short Circuit Current Limitation

nearly sinusoidal lamp voltage to power up • Available in SOIC 16 Package

CCFL or EEFL lamps.

The MP1006 implements burst mode dimming

APPLICATIONS

to the lamp. Burst mode dimming is controlled • LCD TV and LCD Monitor in Off-line System

with either an external DC voltage or PWM • Flat Panel Video Displays

signal. • Off Line Inverter for CCFL/EEFL driver

The Built-in fault management features include “MPS” and “The Future of Analog IC Technology” are Registered Trademarks of

Monolithic Power Systems, Inc.

open lamp regulation and protection, short circuit

R

The MP1006 is covered by US Patents 6,683,422, 6,316,881, and

protection and over temperature protection. The 6,114,814. Other Patents Pending.

protection interface is flexible for various setups

E

and is easy to use.

The MP1006 is available in a 16-pin SOIC

E

package.

MP1006 Rev.0.9 www.MonolithicPower.com 1

11/27/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2009 MPS. All Rights Reserved.

MP1006—OFF LINE CCFL/EEFL CONTROLLER

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION –TCL USE ONLY

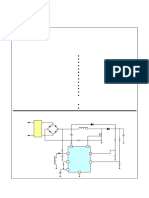

SIMPLIFIED TYPICAL APPLICATION

400V LV1

LI1

MP1006

1 16

OLP OLP GR

2 15

LV LV GND LI2

LV2

3 14

VDRV SLP GL

VDRV

LV3

4 13

LI LI VDRV

LI3

5 12

COMP VIN

11

Y

6

FT EN

7 10

LCC DBRT

L

9 400V GND

8

LCS BOSC

LV4

N

LI4

O

DBRT

LV1

EN LV LV2

LV3

E

VIN

LV4

S

LV1

LI1 LV4

OLP

U

LI LI2

400V LV2

LI3

LV3

400V GND LI4

MP1006 Rev.0.9 www.MonolithicPower.com 2

11/27/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2009 MPS. All Rights Reserved.

MP1006—OFF LINE CCFL/EEFL CONTROLLER

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION –TCL USE ONLY

PACKAGE REFERENCE ABSOLUTE MAXIMUM RATINGS (1)

Input Voltage VIN .......................................... 35V

GL, GR ........................................ -0.3V to 10.7V

Logic Inputs, LV, OLP ................. –0.3V to +6.5V

LI, SLP ........................................ –5.8V to +5.8V

Junction Temperature .............................. 150°C

Lead Temperature (Solder)...................... 260°C

Operating Frequency .............................150KHz

Storage Temperature .............. –55°C to +150°C

(2)

Recommended Operating Conditions

Input Voltage VIN .................................9V to 30V

Y

Operating Frequency ............. 20KHz to 100KHz

Operating Frequency (Typical) ................50KHz

L

Operating Temperature............ –20°C to + 85°C

N

Part Number* Package (3)

Thermal Resistance θJA θJC

MP1006ES SOIC16 SOIC16 ...................................80 ...... 30 ... °C/W

O

Temperature Top Marking

Notes:

–20°C to +85°C MP1006ES 1) Exceeding these ratings may damage the device.

2) The device is not guaranteed to function outside of its

* For Tape & Reel, add suffix –Z (eg. MP1006ES–Z)

E

operating conditions.

For RoHS Compliant Packaging, add suffix –LF (eg. 3) Measured on JESD51-7, 4-layer PCB

MP1006ES–LF–Z)

S

U

ELECTRICAL CHARACTERISTICS

VIN = 12V, TA = +25°C, unless otherwise noted.

Parameter Symbol Condition Min Typ Max Units

Gate driver GL, GR

Gate Pull-Down RGD 2 Ω

Gate Pull-Up RGU 4 Ω

Output Source Current ISOURCE 1 A

Output Sink Current ISINK 2 A

Maximum Duty Cycle DMAX 46%

EN

EN Turn On Threshold VEN-ON 2 V

EN Turn Off Threshold VEN-OFF 1 V

Internal Pull-down Resistor REN-IN 60 kΩ

Brightness Control Range

DBRT Full Scale VDBRT DC burst dimming 1.1 1.2 1.3 V

DBRT Logic Input Threshold VTH-DBRT PWM dimming 1.6 1.9 2.2 V

DBRT Logic Input Hysteresis VTH-DBRT-Hyst PWM dimming 0.3 V

Burst Rate Generator

Source Current ISRC(BRS) VBRS = 2V 120 150 180 µA

Lower Threshold VV(BRS) 2.2 2.4 2.6 V

Upper Threshold VP(BRS) 3.3 3.55 3.8 V

MP1006 Rev.0.9 www.MonolithicPower.com 3

11/27/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2009 MPS. All Rights Reserved.

MP1006—OFF LINE CCFL/EEFL CONTROLLER

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION –TCL USE ONLY

ELECTRICAL CHARACTERISTICS (continued)

VIN = 12V, TA = +25°C, unless otherwise noted.

Parameter Symbol Condition Min Typ Max Units

Supply Current

Supply Current (Enabled) IIN-EN No driver output 1.5 2.5 mA

Supply Current (Disabled) IIN-OFF VIN=30V 1 µA

Operating Frequency fO 25kΩ LCS to GND 46 50 54 kHz

Frequency Set Voltage VLCS 1.1 1.2 1.3 V

Lamp Clock Control (LCC)

Start Sweeping

LCC Enable Threshold VLCC-EN 0.8 0.9 1.0 V

Y

Frequency

At Fault Condition,

L

LCC Source Current ILCC-FT 44 48 51 µA

25kΩ LCS to GND

Frequency Increase Slope ∆F0/∆VLCC 0.9V<VLCC<4.9V 14 15.5 17 kHz/V

N

Lamp Current Feedback (LI)

Magnitude |VLI| 1.13 1.20 1.27 V

O

Sine Equivalent VLI 1.33 Vrms

Input resistance RLI_IN 60 kΩ

E

Lamp Voltage Feedbacks (LV)

Open Lamp Voltage

VTH(LV) 2.2 2.4 2.6 V

S

Feedback Threshold (Peak)

Fault Timer

U

Threshold Vt(FT) 2.2 2.4 2.6 V

Sink Current ISINK(FT) –1 µA

Open Lamp Source Current IPU_OL(FT) 1 µA

Short Lamp Source Current IPU_SL(FT) 100 µA

Comp

Clamp Voltage VCOMP 0.60 V

Reference Current ICOMP+ 20 µA

Reference Current at Fault µA

ICOMP+FT Fault Condition 3.7

Condition

Pull Down Current at Voltage µA

ICOMP-VR LV>2.4V 30

Regulation

Decay Current ICOMP- End of Burst 12 µA

Fault Detection Threshold (OLP, SLP, LI)

OLP Threshold VOLP 2.2 2.4 2.6 V

SLP Threshold VSLP 2.2 2.4 2.6 V

SLP Detection Delay Time TSLP Start when VCOMP>0.9V 400 us

LI threshold VLI 0.55 0.60 0.65 V

LI Detection Delay Time TLI Start when VCOMP>0.9V 400 us

Output Gate Driver (VDRV)

Voltage VVDRV No load 8.7 9.7 10.4 V

Current IVDRV 20 mA

MP1006 Rev.0.9 www.MonolithicPower.com 4

11/27/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2009 MPS. All Rights Reserved.

MP1006—OFF LINE CCFL/EEFL CONTROLLER

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION –TCL USE ONLY

PIN FUNCTIONS

Pin # Name Description

1 OLP Open Lamp Protection Input. A comparator is integrated in this pin for open lamp protection.

If the voltage on this pin gets higher than 2.4V, the open lamp protection will be generated. It

starts the fault timer by sourcing a 1uA current from FT pin, sweeps up the operating

frequency by generating an internal current source flowing out of LCC pin, and disables the

burst dimming.

2 LV Lamp Voltage Feedback Input. The lamp voltage is sensed by this pin through a voltage

divider from the hot end of the lamp to ground. If the voltage at LV exceeds +2.4 V, the

COMP pin voltage is regulated to keep the lamp voltage at a high constant value. At the

same time, the fault protection is triggered and the fault timer is started. The burst dimming is

disabled when fault protection is triggered.

3 SLP Short Lamp Protection Input. A comparator is integrated in this pin for short lamp protection.

Y

If the voltage on this pin gets lower than 2.4V for 400us (counting when VCOMP>0.9V), the

short protection will be generated. It starts the fault timer by sourcing a 100uA current from

FT pin, sweeps up the operating frequency by generating an internal current source flowing

L

out of LCC pin, and disables the burst dimming. The reference for the lamp current feedback

is lowered down to 1/6 in order to limit the short current. The protection function is disabled at

N

burst off interval.

4 LI Lamp Current Feedback Input. Connect this pin to the cold end of the lamp and shunt a

O

sense resistor to ground. The internal error amplifier will sink a current from the COMP pin

proportional to the absolute value of the voltage at this pin. The average of the absolute value

of the voltage at this pin is regulated to 1.2V reference voltage.

The voltage on this pin is also used for open lamp detection and protection. When the voltage

E

on this pin gets lower than 0.6V for 400us (counting when VCOMP>0.9V), the IC recognize this

as open lamp condition and generate a signal to sweep up the operating frequency and

S

disable the burst dimming. At the same time, the fault protection is triggered and fault timer is

started. At burst off interval, the detection and protection are disabled.

U

5 COMP Feedback Compensation Node. Connect a compensation capacitor from this pin to GND.

6 FT Fault Timer. Connect a timing capacitor from this pin to GND to set the fault timeout period.

When the voltage on this pin gets higher than the 2.4V threshold, the IC latches up until EN is

toggled.

7 LCC Lamp Clock Control. The voltage on LCC will control the switching frequency. Connect a

resistor paralleled with a capacitor from this pin to GND. If open lamp or short circuit is

detected, an internal current will source from this pin. The sourcing current is determined by

the LCS pin resistor. The voltage on this pin from 0.9V to 4.9V will linearly increase the

operating frequency by 0 to 61kHz. LCC pin is also a flag that the fault condition is triggered.

8 LCS Lamp Clock Set. Connect a resistor from this pin to GND. This resistor sets the operating

frequency of the MP1006. A 25kOhm resistor sets the operating frequency at typical 50kHz.

9 BOSC Burst Repetition Set. Connect a resistor in parallel with a capacitor from BOSC to GND. The

resistor and capacitor programs the burst repetition rate and the minimum burst duty cycle. If

the burst dimming is to be controlled by an external logic signal, pull up BOSC to VDRV

through a 20kΩ resistor and apply the logic signal to the DBRT pin.

10 DBRT Burst-Mode (Digital) Brightness Control Input. The voltage range from 0 V to 1.2V at DBRT

linearly sets the burst-mode duty cycle from the minimum duty to 100%. For external PWM

input dimming, directly apply the logic signal on this pin. The MP1006 has positive dimming

polarity.

11 EN Enable Input. Pull EN high to turn on the chip, and pull EN low to turn it off.

MP1006 Rev.0.9 www.MonolithicPower.com 5

11/27/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2009 MPS. All Rights Reserved.

MP1006—OFF LINE CCFL/EEFL CONTROLLER

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION –TCL USE ONLY

PIN FUNCTIONS (continued)

Pin # Name Description

12 VIN Supply voltage input.

13 VDRV Linear Regulator Output and Bias Supply of the Gate Driver. It provides the supply for the

gate driver and also the external control circuit, the typical value is 9.7V. Bypass VDRV with a

1μF or larger ceramic capacitor.

14 GL Driving signal output, 180 degree phase shifted of GR

15 GND Ground.

16 GR Driving signal output, 180 degree phase shifted of GL

Y

OPERATION

L

6 FT

N

1 OLP

2.4V VDRV

O

3 SLP

2.4V Fault

Management GL 14

2 C

E

LV Gate

2.4V O Driver

N

S

0.6V

4 T

LI

R

U

O

Error L

1.2V Amplifier VDRV

0.2V at short L

Lamp

5 COMP

PWM O

G 16

GR

8 LCS I Gate

Lamp Driver

7 Clock

C

LCC 15

GND

9 BOSC

Burst

Rate

Generater

10 DBRT VIN 12 VIN

Regulator

11 EN

VDRV 13

Figure 1—MP1006 Block Diagram

MP1006 Rev.0.9 www.MonolithicPower.com 6

11/27/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2009 MPS. All Rights Reserved.

MP1006—OFF LINE CCFL/EEFL CONTROLLER

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION –TCL USE ONLY

DESIGN INFORMATION duty cycle. When burst dimming with external

PWM signal, pull up BOSC pin to VDRV through

Steady State and Enable Control

a 20kΩ resistor and apply the PWM signal on

The MP1006 is a fixed operating frequency off- DBRT pin.

line inverter controller specifically designed for

Fault Protection

the backlighting of multiple lamp liquid crystal

displays (LCD). Powered by 9V to 30V input System fault management facilities include the

supplies, the MP1006 outputs two 180 degree on-chip open-lamp detector and regulator, a dual

phase shifted driving signals for the external mode fault timer and two smart comparators for

power stages. Its enhanced 9V gate driver open lamp and short circuit protection.

provides adequate driving capability to the

The lamp voltage is monitored by the LV pin

external MOSFETs. It is able to directly drive the

through a capacitor divider, once the voltage on

external gate driving transformer.

LV pin exceed 2.4V reference, the MP1006 will

The operating frequency is set by an external pull down the COMP voltage by a current pulse

Y

resistor to minimize the possibility of interference and reduce the power delivering to the power

with the refresh rate of the display. The operating stage. Thus smoothly and stably regulate the

L

frequency can be set by the resistor connected lamp voltage to a user programmed striking

from LCS pin to GND. voltage. At the same time when LV pin voltage

N

hits the 2.4V threshold, the Open Lamp Mode is

The lamp striking frequency under open lamp

triggered.

condition is programmed by the LCC pin. The

O

voltage on LCC in range of 0.9~4.9V linearly At Open Lamp Mode, the IC generates an

increases the operating frequency by 0 to 61kHz. internal current source flowing out of the LCC pin.

When LCC voltage is lower than 0.9V, the Together with the resistor connected from LCC to

E

operating frequency is not influenced. GND, a user programmed voltage is generated,

which linearly increases the operating frequency.

S

The MP1006 utilizes PWM control to the inverter.

The LCC pin voltage in range of 0.9~4.9V linearly

The lamp current is sensed at LI pin and compared

programs the frequency increase by 0 to 61kHz.

with internal reference. The internal error amplifier

U

The LCC pin internal current source is

generates the error signal on COMP pin to control

determined by the LCS pin resistor. And the

the PWM duty cycle. The full-wave lamp current

capacitor on LCC pin helps to program the

sense amplifier provides superior output pulse

frequency sweeping speed. Meanwhile, a 1uA

symmetry and loop response time.

current source will charge the FT cap. If the

The system power is controlled by EN pin. When voltage on FT pin exceeds 2.4V, the controller

the chip is enabled, the built-in regulator for VDRV will shutdown and latch until the EN pin is toggled

is powered up and the internal circuit starts. to restart the IC. Choose a proper capacitor on

FT pin to obtain a desired timeout. In normal

Brightness Control

condition a 1μA sink current keeps the FT pin at

MP1006 implements burst dimming (digital 0V. During Open Lamp Mode, the IC ignores the

brightness) of the lamp. Burst mode operation burst control and runs continuously to ensure

dims the lamp by modulating the duty cycle of a either the lamp has a chance to re-ignite or the

burst of AC lamp current and features soft- fault timer can smoothly and accurately time out.

on/soft-off control of the lamp current envelope.

The MP1006 has a built-in burst oscillator which The lamp current feedback LI pin also functions

can generate a triangle waveform on the BOSC as the open lamp detection. If the peak voltage

pin. Burst dimming can be achieved by either a on LI pin is lower than 0.6V for 400us (count

DC voltage input or external PWM signal. When when VCOMP>0.9V), the IC recognizes the lamp is

burst dimming with a DC input voltage, add a open, and triggers the Open Lamp Mode. At

capacitor in parallel with a resistor on BOSC pin burst dimming off interval, the fault detection on

to set the burst frequency and apply the DC LI pin is disabled.

voltage on the DBRT pin to program the burst

MP1006 Rev.0.9 www.MonolithicPower.com 7

11/27/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2009 MPS. All Rights Reserved.

MP1006—OFF LINE CCFL/EEFL CONTROLLER

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION –TCL USE ONLY

Two smart comparators are integrated for the

open lamp and short circuit protection. It

simplifies the protection design in multiple lamps

application.

The OLP pin is used for open lamp protection.

When the voltage on OLP pin is higher than 2.4V,

the IC recognizes this as open lamp condition

and triggers the Open Lamp Mode.

The SLP pin is used for short lamp protection.

When the voltage on SLP pin is lower than 2.4V

for 400us (count when VCOMP>0.9V), the IC

recognizes it as short lamp condition and triggers

Y

the Short Lamp Mode. At burst dimming off

L

interval, the fault detection on SLP pin is disabled.

At Short Lamp Mode, the IC also charges up the

N

LCC pin to sweep up the frequency and ignores

the burst dimming. It starts the short mode fault

timer by sourcing a 100uA current to charge the

O

FT capacitor, which is 100 times faster than that

in the Open Lamp Mode. During Short Lamp

Mode, the internal current feedback reference is

E

reduced to 1/6 of the normal value, which helps

for limiting the short circuit current to meet the

S

safety requirement.

MP1006 Rev.0.9 www.MonolithicPower.com 8

11/27/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2009 MPS. All Rights Reserved.

MP1006—OFF LINE CCFL/EEFL CONTROLLER

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION –TCL USE ONLY

APPLICATION INFORMATION Pin 5 (COMP):

Pin 1 (OLP): This pin is used for compensation. Connect a

1~4.7nF capacitor from COMP to GND. This cap

Open Lamp Protection: This pin is used for open should be X7R ceramic. The value of this cap

lamp protection, when the voltage on this pin is determines the stability of the lamp current

higher than 2.4V, the IC recognize this as open regulation and open lamp voltage regulation. It

lamp condition and triggers Open Lamp Mode. also affects the soft-on rise time and soft-off fall

Connect the signals which can indicate open time at burst dimming.

lamp condition to this pin. The maximum lamp

voltage, the maximum lamp voltage difference or Pin 6 (FT):

the maximum lamp current difference are usually Connect a capacitor from this pin to GND to set

used to indicate the open lamp condition. the fault timer.

Pin 2 (LV): Open Lamp Time Out:

Open Lamp Voltage Regulation: This pin is used t OPEN LAMP × 1μA

C1 =

for open lamp voltage regulation and open lamp 2.4V

Y

protection. When the voltage on this pin exceeds

2.4V, an internal current source will discharge For a C1 = 1uF, then the time out for open lamp

L

COMP to regulate the open lamp voltage. The will be 2.4 sec.

regulated open lamp voltage is proportional to Short lamp Timeout: When Short Lamp Mode is

N

the ratio of the voltage divider in the voltage triggered, the IC charges the FT cap with 100uA

feedback. When LV voltage hits 2.4V, the IC current. The short lamp timeout is about 1/100 of

recognizes this as open lamp condition and the open lamp timeout. To further reduce the

O

triggers Open Lamp Mode. short lamp timeout, modify the network at the FT

Pin 3 (SLP): pin as shown in Figure 2.

E

Short Lamp Protection: This pin is used for short FT

lamp protection, when the voltage on this pin

S

gets lower than 2.4V for 400us (Count when C2A C2B

VCOMP>0.9V), the IC takes it as short lamp

U

condition and triggers Short Lamp Mode. The

minimum lamp voltage is usually used to indicate

the short lamp condition. Figure 2—Timeout Adjustment

Pin 4 (LI): For C2B = 100nF, then the short lamp timeout is

as short as 2.4ms.

Lamp Current Regulation: This pin is used for

Current regulation. The lamp current is fed back Note: The open lamp time out will remain the

to the LI pin. The absolute voltage on this pin is same value as defined by C2A.

regulated with 1.2V average value. For the

Pin 8 (LCS):

sinusoid waveform on this pin, its RMS value is

regulated to 1.33Vrms. At Short Lamp Mode, the Connect a resistor from this pin to GND to set

reference voltage for LI is reduced to 0.2V (1/6) the lamp operating frequency (fo). The value for

to limit the short circuit current. this resistor R1 is calculated by

LI pin also functions as open lamp detection, 1.25 × 10 9

when the voltage on this pin gets lower than 0.6V R1 =

for 400us (count when VCOMP>0.9V), the IC fo

recognizes this as open lamp condition and For R1 = 25kΩ, operating clock will be 50kHz.

triggers Open Lamp Mode.

MP1006 Rev.0.9 www.MonolithicPower.com 9

11/27/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2009 MPS. All Rights Reserved.

MP1006—OFF LINE CCFL/EEFL CONTROLLER

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION –TCL USE ONLY

Pin 7 (LCC): PWM signal. Logic High is Burst On and a logic

Low is Burst Off.

This pin is used to program the striking frequency

at open lamp condition. The voltage on this pin in Pin 9 (BOSC):

range of 0.9V~4.9V increases the operating

BOSC pin is used to set the burst dimming

frequency by 0~61 kHz, as shown in figure 3.

frequency. Connect a resistor (R2) in parallel with

a capacitor (C3) on this pin to set the burst

dimming frequency and the minimum burst on

time: tMIN, as shown in figure 4.

Y

Figure 3—Striking Frequency vs. LCC Voltage

L

At Open Lamp Mode or Short Lamp Mode, an

internal current source flows out of this pin. With

N

a resistor in parallel with a capacitor on this pin,

the IC softly sweeps up the striking frequency.

O

The resistor determines the striking frequency

value and the capacitor determines the sweeping

speed. It helps to establish the striking voltage to Figure 4—Burst Mode with DC Input Voltage

E

ignite the lamp and also helps to eliminate the at DBRT Pin

voltage spike by its soft sweeping.

Set tMIN to achieve the minimum required system

S

The LCC voltage is:

brightness. Ensure that tMIN is long enough that

1.2V the lamp does not extinguish.

V LCC = × RLCC

U

RLCS

These values are determined as follows:

The striking frequency is:

Fstrike = Fop + (VLCC − 0.9) × 15.5 × 10 3 Select a Minimum Duty Cycle, DMIN, where:

The sweeping frequency can also be D MIN = t MIN × fBurst

programmed externally by applying a voltage to R2 and C3 are determined by:

LCC pin. At this condition, connect a 100Ω

resistor on LCC pin to limit the flowing out current. ⎛ 1 ⎞

R 2 ≈ 21.16k ⎜⎜ − 1⎟⎟ + 21.43k

Pin 10 (DBRT): ⎝ DMIN ⎠

This pin is used for burst brightness control. For

1 − DMIN

C3 =

DC input burst dimming, the DC voltage on this f Burst × R 2 × 0.405

pin controls the burst percentage on the output. For DMIN = 0.1, fBurst = 200Hz, then R2 = 212k, C3 =

The signal is filtered for optimal operation. A voltage 52nF

ranging from 0 to 1.2V on DBRT programs the For direct PWM burst dimming, pull BOSC high

burst dimming duty cycle from the minimum duty to VDRV through a 20kΩ resistor and apply the

cycle to 100%. PWM signal to DBRT pin.

For direct Pulse Width Modulation (PWM) burst

dimming, Pull BOSC high to VDRV through a

20kΩ resistor and connect DBRT to a logic level

MP1006 Rev.0.9 www.MonolithicPower.com 10

11/27/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2009 MPS. All Rights Reserved.

MP1006—OFF LINE CCFL/EEFL CONTROLLER

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION –TCL USE ONLY

Pin 13 (VDRV):

Table 1—Function Mode

This pin provides the gate driver supply voltage,

Pin Connection

Function its typical value is 9.7V. Connect a 1uF or greater

DBRT BOSC ceramic capacitor on this pin to bypass the

Burst Mode with supply voltage. This voltage is also used to

0V to 1.2V C3, R2

DC Input Voltage supply the external control circuit.

To VDRV

Burst Mode with Pin 14(GL), Pin 16 (GR):

PWM through 20kΩ

External Source

resistor Gate driving signals output. GL and GR are 180

Burst Brightness Polarity: 100% duty cycle at degree phase shifted driving signals. With its

DBRT voltage 1.2V. enhanced driving capability, GL and GR are able

to directly drive the externally MOSFET in the off-

Pin 11 (EN): line system through a gate driving transformer.

Pull this pin high to enable the chip, and pull it Connect two 5Ω resistors in series with GL and

low to disable the chip. GR to eliminate the EMI noise injected to the IC.

Y

Pin 12 (VIN):

Supply voltage input. By pass the supply voltage

L

with a 0.1uF or greater ceramic cap. This cap

should be placed close to the IC.

N

O

S E

U

MP1006 Rev.0.9 www.MonolithicPower.com 11

11/27/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2009 MPS. All Rights Reserved.

LY

N

O

S E

U

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION –TCL USE ONLY

P1006—OFF LINE CCFL/EEFL CONTROLLER

M

MP1006—OFF LINE CCFL/EEFL CONTROLLER

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION –TCL USE ONLY

LY

N

O

S E

U

Figure 6—MP1006 400V EEFL Driver for 32” Panel

MP1006 Rev. 0.9 www.MonolithicPower.com 13

11/27/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2009 MPS. All Rights Reserved.

MP1006—OFF LINE CCFL/EEFL CONTROLLER

MPS CONFIDENTIAL AND PROPRIETARY INFORMATION –TCL USE ONLY

Y

PACKAGE INFORMATION

SOIC16

0.386( 9.80)

0.394(10.00) 0.024(0.61) 0.050(1.27)

16 9

0.063

(1.60)

0.150 0.228

(3.80) (5.80) 0.213

PIN 1 ID 0.157 0.244 (5.40)

(4.00) (6.20)

1 8

TOP VIEW RECOMMENDED LAND PATTERN

0.053(1.35)

0.069(1.75)

SEATING PLANE 0.0075(0.19)

0.0098(0.25)

0.013(0.33) 0.050(1.27) 0.004(0.10)

0.020(0.51) BSC 0.010(0.25) SEE DETAIL "A"

FRONT VIEW SIDE VIEW

NOTE:

0.010(0.25)

x 45o

0.020(0.50) 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN

BRACKET IS IN MILLIMETERS.

GAUGE PLANE 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH,

0.010(0.25) BSC PROTRUSIONS OR GATE BURRS.

3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH

OR PROTRUSIONS.

4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING)

0.016(0.41) SHALL BE 0.004" INCHES MAX.

0o-8o 0.050(1.27) 5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION AC.

6) DRAWING IS NOT TO SCALE.

DETAIL "A"

NOTICE: The information in this document is subject to change without notice. Users should warrant and guarantee that third

party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not

assume any legal responsibility for any said applications.

MP1006 Rev. 0.9 www.MonolithicPower.com 14

11/27/2008 MPS Proprietary Information. Unauthorized Photocopy and Duplication Prohibited.

© 2009 MPS. All Rights Reserved.

You might also like

- Pub - Voltage Regulators For Next Generation Microproces PDFDocument421 pagesPub - Voltage Regulators For Next Generation Microproces PDFArtur ZaidullinNo ratings yet

- Nu-Pulse, Half-Bridge and Push-Pull CCFL Inverter ControllerDocument12 pagesNu-Pulse, Half-Bridge and Push-Pull CCFL Inverter ControllerRicardo PiovanoNo ratings yet

- General Description Features: 380Khz, 18V/2A Synchronous Step-Down DC-DC ConverterDocument19 pagesGeneral Description Features: 380Khz, 18V/2A Synchronous Step-Down DC-DC Converteroscar1162001No ratings yet

- Switching From The L6561 To The L6562: AN1757 Application NoteDocument9 pagesSwitching From The L6561 To The L6562: AN1757 Application Notedeilyn rivasNo ratings yet

- Halogen 12vDocument17 pagesHalogen 12veryNo ratings yet

- S Feature D Escriptio: LTC1163/LTC1165 Triple 1.8V To 6V High-Side MOSFET DriversDocument8 pagesS Feature D Escriptio: LTC1163/LTC1165 Triple 1.8V To 6V High-Side MOSFET DriversPablo LloveraNo ratings yet

- Transition-Mode PFC Controller With Fault Condition ProtectionDocument16 pagesTransition-Mode PFC Controller With Fault Condition ProtectionAdailton SantosNo ratings yet

- Transition-Mode PFC Controller With Fault Condition ProtectionDocument20 pagesTransition-Mode PFC Controller With Fault Condition ProtectionMega BoxNo ratings yet

- Design Consideration With AP3041: Application Note 1059Document6 pagesDesign Consideration With AP3041: Application Note 1059subisanNo ratings yet

- AL3066 DiodesDocument14 pagesAL3066 Diodesivan ivanovNo ratings yet

- Full Bridge CCFL Controller: The Future of Analog IC TechnologyDocument12 pagesFull Bridge CCFL Controller: The Future of Analog IC TechnologyRichu UhcirNo ratings yet

- Surge Stopping and Reverse Voltage Protection With The LM5069 PDFDocument7 pagesSurge Stopping and Reverse Voltage Protection With The LM5069 PDFĐỗ Văn ThủyNo ratings yet

- MP3391 r1.12Document18 pagesMP3391 r1.12Elsa Nababan EchaNo ratings yet

- MP3391Document18 pagesMP3391Raul AlfaroNo ratings yet

- Tle6250 v34 Can BusDocument28 pagesTle6250 v34 Can BusBer HonzaNo ratings yet

- Lm3280 Adjustable Step-Down DC-DC Converter and 3 Ldos For RF Power ManagementDocument26 pagesLm3280 Adjustable Step-Down DC-DC Converter and 3 Ldos For RF Power ManagementAdi PopaNo ratings yet

- Lm3280 Adjustable Step-Down DC-DC Converter and 3 Ldos For RF Power ManagementDocument27 pagesLm3280 Adjustable Step-Down DC-DC Converter and 3 Ldos For RF Power ManagementEliecer MenesesNo ratings yet

- 1310 FsDocument12 pages1310 FsMohamed HaddadNo ratings yet

- Flyback Controller Improves Cross Regulation For Multiple Output ApplicationsDocument2 pagesFlyback Controller Improves Cross Regulation For Multiple Output Applications邹昊芃No ratings yet

- Ds8204a 05Document19 pagesDs8204a 05marcelo Chiu LeonNo ratings yet

- Schema Electrica Convertor 2Vcc in 30VccDocument16 pagesSchema Electrica Convertor 2Vcc in 30VccDragos DragoshNo ratings yet

- Green-Mode PWM Controller With High-Voltage Start-Up CircuitDocument17 pagesGreen-Mode PWM Controller With High-Voltage Start-Up Circuitserrano.flia.coNo ratings yet

- Datasheet AP7175Document14 pagesDatasheet AP7175Edwin SorianoNo ratings yet

- Lps 5 eDocument8 pagesLps 5 eArifin IpinNo ratings yet

- Low Power Pulse Width Modulator: Description FeaturesDocument12 pagesLow Power Pulse Width Modulator: Description FeaturespatrykNo ratings yet

- MC145406 PDocument10 pagesMC145406 PpoindextNo ratings yet

- An1624 stsr3 Simplifies Implementation of Synchronous Rectifier in Flyback Converter StmicroelectronicsDocument22 pagesAn1624 stsr3 Simplifies Implementation of Synchronous Rectifier in Flyback Converter Stmicroelectronicsluuk.wNo ratings yet

- Features Descriptio: LT1080/LT1081 Advanced Low Power 5V RS232 Dual Driver/ReceiverDocument13 pagesFeatures Descriptio: LT1080/LT1081 Advanced Low Power 5V RS232 Dual Driver/ReceiverahmedNo ratings yet

- OB3372 On BrightDocument13 pagesOB3372 On BrightPedro Leandro SilvaNo ratings yet

- MPS MP1038 PDFDocument1 pageMPS MP1038 PDFAnas KaruniaNo ratings yet

- Descriptio Features: LT1505 Constant-Current/Voltage High Efficiency Battery ChargerDocument16 pagesDescriptio Features: LT1505 Constant-Current/Voltage High Efficiency Battery ChargerCarlos Henrique RibasNo ratings yet

- A4954 Datasheet PDFDocument9 pagesA4954 Datasheet PDFJason WuNo ratings yet

- Ap5004 Ap5004sg-13Document12 pagesAp5004 Ap5004sg-13carixo98No ratings yet

- 1154 FCDocument18 pages1154 FCZekeZer0xNo ratings yet

- Ucc 25701Document23 pagesUcc 25701hotelmogador.recNo ratings yet

- Advanced Voltage Mode Pulse Width Modulator: Description FeaturesDocument24 pagesAdvanced Voltage Mode Pulse Width Modulator: Description Featuresvanhuong87No ratings yet

- Complete DDR3/ DDR4 Memory Power Solution Controller: General Description FeaturesDocument15 pagesComplete DDR3/ DDR4 Memory Power Solution Controller: General Description FeaturesIgor LabutinNo ratings yet

- MP4012Document17 pagesMP4012Ba RownaNo ratings yet

- Datasheet - HK lp6253 8406861Document11 pagesDatasheet - HK lp6253 8406861Boban CvetkovicNo ratings yet

- RT8204-DS8204-06 Single Synchronous Buck With LDO ControllerDocument19 pagesRT8204-DS8204-06 Single Synchronous Buck With LDO ControllerMaks ProstNo ratings yet

- Dying Gasp Storage and Release Control IC: Description FeaturesDocument13 pagesDying Gasp Storage and Release Control IC: Description FeaturesSALAH NETNo ratings yet

- ACS37800 DatasheetDocument48 pagesACS37800 Datasheetvenkatb7No ratings yet

- LD7522Document18 pagesLD7522uyfcastellNo ratings yet

- UC3842 Current-Mode PWM Controller: Description Pin ConfigurationsDocument8 pagesUC3842 Current-Mode PWM Controller: Description Pin ConfigurationsGabriel RacovskyNo ratings yet

- 3842 PDFDocument8 pages3842 PDFSandro JoséNo ratings yet

- LSP5526Document17 pagesLSP5526Hadi Habibi ShahandashtiNo ratings yet

- Uc3842 PDFDocument8 pagesUc3842 PDFPutri RahmanieNo ratings yet

- Img 020201217155511Document15 pagesImg 020201217155511Jose PerezNo ratings yet

- SSL1623PH: 1. General DescriptionDocument15 pagesSSL1623PH: 1. General Descriptionapi-19914243No ratings yet

- Single Wire CAN-Transceiver Final Data Sheet TLE 6255 G: 1 FeaturesDocument23 pagesSingle Wire CAN-Transceiver Final Data Sheet TLE 6255 G: 1 Features高立璋No ratings yet

- LD 7550Document15 pagesLD 7550Evanier Souza de AlencarNo ratings yet

- DatasheetDocument10 pagesDatasheetmartin andres rodriguez rengifoNo ratings yet

- 1374fdDocument32 pages1374fdOsires Regis CoimbraNo ratings yet

- Hx3589fh CiDocument50 pagesHx3589fh CiRildoNo ratings yet

- Power Factor Corrector: Minidip SO8 Ordering Numbers: L6561 (Minidip) L6561D (SO8)Document11 pagesPower Factor Corrector: Minidip SO8 Ordering Numbers: L6561 (Minidip) L6561D (SO8)Karim CocasNo ratings yet

- High Efficiency 3A, 16V, 500Khz Synchronous Step Down ConverterDocument15 pagesHigh Efficiency 3A, 16V, 500Khz Synchronous Step Down ConverterkadirovNo ratings yet

- Fan5009-298322 DICONSEDocument14 pagesFan5009-298322 DICONSEDaniel Norberto DemariaNo ratings yet

- Automotive ISO 9141 Serial Link Driver: MC33199 SemiconductorDocument12 pagesAutomotive ISO 9141 Serial Link Driver: MC33199 SemiconductorromoNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- 10-kW, Three-Level, Three-Phase T-Type Inverter Reference Design For Solar String InvertersDocument38 pages10-kW, Three-Level, Three-Phase T-Type Inverter Reference Design For Solar String InvertersJhonatan Leandro Clavijo TrochesNo ratings yet

- Traction Inverter: ST New SolutionsDocument12 pagesTraction Inverter: ST New SolutionsN SUJENDRANo ratings yet

- Trinamic Motor Drive ControllerDocument96 pagesTrinamic Motor Drive Controllerwert1a2No ratings yet

- Mosfet Gate DriveDocument6 pagesMosfet Gate DrivegubiliNo ratings yet

- Tiduey 2Document28 pagesTiduey 2Muzaffar MahmoodNo ratings yet

- LM5106 100-V Half-Bridge Gate Driver With Programmable Dead-TimeDocument26 pagesLM5106 100-V Half-Bridge Gate Driver With Programmable Dead-TimeRavi JagtianiNo ratings yet

- MC33486Document9 pagesMC33486NoelNo ratings yet

- Motor Drive Solutions Guide PDFDocument20 pagesMotor Drive Solutions Guide PDFfordNo ratings yet

- 2019 Led LCD T-2-1 PDFDocument70 pages2019 Led LCD T-2-1 PDFDiego Correa100% (2)

- 5V/12V Synchronous Buck PWM DC-DC and Linear Power ControllerDocument18 pages5V/12V Synchronous Buck PWM DC-DC and Linear Power Controllerraed hasaniaNo ratings yet

- Identifying and Mitigating The Problems PDFDocument4 pagesIdentifying and Mitigating The Problems PDFxvehicleNo ratings yet

- Gate Driver For N-Channel Mosfet: Experiment 6Document34 pagesGate Driver For N-Channel Mosfet: Experiment 6Noona MigleiNo ratings yet

- 48-V Battery Powered Inverter Power Stage Reference Design For 5-kW Forklift AC Traction MotorDocument35 pages48-V Battery Powered Inverter Power Stage Reference Design For 5-kW Forklift AC Traction Motorsandeep sNo ratings yet

- Three-Phase Inverter Reference Design Using Gate Driver With Built-In Dead Time InsertionDocument28 pagesThree-Phase Inverter Reference Design Using Gate Driver With Built-In Dead Time InsertionWilliam BelascoNo ratings yet

- drv8301 BLDCDocument39 pagesdrv8301 BLDCAgung DuemilanoveNo ratings yet

- Highly Compact Isolated Gate Driver With Ultrafast Overcurrent Protection For 10 KV SiC MOSFETsDocument14 pagesHighly Compact Isolated Gate Driver With Ultrafast Overcurrent Protection For 10 KV SiC MOSFETsDaniel ToledoNo ratings yet

- DRV 8701Document43 pagesDRV 8701P SNo ratings yet

- Um2932 Getting Started With The Aekmot3p99081 Cancontrolled Brushless Motor Evaluation Board Based On spc560p and l9908 StmicroelectronicsDocument62 pagesUm2932 Getting Started With The Aekmot3p99081 Cancontrolled Brushless Motor Evaluation Board Based On spc560p and l9908 Stmicroelectronicsbofid61905No ratings yet

- Tea1995t (Lta1716)Document18 pagesTea1995t (Lta1716)Adilson SilvérioNo ratings yet

- Esab Arc4000i Tig4000i Mig4000iDocument78 pagesEsab Arc4000i Tig4000i Mig4000iliviucatalinNo ratings yet

- Ti IsolatorDocument21 pagesTi IsolatormimramesNo ratings yet

- Control Integrated Power System (Cipos™) : Ikcs12F60F2A Ikcs12F60F2CDocument19 pagesControl Integrated Power System (Cipos™) : Ikcs12F60F2A Ikcs12F60F2CJorge CarranzaNo ratings yet

- A High-Speed Gate Driver With PCB-EmbeddedRogowski Switch-Current Sensor For A 10 KV, 240A, SiC MOSFET ModuleDocument6 pagesA High-Speed Gate Driver With PCB-EmbeddedRogowski Switch-Current Sensor For A 10 KV, 240A, SiC MOSFET Moduleu.s.routNo ratings yet

- Max17126 Max17126a PDFDocument34 pagesMax17126 Max17126a PDFVukica IvicNo ratings yet

- Paralleling of IGBT Modules - 5SYA 2098 - 25082013Document10 pagesParalleling of IGBT Modules - 5SYA 2098 - 25082013JoseNo ratings yet

- Evaluation Board EVAL-1EDI20H12AH-SIC / EVAL-1EDC20H12AH-SICDocument21 pagesEvaluation Board EVAL-1EDI20H12AH-SIC / EVAL-1EDC20H12AH-SICbharath prabhuNo ratings yet

- A Generalized Double Pulse Test With Potential Short Circuit Protection For SiC MOSFETDocument70 pagesA Generalized Double Pulse Test With Potential Short Circuit Protection For SiC MOSFETJosé Francisco Gallardo OjedaNo ratings yet

- Demonstration Board For STDRIVE601 Triple Gate Driver: Evalstdrive601Document10 pagesDemonstration Board For STDRIVE601 Triple Gate Driver: Evalstdrive601amadNo ratings yet

- An 6076Document13 pagesAn 6076Kannabhiran Arumugam100% (1)