FAN4822

FAN4822

Uploaded by

40818248Copyright:

Available Formats

FAN4822

FAN4822

Uploaded by

40818248Original Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

FAN4822

FAN4822

Uploaded by

40818248Copyright:

Available Formats

www.fairchildsemi.

com

FAN4822

ZVS Average Current PFC Controller

Features General Description

• Average current sensing, continuous boost, leading edge The FAN4822 is a PFC controller designed specifically for

PFC for low total harmonic distortion and near unity high power applications. The controller contains all of the

power factor functions necessary to implement an average current boost

• Built-in ZVS switch control with fast response for high PFC converter, along with a Zero Voltage Switch (ZVS) con-

efficiency at high power levels troller to reduce diode recovery and MOSFET turn-on

• Average line voltage compensation with brownout control losses.

• Current fed gain modulator improves noise immunity and

provides universal input operation The average current boost PFC circuit provides high power

• Overvoltage comparator eliminates output “runaway” due factor (>98%) and low Total Harmonic Distortion (THD).

to load removal Built-in safety features include undervoltage lockout, over-

• UVLO, current limit, and soft-start voltage protection, peak current limiting, and input voltage

• Precision 1.3% reference brownout protection.

The ZVS control section drives an external ZVS MOSFET

which, combined with a diode and inductor, soft switches the

boost regulator. This technique reduces diode reverse recov-

ery and MOSFET switching losses to reduce EMI and maxi-

mize efficiency.

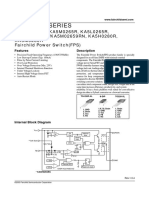

Block Diagram

1 8 2

VEAO GND IEAO

FB

VEA VCC

14 –

OVP VCCZ 12

+ FB +

2.5V R+ 13.5V

IEA

+ 2.7V –

IAC +

4 GAIN –

MODULATOR –

VRMS S Q

5 R– I LIMIT

ISENSE –1V + R

3 –

PFC OUT

RTCT 11

6 OSC S Q

VCCZ

R Q

REF ZVS OUT

13 REF 10

+ S Q

ZV SENSE

7 –– PWR GND

R Q 9

REV. 1.0.1 8/10/01

FAN4822 PRODUCT SPECIFICATION

Pin Configuration

FAN4822 FAN4822

14-Pin DIP (P14) 16-Pin SOIC (S16W)

VEAO 1 14 FB VEAO 1 16 FB

IEAO 2 13 REF IEAO 2 15 REF

ISENSE 3 12 VCC ISENSE 3 14 VCC

IAC 4 11 PFC OUT IAC 4 13 PFC OUT

VRMS 5 10 ZVS OUT VRMS 5 12 ZVS OUT

RTCT 6 9 PWR GND RTCT 6 11 PWR GND

ZV SENSE 7 8 GND ZV SENSE 7 10 GND

TOP VIEW N/C 8 9 N/C

TOP VIEW

Pin Description (Pin numbers is parentheses are for 16-pin package)

Pin Name Function

1 (1) VEAO Transconductance voltage error amplifier output.

2 (2) IEAO Transconductance current error amplifier output.

3 (3) ISENSE Current sense input to the PFC current limit comparator.

4 (4) IAC PFC gain modulator reference input.

5 (5) VRMS Input for RMS line voltage compensation.

6 (6) RTCT Connection for oscillator frequency setting components.

7 (7) ZV SENSE Input to the high speed zero voltage crossing comparator.

8 (10) GND Analog signal ground.

9 (11) PWR GND Return for the PFC and ZVS driver outputs.

10 (12) ZVS OUT ZVS MOSFET driver output.

11 (13) PFC OUT PFC MOSFET driver output.

12 (14) VCC Shunt-regulated supply voltage.

13 (15) REF Buffered output for the internal 7.5V reference.

14 (16) FB Transconductance voltage error amplifier input.

Absolute Maximum Ratings

Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum rat-

ings are stress ratings only and functional device operation is not implied.

Parameter Min Max Unit

Shunt Regulator Current (ICC) 55 mA

Peak Driver Output Current ±500 mA

Analog Inputs –0.3 7 V

Junction Temperature 150 °C

Storage Temperature Range –65 150 °C

Lead Temperature (Soldering, 10 sec) 150 °C

Thermal Resistance (θJA)

Plastic DIP 80 °C/W

Plastic SOIC 110 °C/W

2 REV. 1.0.1 8/10/01

PRODUCT SPECIFICATION FAN4822

Operating Conditions

Temperature Range Min. Max. Units

FAN4822IX –40 85 °C

Electrical Characteristics

Unless otherwise specified, RT = 52.3kΩ, CT = 470pF, TA = Operating Temperature Range (Note 1)

Parameter Conditions Min. Typ. Max. Units

Voltage Error Amplifier

Input Voltage Range 0 7 V

Ω

Transconductance VNON-INV = VINV, VEAO = 3.75V 50 70 120 µ

Feedback Reference Voltage VEAO = VFB 2.4 2.5 2.6 V

Open Loop Gain 60 75 dB

PSRR VCCZ – 3V < VCC < VCCZ – 0.5V 60 75 dB

Output Low 0.65 1 V

Output High 6.0 6.7 V

Source Current ∆VIN = ±0.5V, VOUT = 6V –40 –80 µA

Sink Current ∆VIN = ±0.5V, VOUT = 1.5V 40 80 mA

Current Error Amplifier

Input Voltage Range –1.5 2 V

Ω

Transconductance VNON-INV = VINV, IEAO = 3.75V 130 195 310 µ

Input Offset Voltage ±3 ±15 mV

Open Loop Gain 60 75 dB

PSRR VCCZ – 3V < VCC < VCCZ – 0.5V 60 75 dB

Output Low 0.65 1 V

Output High 6.0 6.7 V

Source Current ∆VIN = ±0.5V, VOUT = 6V –30 –80 µA

Sink Current ∆VIN = ±0.5V, VOUT = 1.5V 40 80 µA

OVP Comparator

Threshold Voltage 2.6 2.7 2.8 V

Hysteresis 80 120 150 mV

ISENSE Comparator

Threshold Voltage –0.8 –1.0 –1.15 V

Delay to Output 150 300 ns

ZV Sense Comparator

Propagation Delay 100mV Overdrive 50 ns

Threshold Voltage 7.35 7.5 7.65 V

Input Capacitance 6 pF

REV. 1.0.1 8/10/01 3

FAN4822 PRODUCT SPECIFICATION

Electrical Characteristics (Continued)

Unless otherwise specified, RT = 52.3kΩ, CT = 470pF, TA = Operating Temperature Range (Note 1)

Parameter Conditions Min. Typ. Max. Units

Gain Modulator

Gain (Note 2) IIAC = 100mA, VVRMS = 0V, 0.36 0.51 0.66

VFB = 0V

IIAC = 50mA, VVRMS = 1.2V, 1.20 1.72 2.24

VFB = 0V

IIAC = 100µA, VVRMS = 1.8V, 0.55 0.78 1.01

VFB = 0V

IIAC = 100µA, VVRMS = 3.3V, 0.14 0.20 0.26

VFB = 0V

Bandwidth IIAC = 250µA 10 MHz

Output Voltage VFB = 0V, VVRMS = 1.15V, IIAC = 0.72 0.8 0.9 V

250µA

Oscillator

Initial Accuracy TA = 25°C 74 80 87 kHz

Voltage Stability VCCZ – 3V < VCC < VCCZ – 0.5V 1 %

Temperature Stability 2 %

Total Variation Line, temperature 72 89 kHz

Ramp Valley to Peak Voltage 2.5 V

Dead Time 100 300 450 ns

CT Discharge Current 4.5 7.5 9.5 mA

Reference

Output Voltage TA = 25°C, IREF = 1mA 7.4 7.5 7.6 V

Line Regulation VCCZ – 3V < VCC < VCCZ – 0.5V 2 10 mV

Load Regulation 1mA < IREF, < 20mA 2 15 mV

Temperature Stability 0.4 %

Total Variation Line, load, and temperature 7.35 7.65 V

Long Term Stability Tj = 125°C, 1000 hours 5 25 mV

Short Circuit Current VCC < VCCZ – 0.5V, VREF = 0V –15 –40 –100 mA

PFC Comparator

Minimum Duty Cycle VIEAO > 6.7V 0 %

Maximum Duty Cycle VIEAO < 1.2V 90 95 %

MOSFET Driver Outputs

Output Low Voltage IOUT = –20mA 0.4 1.0 V

IOUT = –100mA 1.5 3.5 V

IOUT = –10mA, VCC = 8V 0.8 1.5 V

Output High Voltage IOUT = 20mA 9.5 10.3 V

IOUT = 100mA 9 10.3 V

Output Rise/Fall Time CL = 1000pF 40 ns

Undervoltage Lockout

Threshold Voltage VCCZ – VCCZ – VCCZ – V

0.9 0.6 0.2

Hysteresis 2.4 2.9 3.45 V

4 REV. 1.0.1 8/10/01

PRODUCT SPECIFICATION FAN4822

Electrical Characteristics (Continued)

Unless otherwise specified, RT = 52.3kΩ, CT = 470pF, TA = Operating Temperature Range (Note 1)

Parameter Conditions Min. Typ. Max. Units

Supply

Shunt Voltage (VCCZ) ICC =25mA 12.8 13.5 14.2 V

Load Regulation 25mA < ICC < 55mA ±150 ±300 mV

Total Variation Load and temperature 12.4 14.6 V

Start-up Current VCC < 12.3V 0.7 1.1 mA

Operating Current VCC = VCCZ – 0.5V 22 28 mA

Notes

1. Limits are guaranteed by 100% testing, sampling, or correlation with worst-case test conditions.

2. Gain = K x 5.3 V; K = (IGAINMOD – IOFFSET) x IAC x (VEAO – 1.5)–1.

REV. 1.0.1 8/10/01 5

FAN4822 PRODUCT SPECIFICATION

Functional Description bined parasitic capacitance of D1 and Q1 (or optional ZVS

capacitor CZVS). At t3, the voltage across Q1 is sufficiently

Switching losses of wide input voltage range PFC boost con- low that the controller turns Q2 off and Q1 on. Q1 then

verters increase dramatically as power levels increase above behaves as an ordinary PFC switch, storing energy in the

200 watts. The use of zero-voltage switching (ZVS) tech- boost inductor L1. The energy stored in L2 is completely dis-

niques improves the efficiency of high power PFCs by sig- charged into the boost capacitor via D2 during the Q1 off-

nificantly reducing the turn-on losses of the boost MOSFET. time and the value of L2 must be selected for discontinuous-

ZVS is accomplished by using a second, smaller MOSFET, mode operation.

together with a storage element (inductor) to convert the

turn-on losses of the boost MOSFET into useful output Component Selection

power.

Q1 Turn-Off

Because the FAN4822 uses leading edge modulation, the

The basic function of the FAN4822 is to provide a power

PFC MOSFET (Q1) is always turned off at the end of each

factor corrected, regulated DC bus voltage using continuous,

oscillator ramp cycle. For proper operation, the internal ZVS

average current-mode control. Like Micro Linear’s family of

flip-flop must be reset every cycle during the oscillator dis-

PFC/PWM controllers, the FAN4822 employs leading-edge

charge time. This is done by automatically resetting the ZVS

pulse width modulation to reduce system noise and permit

comparator a short time after the drain voltage of the main Q

frequency synchronization to a trailing edge PWM stage for

has reached zero (refer to Figure 1 sense circuit). This sense

the highest possible DC bus voltage bandwidth. For minimi-

circuit terminates the ZVS on time by sensing the main Q

zation of switching losses, circuitry has been incorporated to

drain voltage reaching zero. It is then reset by way of a resis-

control the switching of the ZVS FET.

tor pull-up to VCC (R6). The advantage of this circuit is that

the ZVS comparator is not reset at the main Q turn off which

Theory of Operation occurs at the end of the clock cycle. This avoids the potential

Figure 1 shows a simplified schematic of the output and con- for improper reset of the internal ZVS flip-flop.

trol sections of a high power PFC circuit. Figure 2 shows the

relationship of various waveforms in the circuit. Q1 func- Another concern is the proper operation of the ZVS compar-

tions as the main switching FET and Q2 provides the ZVS ator during discontinuous mode operation (DCM), which

action. During each cycle, Q2 turns on before Q1, diverting will occur at the cusps of the rectified AC waveform and at

the current in L1 away from D1 into L2. The current in L2 light loads. Due to the nature of the voltage seen at the drain

increases linearly until at t2 it equals the current through L1. of the main boost Q during DCM operation, the ZVS com-

When these currents are equal, L1 ceases discharging current parator can be fooled into forcing the ZVS Q on for the

and is now charged through L2 and Q2. At time t2, the drain entire period. By adding a circuit which limits the maximum

voltage of Q1 begins to fall. The shape of the voltage wave- on time of the ZVS Q, this problem can be avoided. Q3 in

form is sinusoidal due to the interaction of L2 and the com- Figure 1 provides this function.

L1 D1

+

C1

VREF

13 VREF L2

FAN4822

12 VCC CZVS(OPT)

D2

Q1

R1 C2

R3 R5 R6 PFC OUT 11

22k 220 22k Q2

ZVS OUT 10

7 ZV SENSE

C3

33pF PWR GND 9

C4 8 GND

330pF MAX ZVS

R4 R2 ON TIME LIMIT

51k

Q3

C5

Figure 1. Simplified PFC/ZVS Schematic.

6 REV. 1.0.1 8/10/01

PRODUCT SPECIFICATION FAN4822

Q1 Turn-On

The turn-on event consists of the time it takes for the current

through L2 to ramp to the L1 current plus the resonant event

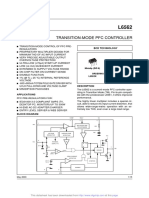

A. SYSTEM

of L2 and the ZVS capacitor. The total event should occur in CLOCK

(INTERNAL)

a minimum of 350–450ns, but can be longer at the risk of

increasing the total harmonic distortion. Setting these times

equal should minimize conducted and radiated emissions.

t Q1 ( OFF ) = t IL2 + t RES = 400ns (1)

B. RTCT

Where IL2 is equal to IL1.

The value of L2 is calculated to remain in discontinuous-

mode:

C. ZVS GATE (Q2)

V BUS × V RMS ( MIN ) × t IL2

L2 = ----------------------------------------------------------------

-

2 × P OUT (2)

The resonant event occurs in 1/4 of a full sinusoidal cycle.

For example, when a 1/4 cycle occurs in 200ns, the fre-

quency is 1.25MHz.

D. VDS (Q2)

1 1

f RES = ----------------------------------- = ---------------------

2π L2 × C 4 × t RES (3)

ZVS

Rearranging and solving for L2:

4 × t RES 2

L2 = -------------------------- E. PFC GATE (Q1)

2

π × C ZVS (4)

The resonant capacitor (CZVS) value is found by setting

equations 2 and 4 equal to each other and solving for CZVS.

4 × t RES 2 × 2 × P OUT

C ZVS = ----------------------------------------------------------------------------

- F. VDS (Q1)

2

π × V BUS × V RMS ( MIN ) × t IL2 (5)

Application

Figure 3 displays a typical application circuit for a 500W

ZVS PFC supply. Full design details are covered in applica-

tion note 33, FAN4822 Power Factor Correction With Zero G. IL2

Voltage Resonant Switching.

t1 t3

t2

Figure 2. Timing Diagrams

REV. 1.0.1 8/10/01 7

8

F1 D1

400VDC

B1 L1 FESI6JT

LINE 8AMP R12 D2 R10

420uH @ 10A

FAN4822

250VAC 453kΩ 1% 102kΩ 1%

n = 57

L2 D3 MUR860

R22 8.5m @ 14A MUR460 R8

C14 GBU6G R13 93.1kΩ 1%

0.47µF 402kΩ 453kΩ 1%

250VAC 1% R1 C21

Q1 Q2 0.1µF R9

R14 3.3kΩ 93.1kΩ 1%

FQA24N50 R3 FQP6N50 3W 200V

R23 100kΩ 1%

402kΩ 10

C4 R20

NEUTRAL 1%

0.1µF D4 93.1kΩ 1%

50V R4 D6 UF4005

R15 1N4747A +

16.2kΩ 10kΩ C2 C1 C3

C6 R11

1% 470pF 330µF 1000pF

0.47µF D5 R6 2.37kΩ

1600V 450V 50V

16V 1N4747A 10kΩ 1%

R18 400VDC RTN

0.0732 5W 1%

D13 D7

1N5401 1N5401 TC4427

1 8

NC NC

2 7

IN A OUT A R2

3 6 10Ω

VS RTN VS

C12 C7 4 5

2.2nF 0.68µF 50V IN B OUT B

50V

C13 C9 C10

R17 1µF 1µF

100pF

C11 220kΩ 50V 50V

50V

68nF

D10 50V FAN4822

UF4005

R19 1 14

VEAO FB R5

10kΩ

Figure 3. FAN4822 Schematic.

R21 39kΩ

2 13 2W

R27 IEAO REF 39kΩ

220 2W

3 12

ISENSE VCC

R16 4 11

8.25kΩ IAC PFC OUT C8 C5

1% 2.2µF 1µF R7 D11

5 10 50V 50V 47 EGP20A

R24 VRMS ZVS OUT L1

22kΩ C15 C16 n = 2.5

6 9

RTCT PWR GND 1500µF 1µF

25V 50V

7 8

ZV SENSE GND

C18

33pF

50V Q3 R29 D9 C17

R25 2N7000 10kΩ 1N5819 1µF

51kΩ 50V

R26 D8

C19 C20 22kΩ 1N5819

330pF 2.2nF C22

50V 50V 100pF

1N4148

D12

EGP20A

PRODUCT SPECIFICATION

REV. 1.0.1 8/10/01

PRODUCT SPECIFICATION FAN4822

Mechanical Dimensions inches (millimeters)

Package: P14

14-Pin PDIP

0.740 - 0.760

(18.79 - 19.31)

14

0.240 - 0.260 0.295 - 0.325

PIN 1 ID

(6.09 - 6.61) (7.49 - 8.25)

1

0.070 MIN

(1.77 MIN) 0.050 - 0.065 0.100 BSC

(4 PLACES) (1.27 - 1.65) (2.54 BSC)

0.015 MIN

(0.38 MIN)

0.170 MAX

(4.32 MAX)

0.016 - 0.022 SEATING PLANE 0.008 - 0.012

0.125 MIN 0º - 15º (0.20 - 0.31)

(0.40 - 0.56)

(3.18 MIN)

Package: S16W

16-Pin Wide SOIC

0.400 - 0.414

(10.16 - 10.52)

16

0.291 - 0.301 0.398 - 0.412

(7.39 - 7.65) (10.11 - 10.47)

PIN 1 ID

1

0.024 - 0.034 0.050 BSC

(0.61 - 0.86) (1.27 BSC)

(4 PLACES) 0.095 - 0.107

(2.41 - 2.72)

0º - 8º

0.012 - 0.020 0.022 - 0.042 0.009 - 0.013

0.090 - 0.094

(0.30 - 0.51) SEATING PLANE 0.005 - 0.013 (0.56 - 1.07)

(2.28 - 2.39) (0.13 - 0.33) (0.22 - 0.33)

REV. 1.0.1 8/10/01 9

FAN4822 PRODUCT SPECIFICATION

Ordering Information

Part Number PFC/PWM Frequency Package

FAN4822IN -40°C to 85°C 14-Pin PDIP (P14)

FAN4822IM -40°C to 85°C 16-Pin Wide SOIC (S16W)

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO

ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME

ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN;

NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

LIFE SUPPORT POLICY

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES

OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR

CORPORATION. As used herein:

1. Life support devices or systems are devices or systems 2. A critical component in any component of a life support

which, (a) are intended for surgical implant into the body, device or system whose failure to perform can be

or (b) support or sustain life, and (c) whose failure to reasonably expected to cause the failure of the life support

perform when properly used in accordance with device or system, or to affect its safety or effectiveness.

instructions for use provided in the labeling, can be

reasonably expected to result in a significant injury of the

user.

www.fairchildsemi.com

8/10/01 0.0m 003

Stock#DS30004803

2001 Fairchild Semiconductor Corporation

You might also like

- Ziv 8idv PDFDocument768 pagesZiv 8idv PDFKevin Carmona ToralNo ratings yet

- Trajectory PredictionDocument16 pagesTrajectory PredictionAlberto CastilloNo ratings yet

- ML4824 Power Factor Correction and PWM Controller Combo: General Description FeaturesDocument16 pagesML4824 Power Factor Correction and PWM Controller Combo: General Description FeaturesTaras100% (1)

- Data Sheet ML 4824Document16 pagesData Sheet ML 4824Jose BenavidesNo ratings yet

- ML4812CPDocument17 pagesML4812CPIntan LianaNo ratings yet

- KA5M0965Q: Fairchild Power Switch (SPS)Document14 pagesKA5M0965Q: Fairchild Power Switch (SPS)Jose Angel TorrealbaNo ratings yet

- 5H0280R (1)Document14 pages5H0280R (1)nguyenhuy66No ratings yet

- 2A20112 PFC Fuentes LG Audio PFC CRITICALDocument9 pages2A20112 PFC Fuentes LG Audio PFC CRITICALAndres AlegriaNo ratings yet

- 5188 yOdRG0FX WT7522Document9 pages5188 yOdRG0FX WT7522madoNo ratings yet

- Controlador en Secundario BitmainDocument15 pagesControlador en Secundario BitmainJesus Teodoro Mendoza GuerraNo ratings yet

- R2A20133DDocument14 pagesR2A20133DLuiz Augusto Freitas SantosNo ratings yet

- 3843ANDocument8 pages3843ANinfosolutionNo ratings yet

- ML - ML4824-2 Samsung Service ManualDocument15 pagesML - ML4824-2 Samsung Service ManualpgcclNo ratings yet

- Cópia de Datasheet l4949Document12 pagesCópia de Datasheet l4949ErikOliveiraNo ratings yet

- Oscilador de PFC Fuente Toshiba 2A20112SPDocument8 pagesOscilador de PFC Fuente Toshiba 2A20112SPAntonio ChavezNo ratings yet

- REN_hip6004_DST_19990408Document12 pagesREN_hip6004_DST_19990408Alireza MoradiNo ratings yet

- SP490E / SP491E: Enhanced Full-Duplex RS-485 TransceiversDocument13 pagesSP490E / SP491E: Enhanced Full-Duplex RS-485 TransceiversThomas ThomasNo ratings yet

- FP6321A FitiDocument14 pagesFP6321A FitiJob GarciaNo ratings yet

- Renesas R2A20113ASP#W5 DatasheetDocument13 pagesRenesas R2A20113ASP#W5 DatasheetbirricaNo ratings yet

- Dual High Side DriverDocument7 pagesDual High Side DriverСаша ДыдаNo ratings yet

- Cxa8038p EtcDocument2 pagesCxa8038p EtcYAZAN AINIANo ratings yet

- Ds8204a 05Document19 pagesDs8204a 05marcelo Chiu LeonNo ratings yet

- TX 2C (RX 2C) Ay PDFDocument12 pagesTX 2C (RX 2C) Ay PDFbilalNo ratings yet

- PDF Fairchild 430756Document14 pagesPDF Fairchild 430756Giovanni Carrillo VillegasNo ratings yet

- KA3525A FairchildSemiconductorDocument7 pagesKA3525A FairchildSemiconductorA.hNo ratings yet

- Switching From The L6561 To The L6562: AN1757 Application NoteDocument9 pagesSwitching From The L6561 To The L6562: AN1757 Application Notedeilyn rivasNo ratings yet

- FA5612_oswq9bzuavDocument30 pagesFA5612_oswq9bzuavAlu ManiNo ratings yet

- TrasDocument11 pagesTrasAmauri RogérioNo ratings yet

- PLL XR2212 ExarCorporationDocument20 pagesPLL XR2212 ExarCorporationHoan TranNo ratings yet

- Design Consideration With AP3041: Application Note 1059Document6 pagesDesign Consideration With AP3041: Application Note 1059subisanNo ratings yet

- OPTO788JDocument21 pagesOPTO788JRoberto CisnerosNo ratings yet

- Is31pm7212 DSDocument12 pagesIs31pm7212 DSdavid.gjeorgevskiNo ratings yet

- Data Sheet: HCPL-788JDocument22 pagesData Sheet: HCPL-788JBegenc777begencNo ratings yet

- SP490E/SP491E Enhanced Full Duplex RS-485 Transceivers: DescriptionDocument12 pagesSP490E/SP491E Enhanced Full Duplex RS-485 Transceivers: DescriptionCarlos AcostaNo ratings yet

- M63975FPDocument5 pagesM63975FPnk7562527No ratings yet

- 3842a DatasheetDocument8 pages3842a DatasheetVịnh DemoNo ratings yet

- Rt8816a-06 Gtx1070 Gigabyte MemoriasDocument21 pagesRt8816a-06 Gtx1070 Gigabyte Memoriastechgamebr85No ratings yet

- Dual-Phase PWM Controller With PWM-VID Reference: General Description FeaturesDocument21 pagesDual-Phase PWM Controller With PWM-VID Reference: General Description FeaturesДмитрий НичипоровичNo ratings yet

- DS8816ADocument21 pagesDS8816AAgustin AyalaNo ratings yet

- An1060 Flyback Converters With The l6561 PFC Controller StmicroelectronicsDocument11 pagesAn1060 Flyback Converters With The l6561 PFC Controller StmicroelectronicsALAIN GOUDEAUNo ratings yet

- KA1H0165RDocument12 pagesKA1H0165Rrujakcuka62No ratings yet

- Very Low Drop Voltage Regulator: DescriptionDocument8 pagesVery Low Drop Voltage Regulator: DescriptionJhonatan CervantesNo ratings yet

- Very Low Drop Voltage Regulator: DescriptionDocument8 pagesVery Low Drop Voltage Regulator: Descriptionjulio montenegroNo ratings yet

- Transition-Mode PFC Controller: BCD TechnologyDocument15 pagesTransition-Mode PFC Controller: BCD TechnologyWilson vargas de la cruzNo ratings yet

- UC3842B, UC3843B, UC2842B, UC2843B High Performance Current Mode ControllersDocument22 pagesUC3842B, UC3843B, UC2842B, UC2843B High Performance Current Mode ControllersAnkitNo ratings yet

- Datasheet PDFDocument10 pagesDatasheet PDFJORGENo ratings yet

- DM311Document16 pagesDM311Hernan Ortiz EnamoradoNo ratings yet

- Toy Car Remote Controller With Nine Functions: TX-5B/RX-5BDocument9 pagesToy Car Remote Controller With Nine Functions: TX-5B/RX-5BYan SuNo ratings yet

- NCN5150 DDocument12 pagesNCN5150 Dgoingforward77No ratings yet

- L6565 DatasheetDocument17 pagesL6565 DatasheetJose BenavidesNo ratings yet

- Ep100 ManualDocument20 pagesEp100 Manualhang100% (1)

- L4973V3.3 - L4973V5.1 L4973D3.3 - L4973D5.1: 3.5A Step Down Switching RegulatorDocument16 pagesL4973V3.3 - L4973V5.1 L4973D3.3 - L4973D5.1: 3.5A Step Down Switching RegulatorLeandro Matias CoelhoNo ratings yet

- Single 12V Input Supply Dual Regulator - Synchronous-Buck-PWM and Linear-Regulator ControllerDocument15 pagesSingle 12V Input Supply Dual Regulator - Synchronous-Buck-PWM and Linear-Regulator ControllerBabei IlieNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Analog Dialogue Volume 46, Number 1: Analog Dialogue, #5From EverandAnalog Dialogue Volume 46, Number 1: Analog Dialogue, #5Rating: 5 out of 5 stars5/5 (1)

- High Voltage Direct Current Transmission: Converters, Systems and DC GridsFrom EverandHigh Voltage Direct Current Transmission: Converters, Systems and DC GridsNo ratings yet

- 180585revb, BT1855Document49 pages180585revb, BT185540818248No ratings yet

- 180585REVB, BT1855 33pDocument33 pages180585REVB, BT1855 33p40818248No ratings yet

- 787801Document1 page78780140818248No ratings yet

- Technical Publications: Product Name(s)Document6 pagesTechnical Publications: Product Name(s)40818248No ratings yet

- Monolithic 6A DC/DC Step-Down Regulator Features: FN7102.7 Data Sheet May 8, 2006Document14 pagesMonolithic 6A DC/DC Step-Down Regulator Features: FN7102.7 Data Sheet May 8, 200640818248No ratings yet

- Technical Publication: Direction 5135612-100 Revision 3 GE Healthcare EMC Conformance Statement (Definium™ 6000)Document30 pagesTechnical Publication: Direction 5135612-100 Revision 3 GE Healthcare EMC Conformance Statement (Definium™ 6000)40818248No ratings yet

- Lmx2370/Lmx2371/Lmx2372 Pllatinum Dual Frequency Synthesizer For RF Personal CommunicationsDocument16 pagesLmx2370/Lmx2371/Lmx2372 Pllatinum Dual Frequency Synthesizer For RF Personal Communications40818248No ratings yet

- LMX 2336Document18 pagesLMX 233640818248No ratings yet

- MS2711 10580-00027Document15 pagesMS2711 10580-0002740818248No ratings yet

- LMX2377USLBXDocument44 pagesLMX2377USLBX40818248No ratings yet

- Lmx2354 Pllatinum Fractional N RF/ Integer N If Dual Low Power Frequency Synthesizer Lmx2354 2.5 Ghz/550 MHZDocument23 pagesLmx2354 Pllatinum Fractional N RF/ Integer N If Dual Low Power Frequency Synthesizer Lmx2354 2.5 Ghz/550 MHZ40818248No ratings yet

- Lmx2487E 7.5 GHZ High Performance Delta-Sigma Low Power Dual Pllatinum Frequency Synthesizers With 3.0 GHZ Integer PLLDocument38 pagesLmx2487E 7.5 GHZ High Performance Delta-Sigma Low Power Dual Pllatinum Frequency Synthesizers With 3.0 GHZ Integer PLL40818248No ratings yet

- LT490 Differential Driver and Receiver PairDocument8 pagesLT490 Differential Driver and Receiver Pair40818248No ratings yet

- PC16552D - Dual Universal AsynchronousReceiver-Transmitter With FIFODocument21 pagesPC16552D - Dual Universal AsynchronousReceiver-Transmitter With FIFO40818248No ratings yet

- CXD1265 - CCD Camera Timing GeneratorDocument24 pagesCXD1265 - CCD Camera Timing Generator40818248No ratings yet

- CXD3172AR Signal Processor LSI For Single CCD Color CameraDocument25 pagesCXD3172AR Signal Processor LSI For Single CCD Color Camera40818248No ratings yet

- ZJYS81 - CanCommon Mode FiltersDocument2 pagesZJYS81 - CanCommon Mode Filters40818248No ratings yet

- Max1406 - 3TX-3RX RS232Document8 pagesMax1406 - 3TX-3RX RS23240818248No ratings yet

- Dual-Channel Digital Isolators Adum1200/Adum1201: Data SheetDocument28 pagesDual-Channel Digital Isolators Adum1200/Adum1201: Data Sheet40818248No ratings yet

- Multiple RS-232 Drivers & Receivers: Product Description FeaturesDocument9 pagesMultiple RS-232 Drivers & Receivers: Product Description Features40818248No ratings yet

- Stages of Group Development (Univ of Vermont)Document12 pagesStages of Group Development (Univ of Vermont)Jessica Adharana KurniaNo ratings yet

- Microwave Mini ProjectDocument21 pagesMicrowave Mini Projectfaizan4033No ratings yet

- AirsteriDocument3 pagesAirsteriJerard EleazarNo ratings yet

- Mauritius Truly A Paradise IslandDocument1 pageMauritius Truly A Paradise IslandqiaunusNo ratings yet

- Resume: Name: Bhuwan Vohra Mob: 9068291781 Career ObjectiveDocument2 pagesResume: Name: Bhuwan Vohra Mob: 9068291781 Career ObjectiveBhuwan VohraNo ratings yet

- Chcece054 Ae Pro2of3 2Document26 pagesChcece054 Ae Pro2of3 2bellahuynh0205No ratings yet

- Jason Hickel's De-DevelopmentDocument2 pagesJason Hickel's De-DevelopmentLOVE JOYNo ratings yet

- Control Tutorials For MATLAB and Simulink - Cruise Control - System ModelingDocument3 pagesControl Tutorials For MATLAB and Simulink - Cruise Control - System Modelingdialauchenna100% (1)

- A. Leadership and GovernanceDocument2 pagesA. Leadership and GovernanceRose YaGoNo ratings yet

- The Concept of Experience by John Dewey Revisited - Conceiving, Feeling and Enliving (H. Hohr)Document14 pagesThe Concept of Experience by John Dewey Revisited - Conceiving, Feeling and Enliving (H. Hohr)Juan Pablo SerraNo ratings yet

- Lesson Plan - Weathering - Education WorldDocument3 pagesLesson Plan - Weathering - Education WorldEugene HaroNo ratings yet

- Anochrome Coating Data Sheet 15-10-14Document3 pagesAnochrome Coating Data Sheet 15-10-14ellisforheroesNo ratings yet

- Filipino Culture - World View, Values and Expressions 1Document166 pagesFilipino Culture - World View, Values and Expressions 1Khimiana Salazar90% (10)

- CRV 2.0 (2WD) 2017YM - Current: Engine Oil + Drain Plug Washer Oil FilterDocument1 pageCRV 2.0 (2WD) 2017YM - Current: Engine Oil + Drain Plug Washer Oil FilterGeorge BulangNo ratings yet

- Test / Warranty Certificate: MGM Varvel Power Transmission PVT LTDDocument1 pageTest / Warranty Certificate: MGM Varvel Power Transmission PVT LTDSiddesh KadamNo ratings yet

- STAMFORD AVK DIGITAL AVR, MA330-Wuxi Huaxiang Control Co.,LtdDocument3 pagesSTAMFORD AVK DIGITAL AVR, MA330-Wuxi Huaxiang Control Co.,Ltdssahrizal50No ratings yet

- Two Empires: Warhammer 40k Vs Star WarsDocument33 pagesTwo Empires: Warhammer 40k Vs Star Warskartar5100% (1)

- 2022 Trend Report InvisionDocument34 pages2022 Trend Report InvisionrazintntNo ratings yet

- JHA For Gravity TestDocument3 pagesJHA For Gravity TestSafety First TV PhNo ratings yet

- WINCC Runtime Professional S7-Graph Overview and PLC Code ViewerDocument35 pagesWINCC Runtime Professional S7-Graph Overview and PLC Code ViewerCarlos Octavio Gamarra LimaNo ratings yet

- AI InversionDocument30 pagesAI InversionYoggie Surya PradanaNo ratings yet

- I Just Want To Download 1 PDFDocument14 pagesI Just Want To Download 1 PDFSachika ValenlieNo ratings yet

- Linear Algebra UCDDocument152 pagesLinear Algebra UCDSofia AniNo ratings yet

- LOM - International Automotive EngineeringDocument2 pagesLOM - International Automotive EngineeringRagyaddy TeslaNo ratings yet

- Astm B77Document2 pagesAstm B77kashif ehsanNo ratings yet

- Compiler Design Lab ManualDocument37 pagesCompiler Design Lab ManualPratham WakdeNo ratings yet

- Journal Stakeholder TheoryDocument2 pagesJournal Stakeholder TheoryvaruntyagiNo ratings yet