Service Manual For: Repair Technology Research Department /EDVD Feb.2004

Uploaded by

naughtybigboyCopyright:

Available Formats

Service Manual For: Repair Technology Research Department /EDVD Feb.2004

Uploaded by

naughtybigboyOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Service Manual For: Repair Technology Research Department /EDVD Feb.2004

Uploaded by

naughtybigboyCopyright:

Available Formats

BY: Grass Grass.Ren .

Ren

Repair Technology Research Department /EDVD Repair Technology Research Department /EDVD

Feb.2004

SERVICE MANUAL FOR

8050

8050 8050 N/B Maintenance N/B Maintenance

1

1. Hardware Engineering Specification ..

1.1 Introduce .

1.2 System Overview .

1.3 System Hardware Parts ....

2. System View & Disassembly ..

2.1 System View ...

2.2 System Disassembly .

3. Definition & Location of Connectors / Switches Setting

4. Definition & Location of Major Component ..

5. Pin Description of Major Component..

5.1 Pentium4 (Willamette/Northwood) processor ...

5.2 Sis650 North Bridge .

5.3 Sis962 South Bridge .

6. System Block Diagram ..

7. Maintenance Diagnostics ..

7.1 Introduction

7.2 Debug Card

7.3 Error code ..

Contents

3

3

6

9

34

37

57

60

62

62

66

75

83

84

84

86

85

34

8050 8050 N/B Maintenance N/B Maintenance

2

8. Trouble Shooting

8.1 No Power .

8.2 Battery Can not Be Charged .

8.3 No Display ..

8.4 External Monitor No Display ....

8.5 Memory Test Error .

8.6 Keyboard/Touch-pad Test Error ..

8.7 USB Port Test error..

8.8 Hard Disk Drive Test Error...

8.9 CD-ROM Test Error

8.10 Audio Test Failure..

8.11 LAN Test Error .

8.12 Modem Test Error .

8.13 Mini-PCI Test Error.. ...

8.14 Card Bus&Reader Test Error..

8.15 TV Encoder Test Failure .

8.16 IEEE1394 Test Failure ...

9. Spare Parts List .

10. System Exploded View

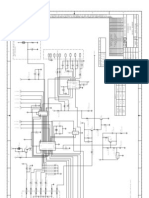

11. Circuit Diagram ..

12. Reference Material .

Contents

89

90

95

97

103

105

107

109

111

113

115

118

120

122

124

126

128

141

142

130

176

8050

8050

N/B Maintenance

N/B Maintenance

3

1.1 Introduce

1. Engineer Hardware Specification

The MiTAC 8050 model is designed for Intel Banias processor with 400MHz FSB with Micro-FCPGA package.

It can support Banias 1.5G ~ 1.9GHz/Dothan 2.0GHz and above.

This system is based on PCI architecture and is fully compatible with IBM PC/AT specification, which has

standard hardware peripheral interface. The power management complies with Advanced Configuration and

Power Interface (ACPI) 2.0. It also provides easy configuration through CMOS setup, which is built in system

BIOS software and can be pop-up by pressing F2 key at system start up or warm reset. System also provides icon

LEDs to display system status, such as AC Power indicator, Battery Power indicator, Battery status indicator,

HDD,CD-ROM, NUM LOCK, CAP LOCK, SCROLL LOCK, RF on/off Card Reader indicator. It also equipped

with LAN, 56K Fax MODEM, 3 USB port, S-Video and audio line in/out , external microphone function.

The memory subsystem supports two expansion DDR SDRAM slot with unbuffered PC1600/PC2100 DDR-

SDRAM.

The Montara-GME GMCH Host Memory Controller integrates a high performance host interface for Intel

Banias processor, a high performance 2D/3D Graphic Engine, a high performance memory controller, Digital

Video port (DVOB & DVOC) interface, and Intel Hub interface Technology connecting with Intel 82801DBM

ICH4-M.

The Intel ICH4-M integrates three Universal Serial Bus 2.0 Host Controllers Interface (UHCI), the Audio

Controller with AC97 interface, the Ethernet includes a 32-bit PCI controller, the IDE Master/Slave controllers,

8050

8050

N/B Maintenance

N/B Maintenance

4

and Intel Hub interface technology.

The MOBILITY M10 provides one of the fastest and most advanced 2D, 3D, and multimedia graphics2

performance for notebooks. Its architecture introduces the latest achievements in the graphics industry, which

enable the use of the progressive new features in upcoming applications, but without compromising performance.

ATIs support of support of DirectX 9 features, highly optimized Open GL support, and flexible memory

configurations allow implementations targeted at the gaming enthusiast, consumer, business and workstation

platforms.

The Realtek RTL8100C(L) is a highly integrated, cost-effective single-chip Fast Ethernet controller that provides

32-bit performance, PCI bus master capability, and full compliance with IEEE 802.3u 100Base-T specifications

and IEEE 802.3x Full Duplex Flow Control. It also supports the Advanced Configuration Power management

Interface (ACPI).

The VT6307L is a single chip PCI Host Controller for IEEE 1394-1995 Release 1.0 and IEEE 1394a P2000. It

implements the Link and PHY layers for IEEE 1394-1995 High Performance Serial Bus specification release 1.0

and 1394a P2000. It is compliant with 1394 Open HCI 1.0 and 1.1 with DMA engine support for high

performance data transfer via a 32-bit bus master PCEI host bus interface. The VT6307L supports 100, 200 and

400 Mbit/sec transmission via an integrated 2-port PHY. The VT6307L services two types of data packets:

asynchronous and isochronous(real time). The 1394 link core performs arbitration requesting, packet generation

and checking, and bus cycle master operations. It also has root node capability and performs retry operations.

The RICOH R5C592 CardBus/Media Reader controller functions as a single slot PCI to Cardbus bridge and also

PCI interface smart card and MS/SD/MMC flash card reader. The R5C592 provide one Cardbus slot and all reader

interface may operate simultaneously.

8050

8050

N/B Maintenance

N/B Maintenance

5

The CH7011A is a display controller device which accepts a digital graphics input signal, and encodes and

transmits data to a TV output (analog composite, s-video or RGB). The device accepts data over one 12-bit wide

variable voltage data port which supports five different data format including RGB and YcrCb. The TV-Out

processor will perform non-interlace to interlace conversion with scaling and flicker filters, and encode the data

into any of the NTSC or PAL video standards. The scaling and flicker filter is adaptive and programmable to

enable superior text display. Eight graphics resolutions are supported up to 1024 X 768 with full vertical and

horizontal underscan capability in all modes. A high accuracy low jitter phase locked loop is integrated to create

outstanding video quality. Support is provided for Macrovision and RGB bypass mode which enable driving a

VGA CRT with the input data.

The W83L950D is a high performance microcontroller on-chip supporting functions optimized for embedded

control.These include ROM, RAM, four types of timers, a serial communication interface, optional IC bus

interface, host interface, A/D converter, D/A converter, I/O ports, and other functions needed in control system

configurations, so that compact, high performance systems can be implemented easily.

A full set of software drivers and utilities are available to allow advanced operating systems such as Windows ME,

Windows 2000 and Windows XP to take full advantage of the hardware capabilities. Features such as bus

mastering IDE, Plug and Play, Advanced Power Management (APM) with application restart, software-controlled

power shutdown.

Following chapters will have more detail description for each individual sub-systems and functions.

8050

8050

N/B Maintenance

N/B Maintenance

6

1.2 System Overview(1)

Intel Mobile Pentium-M Processor 1.5G ~ 1.9GHz/Dothan 2.0GHz and above

-Thermal spec 35W TDP

Chip Set

Intel 855GME+ICH4

L2 Cache

1MB on-die for Pentium-M/ 2MB for Dothan

System BIOS

512KB Flash EPROM - include System BIOS, VGA BIOS - Plug&Play capability -ACPI

0MB DDR266/333 SDRAM memory on board

- 200pin DDR266/333 SDRAM SO-DIMM Memory Module

- Expandable to 1,024MB

- 1.25-inch height memory module supported

1.SMA

2.Reserve external VGA for Ati M10/M11

Optical drive

Combo / DVD-RW, DVD-RAM (12.7mm)

FDD

External USB I/F Option

2.5" 30GB / 40GB / 60GB / 80GB HDD(9.5mm) 4200rpm or 5400rpm

- Ultra DMA 100

15.4" Wide WXGA+ TFT

-Resolution: 1280x800

- 1 CCFT Typical 185cd/m2

-16.77 Million Colors with dithering

CPU

Memory

Video Controller

HDD

Display

8050

8050

N/B Maintenance

N/B Maintenance

8

1.2 System Overview(2)

Continue to previous page

US/UK/Japanese keyboard layout(Use the Orignal KBD that other model used)

- 19mm key pitch / 3mm stroke

- Hot key spec: Fn+F1 : WirelessLAN ON/OFF, Fn+F3/E4 : Volume down/up, Fn+F5 :

LCD/CRT output change

Fn+F6/F7: Brightness up/down, Fn+F11: Display ON/OFF, Fn+F12: Standby

TouchPad (No scroll button)

TypeII x 1

-PCMCIA Standard Rev.2.1 , CardBus support , w/o ZV port

Built-in Sound system

- SCMS support - AC97 I/F

- 16-bit Sampling and Playback - 16-bit stereo - Full duplex supported - 3D sound supported

- AC-3 support

- Built-in 2W Woofer

- Built-in stereo speaker, Built-in microphone

- Sound Volume control by Hot-Key (Fn + F3 : Volume down, Fn + F4 : Volume up)

Card Reader

Support Mulit Card Reader

USB(2.0) x 3

IEEE1394 port x 1(4pins)

Mic-in(mono) x 1

Headphone-out(stereo)/SPDIFx 1

Keyboard

Pointing Device

Audio System

I/O Port

8050 8050 N/B Maintenance N/B Maintenance

8

Line-in x 1

TV-out (PAL/NTSC) x 1 (Macrovision supported)

RJ-45 LAN Jack x 1 (with cap) RJ-11Modem Jack x 1 (with cap)

Mini-PCI connetor (for WirelessLAN Card)

VGA port x 1 DC-in x 1

56Kbps(V.90) Fax Modem(MDC) and 100Base-TX LAN

Wireless LAN (IEEE802.11b, g,a/g)

Li-ion Battery 2200mAh(6-cell) - Battery Life: (TBD)

-RTC bckup battery(Lithium) Standard -Power-ON charge available

Power Supply

60W Universal AC Adapter(100-240V)

Safety Lock

Security Lock hole

Dimension

W353.8 x D250 x H25~32mm

Weight

(P)3.0kg

OS

Windows XP Home Service Pack 1

Accessories

TBD

Windows Logo

Support PC2001 Specification

- need to get the Logo for WindowsXP Home, WHQL Certified

EMI:CE/FCC/UL/TUV, BSMI/CCC(TBD)

Wireless:CE/FCC,WiFi, PTT:CE/FCC, USB:USB2.0 Logo, Energy Star, Harmonic Noise

regulations

Communication

Battery

EMI / Safety / Regulation

1.2 System Overview(3)

Continue to previous page

8050

8050

N/B Maintenance

N/B Maintenance

9

1.3.1 Intel Banias processors in Micro-FCPGA package.

Intel Banias Processors with 478 pins Micro-FCPGA package.

The first Intel mobile processor with the Intel NetBurst micro-architecture which features include hyper-pipelined

technology, a rapid execution engine, a 400MHz system, an execution trace cache, advanced dynamic execution,

advanced transfer cache, enhanced floating point and multi-media unit, and Streaming SIMD Extensions 2

(SSE2).

The Streaming SIMD Extensions 2 (SSE2) enable break-through levels of performance in multimedia applications

including 3-D graphics, video decoding/encoding, and speech recognition.

Use Source-Synchronous Transfer (SST) of address and data to improve performance by transferring data four

times per bus clock.

Support Enhanced Intel SpeedStep technology, which enables real-time dynamic switching of the voltage and

frequency between two performance modes.

1.3.2 Clock Generator

System frequency synthesizer: ICS950810 Programmable output frequency, divider ratios, output rise/fall time,

1.3 System Hardware Parts

8050

8050

N/B Maintenance

N/B Maintenance

10

1.3.3 Montara-GME GMCH IGUI 3D Graphic DDR/SDR Chipset

output skew. Programmable spread percentage for EMI control. Watchdog timer technology to reset system if

system malfunctions. Programmable watchdog safe frequency. Support I2C Index read/write and block read/write

operations. Use external 14.318MHz crystal.

Montara-GME GMCH IGUI Host Memory Controller integrates a high performance host interface for Intel

Banias processor, a high performance 2D/3D Graphic Engine, a high performance memory controller, an AGP 4X

interface, and Intel I/O Hub architecture INTEL 82801DBM ICH4-M.

Montara-GME GMCH Host Interface features the AGTL & AGTL+ compliant bus driver technology with

integrated on-die termination to support Intel Banias processors. Montara-GME GMCH provides a 12-deep In-

Order-Queue to support maximum outstanding transactions up to 12. It integrated a high performance 2D/3D

Graphic Engine, Video Accelerator and Advanced Hardware Acceleration MPEGI/MPEGII Video Decoder for

the Intel Banias series based PC systems. It also integrates a high performance 2.1GB/s DDR266 Memory

controller to sustain the bandwidth demand from the integrated GUI or external AGP master, host processor, as

well as the multi I/O masters. In addition to integrated GUI, Montara-GME GMCH also can support external AGP

slot with AGP 1X/2X/4X capability and Fast Write Transactions. A high bandwidth and mature Intel I/O Hub

architecture is incorporated to connect Montara-GME GMCH and INTEL 82801DBM ICH4-Mtogether. Intel

I/O Hub architecture is developed into three layers, the Multi-threaded I/O Link Layer delivering 1.2GB

bandwidth to connect embedded DMA Master devices and external PCI masters to interface to Multi-threaded I/O

Link layer, the Multi-threaded I/O Link Encoder/Decoder in INTEL 82801DBM ICH4-M to transfer data w/ 533

MB/s bandwidth

8050

8050

N/B Maintenance

N/B Maintenance

11

Features

Processor/Host Bus Support

from/to Multi-threaded I/O Link layer to/from Montara-GME GMCH, and the Multi-threaded I/O Link

Encoder/Decoder in Montara-GME GMCH to transfer data w/ 533 MB/s from/to Multi-threaded I/O Link layer

to/from INTEL 82801DBM ICH4-M.

An Unified Memory Controller supporting DDR266 DRAM is incorporated, delivering a high performance data

transfer to/from memory subsystem from/to the Host processor, the integrated graphic engine or external AGP

master, or the I/O bus masters. The memory controller also supports the Suspend to RAM function by retaining

the CKE# pins asserted in ACPI S3 state in which only AUX source deliver power. The Montara-GME GMCH

adopts the Shared Memory Architecture, eliminating the need and thus the cost of the frame buffer memory by

organizing the frame buffer in the system memory. The frame buffer size can be allocated from 8MB to 64MB.

Intel Banias processor

Support host bus Dynamic Bus Inversion (DBI)

2X Address, 4X data

Supports system bus at 400MT/s (100 MHz) Supports 64-bit host bus addressing

8-deep In-Order-Queue

8050

8050

N/B Maintenance

N/B Maintenance

12

AGTL+ bus driver technology with integrated GTL termination resistors and low voltage operation

(1.05V)

Supports Enhanced Intel Speed Step TM Technology (EIST) and Geyserville III

Support for DPWR# signal to Banias processor for PSB power management

Memory System

Directly supports one DDR channel, 64-bts wide (72-b with ECC).

Supports 200-MHz and 266-MHz DDR devices with max of 2 Double-Sided SO-DIMMs(4 rows populated)

with unbuffered PC1600/PC2100 DDR(with ECC).

Supports 128-Mb, 256-Mb and 512-Mbit technologies providing maximum capacity of 1-GB with only x 16

devices.

All supported devices have 4 banks.

Supports up to 16 simultaneous open pages.

Supports page sizes of 2KB, 4KB, 8KB, and 16KB. Page size is individually selected for every row. UMA

support only.

System Interrupt

8050

8050

N/B Maintenance

N/B Maintenance

13

Supports 8259 and Processor

System Bus interrupt delivery mechanism

Supports interrupts signaled as upstream Memory Writes from PCI and Hub interface

MSI sent to the CPU through the system Bus

From IOxAPIC in ICH4-M

Provides redirection for upstream interrupts to the System Bus

Video Stream Decoder

Improved HW Motion Compensation for MPEG2

All format decoder (18 ATSC formats) supported Dynamic Bob and Weave support for Video Streams

Software DVD at 60 fields/second and 30 frames/second full screen

Support for 720x480 pixel resolution DVD quality encoding at low CPU utilization Video Overlay

Single high quality scalable overlay and second Sprite to support second overlay

Multiple overlay functionality provided via Arithmetic Stretch Blt

Direct YUV from Overlay to TV-out

8050

8050

N/B Maintenance

N/B Maintenance

14

Independent Gamma Correction

Independent Brightness / Contrast / Saturation

Independent Tint / Hue support

Destination Color keying

Source Chroma keying

Maximum source resolution of 1920x1080 pixels

Maximum overlay clock of 133 MHz/200 MHz provides a pixel resolution up to 1600x1200@ 60Hz or

1280x1024@ 85 Hz

Analog Display Support 350 MHz integrated 24-bit RAMDAC that can drive a standard progressive scan

analog monitor up to 1800x1350 @ 85 Hz accompanying I2C and DDC channels provided through

multiplexed interface hot plug and display support

Dual independent pipe with single display support Simultaneous: Same images and native display timings on

each display device

DVO (DVOB) support

Digital video out port DVOB with 165-MHz dot clock on 12-bit interface

L Display

8050

8050

N/B Maintenance

N/B Maintenance

15

- Variety of DVO devices channel

- Compliant with DVI Specification 1.0, thereby providing support for a flat panel up to 2048x1536 pixel

resolution, or digital CRT up to 1920x1080 pixel resolution

1.3.4 I/O Controller Hub : INTEL 82801DBM

The INTEL 82801DBM ICH4-M integrates three Universal Serial Bus 2.0 Host Controllers, the Audio Controller

with AC 97 Interface, the IDE Master/Slave controllers, and Intel I/O Hub architecture. The PCI to LPC Bridge,

I/O Advanced Programmable Interrupt Controller, legacy system I/O and legacy power management

functionalities are integrated as well.

The integrated Universal Serial Bus Host Controllers features Dual Independent UHCI Compliant Host controllers

with six USB ports delivering 480 Mb/s bandwidth and rich connectivity. Besides, Legacy USB devices as well as

over current detection are also implemented.

The Integrated AC97 v2.3 compliance Audio Controller that features a 7-channels of audio speaker out and HSP

v.90 modem support. Additionally, the AC97 interface supports 4 separate SDATAIN pins that is capable of

supporting multiple audio codecs with one separate modemcodec.

The integrated IDE Master/Slave controllers features Dual Independent IDE channels supporting PIO mode

transfers up to 16 Mbytes/sec and Ultra DMA 33/66/100. It provides two separate data paths for the dual IDE

channels that sustain the high data transfer rate in the multitasking environment.

8050

8050

N/B Maintenance

N/B Maintenance

16

INTEL 82801DBM ICH4-M supports 6 PCI masters and complies with PCI 2.2 specification. It also incorporates

the legacy system I/O like: two 82C37 compatible DMA controllers, Channels 0-3 are hardwired to 8 bit, three

8254 compatible programmable 16-bit counters channels 5-7, hardwired keyboard controller and PS2 mouse

interface(not use in MiTAC 8050 model), Real Time clock with 512Bytes CMOS SRAM and two 82C59

compatible Interrupt controllers. Besides, the I/O APIC managing up to 14 interrupts with both Serial and FSB

interrupt delivery modes is supported.

The integrated power management module incorporates the ACPI 1.0b compliance functions, the APM 1.2

compliance functions, and the PCI bus power management interface spec. v1.1. Numerous power-up events and

power down events are also supported. 21 general purposed I/O pins are provided to give an easy to use logic for

specific application. In addition, the INTEL 82801DBM ICH4-M supports Deeper Sleep power state for Intel

Mobile processor.

A high bandwidth and mature Intel I/O Hub architecture is incorporated to connect Montara and Intel

82801DBM ICH4-M Hub interface together. Intel I/O Hub architecture is developed.

1.3.5 Introducing MOBILITY M10 (Option)

The MOBILITY M10 provides one of the fastest and most advanced 2D, 3D, and multimedia graphics

performance for notebooks. Its architecture introduces the latest achievements in the graphics industry, which

enable the use of the progressive new features in upcoming applications, but without compromising performance.

ATIs support of DirectX 9 features, highly optimized OpenGL support, and flexible memory configurations

allow implementations targeted at the gaming enthusiast, consumer, business and workstation platforms.

8050

8050

N/B Maintenance

N/B Maintenance

17

L SMARTSHADER2.0 Advanced Shader Technology

Provides complete hardware-accelerated support for the new DirectX 9 programmable shader model,

enabling more complex and realistic texture and lighting effects than ever before.

Significant improvement over first-generation shaders introduced in DirectX 8, with a much more

powerful and intuitive instruction set. Offers full support for this feature in OpenGL applications.

L MOOTHVISION2.0 Flexible Anti-Aliasing and Anisotropic Filtering

2x/4x/6x full-scene anti-aliasing modes

Adaptive algorithm with programmable sample patterns

2x/4x/8x/16x anisotropic filtering modes

Adaptive algorithm with bi-linear (performance) and tri-linear (quality) options

Incorporates support for DDR SDRAM/SGRAM.

Features key items from ATIs third generation HYPER ZIII technology that conserves memory

bandwidth for improved performance in demanding applications.

L High Performance Memory Support

L Dual Display Support

8050

8050

N/B Maintenance

N/B Maintenance

18

Leading-edge technology, fully optimized with HYDRA VISION, flexibly supports multiple

combinations of notebook LCD, traditional CRT monitors, flat panel displays and TV.

Features Dual Channel DVI support.

230MHz LVDS transmitter supports LCD panels up to QXGA (2048x1536) resolution.

Integrated 165MHz TMDS transmitter supports external flat panels up to UXGA (1600x1200) resolution.

High performance DAC speeds of 400MHz.

Features in Detail

L VIDEO Acceleration

M10 allows the integration of industry leading digital video features, including advanced de-interlacing

algorithms for unprecedented video quality and integrated digital TV decode capability. Includes

programmable,independent gamma control for the video overlay.

New FULLSTREAMtechnology removes blocky artifacts from streaming and Internet video and

provides sharper image quality.

Integrated general purpose xDCT engine (capable of performing both forward and inverse discrete cosine

transform) and motion compensation (MC) support for the acceleration of MPEG encoding and decoding

as well as DV (digital video) encoding and decoding.

8050

8050

N/B Maintenance

N/B Maintenance

19

The CH7011 is a Display controller device which accepts a digital graphics input signal, and encodes and

transmits data to a TV output (analog composite, s-video or RGB). The device accepts data over one 12-bit wide

variable voltage data port which supports five different data formats including RGB and YCrCb.The TV-Out

processor will perform non-interlace to interlace conversion with scaling and flicker filters, and encode the data

into any of the NTSC or PAL video standards. The scaling and flicker filter is adaptive and programmable to

enable superior text display. Eight graphics resolutions are supported up to 1024 by 768 with full vertical and

horizontal underscan capability in all modes. A high accuracy low jitter phase locked loop is integrated to create

outstanding video quality. Support is provided for Macrovisionand RGB bypass mode which enables driving a

VGA CRT with the input data.

Features

TV output supporting up to 1024x768 graphics resolutions

Macro vision7.X copy protection support

Programmable digital interface supports RGB and YCrCb

True scale rendering engine supports under scan in all TV output resolutions

Enhanced text sharpness and adaptive flicker removal with up to 7 lines of filtering

Support for all NTSC and PAL formats

1.3.6 TV CH7011

8050

8050

N/B Maintenance

N/B Maintenance

20

Provides CVBS, S-Video and SCART (RGB) outputs

TV connection detect

Programmable power management

10-bit video DAC outputs

Fully programmable through serial port

Complete Windows and DOS driver support

Low voltage interface support to graphics device

The ALC655 is a 16-bit, full duplex AC'97 2.3 compatible six channels audio CODEC designed for PC

multimedia systems,including host/soft audio and AMR/CNR based designs. The ALC655 incorporates

proprietary converter technology to meet performance requirements on PC99/2001 systems. The ALC655

CODEC provides three pairs of stereo outputs with 5-Bitvolume controls, a mono output, and multiple stereo and

mono inputs, along with flexible mixing, gain and mute functions to provide a complete integrated audio solution

for PCs. The digital interface circuitry of the ALC655 CODEC operates from a 3.3V power supply for use in

notebook and PC applications. The ALC655 integrates 50mW/20ohm headset audio amplifiers at Front-Out and

Surr-Out, built-in 14.318M 24.576MHz PLL and PCBEEP generator, those can save BOM costs. The ALC655

1.3.7 AC97 AUDIO SYSTEM: Advance Logic, Inc, ALC655

8050

8050

N/B Maintenance

N/B Maintenance

21

also supports the S/PDIF input and output function, which can offer easy connection of PCs to consumer

electronic products, such as AC3 decoder/speaker and mini disk devices. ALC655 supports host/soft audio from

Intel ICHx chipsets as well as audio controller based VIA/SIS/ALI/AMD/nVIDIA/ATI chipset. Bundled Windows

series drivers (Win XP/ME/2000/98/NT), EAX/Direct Sound 3D/ I3DL2/ A3D compatible sound effect utilities

(supporting Karaoke, 26-kind of environment sound emulation,10-band equalizer), HRTF 3D positional audio and

Sensaura3D (optional) provide an excellent entertainment package and game experience for PC users. Besides,

ALC655 includes Realteks impedance sensing techniques that makes device load on outputs and inputs can be

detected.

Meets performance requirements for audio on PC99/2001 systems

Meets Microsoft WHQL/WLP 2.0 audio requirements

16-bit Stereo full-duplex CODEC with 48KHz sampling rate

Compliant with AC97 2.3 specifications

- Front-Out, Surround-Out, MIC-In and LINE In Jack Sensing

- 14.318MHz- 24.576MHz PLL to save crystal

- 12.288MHz BITCLK input can be consumed

- Integrated PCBEEP generator to save buzzer

- Interrupt capability

8050

8050

N/B Maintenance

N/B Maintenance

22

Three analog line-level stereo inputs with 5-bit volume control: LINE_IN, CD, AUX

High quality differential CD input

Two analog line-level mono input: PCBEEP,PHONE-IN

Two software selectable MIC inputs

A dedicated Front-MIC input for front panel applications (software selectable)

Boost preamplifier for MIC input shared with Center and LFE output

Both Front-out and Surround-Out built-in

LINE Input shared with surround output;

MIC 50mW/20 amplifier

1.3.8 MDC:PCTEL MODEM DAUGHTER CARD PCT2303W (ASKEY

V1456VQL-P1)

The PCT2303W chipset is designed to meet the demand of this emerging worldwide AMR/MDC market. Theof

PC-TELs well proven PCT2303W chipset and the HSP56TM MR software modem driver allows systems

manufactures to implement modem functions in PCs at a lower bill of materials (BOM) while maintaining higher

system performance.

8050

8050

N/B Maintenance

N/B Maintenance

23

PC-TEL has streamlined the traditional modem into the Host Signal Processing (HSP) solution. Operating with

the Pentium class processors, HSP becomes part of the host computers system software. It requires less power to

operate and less physical space than standard modem solutions. PC-TELs HSP modem is an easily integrated,

cost-effective communications solution that is flexible enough to carry you into the future.

The PCT2303W chip set is an integrated direct access arrangement (DAA) and Codec that provides a

programmable line interface to meet international telephone line requirements. The PCT2303W chip set is

available in two 16-pin small outline packages (AC97 interface on PCT303A and phone-line interface on

PCT303W). The chip set eliminates the need for an AFE, an isolation transformer, relays, opto-isolators, and 2-to

4-wire hybrid. The PCT2303W chip set dramatically reduces the number of discrete components and cost

required to achieve compliance with international regulatory requirements. The PCT2303W complies with

AC97 Interface specification Rev. 2.1.

The chip set is fully programmable to meet world-wide telephone line interface requirements including those

described by CTR21, NET4, JATE, FCC, and various country-specific PTT specifications. The programmable

parameters of the PCT2303W chip set include AC termination, DC termination, ringer impedance, and ringer

threshold. The PCT2303W chip set has been designed to meet stringent world-wide requirements for out-of-band

energy, billing-tone immunity, lightning surges, and safety requirements.

Features

Virtual com port with a DTE throughout up to 460.8Kbps.

G3 Fax compatible

8050

8050

N/B Maintenance

N/B Maintenance

24

Codec/DAA Features

AC97 2.1 compliant

86dB dynamic range TX/RX paths

2-4-wire hybrid

Integrated ring detector

High voltage isolation of 4000V

Support for Caller ID

Compliant with FCC Part68, CTR21, Net4 and JATE

Low power standby

Low profile SOIC package 16 pins 10x3x1.55mm

Low power consumption

10mA @ 3.3V operation

Auto dial and auto answer

Ring detection

8050

8050

N/B Maintenance

N/B Maintenance

25

Standard Features

Data ITU-T V.90 (56Kbps), V.34 (4.8Kbps TO 33.6 Kbps), V.32 bis (4.8Kbps to 14.4Kbps), V.22 bis (1.2 bps

to 2.4 Kbps), V.21 and Bell 103 and 212A(300 to 1200 bps) modulation protocol.

Data Compression ITU-T V.42bis MNP Class 5

Error Correction ITU-T V.42 LAPM MNP 2-4

Fax ITU-T V. 17, V.29, V.27ter, V.21, Channel 2, Group 3, EIA Class I

1mA @ 3.3V power down

Integrated modemcodec

8050

8050

N/B Maintenance

N/B Maintenance

26

1.3.9 IEEE1394 VT6307L (Option)

1.3.9.1 Overview

The VT6307 IEEE 1394 OHCI Host Controller provides high performance serial connectivity. It implements the

Link and Phy layers for IEEE 1394-1995 High Performance Serial Bus specification release 1.0 and 1394a-2000.

It is compliant with 1394 Open HCI 1.0 and 1.1 with DMA engine support for high performance data transfer via

a 32-bit bus master PCI host bus interface. The VT6307 supports 100, 200 and 400 M bit/sec transmission via an

integrated 2-port PHY. The VT6307 services two types of data packets: asynchronous and isochronous (real time).

The 1394 link core performs arbitration requesting, packet generation and checking, and bus cycle master

operations. It also has root node capability and performs retry operations. The VT6307 is ready to provide

industry-standard IEEE 1394 peripheral connections for desktop and mobile PC platforms. Support for the

VT6307 is built into Microsoft Windows 98, Windows ME, Windows 2000, and Windows XP.

32 bit CRC generator and checker for receive and transmit data

On-chip isochronous and asynchronous receive and transmit FIFOs for packets (2K for general receive plus

2K for isochronous transmit plus 2K for asynchronous transmit)

8 isochronous transmit contexts

4 isochronous receive contexts

1.3.9.2. Features

8050

8050

N/B Maintenance

N/B Maintenance

27

3-deep physical post-write queue

2-deep physical response queue

Dual buffer mode enhancements

Skip Processing enhancements

Block Read Request handling

Ack_tardy processing

L Firmware Hub for Intel 810, 810E, 815, 815E,815EP, 820, 840, 850 Chipsets

L Flexible Erase Capability

1.3.10 System Flash Memory (BIOS)

Uniform 4 K Byte Sectors

Uniform 16 K Byte overlay blocks for SST49LF002A

Uniform 64 K Byte overlay blocks for SST49LF004ATop boot block protection

16 K Byte for SST49LF002A

8050

8050

N/B Maintenance

N/B Maintenance

28

5-signal communication interface supporting byte Read and Write

33 MHz clock frequency operation

WP# and TBL# pins provide hardware write protect for entire chip and/or top Boot Block

Block Locking Register for all blocks

Standard SDP Command Set

Data# Polling and Toggle Bit for End-of-Write detection

5 GPI pins for system design flexibility

4 ID pins for multi-chip selection

L Single 3.0-3.6V Read and Write Operations

L Superior Reliability

L Firmware Hub Hardware Interface Mode

64 K Byte for SST49LF004A

Chip-Erase for PP Mode

8050

8050

N/B Maintenance

N/B Maintenance

29

JEDEC-standard 200-pin, small-outline, dual in-line memory module (SODIMM)

Utilizes 200 Mb/s and 266 Mb/s DDR SDRAM components

64MB (8 Meg x 64 [H]); 128MB (16 Meg x 64, [H] and [HD]); 256MB (32 Meg x 64 [HD]); 512MB

(64Meg x 64 [HD])

VDD= VDDQ= +2.5V 0.2V

VDDSPD = +2.2V to +5.5V

2.5V I/O (SSTL_2 compatible)

Commands entered on each positive CK edge

DQS edge-aligned with data for READs; center-aligned with data for WRITEs

Internal, pipelined double data rate (DDR) architecture; two data accesses per clock cycle Bidirectional data

strobe (DQS) transmitted/received with datai.e.,source-synchronous data capture

Differential clock inputs (CK and CK# - can be multiple clocks, CK0/CK0#, CK1/CK1#, etc.)

1.3.11 Memory System

1.3.11.1 64MB, 128MB, 256MB, 512MB (x64) 200-Pin DDR SDRAM SODIMM

8050

8050

N/B Maintenance

N/B Maintenance

30

Four internal device banks for concurrent operation

Selectable burst lengths: 2, 4, or 8

Auto precharge option

Auto Refresh and Self Refresh Modes

15.6s (MT4VDDT864H, MT8VDDT1664HD), 7.8125s (MT4VDDT1664H, MT8VDDT3264HD,

MT8VDDT6464HD) maximum average periodic refresh interval

Serial Presence Detect (SPD) with EEPROM

Fast data transfer rates PC2100 or PC1600

Selectable READ CAS latency for maximum compatibility

Gold-plated edge contacts

1.3.12 PHY: 3.3-V 10Base-T/100Base-TX Integrated PHY Ceiver ,The ICS1893

is a low-power, physical-layer device (PHY)

General

The Realtek RTL8100C(L) is a highly integrated, cost-effective single-chip Fast Ethernet controller that provides

32-bit performance, PCI bus master capability, and full compliance with IEEE 802.3u 100Base-T specifications

8050

8050

N/B Maintenance

N/B Maintenance

31

and IEEE 802.3x Full Duplex Flow Control. It also supports the Advanced Configuration Power management

Interface (ACPI), PCI power management for modern operating systems that are capable of Operating System

Directed Power Management (OSPM) to achieve the most efficient power management possible.The

RTL8100C(L) does not support CardBus mode as the RTL8139C does. In addition to the ACPI feature, the

RTL8100C(L) also supports remote wake-up (including AMD Magic Packet, LinkChg, and Microsoft wake-

upframe) in both ACPI and APM environments. The RTL8100C(L) is capable of performing an internal reset

through the application of auxiliary power. When auxiliary power is applied and the main power remains off, the

RTL8100C(L) is ready and waiting for the Magic Packet or Link Change to wake the system up. Also, the

LWAKE pin provides 4 different output signals including active high, active low, positive pulse, and negative

pulse. The versatility of the RTL8100C(L) LWAKE pin provides motherboards with Wake-On-LAN (WOL)

functionality. The RTL8100C(L) also supports Analog Auto-Power-down, that is, the analog part of the

RTL8100C(L) can be shut down temporarily according to user requirements or when the RTL8100C(L) is in a

power down state with the wakeup function disabled.In addition, when the analog part is shut down and the Isolate

B pin is low (i.e. the main power is off), then both the analog and digital parts stop functioning and the power

consumption of the RTL8100C(L) will be negligible. The RTL8100C(L) also supports an auxiliary power

auto-detect function, and will auto-configure related bits of their own PCI power management registers in

PCI configuration space.

128 pin QFP/LQFP

Integrated Fast Ethernet MAC, Physical chip and transceiver in one chip

10 Mb/s and 100 Mb/s operation

Supports 10 Mb/s and 100 Mb/s N-way Auto-negotiation operation

8050

8050

N/B Maintenance

N/B Maintenance

32

- Compliant to PCI Revision 2.2Supports PCI clock 16.75MHz-40MHz

- Supports PCI target fast back-to-back transaction

- Provides PCI bus master data transfers and PCI

- Memory space or I/O space mapped data transfers of RTL8100C(L)'s operational registers

- Supports PCI VPD (Vital Product Data)

- Supports ACPI, PCI power management

Supports 25MHz crystal or 25MHz OSC as the internal

Clock source. The frequency deviation of either crystal or OSC must be within 50 PPM.

Compliant to PC99/PC2001 standard

Supports Wake-On-LAN function and remote wake-up (Magic Packet*, LinkChg and Microsoft wake-

up frame)

Supports 4 Wake-On-LAN (WOL) signals (active high, active low, positive pulse, and negative pulse)

Supports auxiliary power-on internal reset, to be ready for remote wake-up when main power still

remains off

PCI local bus single-chip Fast Ethernet controller

8050

8050

N/B Maintenance

N/B Maintenance

33

Supports auxiliary power auto-detect, and sets the related capability of power management registers in PCI

configuration space.

Includes a programmable, PCI burst size and early Tx/Rx threshold. Supports a 32-bit general-purpose

timer with the external PCI clock as clock source, to generate timer-interrupt

Contains two large (2Kbyte) independent receive and transmit FIFOs

Advanced power saving mode when LAN function or wakeup function is not used

Uses 93C46 (64*16-bit EEPROM) to store resource configuration, ID parameter, and VPD data.

Supports LED pins for various network activity indications

Supports loopback capability

Half/Full duplex capability

Supports Full Duplex Flow Control (IEEE 802.3x)

8050

8050

N/B Maintenance

N/B Maintenance

34

2.1 System View

2.1.1 Front View

Line Out Connector

1394 Jack

MIC In Connector

Line In Connector

2.1.2 Left-side View

USB Ports *1

RJ-11 Connector

VGA Port

Ventilation Openings

S-Video Port

SD Card Slot

O

O

O

OO

O

Top Cover Latch

OO

O

O

O

O O

RJ-45 Connector

PCMCIA Card Socket

2. System View and Disassembly

8050

8050

N/B Maintenance

N/B Maintenance

35

2.1.3 Right-side View

2.1.4 Rear View

Kensington Lock

Power Connector

CD-ROM/DVD-ROM Drive

USB Port*2

O O

O

O

O

Kensington Lock

8050

8050

N/B Maintenance

N/B Maintenance

36

2.1.5 Bottom View

Hard Disk Drive

DDR SDRAM Card

Wireless Card

2.1.6 Top-open View

LCD Screen

Device LED Indicators

Keyboard

Stereo Speaker Set

Power Button

Battery Park

CPU

Touch Pad

Hard Disk Drive Indicator

Battery Power Charging Indicator

O

O

O

O

O

O

Stereo Speaker Set

O

O

O

O

O

O

O

O

O

Power Indicator

8050

8050

N/B Maintenance

N/B Maintenance

37

2.2 System Disassembly

The section discusses at length each major component for disassembly/reassembly and show corresponding

illustrations.Use the chart below to determine the disassembly sequence for removing components from the

notebook.

NOTE: Before you start to install/replace these modules, disconnect all peripheral devices and make sure the

notebook is not turned on or connected to AC power.

Modular Components

LCD Assembly Components

Base Unit Components

NOTEBOOK

2.2.1 Battery Pack

2.2.2 Keyboard

2.2.3 CPU

2.2.4 HDD Module

2.2.5 DVD-ROM Drive

2.2.6 Wireless Card

2.2.7 Modem Card

2.2.8 DDR-SDRAM

2.2.9 LCD Assembly

2.2.10 LCD Panel

2.2.11 Inverter Board

2.2.12 System Board

2.2.13 Touch Pad

8050

8050

N/B Maintenance

N/B Maintenance

38

1. Replace the battery pack into the compartment. The battery pack should be correctly connected when you

hear a clicking sound.

2. Slide the release lever to the lock ( ) position.

2.2.1 Battery Pack

Disassembly

1. Carefully put the notebook upside down.

2. Slide the two release lever outwards to the unlock ( ) position (), while take the battery pack out of the

compartment (). (Figure 2-1)

Figure 2-1 Remove the battery pack

Reassembly

8050

8050

N/B Maintenance

N/B Maintenance

39

2.2.2 Keyboard

Disassembly

1. Remove the battery pack. (Refer to section 2.2.1 Disassembly)

2. Open the top cover.

3. Loosen the four latches locking the keyboard. (Figure 2-2)

4. Slightly lift up the keyboard and disconnect the cable from the mother board, then separate the keyboard.

(Figure 2-3)

Figure 2-2 Loosen the four latches Figure 2-3 Disconnect the cable

Reassembly

1. Reconnect the keyboard cable and fit the keyboard back into place with four latches.

2. Replace the battery pack. (Refer to section 2.2.1 reassembly)

8050

8050

N/B Maintenance

N/B Maintenance

40

1. Remove the battery pack. (Refer to section 2.2.1 Disassembly)

2. Remove three screws fastening the heatsink cover. (Figure 2-4)

3. Remove three spring screws that secure the heatsink upon the CPU and disconnect the fans power cord

from system board. (Figure 2-5)

2.2.3 CPU

Disassembly

Figure 2-4 Remove three screws Figure 2-5 Free the heatsink

8050

8050

N/B Maintenance

N/B Maintenance

41

Reassembly

1. Carefully, align the arrowhead corner of the CPU with the beveled corner of the socket, then insert CPU

pins into the holes. Tighten the screw by a flat screwdriver to locking the CPU.

2. Connect the fans power cord to the system board, fit the heatsink upon the CPU and secure with three

spring screws.

3. Replace the CPU cover and secure with three screws.

4. Replace the battery pack. (Refer to section 2.2.1 reassembly)

4. To remove the existing CPU, Loosen the screw by a flat screwdriver,upraise the CPU socket to unlock

the CPU. (Figure 2-6)

Figure 2-6 Remove the CPU

8050

8050

N/B Maintenance

N/B Maintenance

42

2.2.4 HDD Module

Disassembly

1. Carefully put the notebook upside down. Remove the battery pack. (Refer to section 2.2.1 Disassembly)

2. Remove two screws fastening the HDD compartment cover. (Figure 2-7)

3. Remove the one screw and slide the HDD module out of the compartment. (Figure 2-8)

Figure 2-8 Remove HDD module Figure 2-7 Remove the HDD compartment cover

8050

8050

N/B Maintenance

N/B Maintenance

43

4. Remove four screws to separate the hard disk drive from the bracket, remove four screws.

(Figure 2-9)

Reassembly

1. Attach the bracket to hard disk drive and secure with four screws.

2. Slide the HDD module into the compartment and secure with one screw.

3. Place the HDD compartment cover and secure with two screws.

4. Replace the battery pack. (Refer to section 2.2.1 reassembly)

Figure 2-9 Remove hard disk drive

8050

8050

N/B Maintenance

N/B Maintenance

44

2.2.5 CD/DVD-ROM Drive

Disassembly

Figure 2-10 Remove one screw

1. Carefully put the notebook upside down. Remove the battery pack. (Refer to section 2.2.1 Disassembly)

2. Remove one screw fastening the CD/DVD-ROM drive. (Figure 2-10)

3. Push firmly to release the tray. Then gently pull out the CD/DVD-ROM drive by holding the tray that

pops out. (Figure 2-11)

Reassembly

1. Push the CD/DVD-ROM drive into the compartment and secure with one screw.

2. Replace the battery pack. (Refer to section 2.2.1 reassembly)

Figure 2-11 Remove the CD/DVD-

ROM drive

8050

8050

N/B Maintenance

N/B Maintenance

45

2.2.6 Wireless Card

Disassembly

1. Carefully put the notebook upside down. Remove the battery pack. (Refer to sections 2.2.1 Disassembly)

2. Remove the two screws fastening the Mini PCI compartment cover. (Figure 2-12)

3. Disconnect the wireless cards antennae first (). Then pull the retaining clips outwards () and remove

the wireless card (). (Figure 2-13)

Figure 2-12 Remove two screws

Figure 2-13 Remove the Wireless card

Reassembly

1. To install the wireless card, match the wireless card 's notched part with the socket's projected part and firmly

insert it into the socket. Then push down until the retaining clips lock the wireless card into position. Then

sure that the antennae fully populated.

2. Tighten the screws to secure the wireless card compartment cover to the housing.

3. Replace the battery pack. (Refer to section 2.2.1 reassembly)

8050

8050

N/B Maintenance

N/B Maintenance

46

2.2.7 Modem Card

Disassembly

1. Carefully put the notebook upside down. Remove the battery pack. (Refer to section 2.2.1 Disassembly)

2. Remove two screws fastening modem cards compartment cover. (Refer to steps 1-2 of section 2.2.6

Disassembly)

3. Remove two screws fastening the modem card. (Figure 2-14)

4. Lift up the modem card and disconnect the cord. (Figure 2-15)

Figure 2-14 Remove two screws Figure 2-15 Disconnect the cord

Reassembly

1. Reconnect the cord and fit the modem card.

2. Fasten the modem card by two screws.

3. Replace the modem cards compartment cover by two screws. (Refer to step 2 of section 2.2.6 reassembly).

4. Replace the battery pack. (Refer to section 2.2.1 reassembly)

8050

8050

N/B Maintenance

N/B Maintenance

47

2.2.8 DDR-SDRAM

Disassembly

1. Carefully put the notebook upside down. And remove the battery pack. (See section 2.2.1 disassembly)

2. Remove two screws fastening the DDR compartment cover to access the SO-DIMM socket. (Figure 2-16)

Figure 2-16 Remove the cover Figure 2-17 Remove the SO-DIMM

3. Pull the retaining clips outwards () and remove the SO-DIMM (). (Figure 2-17)

Reassembly

1. To install the DDR, match the DDR's notched part with the socket's projected part and firmly insert the

SO-DIMM into the socket at 20-degree angle. Then push down until the retaining clips lock the DDR

into position.

2. Replace two screws to fasten the DDR compartment cover.

3. Replace the battery pack. (See section 2.2.1 reassembly)

8050

8050

N/B Maintenance

N/B Maintenance

48

2.2.9 LCD ASSY

Disassembly

1. Remove the battery pack, keyboard,CPU, hard disk drive, CD/DVD-drive and wireless card.

(See sections 2.2.1,2.2.2, 2.2.3, 2.2.4, 2.2.5 and 2.2.6 Disassembly)

2. Remove the nineteen screws on the bottom of notebook. (Figure 2-18)

3. Remove the four screws that secure the hinge cover. (Figure 2-19)

Figure 2-18 Remove nineteen screws Figure 2-19 Remove four screws

8050

8050

N/B Maintenance

N/B Maintenance

49

4. Remove the two screws and disconnect the touch pads cable, then free the top cover.(Figure 2-20)

5. Remove the two hinge covers. (Figure 2-21)

Figure 2-20 Free the Top cover Figure 2-21 Remove the hinge covers

8050

8050

N/B Maintenance

N/B Maintenance

50

Figure 2-22 Remove the four screws and

Disconnect the two cables

Figure 2-23 Remove the eight screws

6. Disconnect the two cables and remove the four screws. (Figure 2-22)

7. Remove the eight screws. (Figure 2-23)

8050

8050

N/B Maintenance

N/B Maintenance

51

8. Carefully pull the antenna wires out. Now you can lift up the LCD ASSY from base unit. (Figure 2-24)

Figure 2-24 Free the LCD ASSY

1. Attach the LCD assembly to the base unit and secure with four screws.

2. Rip the antenna wires back into Min-PCI compartment.

3. Reconnect the two cables to the system board. Screw the hinge covers by two screws.

4. Replace the shield and secure with eight screws.

5. Replace the top cover and secure with two screws. And reconnect the touch pads cable.

6. Upside down the notebook. secure the housing by nineteen screws and secure two screws in the rear.

7. Replace the Wireless card, CD/DVD-ROM, hard disk drive, CPU, keyboard and battery pack. (Refer to

sections 2.2.6, 2.2.5, 2.2.4, 2.2.3, 2.2.2 and 2.2.1 reassembly)

Reassembly

8050

8050

N/B Maintenance

N/B Maintenance

52

2.2.10 LCD Panel

Disassembly

1. Remove the battery, keyboard, hard disk drive, CD/DVD-ROM drive and LCD assembly. (Refer to

section 2.2.1, 2.2.2, 2.2.4, 2.2.5 and 2.2.9 Disassembly)

2. Remove the two rubber pads and two screws on the corners of the panel. (Figure 2-25)

3. Insert a flat screwdriver to the lower part of the LCD cover and gently pry the frame out. Repeat the

process until the cover is completely separated from the housing.

4. Remove the twelve screws and disconnect the cable. (Figure 2-26)

Figure 2-26 Remove twelve screws and

disconnect the cable

Figure 2-25 Remove LCD cover

8050

8050

N/B Maintenance

N/B Maintenance

53

Reassembly

1. Replace the cable to the LCD.

2. Attach the LCD panels bracket back to LCD panel and secure with six screws.

3. Replace the LCD panel into LCD housing.and reconnect two cables to inverter board and secure with two

screws.

4. Fasten the LCD panel by ten screws.

5. Fit the LCD cover and secure with two screws and rubber pads.

6. Replace the LCD assembly, CD/DVD-ROM drive, hard disk drive, keyboard, battery pack. (See sections

2.2.9, 2.2.5, 2.2.4, 2.2.2, and 2.2.1 reassembly)

Figure 2-28 Free the LCD panel

5. Remove the six screws that secure the LCD bracket. (Figure 2-27)

6. Disconnect the cable to free the LCD panel. (Figure 2-28)

Figure 2-27 Remove the six screws

8050

8050

N/B Maintenance

N/B Maintenance

54

2.2.11 Inverter Board

Disassembly

1. Remove the battery, keyboard, hard disk drive, CD/DVD-ROM drive and LCD assembly. (Refer to

section 2.2.1, 2.2.2, 2.2.4, 2.2.5 and 2.2.9 Disassembly)

2. Remove the LCD cover and LCD panel. (Refer to the steps 1-4 of section 2.2.10 Disassembly )

3. Remove the one screw fastening the inverter board and disconnect the cable, Then free the inverter board.

(Figure 2-29)

Figure 2-29 Free the inverter board

Reassembly

1. Reconnect the cable. Fit the inverter board back into place and secure with one screw.

2. Replace the LCD Panel and LCD cover. (Refer to section 2.2.10 reassembly)

3. Replace the LCD assembly. (Refer to section 2.2.9 reassembly)

4. Replace the CD/DVD-ROM drive, hard disk drive, keyboard and battery pack. (Refer to sections 2.2.5,

2.2.4, 2.2.2 and 2.2.1 reassembly)

8050

8050

N/B Maintenance

N/B Maintenance

55

1. Remove the battery, keyboard, hard disk drive, CD/DVD-ROM drive, Wireless card and LCD assembly.

(Refer to sections 2.2.1, 2.2.2, 2.2.4, 2.2.5, 2.2.6 and 2.2.9 Disassembly)

2. Remove the four screws that secure the system board and disconnect the two speakers cables. Then lift it

up from the housing. (Figure 2-30)

3. Disconnect the one speakers cables from the system board and remove the two screws, Then separate the

bracket and free the system board. (Figure 2-31)

2.2.12 System Board

Disassembly

Figure 2-30 Remove four screws and

disconnect the two cables Figure 2-31 Free the system board

Reassembly

1. Fit the bracket and secure with two screws .

2. Turn over the system board. Reconnect the speakers cords.

3. Replace the system board back into the housing and secure with four screws, then reconnect the cable.

4. Replace the LCD assembly, CD/DVD-ROM, HDD, keyboard and battery pack. (Refer to previous section

reassembly)

8050

8050

N/B Maintenance

N/B Maintenance

56

2.2.13 Touch Pad

Disassembly

1. Remove the battery pack, keyboard, hard disk drive and CD/DVD-drive. (See sections 2.2.1,2.2.2 , 2.2.4 and

2.2.5 Disassembly)

2. Remove the top cover. (See steps 1-5 in section 2.2.9 Disassembly)

3. Remove the two screws and free the touch pad. (Figure 2-32).

Reassembly

1. Replace the touch pad and secure the two screws.

2. Replace the top cover. (Refer to the section in 2.2.9 reassembly)

3. Replace the battery pack, keyboard, hard disk drive and CD/DVD-drive. (See sections 2.2.1,2.2.2 ,

2.2.4 and 2.2.5 Disassembly).

Figure 2-32 Remove the two screws

8050

8050

N/B Maintenance

N/B Maintenance

57

3. Definition & Location of Connectors / Switches

3.1 Mother Board - A

J1 : Inverter Board Connector

J2 : LCD panel connector

J3 : Internal Left Speaker Connector

J4 : Touch-pad Module Connector

J5 : Internal Key-board Connector

J6 : PCMCIA Card Connector

J7 : Internal Right Speaker Connector

SW2 : Power Button

SW4 : Left Button Switch of Touch-pad

SW5 : Right Button Switch of Touch-pad

J6

J2

J1

J3

J5

J4

J7

SW4

SW5

SW2

8050

8050

N/B Maintenance

N/B Maintenance

58

3. Definition & Location of Connectors / Switches

3.2 Mother Board - B

PJ701 : AC Adaptor Connector

J701&J706 : USB Port Connector

J702 : CRT Connector

J703 : Battery Connector

J704 : External VGA Connector

J705 : Internal Subwoofer Speaker

J707: FAN Connector

J708 : CD-ROM IDE Connector

J709: Lan & Phone Lan Connector

J710 : RTC Battery Connector

J711&J712 : DDR SO-DIMM Module Socket

J713 : Mini-PCI Connector

J714 : Hard Disk Driver Connector

-----To next page-----

J706

PJ701

J701

J713

J

7

1

1

J

7

1

2

J705

J703

J708 J714

J710

J702 J704

J707

J709

8050

8050

N/B Maintenance

N/B Maintenance

59

3. Definition & Location of Connectors / Switches

3.2 Mother Board - B

-----Continue From Previous Page-----

J715&J717: Modem Daughter Board Connector

J716 : SD&MS Card Socket

J718 : IEEE 1394 Connector

J719 : External Micro Phone Jack

J720 : Line Out HP/OPT Jack

J721 : External Line-in Jack

J719

J721

J720

J715

J717

J718

J716

8050

8050

N/B Maintenance

N/B Maintenance

60

4. Definition & Location of Major Components

4.1 Mother Board - A

PU2 : +3VS/+5VS Voltage Generator

PU3 : CPU Core Voltage Generator

PU14: +1.8V/+1.35V Voltage Generator

PU15 : +2.5VS/+1.25V Voltage Generator

U2 : TV Encoder Controller

U15: SYS BIOS Controller

U16: WINBOND KBC Controller

U524: TPA02012 Audio Amplifier

PU2

PU3

U2

PU14

PU15

U16

U524

U15

8050

8050

N/B Maintenance

N/B Maintenance

61

4. Definition & Location of Major Components

4.2 Mother Board - B

U706 : Thermal Sensor/Fan Controller

U713 : Intel BANIAS CPU

U714 : Intel 855GM/GME North Bridge

U715 : Intel ICH4-M South Bridge

U719 : LAN-RTL8100CL Controller

U724 : IEEE1394 Controller

U725 : SUBWOOFER AMP Controller

U726 : Audio CODEC(ALC655)

U727 : CB710 Card Bus Reader Controller

U715

U714

U713

U719

U727

U724

U706

U725

U726

8050

8050

N/B Maintenance

N/B Maintenance

62

5. Pin Descriptions of Major Components

5.1 Intel Banias Pentium M Processor(1)

Signal Name Type Description

A[31:3]#

I/O A[31:3]# (Address) define a 2 32 -byte physical memory address space.

In sub-phase 1 of the address phase, these pins transmit the address of a

transaction. In sub-phase 2, these pins transmit transaction type

information. These signals must connect the appropriate pins of both

agents on the Intel Pentium M processor system bus. A[31:3]# are source

synchronous signals and are latched into the receiving buffers by

ADSTB[1:0]#. Address signals are used as straps which are sampled

before RESET# is deasserted.

A20M# I If A20M# (Address-20 Mask) is asserted, the processor masks physical

address bit 20 (A20#) before looking up a line in any internal cache and

before driving a read/write transaction on the bus. Asserting A20M#

emulates the 8086 processor's address wrap-around at the 1-Mbyte

boundary. Assertion of A20M# is only supported in real mode.

A20M# is an asynchronous signal. However, to ensure recognition of

this signal following an Input/Output write instruction, it must be valid

along with the TRDY# assertion of the corresponding Input/Output

Write bus transaction.

ADS# I/O ADS# (Address Strobe) is asserted to indicate the validity of the

transaction address on the A[31:3]# and REQ[4:0]# pins. All bus agents

observe the ADS# activation to begin parity checking, protocol

checking, address decode, internal snoop, or deferred reply ID match

operations associated with the new transaction.

ADSTB[1:0]# I/O Address strobes are used to latch A[31:3]# and REQ[4:0]# on their rising

and falling edges. Strobes are associated with signals as shown below.

Signals Associated Strobe

REQ[4:0]#, A[16:3]# ADSTB[0]#

A[31:17]# ADSTB[1]#

BCLK[1:0] I The differential pair BCLK (Bus Clock) determines the system bus

frequency. All processor system bus agents must receive these signals to

drive their outputs and latch their inputs.

BNR# I/O BNR# (Block Next Request) is used to assert a bus stall by any bus agent

that is unable to accept new bus transactions. During a bus stall, the

current bus owner cannot issue any new transactions.

BPM[2:0]#

BPM[3]

O

I/O

BPM[3:0]# (Breakpoint Monitor) are breakpoint and performance

monitor signals. They are outputs from the processor that indicate the

status of breakpoints and programmable counters used for monitoring

processor performance. BPM[3:0]# should connect the appropriate pins

of all Intel Pentium M processor system bus agents. This includes debug

or performance monitoring tools.

Signal Name Type Description

BPRI# I BPRI# (Bus Priority Request) is used to arbitrate for ownership of the

processor system bus. It must connect the appropriate pins of both

processor system bus agents. Observing BPRI# active (as asserted by

the priority agent) causes the other agent to stop issuing new requests,

unless such requests are part of an ongoing locked operation. The

priority agent keeps BPRI# asserted until all of its requests are

completed, then releases the bus by deasserting BPRI#.

BR0# I/O BR0# is used by the processor to request the bus. The arbitration is done

between the Intel Pentium M processor (Symmetric Agent) and the

MCH-M (High Priority Agent) of the Intel 855PM or Intel 855GM

chipset.

COMPP3:0] Analog COMP[3:0] must be terminated on the system board using precision

(1% tolerance) resistors. Refer to the platform design guides for more

implementation details.

D[63:0]# I/O D[63:0]# (Data) are the data signals. These signals provide a 64-bit data

path between the processor system bus agents, and must connect the

appropriate pins on both agents. The data driver asserts DRDY# to

indicate a valid data transfer.

D[63:0]# are quad-pumped signals and will thus be driven four times in

a common clock period. D[63:0]# are latched off the falling edge of

both DSTBP[3:0]# and DSTBN[3:0]#. Each group of 16 data signals

correspond to a pair of one DSTBP# and one DSTBN#. The following

table shows the grouping of data signals to data strobes and DINV#.

Quad-Pumped Signal Groups

Data Group DSTBN#/DSTBP# DINV#

D[15:0]# 0 0

D[31:16]# 1 1

D[47:32]# 2 2

D[63:48]# 3 3

Furthermore, the DINV# pins determine the polarity of the data signals.

Each group of 16 data signals corresponds to one DINV# signal. When

the DINV# signal is active, the corresponding data group is inverted and

therefore sampled active high.

DBR# O DBR# (Data Bus Reset) is used only in processor systems where no

debug port is implemented on the system board. DBR# is used by a

debug port interposer so that an in-target probe can drive system reset. If

a debug port is implemented in the system, DBR# is a no connect.

DBR# is not a processor signal.

8050

8050

N/B Maintenance

N/B Maintenance

63

5.1 Intel Banias Pentium M Processor(2)

Signal Name Type Description

DBSY# I/O DBSY# (Data Bus Busy) is asserted by the agent responsible for driving

data on the processor system bus to indicate that the data bus is in use.

The data bus is released after DBSY# is deasserted. This signal must

connect the appropriate pins on both processor system bus agents.

DEFER# I DEFER# is asserted by an agent to indicate that a transaction cannot be

guaranteed in-order completion. Assertion of DEFER# is normally the

responsibility of the addressed memory or Input/Output agent. This

signal must connect the appropriate pins of both processor system bus

agents.

DINV[3:0]#

I/O DINV[3:0]# (Data Bus Inversion) are source synchronous and indicate

the polarity of the D[63:0]# signals. The DINV[3:0]# signals are

activated when the data on the data bus is inverted. The bus agent will

invert the data bus signals if more than half the bits, within the covered

group, would change level in the next cycle.

DINV[3:0]# Assignment To Data Bus

Bus Signal Data Bus Signals

DINV[3]# D[63:48]#

DINV[2]# D[47:32]#

DINV[1]# D[31:16]#

DINV[0]# D[15:0]#

DPSLP# I DPSLP# when asserted on the platform causes the processor to

transition from the Sleep state to the Deep Sleep state. In order to return

to the Sleep state, DPSLP# must be deasserted. DPSLP# is driven by the

ICH4-M component and also connects to the MCH-M component of the

Intel 855PM or Intel 855GM chipset.

DRDY# I/O DRDY# (Data Ready) is asserted by the data driver on each data

transfer, indicating valid data on the data bus. In a multi-common clock

data transfer, DRDY# may be deasserted to insert idle clocks. This

signal must connect the appropriate pins of both processor system bus

agents.

DSTBN[3:0]# I/O Data strobe used to latch in D[63:0]#.

Signals Associated Strobe

D[15:0]#, DINV[0]# DSTBN[0]#

D[31:16]#, DINV[1]# DSTBN[1]#

D[47:32]#, DINV[2]# DSTBN[2]#

D[63:48]#, DINV[3]# DSTBN[3]#

DSTBP[3:0]# I/O Data strobe used to latch in D[63:0]#.

Signals Associated Strobe

D[15:0]#, DINV[0]# DSTBP[0]#

D[31:16]#, DINV[1]# DSTBP[1]#

D[47:32]#, DINV[2]# DSTBP[2]#

D[63:48]#, DINV[3]# DSTBP[3]#

Signal Name Type Description

DPWR# I DPWR# is a control signal from the Intel 855PM and Intel 855GM

chipsets used to reduce power on the Intel Pentium M data bus input

buffers.

FERR#/PBE# O FERR# (Floating-point Error)/PBE#(Pending Break Event) is a

multiplexed signal and its meaning is qualified by STPCLK#. When

STPCLK# is not asserted, FERR#/PBE# indicates a floating point when

the processor detects an unmasked floating-point error. FERR# is

similar to the ERROR# signal on the Intel 80387 coprocessor, and is

included for compatibility with systems using MS-DOS* type

floating-point error reporting. When STPCLK# is asserted, an assertion

of FERR#/PBE# indicates that the processor has a pending break event

waiting for service. The assertion of FERR#/PBE# indicates that the

processor should be returned to the Normal state. When FERR#/PBE# is

asserted, indicating a break event, it will remain asserted until

STPCLK# is deasserted. Assertion of PREQ# when STPCLK# is active

will also cause an FERR# break event.

GTLREF I GTLREF determines the signal reference level for AGTL+ input pins.

GTLREF should be set at 2/3 VCCP . GTLREF is used by the AGTL+

receivers to determine if a signal is a logical 0 or logical 1.

HIT#

HITM#

I/O

I/O

HIT# (Snoop Hit) and HITM# (Hit Modified) convey transaction snoop

operation results. Either system bus agent may assert both HIT# and

HITM# together to indicate that it requires a snoop stall, which can be

continued by reasserting HIT# and HITM# together.

IERR# O IERR# (Internal Error) is asserted by a processor as the result of an

internal error. Assertion of IERR# is usually accompanied by a

SHUTDOWN transaction on the processor system bus. This transaction

may optionally be converted to an external error signal (e.g., NMI) by

system core logic. The processor will keep IERR# asserted until the

assertion of RESET#, BINIT#, or INIT#.

IGNNE# I IGNNE# (Ignore Numeric Error) is asserted to force the processor to

ignore a numeric error and continue to execute noncontrol floating-point

instructions. If IGNNE# is deasserted, the processor generates an

exception on a noncontrol floating-point instruction if a previous

floating-point instruction caused an error. IGNNE# has no effect when

the NE bit in control register 0 (CR0) is set.

IGNNE# is an asynchronous signal. However, to ensure recognition of

this signal following an Input/Output write instruction, it must be valid

along with the TRDY# assertion of the corresponding Input/Output

Write bus transaction.

REQ[4:0]# I/O REQ[4:0]# (Request Command) must connect the appropriate pins of

both processor system bus agents. They are asserted by the current bus

owner to define the currently active transaction type. These signals are

source synchronous to ADSTB[0]#.

8050

8050

N/B Maintenance

N/B Maintenance

64

Signal Name Type Description

INIT#

I INIT# (Initialization), when asserted, resets integer registers inside the

processor without affecting its internal caches or floating-point registers.

The processor then begins execution at the power on Reset vector

configured during power on configuration. The processor continues to

handle snoop requests during INIT# assertion. INIT# is an asynchronous

signal. However, to ensure recognition of this signal following an

Input/Output Write instruction, it must be valid along with the TRDY#

assertion of the corresponding Input/Output Write bus transaction.

INIT# must connect the appropriate pins of both processor system bus

agents. If INIT# is sampled active on the active to inactive transition of

RESET#, then the processor executes its Built-in Self-Test (BIST)

LINT[1:0] I LINT[1:0] (Local APIC Interrupt) must connect the appropriate pins of

all APIC Bus agents. When the APIC is disabled, the LINT0 signal

becomes INTR, a maskable interrupt request signal, and LINT1

becomes NMI, a nonmaskable interrupt. INTR and NMI are backward

compatible with the signals of those names on the Pentium processor.

Both signals are asynchronous.

Both of these signals must be software configured using BIOS

programming of the APIC register space and used either as NMI/INTR

or LINT[1:0]. Because the APIC is enabled by default after Reset,

operation of these pins as LINT[1:0] is the default configuration.

LOCK# I/O LOCK# indicates to the system that a transaction must occur atomically.

This signal must connect the appropriate pins of both processor system

bus agents. For a locked sequence of transactions, LOCK# is asserted

from the beginning of the first transaction to the end of the last

transaction.

When the priority agent asserts BPRI# to arbitrate for ownership of the

processor system bus, it will wait until it observes LOCK# deasserted.

This enables symmetric agents to retain ownership of the processor

system bus throughout the bus locked operation and ensure the

atomicity of lock.

PRDY#

O Probe Ready signal used by debug tools to determine processor debug

readiness.

PREQ# I Probe Request signal used by debug tools to request debug operation of

the processor.

PROCHOT# O PROCHOT# (Processor Hot) will go active when the processor

temperature monitoring sensor detects that the processor has reached its

maximum safe operating temperature. This indicates that the processor

Thermal Control Circuit has been activated, if enabled.

This signal may require voltage translation on the motherboard.

PSI# O Processor Power Status Indicator signal. This signal is asserted when the

processor is in a lower state (Deep Sleep and Deeper Sleep).

Signal Name Type Description

PWRGOOD I PWRGOOD (Power Good) is a processor input. The processor requires

this signal as a clean indication that the clocks and power supplies are

stable and within their specifications. Clean implies that the signal will

remain low (capable of sinking leakage current), without glitches, from

the time that the power supplies are turned on until they come within

specification. The signal must then transition monotonically to a high

state. PWRGOOD can be driven inactive at any time, but clocks and

power must again be stable before a subsequent rising edge of

PWRGOOD.

The PWRGOOD signal must be supplied to the processor; it is used to

protect internal circuits against voltage sequencing issues. It should be

driven high throughout the boundary scan operation.

ITP_CLK[1:0] I ITP_CLK[1:0] are copies of BCLK that are used only in processor

systems where no debug port is implemented on the system board.

ITP_CLK[1:0] are used as BCLK[1:0] references for a debug port

implemented on an interposer. If a debug port is implemented in the

system, ITP_CLK[1:0] are no connects. These are not processor signals.

RESET# I Asserting the RESET# signal resets the processor to a known state and

invalidates its internal caches without writing back any of their contents.

For a power-on Reset, RESET# must stay active for at least two

milliseconds after VCC and BCLK have reached their proper

specifications. On observing active RESET#, both system bus agents

will deassert their outputs within two clocks. All processor straps must

be valid within the specified setup time before RESET# is deasserted.

RS[2:0]# I RS[2:0]# (Response Status) are driven by the response agent (the agent

responsible for completion of the current transaction), and must connect

the appropriate pins of both processor system bus agents.

RSVD - These pins are RESERVED and must be left unconnected on the board.

However, it is recommended that routing channels to these pins on the

board be kept open for possible future use. Please refer to the platform

design guides for more details.

SLP# I SLP# (Sleep), when asserted in Stop-Grant state, causes the processor to

enter the Sleep state. During Sleep state, the processor stops providing

internal clock signals to all units, leaving only the Phase-Locked Loop

(PLL) still operating. Processors in this state will not recognize snoops

or interrupts. The processor will recognize only assertion of the

RESET# signal, deassertion of SLP#, and removal of the BCLK input

while in Sleep state. If SLP# is deasserted, the processor exits Sleep

state and returns to Stop-Grant state, restarting its internal clock signals

to the bus and processor core units. If DPSLP# is asserted while in the

Sleep state, the processor will exit the Sleep state and transition to the

Deep Sleep state.

5.1 Intel Banias Pentium M Processor(3)

8050

8050

N/B Maintenance

N/B Maintenance

65

Signal Name Type Description

SMI# I SMI# (System Management Interrupt) is asserted asynchronously by

system logic. On accepting a System Management Interrupt, the

processor saves the current state and enter System Management Mode

(SMM). An SMI Acknowledge transaction is issued, and the processor

begins program execution from the SMM handler.

If SMI# is asserted during the deassertion of RESET# the processor will

tristate its outputs.

STPCLK# I STPCLK# (Stop Clock), when asserted, causes the processor to enter a

low power Stop-Grant state. The processor issues a Stop-Grant

Acknowledge transaction, and stops providing internal clock signals to

all processor core units except the system bus and APIC units. The

processor continues to snoop bus transactions and service interrupts

while in Stop-Grant state. When STPCLK# is deasserted, the processor

restarts its internal clock to all units and resumes execution. The

assertion of STPCLK# has no effect on the bus clock; STPCLK# is an

asynchronous input.

TCK I TCK (Test Clock) provides the clock input for the processor Test Bus

(also known as the Test Access Port).

TDI I TDI (Test Data In) transfers serial test data into the processor. TDI

provides the serial input needed for JTAG specification support.

TDO O TDO (Test Data Out) transfers serial test data out of the processor. TDO

provides the serial output needed for JTAG specification support.

TEST1,

TEST2,

TEST3

I TEST1, TEST2, and TEST3 must be left unconnected but should have a

stuffing option connection to V SS separately using 1-k, pull-down

resisitors.

THERMDA Other Thermal Diode Anode.

THERMDC Other Thermal Diode Cathode.