Final Rep

Uploaded by

Subramaniam GanesanFinal Rep

Uploaded by

Subramaniam GanesanANALYTICAL MODELING OF TUNNEL FETS

FOR CIRCUIT SIMULATORS

submitted by

ANANDAN NARENDIRAN

A thesis submitted to the

FACULTY OF INFORMATION AND COMMUNICATION ENGINEERING

In partial fulllment of the requirements for the award of the degree of

MASTER OF ENGINEERING

in

APPLIED ELECTRONICS

COLLEGE OF ENGINEERING, GUINDY

ANNA UNIVERSITY

Chennai 600 025

MAY 2012

BONAFIDE CERTIFICATE

Certied that this project titled Analytical Modeling of Tunnel FETs for circuit

simulators is the bonade work of Anandan Narendiran (Roll number 2010203027)

that is carried out under my supervision. Certied further, that to the best of my

knowledge that the work reported herein does not form part of any other thesis on

the basis of which a degree or award was conferred on an earlier occasion on this or

any other candidate.

Dr. N. KUMARAVEL

Head of the Department

Department of Electronics and Communication

Engineering,

College of Engineering Guindy,

Anna University,

Chennai 600025

Dr. B. BINDU

Project Guide

Department of Electronics and Communication

Engineering,

College of Engineering Guindy,

Anna University,

Chennai 600025

i

ACKNOWLEDGEMENT

I express my gratitude to the Supreme Being for showering his benevolent bless-

ings on me to complete this project work successfully. I express my sincere thanks

to Prof. N.Kumaravel, Head of the Department, Department of Electronics and

Communication engineering, College of Engineering, Anna University, for the sup-

port and the facilities provided to me during this project.

I am grateful to Dr. B. Bindu, Department of Electronics and Communication

Engineering, College of Engineering, Anna University Chennai, for her valuable

ideas, motivation, and enthusiasm she has given me during my project work.

I would also like to thank all faculties for their suggestions and valuable ideas

during the review of this project. I am very much pleased to acknowledge my thanks

to my family and friends for their moral support which helped me to bring out this

work successfully.

Anandan Narendiran

ii

iii

ABSTRACT

Tunnel FETs are promising alternatives to conventional MOSFETs for low power

applications. Unlike MOSFETs, the subthreshold slope of Tunnel FETS is not lim-

ited to 60 mV/decade, which enables us to further scale down the supply voltage.

In this project, I present a highly accurate two dimesional model for the double gate

tunnel eld-effect transistors (DG - TFET).

The evanescent mode analysis is used to obtain an analytical model for potential,

electric eld and band-to-to band generation rate. The model is evaluated for various

device parameters such as channel length, channel thickness, oxide thickness and

high-k dielectrics. The results show excellent agreement with nite element simula-

tions performed using TCAD Sentaurus.

iv

TABLE OF CONTENTS

CHAPTER NO TITLE PAGE NO

ACKNOWLEDGEMENT ii

ABSTRACT Tamil iii

ABSTRACT English iv

TABLE OF CONTENTS v

LIST OF TABLES vii

LIST OF FIGURES vii

1 Introduction 1

1.1 Motivation 1

1.2 Organisation of Thesis 2

2 Background 3

2.1 Tunnel FETs 3

2.2 Device Simulation 4

2.2.1 Types of Simulations 4

2.3 Device Modelling 5

2.3.1 Analytical modelling of Tunnel FETs 5

3 Analytical Model 6

3.1 Channel Potential 7

3.2 Electric Field 11

3.3 Current 11

v

4 Results and Discussions 13

4.1 Physics of simulation 13

4.2 Validation of Potential and Electric Fields 14

4.3 Performance against Scaling 16

4.4 High-K Dielectrics 19

4.5 Oxide Thickness 19

4.6 Channel Thickness 24

5 Conclusion 27

REFERENCES 28

vi

LIST OF TABLES

4.1 Simulation parameters 13

LIST OF FIGURES

2.1 Double Gate Tunnel FET 3

3.1 Schematic diagram of Double Gate Tunnel FET 6

3.2 Energy Band diagram of Double Gate Tunnel FET 7

4.1 Simulation structure of Double Gate Tunnel FET 13

4.2 Channel Potential for various gate voltages. 14

4.3 Electric Field for various gate voltages. 15

4.4 Drain Current vs Gate Voltage Characteristics 16

4.5 Electric Field for various channel lengths. 17

4.6 Potential and Current Characteristics for various channel lengths. 18

4.7 Electric Field for various oxide dielectrics. 20

4.8 Potential and Current Characteristics for various oxide dielectrics. 21

4.9 Electric Field for various oxide thickness. 22

4.10 Potential and Current Characteristics for various oxide thickness. 23

4.11 Electric Field for various channel thickness. 25

4.12 Potential and Current Characteristics for various channel thickness. 26

vii

CHAPTER 1

INTRODUCTION

1.1 Motivation

The traditional MOSFET structure has been used in the Integrated circuit for a long

time, with each new generation of MOSFETs, the minimum channel length has been

shrinking continuously. The motivation behind this shrinking of device dimensions

has been an increasing interest in high speed and high packing density integrated

circuits. The scaling of MOSFETs followed the Moores Law, an empirical observa-

tion by Gordon Moore, co-founder of Intel. According to Moores law, the number

of transistors on a chip roughly doubles every two years.

As we move deep into the nanometer regime we are confronted by problems

that were once considered negligible, we are at point were the advantages of further

reduction in feature size will be offset by other effects such as short schannel effects

etc. The scaling of conventional MOSFET is reaching its limit mainly because of

its increased leakage and thus new ideas, non-classical devices and concepts are

required to overcome the shortcomings of MOSFETs.

Apart from scaling of device dimensions, we also need to scale down supply volt-

age. If the device is scaled down without corresponding reduction in supply voltage,

the electric eld in the device increases leading to adverse effects. However the sup-

ply voltage scaling faces serious limitations; while we have scaled down the device

dimensions by several orders of magnitude, the supply voltage has been scalled down

from around 5V to just around 1V.

One obvious obstruction to supply voltage reduction is noise, at lower operat-

ing voltages, the noise present in the signal becomes signicant. Another serious

limitation to supply voltage reduction is the subthreshold slope of MOSFET. The

subthreshold slope of MOSFET is theoretically limited to 60 mV/decade. It is a con-

stant and is dependent on basic properties of silicon and the MOSFETs operating

1

principle. Furthermore the OFF current of the device depends on the subthreshold

slope.

Tunnel FETs (TFET) are promising alternatives to MOSFETS for low power

applications, they promise steeper subthreshold slope and lower off current. Unlike

conventional MOSFETs the primary carrier injection mechanism in TFETs is band-

to-band tunneling. Due to this the leakage current is lower by several orders of

magnitude in TFETS, and so is their drain current. Although their drain current is

low, its low leakage current is a compelling motivation for their use in low power

applications.

TFETs are relatively new devices and focus on their research is growing steadily.

So far they are mostly studied using nite element simulations which takes very long

time to complete, and they are not much used by circuit designers for the lack of

proper models. The availability of simple analytical model will aid in the develop-

ment of circuits based on TFETs and will be useful for hand calculations.

1.2 Organisation of Thesis

Chapter 2 provides an introduction to double-gate device, and explains the basic

structure and principle of operation of TFETS. The various approaches to analytical

modeling are discussed and the different types of simulations are explained.

In Chapter 3 presents the model derivation for the Tunnel FET is presented. The

model is compared with simulation results obtained and analysed in chapter 4.

The results obtained are conclusively interpreted in Chapter 5 and the the future

scope of the project is discussed.

2

CHAPTER 2

BACKGROUND

2.1 Tunnel FETs

The gated p-i-n structure was rst proposed by Quinn et al.in 1978 and Banerjee

et al.studied the operation of three terminal silicon tunnel FETS. Fig. 2.1 shows

the structure of a double gate tunnelfet. It is operated by reverse biasing the p-i-n

junction and applying the control voltage to the gate. Here the primary injection

mechanism is band-to-band tunneling, which can be nely controlled between ON

and OFF states by the applied gate voltage. Zener was the rst to identify this tun-

neling mechanism that occurs in the high electric eld regions, which is mostly near

the junction depletion region.

Tunnel FETs are in general ambipolar device, when positive gate voltage is ap-

plied, electrons tunnel from the conduction band of source to the valance band of

channel and reach the drain be drift diffusion showing n-type behaviour. Similarly

when a negative gate voltage is applied, electrons tunnel from the valence band of

the channel to the conduction band of the drain and the generated holes reach the

source by drift diffusion exhibiting a p-type behaviour.

Gate

Gate

Source Drain p

i

n

Figure 2.1: Double Gate Tunnel FET

3

This ambipolar behaviour can however be suppressed by using asymmetrical

doping proles or hetrostructures. It is preferable to have a low band gap at source to

enable maximumcurrent in ONstate and to have high band gap at drain to mininmize

current in OFF state.

The applied gate voltage affects the position of fermi level in the channel and

hence changes the tunneling barrier. As a consequence the subthreshold slope is a

function of applied gate to source bias.

Recent experimental results promise tunnel FETs based on various materials (like

carbon, SiGe, Group III-V combination) to be succesfull candidates for sub 0.5 V

logic.

2.2 Device Simulation

The semiconductor industry is prohibitively expensive and time consuming. It is not

feasible to test new designs with actual fabrication and trail-and-error method every

time. Simulation serves as the rst test to verication of the device before heading

towards fabrication.

2.2.1 Types of Simulations

From a circuit point of view, the key parameters of interest are relation between

input(applied bias) and output(current), capacitance, time delay etc. For circuit sim-

ulations we need compact models for these to be able to calculate quickly the current

and voltages all over the circuit. They are not bothered with the actual working of

the device.

From a device point of view, we are interested in the actual working principle of

the device. Device simulation tools simulate the electrical characteristics of the de-

vice with respect to the given environmental conditions like temperature, bias strain

etc. Depending on the application, it may also be required to obtain the optical or

thermal characterisctics of the device.

4

Device simulators take into account the fundamental physics behind the materi-

als to calculate the characteristics all over the device in two or three dimensions, a

method know as nite element simulation. These simulations are accurate but tend to

extremely slow and are hence unsuitable for circuit simulations. Modern semicon-

ductor device simulators are capable including quantum mechanical effects in their

simulations.

2.3 Device Modelling

To incorporate device behaviour in circuit simulators, it is essential to have com-

pact models. Compact models are specied using analytical models are determined

emperically from curve tting.

2.3.1 Analytical modelling of Tunnel FETs

Tunnel FETa are relatively new in the industry and so far their analysis was largly

based on nite element simulation. Verhulst et al.proposed a one dimensional so-

lution to poissons eqquation along the tunneling path. The variational approach ap-

plied by Sern et al.have been used extensively in MOSFETs. These models however

cannot provide simple models for drain current. Brandon et al.proposed a two dime-

sional analytical model for the potential including the source and drain depletion

regions. Their approach uses the parabolic method to model the potential.

The evanescent mode analysis is a powerfull method which accurately models

the channel potential. This method was applied to 3T and 4T double gate MOSFETs

by Aritara et al.but is not applied to TFETs. In this project we use this method to

derive an analytical model for tunnel FETs.

5

CHAPTER 3

ANALYTICAL MODEL

The device structure considered in our analysis are shown in Fig. 3.1. The inuence

of source and drain depletion region on the channel is taken into account by adjusting

the channel starting and ending positions. The source is heavily doped with p-type

material with a doping concentration of N

S

, the intrinsic region is slightly p-type with

a doping concentration of N

C

and the n-type drain has a doping concentration of N

D

.

The channel length is L

C

and channel has thickness of t

si

.The starting and ending

positions of the channel are x

1

and x

2

respectively. The oxide thickness is specied

by t

ox

. The co-ordinate system starts at the source channel junction and the vertical

center of silicon.

The gate contact used is a metal with workfunction of 4.5 and the source and

drain are having ohmic contacts.

Gate

Gate

Source Drain

p

i

n

x

1

x

2

L

dd

L

ds

t

ox1

t

ox2

t

si

x

y

Figure 3.1: Schematic diagram of Double Gate Tunnel FET

6

V

bis

V

bid

C

P

+

N

+

P

-

E

c

E

i

E

f

E

v

E

c

E

i

E

f

E

v

Figure 3.2: Energy Band diagram of Double Gate Tunnel FET

3.1 Channel Potential

Figure Fig. 3.2 shows the energy band diagram for tunnel FET, with the all the

terminals left oating.

The position of fermi level with respect to the intrisic level is given at equillib-

rium in source, channel and drain regions are

S

,

C

,

D

respectively. they are given

as

S

=KT ln

_

N

S

n

i

_

(3.1)

C

=KT ln

_

N

C

n

i

_

(3.2)

D

= KT ln

_

N

D

n

i

_

(3.3)

On application of external voltage, the potential in the deep in the source and

drain can be written as

S

=

S

(3.4)

D

=

D

+V

DS

(3.5)

7

and the potential in the channel region is modelled as

C

(x, y) =

C

+(x, y) (3.6)

Here (x, y) is the 2D solution to the poissons equation in the channel region,

which is obtained using evanescent mode analysis[s10]. In this method the channel

potential is seperated into two parts.

(x, y) =

L

(y) +(x, y) (3.7)

where

L

(y) is the long channel solution to the channel potential which satises the

1D poissons equation along the vertical direction as.

2

y

L

(y) =

qN

C

si

(3.8)

The solution for

L

(y) can be written as

L

(y) =

qN

C

si

_

y

2

_

tsi

2

_

2

_

+

s2

s2

t

si

+

s1

+

s2

2

(3.9)

where

s1

and

s2

are the potentials at the front and back silicon surfaces, respec-

tively. These potentials satisfy the following equations[sirpaper]

s1

=

(1+r

2

)V

GFS

+r

1

V

GBS

1+r

1

+r

2

qN

C

t

si

2(1+r

1

+r

2

)

_

1+r

2

C

ox1

+

r

1

C

ox2

_

(3.10)

s2

=

r

2

V

GFS

+(1+r

1

)V

GBS

1+r

1

+r

2

qN

C

t

si

2(1+r

1

+r

2

)

_

r

2

C

ox1

+

1+r

1

C

ox2

_

(3.11)

where V

GFS

= V

GF

V

FBF

, V

GBS

= V

GB

V

FBB

, C

ox1

=

ox1

/t

ox1

, C

ox1

=

ox2

/t

ox2

,

r

1

=C

si

/C

ox1

, r

2

=C

si

/C

ox2

and C

si

=

si

/t

tsi

. V

FBF

and V

FBF

are the atband voltage

at the front and back interfaces.

8

Now

2D

(x, y) accounts for the 2D variation of potential along the channel by

including the source and drain bias conditions and satises the 2D laplace equation

given by

2D

x

2

+

2

2D

y

2

= 0 (3.12)

The general solution (3.12) can be expressed in Fourier series expansion as

2D

(x, y =

n=0

cos(

ny

n

) +A

n

sin(

ny

n

)

sinh(

L

n

)

_

U sinh

x x

1

n

+V sinh

x

2

x

n

_

The higher order terms decay fast and we can approximate (??) by ignoring the

higher order modes as

2D

(x, y) =

cos(

y

)

sinh(

L

)

_

U sinh

x x

1

+V sinh

x

2

x

_

(3.13)

where L =x

2

x

1

is the effective channel length, x

1

and x

2

are the starting and ending

positions of the channel which are obtained given by

x1 =K

S

L

ds

(3.14)

x2 = L

C

+K

D

L

dd

(3.15)

where L

ds

denotes the penetration of depletion region into the source region consider-

ing the source and channel alone. Similarly L

dd

denotes the penetration of depletion

region into the drain region considering the drain and channel alone. They are given

as

L

dd

=

2

si

q

N

C

N

D

1

N

C

+N

D

[V

D

+v

bid

L

(0)] (3.16)

L

ds

=

2

si

q

N

C

N

S

1

N

C

+N

S

[v

bis

L

(0)] (3.17)

9

However due to large doping concentrations employed in tunnel FETs and the

short channel lengths used, the depletion regions usually merge and inuence each

other. The inuence of source and drain in each others depletion region can be

accounted for by scaling the obtained depletion lengths by a constant factor. K

S

and K

D

are the scaling factors used at source and drain depletion regions, and are

obtained from curve tting with simulation results as K

S

= 7 and K

D

= 2.2

To obtain the values of A,U,V and we use the following boundary condi-

tions[sirpaper] at the front and back surfaces and also at the source and drain junc-

tions.

2D

_

x,

t

si

2

_

= r

1

t

si

2D

y

y=t

si

/2

(3.18)

2D

_

x,

t

si

2

_

=r

2

t

si

2D

y

y=t

si

/2

(3.19)

2D

(x

1

, y) =V

bis

L

(y) (3.20)

2D

(x

2

, y) =V

bid

+V

DS

L

(y) (3.21)

where V

bis

and V

bid

are the built in potential at the source and drain junctions respec-

tively. From boundary conditions (3.18) and (3.19) we get

A =

12r

1

tan

tan +2r

1

=

12r

1

tan

tan +2r

1

(3.22)

where = t

si

/2. The solution of (3.22) gives us the value of the decay constant

and A. Applying boundary conditions (3.20) and (3.21) at y = 0 we get

V =V

bis

L

(0) (3.23)

U =V

bid

+V

DS

L

(0) (3.24)

Substitutng the values of A,U,V and in (3.13) we can obtain

2D

in terms of

the the applied voltage and material parameters. Using equations (3.6), (3.7), (3.9)

and (3.13) we can determine the potential at any point inside the channel.

10

For the special case of symmetrical 3-T device, A = 0, r

1

= r

2

= r,

s1

=

s1

=

s

,V

GFS

=V

GBS

=V

GS

,V

FBF

=V

FBB

,C

ox1

=C

ox2

=C

ox

and equations (3.9), (3.10),

(3.13) and (3.22) reduce to,

L

(y) =

s

+

qN

C

2

si

_

y

2

_

t

si

2

_

2

_

(3.25)

s

=V

GS

qN

C

t

si

2C

ox

(3.26)

2r tan = 1 (3.27)

2D

(x, y) =

cos(

y

)

sinh(

L

)

_

U sinh

x x

1

+V sinh

x

2

x

_

(3.28)

3.2 Electric Field

The Electric eld in the channel region can be obtained by differentiating the channel

potential.

E

x

(x, y) =

x

(x, y) (3.29)

E

x

(x, y) =

cos(

y

)

sinh(

L

)

_

U cosh

x x

1

V cosh

x

2

x

_

(3.30)

E

y

(x, y) =

x

(x, y) (3.31)

E

y

(x, y) =

qN

A

y

si

sin(

y

)

sinh(

L

)

_

U sinh

x x

1

+V sinh

x

2

x

_

(3.32)

3.3 Current

The primary injection mechanism in TFETs is the band-to-band tunneling. The cur-

rent can be obtained by integrating the band-to-band generation over the channel

area.

I = q

__

Channel

G

btb

dxdy (3.33)

11

In the model used in simulation, the band-to-band generation rate is given by

G

btb

(x, y) = AE(x, y)

2

exp

_

B

E(x, y)

_

(3.34)

where (A = 3.110

21

cm

1

s

1

V

1

) and (B = 22.610

6

Vcm

2

) are the parame-

ters used in simulation and E(x, y) is the magnitude of electric eld and is given as

E(x, y) =

_

E

x

(x, y)

2

+E

y

(x, y)

2

(3.35)

where E

x

and E

y

can be obtained by differentiating (3.6) with respect to x and y

respectively.

The current is then obtained by numerical integration of (3.34). Although we

neglected mobile charges in our model formulation, the current can be obtained with

this method as the band-to-band generation depends only on the electric eld which

is primarily determined by the xed charges.

12

CHAPTER 4

RESULTS AND DISCUSSIONS

The performance of the model is evaluated by comparison with nite element sim-

ulations. The simulator used is TCAD Sentaurus device simulator and the structure

used for simulation is shown in Fig. 4.1. The parameters of the device are listed in

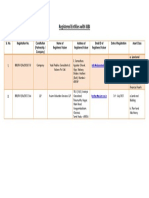

Table 4.1.

Region

Dopant Concentration Length

Source Boron 1e20 30 nm

Channel Boron 1e17 50 nm

Drain Phosporus 5e18 30nm

Oxide Thickness 3 nm

Table 4.1: Simulation parameters

4.1 Physics of simulation

The E 2 band-to-band tunneling provied by the TCAD sentaurus device simulator

was used during simulations. The MLDA multivally band gap model was selected

and the Jain-Roulstan bandgap narrowing model was enabled. In order to improve

the accuracy of the simulations, Fermi statistics were used instead of Boltzman statis-

tics. High Field Saturation was enabled for both holes and electrons. The source and

Figure 4.1: Simulation structure of Double Gate Tunnel FET

13

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

0 10 20 30 40 50

P

o

t

e

n

t

i

a

l

(

V

)

Position along channel (nm)

Vg = 0 V

Vg = 0.2 V

Vg = 0.4 V

Figure 4.2: Comparison of channel potential for various gate voltages between

model(points) and simulation(lines).

drain have ohmic contacts where as the gate is a metal with a workfunction of 4.5

eV.

4.2 Validation of Potential and Electric Fields

The model was tested for the device described in Table 4.1. The gate voltage was

varied from0 Vto 0.6 Vin steps of 0.2 Vand the potential along the channel is shown

in Fig. 4.2 for each step. The comparison of horizontal and vertical components of

electric led between the model and simulation are shown in Fig. 4.3a and Fig. 4.3b

respectively.

As we can see the model is in good agreement with the simulation results for

various gate voltages. There is small mismatch at the drain and source ends as their

inuence on each other have only been approximated by scaling the depletion region

lengths with a constant.

14

0

0.2

0.4

0.6

0.8

1

1.2

0 10 20 30 40 50

E

x

(

M

V

/

c

m

)

Position along channel (nm)

Vg = 0 V

Vg = 0.2 V

Vg = 0.4 V

(a) Horizontal Component

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

0 10 20 30 40 50

E

y

(

M

V

/

c

m

)

Position along channel (nm)

Vg = 0 V

Vg = 0.2 V

Vg = 0.4 V

(b) Vertical Component

Figure 4.3: Comparison of Electric Field for various gate voltages between

model(points) and simulation(lines).

15

10

-14

10

-13

10

-12

10

-11

10

-10

10

-9

10

-8

10

-7

10

-6

0 0.2 0.4 0.6 0.8 1

D

r

a

i

n

C

u

r

r

e

n

t

(

A

)

Gate Voltage (V)

10 nm

Figure 4.4: Drain Current vs Gate Voltage Characteristics bewtween model(points)

and simulation(lines)

For this device, the Drain Current vs Gate Voltage Charactersitics was obtained

and compared in Fig. 4.4 and the model performs well and gives close results despite.

It is important to accurately predict the channel potential and electric eld at low gate

voltages as they determie the subthreshold slope and OFF current.

4.3 Performance against Scaling

To be able to compete with CMOS technology, TFETS have to perform well at

nanoscale dimesions. The OFF current is expected to be limited by the reverse

leakage current of source-channel PN junction diode. The model was tested three

different channel lengths which are 25 nm (short channel), 50 nm and 75 nm while

maintaining the remaining parameters at the values listed in Table 4.1

The comparison of horizontal and vertical components of electric led between

the model and simulation are shown in Fig. 4.5a and Fig. 4.5b respectively. We can

16

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1

0 10 20 30 40 50 60 70

E

x

(

M

V

/

c

m

)

Position along channel (nm)

25 nm

50 nm

75 nm

(a) Horizontal Component

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

0 10 20 30 40 50 60 70

E

y

(

M

V

/

c

m

)

Position along channel (nm)

25 nm

50 nm

75 nm

(b) Vertical Component

Figure 4.5: Comparison of Electric Field for various channel lengths between

model(points) and simulation(lines).

17

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

0 10 20 30 40 50 60 70

P

o

t

e

n

t

i

a

l

(

V

)

Position along channel (nm)

25 nm

50 nm

75 nm

(a) Potential

10

-14

10

-13

10

-12

10

-11

10

-10

10

-9

10

-8

0 0.1 0.2 0.3 0.4 0.5

D

r

a

i

n

C

u

r

r

e

n

t

(

A

)

Gate Voltage (V)

25 nm

50 nm

75 nm

(b) Drain Current vs Gate Voltage Characteristics

Figure 4.6: Potential and Current Characteristics for various channel lengths between

model(points) and simulation(lines).

18

see the small mismatch at the depletion regions , however they are independent of

the channel length.

Fig. 4.6a shows the potential plot for the three different channel and Fig. 4.6b

shows their respective current characteristics. From the current characteristics we

can see that the model predicts the current close to the simulation results. It is also

observed that the error between the simulation and model is almost independent of

channel lengths.

4.4 High-K Dielectrics

The model was tested different oxide dielectrics which are Silicon Dioxide(SiO

2

)

and Silicon Nitride(Si

3

N

4

) while maintaining the remaining parameters at the values

listed in Table 4.1

The comparison of horizontal and vertical components of electric led between

the model and simulation are shown in Fig. 4.7a and Fig. 4.7b respectively. Although

there is a small mismatch at the depletion regions, they are different for each material.

This is an indicator that the possible source of error is the approach in determining

the depletion region length.

However as seen from the potential plots in Fig. 4.8a and the current character-

istics shown in Fig. 4.8b this difference is negligible. As we can see the current is

higher for high-K dielectric and the model preforms well with respect to different

oxide materials.

4.5 Oxide Thickness

The model was tested different oxide thickness which are 2 nm, 3 nm and 4 nm while

maintaining the remaining parameters at the values listed in Table 4.1

The comparison of horizontal and vertical components of electric led between

the model and simulation are shown in Fig. 4.9a and Fig. 4.9b respectively. It can

19

0

0.2

0.4

0.6

0.8

1

1.2

0 10 20 30 40 50

E

x

(

M

V

/

c

m

)

Position along channel (nm)

SiO

2

Si

3

N

4

(a) Horizontal Component

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

1.2

0 10 20 30 40 50

E

y

(

M

V

/

c

m

)

Position along channel (nm)

SiO

2

Si

3

N

4

(b) Vertical Component

Figure 4.7: Comparison of Electric Field for various oxide dielectrics between

model(points) and simulation(lines).

20

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

0 10 20 30 40 50

P

o

t

e

n

t

i

a

l

(

V

)

Position along channel (nm)

SiO

2

Si

3

N

4

(a) Potential

10

-14

10

-13

10

-12

10

-11

10

-10

10

-9

10

-8

10

-7

10

-6

10

-5

10

-4

0 0.2 0.4 0.6 0.8 1

D

r

a

i

n

C

u

r

r

e

n

t

(

A

)

Gate Voltage (V)

SiO

2

Si

3

N

4

HfO

2

(b) Drain Current vs Gate Voltage Characteristics

Figure 4.8: Potential and Current Characteristics for various oxide dielectrics be-

tween model(points) and simulation(lines).

21

0

0.2

0.4

0.6

0.8

1

1.2

0 10 20 30 40 50

E

x

(

M

V

/

c

m

)

Position along channel (nm)

2 nm

3 nm

4 nm

(a) Horizontal Component

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

0 10 20 30 40 50

E

y

(

M

V

/

c

m

)

Position along channel (nm)

2 nm

3 nm

4 nm

(b) Vertical Component

Figure 4.9: Comparison of Electric Field for various oxide thickness between

model(points) and simulation(lines).

22

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

0 10 20 30 40 50

P

o

t

e

n

t

i

a

l

(

V

)

Position along channel (nm)

2 nm

3 nm

4 nm

(a) Potential

10

-15

10

-14

10

-13

10

-12

10

-11

10

-10

10

-9

10

-8

10

-7

10

-6

0 0.2 0.4 0.6 0.8 1

D

r

a

i

n

C

u

r

r

e

n

t

(

A

)

Gate Voltage (V)

2 nm

3 nm

4 nm

(b) Drain Current vs Gate Voltage Characteristics

Figure 4.10: Potential and Current Characteristics for various oxide thickness be-

tween model(points) and simulation(lines).

23

be clearly seen from these plots that mismatch varies with oxide thickness. This

suggests that error may lie in determination of depletion region width.

However as seen from the potential plots in Fig. 4.10a and the current character-

istics shown in Fig. 4.10b this difference is negligible. As we can see the current is

higher for lower oxide thickness and the model preforms well with respect to differ-

ent oxide thickness.

4.6 Channel Thickness

The model was tested different channel thickness which are 10 nm and 15 nm while

maintaining the remaining parameters at the values listed in Table 4.1

The comparison of horizontal and vertical components of electric led between

the model and simulation are shown in Fig. 4.11a and Fig. 4.11b respectively. It is

clear from the plots that the error is more in horziontal component of electric eld

when compared to electric led.

However as seen from the potential plots in Fig. 4.12a and the current character-

istics shown in Fig. 4.12b this difference is negligible. Another suggestion that the

error lies in the approach for horizontal boundary conditions.

24

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1

0 10 20 30 40 50

E

x

(

M

V

/

c

m

)

Position along channel (nm)

10 nm

15 nm

(a) Horizontal Component

-0.6

-0.4

-0.2

0

0.2

0.4

0.6

0.8

0 10 20 30 40 50

E

y

(

M

V

/

c

m

)

Position along channel (nm)

10 nm

15 nm

(b) Vertical Component

Figure 4.11: Comparison of Electric Field for various channel thickness between

model(points) and simulation(lines).

25

-0.4

-0.2

0

0.2

0.4

0.6

0.8

1

0 10 20 30 40 50

P

o

t

e

n

t

i

a

l

(

V

)

Position along channel (nm)

10 nm

15 nm

(a) Potential

10

-15

10

-14

10

-13

10

-12

10

-11

10

-10

10

-9

0 0.1 0.2 0.3 0.4 0.5

D

r

a

i

n

C

u

r

r

e

n

t

(

A

)

Gate Voltage (V)

10 nm

15 nm

(b) Drain Current vs Gate Voltage Characteristics

Figure 4.12: Potential and Current Characteristics for various channel thickness be-

tween model(points) and simulation(lines).

26

CHAPTER 5

CONCLUSION

In this project, an analytical model based on evanescent model analysis is developed

for Double Gate Tunnel FET which can be incorporated in circuit simulators. The

model predicts the two dimensional variation of potential and electric eld within

the channel region. From these the current is obtained using Kanes model and the

results are in good agreement with simulations.

The model also includes an approximate correction to the depletion region widths

to account for inuence of source and drain on each others depletion regions. Al-

though the model has an excellent match in the channel center, there is minor mis-

match between the model and the simulation near the junction. It can also be seen

that the error in horizontal component is more compared to the error in vertical com-

ponent of eld near the junctions.

These ndings suggest that the error may be due to the approach used to handle

the horizontal boundary conditions. It must also be kept in mind that the current is

obtained through numerical calculation rather than from a straight forward analytical

expression. This can be one of the possible sources of error apart from the scaling

factors of the depletion region width.

Further the dependence on the mismatch with the dielectric and oxide thickness

suggest the inuence of gate on the horizontal boundary conditions. The above ob-

servations suggests that in order to get more accurate results, we need to divide the

device into three seperate regions and explicitly obtain the boundary conditions for

the three regions seperately whic is a hughly complex task. Further we need to solve

for the poissons equation expliciltly in all these regions to get exact results.

The model presented in this project performs well without these complexities and

is able to give reasonably good results. Further it has lower computational require-

ments and can give fast results.

27

REFERENCES

1. Aritra Dey, Anjan Chakravorty, Nandita DasGupta, and Amitava DasGupta,

(2008) Analytical Model of Subthreshold Current and Slope for Asymmetric 4-

T and 3-T Double-Gate MOSFETs, IEEE Transactions on Electron Devices,

vol. 55, no. 12, pp: 3442-3449

2. Banerjee, S., Richardson W., Coleman J. and Chatterjee A., (1987) A new

three-terminal tunnel device, IEEE Electron Device Letter. vol. 8, pp: 347349

3. Bardon M. G, Herc P. Neves, Robert Puers and Chris Van Hoof, (2010) Pseudo-

Two-Dimensional Model for Double-Gate Tunnel FETs Considering the Junc-

tions Depletion Regions IEEE Transsaction on Electron Devices, vol. 57, no.

4, pp: 827-834

4. Chen Shen, Sern-Long Ong, Chun-Huat Heng, Samudra, G., Yee-Chia Yeo,

(2008) A variational approach to the two-dimensional nonlinear Poissons

equation for the modeling of tunneling transistors, IEEE Electron Device Let-

ter, vol. 29, no. 11, pp: 12521255.

5. Rusu, A., Salvatore, G. A., Jimenez, D. and Ionescu A. M., (2010) Metal-

ferroelectric-meta-oxide-semiconductor eld effect transistor with sub-60mV/decade

subthreshold swing and internal voltage amplication, IEEE International

Electron Devices Meet. pp: 16.3.116.3.4

6. Quinn, J., Kawamoto, G. and McCombe, B. (1978), Subband spectroscopy

by surface channel tunneling. Surf. Sci. vol. 73, pp: 190196

7. A. S. Verhulst, W. G. Vandenberghe, K. Maex, and G. Groeseneken (2008),

Boosting the on-current of a n-channel nanowire tunnel eld-effect transistor

by source material optimization, Journal of Applied Physics, vol. 104, no. 6,

pp: 064514 (10 pages)

28

You might also like

- Vdoc - Pub Finfet Devices For Vlsi Circuits and SystemsNo ratings yetVdoc - Pub Finfet Devices For Vlsi Circuits and Systems339 pages

- Advancement and Challenges in MOSFET ScalingNo ratings yetAdvancement and Challenges in MOSFET Scaling17 pages

- It Is Quite Another Electricity: Transmitting by One Wire and Without GroundingFrom EverandIt Is Quite Another Electricity: Transmitting by One Wire and Without Grounding4.5/5 (2)

- Dokumen.pub Advanced Ultra Low Power Semiconductor Devices Design and Applications 9781394166411No ratings yetDokumen.pub Advanced Ultra Low Power Semiconductor Devices Design and Applications 9781394166411313 pages

- Sub-10nm Transistors For Low Power Computing - Tunnel FETs and Neg - 2No ratings yetSub-10nm Transistors For Low Power Computing - Tunnel FETs and Neg - 2137 pages

- Analytical Modeling of Tunneling Field Effect Transistor (TFET)No ratings yetAnalytical Modeling of Tunneling Field Effect Transistor (TFET)22 pages

- A Technical Seminar Report 19q91a0429 Ece ANo ratings yetA Technical Seminar Report 19q91a0429 Ece A32 pages

- Design and Simulation of Double Gate Fets Using Atlas: National Institute of Technology RourkelaNo ratings yetDesign and Simulation of Double Gate Fets Using Atlas: National Institute of Technology Rourkela33 pages

- Vertical_Tunnel_Field_Effect_Transistors_VTFETs_A_Potential_Candidate_for_Low_Power_Applications (3)No ratings yetVertical_Tunnel_Field_Effect_Transistors_VTFETs_A_Potential_Candidate_for_Low_Power_Applications (3)7 pages

- (Ebook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors Ebook All Chapters PDF100% (5)(Ebook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors Ebook All Chapters PDF41 pages

- Double Gate All Around Tunnel Field Effect Transistor DesigNo ratings yetDouble Gate All Around Tunnel Field Effect Transistor Desig6 pages

- An SOI N-P-N Double Gate TFET For Low Power Applications: Abstract - This Article Proposes A Tunnel Field EffectNo ratings yetAn SOI N-P-N Double Gate TFET For Low Power Applications: Abstract - This Article Proposes A Tunnel Field Effect3 pages

- Download full (eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors ebook all chapters100% (6)Download full (eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors ebook all chapters56 pages

- (eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistorsinstant download100% (4)(eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistorsinstant download49 pages

- 483(eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors pdf download100% (1)483(eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors pdf download57 pages

- Enhancing Frequency Performance of Underlap Tunnel Field-Effect Transistor For Analog/RF ApplicationsNo ratings yetEnhancing Frequency Performance of Underlap Tunnel Field-Effect Transistor For Analog/RF Applications7 pages

- "Tunnel Field Effect Transistors (TFET) ": Prepared By:-Group 1050% (2)"Tunnel Field Effect Transistors (TFET) ": Prepared By:-Group 1024 pages

- (eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors pdf downloadNo ratings yet(eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors pdf download51 pages

- Tunneling Field Effect Transistors: Design, Modeling and Applications 1st Edition T. S. Arun Samuel downloadNo ratings yetTunneling Field Effect Transistors: Design, Modeling and Applications 1st Edition T. S. Arun Samuel download38 pages

- Signal-Processing Application Based on FerroelectricNo ratings yetSignal-Processing Application Based on Ferroelectric5 pages

- (eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors all chapter instant download100% (18)(eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors all chapter instant download35 pages

- Two-Stage Op-Amp and Integrator Realisation Through Gaasp/Algasb Nanowire Cp-TfetNo ratings yetTwo-Stage Op-Amp and Integrator Realisation Through Gaasp/Algasb Nanowire Cp-Tfet6 pages

- Challenges and Solutions of the TFET Circuit DesignNo ratings yetChallenges and Solutions of the TFET Circuit Design14 pages

- Medical Science: Review of Contemporary Research in Finfet TechnologyNo ratings yetMedical Science: Review of Contemporary Research in Finfet Technology3 pages

- Electronics Expert Portfolio by SlidesgoNo ratings yetElectronics Expert Portfolio by Slidesgo8 pages

- Generalized Scaling Theory and Its Application To A Micrometer MOSFET DesignNo ratings yetGeneralized Scaling Theory and Its Application To A Micrometer MOSFET Design11 pages

- Power Line Communications: Principles, Standards and Applications from Multimedia to Smart GridFrom EverandPower Line Communications: Principles, Standards and Applications from Multimedia to Smart GridLutz LampeNo ratings yet

- (Application Format For Empanelment of Valuers With Banks) (To Be Obtained in The Letterhead of The Valuer)No ratings yet(Application Format For Empanelment of Valuers With Banks) (To Be Obtained in The Letterhead of The Valuer)5 pages

- 2.5.H-Compilation and Execution of A C ProgramNo ratings yet2.5.H-Compilation and Execution of A C Program2 pages

- 3.2.G-Employee Payroll Program (Payroll.c)No ratings yet3.2.G-Employee Payroll Program (Payroll.c)3 pages

- Cryogenic Characterization of 28 NM Bulk CMOS Technology For Quantum ComputingNo ratings yetCryogenic Characterization of 28 NM Bulk CMOS Technology For Quantum Computing5 pages

- Optimization of CMOS at Deep Cryogenic TemperaturesNo ratings yetOptimization of CMOS at Deep Cryogenic Temperatures56 pages

- Challenges of MOS Analog Circuit Simulation With SPICENo ratings yetChallenges of MOS Analog Circuit Simulation With SPICE5 pages

- Design Of A Low Drop-Out Voltage Regulator Using 0.13 Μm Cmos TechnologyNo ratings yetDesign Of A Low Drop-Out Voltage Regulator Using 0.13 Μm Cmos Technology17 pages

- Information Systems Design and Intelligent Applications Volume 1 PDF50% (2)Information Systems Design and Intelligent Applications Volume 1 PDF735 pages

- Field-Effect Transistors: Microelectronic Circuit Design, Richard C. Jaeger, Travis N. BlalockNo ratings yetField-Effect Transistors: Microelectronic Circuit Design, Richard C. Jaeger, Travis N. Blalock38 pages

- A Dynamic-Adjusting Threshold-Voltage Scheme For Finfets Low Power DesignsNo ratings yetA Dynamic-Adjusting Threshold-Voltage Scheme For Finfets Low Power Designs4 pages

- A Study On Multi Material Gate All Around SOI MOSFETNo ratings yetA Study On Multi Material Gate All Around SOI MOSFET5 pages

- Vdoc - Pub Finfet Devices For Vlsi Circuits and SystemsVdoc - Pub Finfet Devices For Vlsi Circuits and Systems

- It Is Quite Another Electricity: Transmitting by One Wire and Without GroundingFrom EverandIt Is Quite Another Electricity: Transmitting by One Wire and Without Grounding

- Dokumen.pub Advanced Ultra Low Power Semiconductor Devices Design and Applications 9781394166411Dokumen.pub Advanced Ultra Low Power Semiconductor Devices Design and Applications 9781394166411

- Sub-10nm Transistors For Low Power Computing - Tunnel FETs and Neg - 2Sub-10nm Transistors For Low Power Computing - Tunnel FETs and Neg - 2

- Analytical Modeling of Tunneling Field Effect Transistor (TFET)Analytical Modeling of Tunneling Field Effect Transistor (TFET)

- Design and Simulation of Double Gate Fets Using Atlas: National Institute of Technology RourkelaDesign and Simulation of Double Gate Fets Using Atlas: National Institute of Technology Rourkela

- Vertical_Tunnel_Field_Effect_Transistors_VTFETs_A_Potential_Candidate_for_Low_Power_Applications (3)Vertical_Tunnel_Field_Effect_Transistors_VTFETs_A_Potential_Candidate_for_Low_Power_Applications (3)

- (Ebook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors Ebook All Chapters PDF(Ebook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors Ebook All Chapters PDF

- Double Gate All Around Tunnel Field Effect Transistor DesigDouble Gate All Around Tunnel Field Effect Transistor Desig

- An SOI N-P-N Double Gate TFET For Low Power Applications: Abstract - This Article Proposes A Tunnel Field EffectAn SOI N-P-N Double Gate TFET For Low Power Applications: Abstract - This Article Proposes A Tunnel Field Effect

- Download full (eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors ebook all chaptersDownload full (eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors ebook all chapters

- (eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistorsinstant download(eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistorsinstant download

- 483(eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors pdf download483(eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors pdf download

- Enhancing Frequency Performance of Underlap Tunnel Field-Effect Transistor For Analog/RF ApplicationsEnhancing Frequency Performance of Underlap Tunnel Field-Effect Transistor For Analog/RF Applications

- "Tunnel Field Effect Transistors (TFET) ": Prepared By:-Group 10"Tunnel Field Effect Transistors (TFET) ": Prepared By:-Group 10

- (eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors pdf download(eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors pdf download

- Tunneling Field Effect Transistors: Design, Modeling and Applications 1st Edition T. S. Arun Samuel downloadTunneling Field Effect Transistors: Design, Modeling and Applications 1st Edition T. S. Arun Samuel download

- Signal-Processing Application Based on FerroelectricSignal-Processing Application Based on Ferroelectric

- (eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors all chapter instant download(eBook PDF) Modeling Nanowire and Double-Gate Junctionless Field-Effect Transistors all chapter instant download

- Two-Stage Op-Amp and Integrator Realisation Through Gaasp/Algasb Nanowire Cp-TfetTwo-Stage Op-Amp and Integrator Realisation Through Gaasp/Algasb Nanowire Cp-Tfet

- Challenges and Solutions of the TFET Circuit DesignChallenges and Solutions of the TFET Circuit Design

- Medical Science: Review of Contemporary Research in Finfet TechnologyMedical Science: Review of Contemporary Research in Finfet Technology

- Generalized Scaling Theory and Its Application To A Micrometer MOSFET DesignGeneralized Scaling Theory and Its Application To A Micrometer MOSFET Design

- Power Line Communications: Principles, Standards and Applications from Multimedia to Smart GridFrom EverandPower Line Communications: Principles, Standards and Applications from Multimedia to Smart Grid

- (Application Format For Empanelment of Valuers With Banks) (To Be Obtained in The Letterhead of The Valuer)(Application Format For Empanelment of Valuers With Banks) (To Be Obtained in The Letterhead of The Valuer)

- Cryogenic Characterization of 28 NM Bulk CMOS Technology For Quantum ComputingCryogenic Characterization of 28 NM Bulk CMOS Technology For Quantum Computing

- Optimization of CMOS at Deep Cryogenic TemperaturesOptimization of CMOS at Deep Cryogenic Temperatures

- Challenges of MOS Analog Circuit Simulation With SPICEChallenges of MOS Analog Circuit Simulation With SPICE

- Design Of A Low Drop-Out Voltage Regulator Using 0.13 Μm Cmos TechnologyDesign Of A Low Drop-Out Voltage Regulator Using 0.13 Μm Cmos Technology

- Information Systems Design and Intelligent Applications Volume 1 PDFInformation Systems Design and Intelligent Applications Volume 1 PDF

- Field-Effect Transistors: Microelectronic Circuit Design, Richard C. Jaeger, Travis N. BlalockField-Effect Transistors: Microelectronic Circuit Design, Richard C. Jaeger, Travis N. Blalock

- A Dynamic-Adjusting Threshold-Voltage Scheme For Finfets Low Power DesignsA Dynamic-Adjusting Threshold-Voltage Scheme For Finfets Low Power Designs

- A Study On Multi Material Gate All Around SOI MOSFETA Study On Multi Material Gate All Around SOI MOSFET