FAN6755W

FAN6755W

Uploaded by

Andres AlegriaCopyright:

Available Formats

FAN6755W

FAN6755W

Uploaded by

Andres AlegriaCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

FAN6755W

FAN6755W

Uploaded by

Andres AlegriaCopyright:

Available Formats

May 2013

2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6755W / FAN6755UW Rev. 1.0.7

F

A

N

6

7

5

5

W

/

F

A

N

6

7

5

5

U

W

m

W

S

a

v

e

r

C

o

n

t

r

o

l

l

e

r

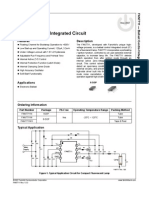

FAN6755W / FAN6755UW

mWSaver

PWM Controller

Features

mWSaver

Technology Provides Industrys Best-

in-Class Standby Power

- <100 mW at 25-mW Load for LCDM Adaptor

- Internal High-Voltage JFET Startup

- Low Operating Current: Under 2 mA

- Adaptively Decrease PWM Frequency to

23 kHz at Light-Load Condition for Better

Efficiency

- Feedback Impedance Switching During

Minimum Load or No Load

Proprietary Asynchronous Frequency Hopping

Technique that Reduces EMI

Fixed PWM Frequency: 65 kHz (FAN6755W),

130 kHz (FAN6755UW)

Internal Leading-Edge Blanking

Built-in Synchronized Slope Compensation

Auto-Restart Protection: Feedback Open-Loop

Protection (OLP), VDD Over-Voltage Protection

(OVP), Over-Temperature Protection (OTP), and

Line Over-Voltage Protection

Soft Gate Drive with Clamped Output Voltage: 18 V

VDD Under-Voltage Lockout (UVLO)

Programmable Constant Power Limit

(Full AC Input Range)

Internal OTP Sensor with Hysteresis

Build-in 5-ms Soft-Start Function

Input Voltage Sensing (VIN Pin) for Brown-In/Out

Protection with Hysteresis and Line Over-Voltage

Protection

Applications

General-purpose switched-mode power supplies and

flyback power converters, including:

LCD Monitor Power Supply

Open-Frame SMPS

Description

This highly integrated PWM controller provides several

features to enhance the performance of flyback

converters.

To minimize standby power consumption, a proprietary

adaptive green-mode function reduces switching

frequency at light-load condition. To avoid acoustic-

noise problems, the minimum PWM frequency is set

above 23 kHz. This green-mode function enables the

power supply to meet international power conservation

requirements, such as Energy Star

. With the internal

high-voltage startup circuitry, the power loss caused by

bleeding resistors is also eliminated. To further reduce

power consumption, FAN6755W/UW uses the BiCMOS

process, which allows an operating current of only

2 mA. The standby power consumption can be under

100 mW for most of LCD monitor power supply designs.

FAN6755W/UW integrates a frequency-hopping

function that reduces EMI emission of a power supply

with minimum line filters. The built-in synchronized

slope compensation achieves a stable peak-current-

mode control and improves noise immunity. The

proprietary line compensation ensures constant output

power limit over a wide AC input voltage range from

90 VAC to 264 VAC.

FAN6755W/UW provides many protection functions.

The internal feedback open-loop protection circuit

protects the power supply from open-feedback-loop

condition or output-short condition. It also has line

under-voltage protection (brownout protection) and

over-voltage protection using an input voltage sensing

pin (VIN).

FAN6755W/UW is available in a 7-pin SOP package.

ENERGY STAR is a registered trademark of the U.S. Department of Energy and the U.S. Environmental Protection Agency.

2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6755W / FAN6755UW Rev. 1.0.7 2

F

A

N

6

7

5

5

W

/

F

A

N

6

7

5

5

U

W

m

W

S

a

v

e

r

C

o

n

t

r

o

l

l

e

r

Ordering Information

Part Number

Operating

Temperature

Range

Package

PWM

Frequency

Packing

Method

FAN6755WMY -40 to +105C

7-Lead, Small Outline Integrated Circuit

(SOIC), Depopulated JEDEC MS-112, .150

Inch Body

65 kHz Reel & Tape

FAN6755UWMY -40 to +105C 130 kHz Reel & Tape

Application Diagram

L

N

EMI

Filter

+

+

HV VDD

FAN6755W

5

2

7

+

FB

VIN

SENSE

GATE

6

3

4

1

Vo+

Vo-

Figure 1. Typical Application

2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6755W / FAN6755UW Rev. 1.0.7 3

F

A

N

6

7

5

5

W

/

F

A

N

6

7

5

5

U

W

m

W

S

a

v

e

r

C

o

n

t

r

o

l

l

e

r

Internal Block Diagram

Figure 2. Internal Block Diagram

Marking Information

Figure 3. Top Mark

Z: Plant Code

X: 1-Digit Year Code

Y: 1-Digit Week Code

TT: 2-Digit Die Run Code

T: Package Type (M:SOP)

P: Y=Green Package

M: Manufacture Flow Code

ZXYTT

6755

WTPM

7

ZXYTT

6755U

WTPM

7

GATE

FB

SENSE

GND

VDD

VIN 1

5.3V

Soft

Driver

Q S

R

VIN-Protect

UVLO

Blanking

Circuit

OLP

OVP

Delay

Debounce

VDD-OVP

6

7

5

2

3

HV

Brownout Protection

OLP

3R

OLP

Comparator

PWM

Comparator

Internal

BIAS

Soft-Start

VLimit

Slope

Compensation

R

Current Limit

Comparator

Soft-Start

Comparator

4

VIN-ON / VIN-OFF

VLimit

Brownout Protection

High/Low

Line Compensation

Debounce

OLP

Re-start

Protection

OVP

VDD

OTP

V

D

D

-

O

N

/

V

D

D

-

O

F

F

V

FB-OLP

V

IN

-OVP

Green

Mode

OSC

Pattern

Generator

V

RESET

V

PWM

VRESET

Max.

Duty

VPWM

VIN-OVP

2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6755W / FAN6755UW Rev. 1.0.7 4

F

A

N

6

7

5

5

W

/

F

A

N

6

7

5

5

U

W

m

W

S

a

v

e

r

C

o

n

t

r

o

l

l

e

r

Pin Configuration

Figure 4. Pin Configuration (Top View)

Pin Definitions

Pin # Name Description

1 VIN

Line-voltage detection. The line-voltage detection is used for brownout protection with

hysteresis. Constant output power limit over universal AC input range is also achieved using this

VIN pin. It is suggested to add a low-pass filter to filter out line ripple on the bulk capacitor.

Pulling VIN HIGH also triggers auto-restart protection.

2 FB

The signal from the external compensation circuit is fed into this pin. The PWM duty cycle is

determined in response to the signal on this pin and the current-sense signal on the SENSE pin.

3 SENSE

Current sense. The sensed voltage is used for peak-current-mode control and cycle-by-cycle

current limiting.

4

GND Ground

5 GATE The totem-pole output driver. Soft-driving waveform is implemented for improved EMI.

6 VDD

Power supply. The internal protection circuit disables PWM output as long as VDD exceeds the

OVP trigger point.

7 HV For startup, this pin is connected to the line input or bulk capacitor in series with resistors.

SOP-7

VIN

VDD

GATE

HV

GND

SENSE

FB

1 7

6

5 4

2

3

2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6755W / FAN6755UW Rev. 1.0.7 5

F

A

N

6

7

5

5

W

/

F

A

N

6

7

5

5

U

W

m

W

S

a

v

e

r

C

o

n

t

r

o

l

l

e

r

Absolute Maximum Ratings

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be

operable above the recommended operating conditions and stressing the parts to these levels is not recommended.

In addition, extended exposure to stresses above the recommended operating conditions may affect device

reliability. The absolute maximum ratings are stress ratings only.

Symbol Parameter Min. Max. Unit

VVDD DC Supply Voltage

(1, 2)

30 V

VFB FB Pin Input Voltage -0.3 7.0 V

VSENSE SENSE Pin Input Voltage -0.3 7.0 V

VVIN VIN Pin Input Voltage -0.3 7.0 V

VHV HV Pin Input Voltage 700 V

PD Power Dissipation (TA50C) 400 mW

JA Thermal Resistance (Junction-to-Air) 150 C/W

TJ Operating Junction Temperature -40 +125 C

TSTG Storage Temperature Range -55 +150 C

TL Lead Temperature (Wave Soldering or IR, 10 Seconds) +260 C

ESD

Human Body Model,

JEDEC: JESD22-A114

All Pins Except HV Pin 5.5

kV

Charged Device Model,

JEDEC: JESD22-C101

All Pins Except HV Pin 2.0

Notes:

1. All voltage values, except differential voltages, are given with respect to the network ground terminal.

2. Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device.

3. ESD with HV pin: CDM=2000 V (FAN6755W) or 1500 V (FAN6755UW), and HBM=3500 V.

2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6755W / FAN6755UW Rev. 1.0.7 6

F

A

N

6

7

5

5

W

/

F

A

N

6

7

5

5

U

W

m

W

S

a

v

e

r

C

o

n

t

r

o

l

l

e

r

Electrical Characteristics

VDD=15 V, TA=25C, unless otherwise noted.

Symbol Parameter Conditions Min. Typ. Max. Unit

V

DD

Section

VOP Continuously Operating Voltage Full Load 22 V

VDD-ON Start Threshold Voltage 15 16 17 V

VDD-OFF Protection Mode 9 10 11 V

UVLO Normal Mode 6.8 7.8 8.8 V

IDD-ST Startup Current VDD-ON 0.16 V 30 A

IDD-OP Operating Supply Current VDD=15 V, GATE Open 2 mA

IDD-OLP Internal Sink Current VDD-OLP+0.1 V 30 60 90 A

VDD-OLP

Threshold Voltage on VDD for HV

JFET Turn-On

6.5 7.5 8.0 V

VDD-OVP VDD Over-Voltage Protection 25 26 27 V

tD-VDDOVP

VDD Over-Voltage Protection

Debounce Time

75 125 200 s

HV Section

IHV Supply Current Drawn from HV Pin

VDC=120 V, VDD=10 F,

VDD=0 V

2.0 3.5 5.0 mA

IHV-LC Leakage Current after Startup

HV=700 V, VDD=VDD-

OFF+1 V

1 20 A

VDD-ON

V

DD

UVLO

t

Normal Mode

VDD-ON

V

DD

VDD-OFF

t

VDD-OLP

Protection Mode

Figure 5. VDD Behavior

Continued on the following page

2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6755W / FAN6755UW Rev. 1.0.7 7

F

A

N

6

7

5

5

W

/

F

A

N

6

7

5

5

U

W

m

W

S

a

v

e

r

C

o

n

t

r

o

l

l

e

r

Electrical Characteristics

VDD=15 V, TA=25C, unless otherwise noted.

Symbol Parameter Conditions Min. Typ. Max. Unit

Oscillator Section

fOSC Frequency in Normal Mode

Center

Frequency

FAN6755W 62 65 68

kHz

FAN6755UW 124 130 136

Hopping

Range

FAN6755W 4.5 5.2 5.9

FAN6755UW 9 10.4 11.8

fOSC-G Green-Mode Frequency 20 23 26 kHz

tHOP Hopping Period 10 12 14 ms

fDV

Frequency Variation vs. VDD

Deviation

VDD=11 V to 22 V 5 %

fDT

Frequency Variation vs.

Temperature Deviation

TA=-40 to 85C=TJ 5 %

V

IN

Section

VIN-OFF

PWM Turn-Off (Brown-out)

Threshold Voltage

0.66 0.70 0.74

V

VIN-ON

PWM Turn-On (Brown in)

Threshold Voltage

VIN-OFF+

0.17

VIN-OFF+

0.20

VIN-OFF+

0.23

V

VIN-Protect

Threshold Voltage of VIN Over-

Voltage Protection

5.1 5.3 5.5 V

tVIN-Protect

Debounce Time of VIN Over-

Voltage Protection

60 100 140 s

Current-Sense Section

VLIMIT at

VIN=1 V

Threshold Voltage for Current Limit VIN=1 V 0.80 0.83 0.86 V

VLIMIT at

VIN=3 V

Threshold Voltage for Current Limit VIN=3 V 0.67 0.70 0.73 V

tPD Delay to Output 100 200 ns

tLEB Leading-Edge Blanking Time

Soft-Start (FAN6755UW) 125 150 175

ns

Steady State 240 290 340

tSS Period During Soft-Start Time Startup Time 4.0 5.5 7.0 ms

V

Limit

VIN

VIN-OFF VIN-Protect

=3V VIN VIN=1V

VSENSE=0.83V

VSENSE =0.7V

=0.92V =5.3V

Figure 6. VIN vs. VSENSE

Continued on the following page

2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6755W / FAN6755UW Rev. 1.0.7 8

F

A

N

6

7

5

5

W

/

F

A

N

6

7

5

5

U

W

m

W

S

a

v

e

r

C

o

n

t

r

o

l

l

e

r

Electrical Characteristics

VDD=15 V, TA=25C, unless otherwise noted.

Symbol Parameter Conditions Min. Typ. Max. Unit

Feedback Input Section

AV Internal FB Voltage Attenuation 1/4.5 1/4.0 1/3.5 V/V

ZFB Input Impedance V

FB

=4 V 10 15 19 k

VFB-OPEN The Maximum Clamp of FB Voltage FB Pin Open 5.1 5.3 5.5 V

VFB-OLP

FB Open-Loop Protection Triggering

Level

4.4 4.6 4.8 V

tD-OLP

Delay Time of FB Pin Open-loop

Protection

45.0 62.5 70.0 ms

VFB-N Green-Mode Entry FB Voltage 2.8 3.0 3.2 V

VFB-G Green-Mode Ending FB Voltage VFB-N - 0.6 V

VFB-ZDCR

FB Threshold Voltage for Zero-Duty

Recovery

1.6 1.8 2.0 V

VFB-ZDC FB Threshold Voltage for Zero-Duty 1.4 1.6 1.8 V

VFB-ZDCR -

VFB-ZDC

ZDC Hysteresis 0.12 0.15 0.19 V

f

OSC

f

OSC-G

V V

FB-N FB-G FB

V

Frequency

PWM

Frequency

FB-ZDC

V

FB-ZDCR

V

+ hopping range

- hopping range

+1.76KHz

-1.76KHz

Figure 7. VFB vs. PWM Frequency

Continued on the following page

2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6755W / FAN6755UW Rev. 1.0.7 9

F

A

N

6

7

5

5

W

/

F

A

N

6

7

5

5

U

W

m

W

S

a

v

e

r

C

o

n

t

r

o

l

l

e

r

Electrical Characteristics

VDD=15 V, TA=25C, unless otherwise noted.

Symbol Parameter Conditions Min. Typ. Max. Unit

GATE Section

DCYMAX Maximum Duty Cycle 60 75 90 %

VGATE-L Gate Low Voltage VDD=15 V, IO=50 mA 1.5 V

VGATE-H Gate High Voltage VDD=12 V, IO=50 mA 8 V

tr Gate Rising Time VDD=15 V, CL=1 nF

100 ns

tf Gate Falling Time VDD=15 V, CL=1 nF

30 ns

IGATE-

SOURCE

Gate Source Current VDD=15 V, GATE=6 V 700 mA

VGATE-

CLAMP

Gate Output Clamping Voltage VDD=22 V 18 V

Over-Temperature Protection Section (OTP)

TOTP Protection Junction Temperature

(4,6)

140 C

TRestart Restart Junction Temperature

(5,6)

TOTP-25 C

Notes:

4. When OTP is activated, the PWM switching is shut down.

5. When junction temperature is lower than this level, IC resumes PWM switching.

6. These parameters are guaranteed by design.

2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6755W / FAN6755UW Rev. 1.0.7 10

F

A

N

6

7

5

5

W

/

F

A

N

6

7

5

5

U

W

m

W

S

a

v

e

r

C

o

n

t

r

o

l

l

e

r

Typical Performance Characteristics

Figure 8. Startup Current (IDD-ST) vs. Temperature

Figure 9. Operation Supply Current (IDD-OP)

vs. Temperature

Figure 10. Start Threshold Voltage (VDD-ON)

vs. Temperature

Figure 11. Minimum Operating Voltage (VDD-OFF)

vs. Temperature

Figure 12. Supply Current Drawn from HV Pin (IHV)

vs. Temperature

Figure 13. HV Pin Leakage Current After Startup

(IHV-LC) vs. Temperature

Figure 14. Frequency in Normal Mode (fOSC)

vs. Temperature

Figure 15. Maximum Duty Cycle (DCYMAX)

vs. Temperature

2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6755W / FAN6755UW Rev. 1.0.7 11

F

A

N

6

7

5

5

W

/

F

A

N

6

7

5

5

U

W

m

W

S

a

v

e

r

C

o

n

t

r

o

l

l

e

r

Typical Performance Characteristics

Figure 16. FB Open-Loop Trigger Level (VFB-OLP)

vs. Temperature

Figure 17. Delay Time of FB Pin Open-Loop Protection

(tD-OLP) vs. Temperature

Figure 18. PWM Turn-Off Threshold Voltage

(VIN-OFF & VIN-ON) vs. Temperature

Figure 19. VDD Over-Voltage Protection (VDD-OVP)

vs. Temperature

Figure 20. VIN vs. VLIMIT

2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6755W / FAN6755UW Rev. 1.0.7 12

F

A

N

6

7

5

5

W

/

F

A

N

6

7

5

5

U

W

m

W

S

a

v

e

r

C

o

n

t

r

o

l

l

e

r

Functional Description

Startup Current

For startup, the HV pin is connected to the line input or

bulk capacitor in series with diodes and/or resistors. If HV

pin is connected to the line input, a 1-kV/ 1-A diode and a

100 k resistor are recommended. If HV pin is connected

to the bulk capacitor, only the resistor is required. Startup

current drawn from pin HV (typically 3.5 mA) charges the

hold-up capacitor through the diode and resistor. When

the VDD capacitor level reaches VDD-ON, the startup current

switches off. At this moment, only the VDD capacitor

supplies the FAN6755W/UW to maintain VDD before the

auxiliary winding of the main transformer to provide the

operating current.

Operating Current

Operating current is below 2 mA. The low operating

current enables better efficiency and reduces the

requirement of VDD hold-up capacitance.

Green-Mode Operation

The proprietary green-mode function provides an off-

time modulation to reduce the switching frequency in

light-load and no-load conditions. The on time is limited

for better abnormal or brownout protection. VFB, which is

derived from the voltage feedback loop, is taken as the

reference. Once VFB is lower than the threshold voltage,

switching frequency is continuously decreased to the

minimum green-mode frequency of around 23 kHz.

Current Sensing / PWM Current Limiting

Peak-current-mode control is utilized to regulate output

voltage and provide pulse-by-pulse current limiting. The

switching current is detected by the current-sensing

resistor of SENSE pin. The PWM duty cycle is

determined by this current sense signal and VFB, the

feedback voltage. When the voltage on the SENSE pin

reaches around VCOMP=(VFB0.6)/4, the PWM switching

turns off immediately.

Leading-Edge Blanking (LEB)

Each time the power MOSFET is switched on, a turn-on

spike occurs on the sense resistor. To avoid premature

termination of the switching pulse, a leading-edge

blanking time is built in. During this blanking period, the

current-limit comparator is disabled and cannot switch

off the gate driver.

Under-Voltage Lockout (UVLO)

The turn-on and turn-off thresholds are fixed internally

at 16 V and 7.8 V in normal mode. During startup, the

hold-up capacitor must be charged to 16 V through the

startup resistor to enable the IC. The hold-up capacitor

continues to supply VDD before the energy can be

delivered from auxiliary winding of the main transformer.

VDD must not drop below 7.8 V during startup. This

UVLO hysteresis window ensures that the hold-up

capacitor is adequate to supply VDD during startup.

Gate Output / Soft Driving

The BiCMOS output stage is a fast totem-pole gate

driver. Cross conduction has been avoided to minimize

heat dissipation, increase efficiency, and enhance

reliability. The output driver is clamped by an internal

18 V Zener diode to protect power MOSFET transistors

against undesirable gate over voltage. A soft-driving

circuit is implemented to minimize EMI.

Soft-Start

For many applications, it is necessary to minimize the

inrush current at startup. The built-in 5.5 ms soft-start

circuit significantly reduces the startup current spike

and output voltage overshoot.

Slope Compensation

The sensed voltage across the current-sense resistor is

used for peak-current-mode control and pulse-by-pulse

current limiting. Built-in slope compensation improves

stability and prevents sub-harmonic oscillation.

FAN6755W/UW inserts a synchronized positive-going

ramp at every switching cycle as slope compensation.

Constant Output Power Limit

For constant output power limit over universal input-

voltage range, the peak-current threshold is adjusted by

the voltage of the VIN pin. Since the VIN pin is

connected to the rectified AC input line voltage through

the resistive divider, a higher line voltage generates a

higher VIN voltage. The threshold voltage decreases as

VIN increases, making the maximum output power at

high-line input voltage equal to that at low-line input.

The value of R-C network should not be so large that it

affects the power limit (shown in Figure 21). R and C

should be less than 100 and 470 pF, respectively.

FAN6755W

SENSE

GATE

Blanking

Circuit

R

C

Figure 21. Current-Sense R-C Filter

2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6755W / FAN6755UW Rev. 1.0.7 13

F

A

N

6

7

5

5

W

/

F

A

N

6

7

5

5

U

W

m

W

S

a

v

e

r

C

o

n

t

r

o

l

l

e

r

V

DD

Over-Voltage Protection

VDD over-voltage protection prevents damage due to

abnormal conditions. Once the VDD voltage is over the

over-voltage protection voltage (VDD-OVP), and lasts for tD-

VDDOVP, the PWM pulses are disabled. When the VDD

voltage drops below the UVLO, the internal startup circuit

turns on, and VDD is charged to VDD-ON to restart IC.

Feedback Impedance Switching

FAN6755W/UW actively varies FB-pin impedance

(ZFB) to reduce no-load power consumption. This

technique can further reduce operating current of the

controller when FB-pin voltage drops below VFB-ZDC.

Figure 22 exhibits the range that ZFB changes. When

VFB is lower than VFB-ZDC, PWM switching is stopped

and ZFB is switched from 15 k to 90 k. On the other

hand, ZFB is switched from 90 k to 15 k when VFB is

higher than VFB-ZDCR.

V

FB

(V)

f

osc

(kHz)

VFB-ZDCR VFB-ZDC

Z

FB

=90k

Z

FB

=15k

Proprietary

Figure 22. ZFB-Switching Activating Range

Brownout Protection

Since the VIN pin is connected through a resistive

divider to the rectified AC input line voltage, it can also

be used for brownout protection. If VIN is less than

0.7 V, the PWM output is shut off. When VIN reaches

over 0.9 V, the PWM output is turned on again. The

hysteresis window for ON/OFF is around 0.2 V. The

brownout voltage setting is determined by the potential

divider formed with RUpper and RLower. Equations to

calculate the resistors are shown below:

) V unit ( , V

R R

R

V

AC

Upper Lower

Lower

IN

2

(1)

Thermal Overload Protection

Thermal overload protection limits total power

dissipation. When the junction temperature exceeds TJ=

+140C, the thermal sensor signals the shutdown logic

and turns off most of the internal circuitry. The thermal

sensor turns internal circuitry on again after the ICs

junction temperature drops by 25C. Thermal overload

protection is designed to protect the FAN6755W/UW in

the event of a fault condition. For continual operation,

the controller should not exceed the absolute maximum

junction temperature of TJ = +140C.

Limited Power Control

The FB voltage is saturated HIGH when the power

supply output voltage drops below its nominal value and

shut regulator (KA431) does not draw current through

the opto-coupler. This occurs when the output feedback

loop is open or output is short circuited. If the FB

voltage is higher than a built-in threshold for longer than

tD-OLP, PWM output is turned off. As PWM output is

turned off, VDD begins decreasing since no more energy

is delivered from the auxiliary winding.

As the protection is triggered, VDD enters into UVLO

mode. This protection feature continues as long as the

over loading condition persists. This prevents the power

supply from overheating due to overloading conditions.

Noise Immunity

Noise on the current sense or control signal may cause

significant pulse-width jitter, particularly in continuous-

conduction mode. Slope compensation helps alleviate

this problem. Good placement and layout practices

should be followed. Avoiding long PCB traces and

component leads, locating compensation and filter

components near the FAN6755W/UW, and increasing

the gate resistor from GATE pin to MOSFET improve

performance.

2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6755W / FAN6755UW Rev. 1.0.7 14

F

A

N

6

7

5

5

W

/

F

A

N

6

7

5

5

U

W

m

W

S

a

v

e

r

C

o

n

t

r

o

l

l

e

r

Typical Application Circuit

2

1

3

4

BD1

F1

+

C11

R9

C17

R19

C16

R18

1

2

3

Q1

R28

R12

2

1

D4

+ C18

C4

2

1

D3

1

2

4

3

U2

A

K

R

U3

R21 C20

R26

R23 R24

12V 5V

R20

+ C8 + C9

12V

+ C14

5V

R5

R7

C7

C6

1

2

3

CN1

AC IN

1

3

2

D5

1

3

2

D1

R6

R4

1 2

L2

1 2

L3

R16

7

10

2

1

6

4 12

11

9

8

TX1

1

2 3

4

L1

C5

M1

2

1

D2 R11

C15

C10

R1

R2

C3

C1

C2

R8

R17

L

N

N1 N2

N3

N4

N5 N6

N7

N8

N9

VDD FB

SENSE

GATE

HV

N10

N12 N13

N14 N15

N16

N17

N18

N20

N21

N1A

N28

N29

P1

12V

P2

5V

P3

SGND

+ C13

C19

R15

12V1

R27

R25

R13

R10

N30

C12

R3

R14

VIN

VIN

2

1

ZD1

R22

5V1

5V1

VIN

1

FB

2

SENSE

3

GND

4

GATE

5

VDD

6

HV

7

U1

FAN6755

FAN6755W

Figure 23. 44 W Flyback 12 V/2 A, 5 V/4 A Application Circuit

2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6755W / FAN6755UW Rev. 1.0.7 15

F

A

N

6

7

5

5

W

/

F

A

N

6

7

5

5

U

W

m

W

S

a

v

e

r

C

o

n

t

r

o

l

l

e

r

Bill of Materials

Designator Part Type Designator Part Type

BD1 BD 4 A/600 V Q1 MOS 9 A/600 V

C1 YC 2200 pF/Y1 R1 R 1.5 M 1/4 W

C2 YC 2200 pF/Y1 R2 R 1.5 M 1/4 W

C3 XC 0.33 F/300 V R3 R 10 M 1/4 W

C4 NC R4, R5, R6, R7 R 47 1/4 W

C5 YC 2200 pF/Y1 R8, R17, R25, R27 NC

C6 CC 2200 pF/100 V R9 R 50 K 1/4 W

C7 CC 1000 pF/100 V R10 R 50 K 1/4 W

C8 EC 1000 F/25 V R11 R 0 1/8 W

C9 EC 470 F/25 V R12 R 47 1/8 W

C10 CC 100 pF/50 V R13 R 100 K 1/8 W

C11 EC 100 F/400 V R14 R 0 1/4 W

C12 C 1 F/50 V R15 R 10 K 1/8 W

C13 EC 1000 F/10 V R16 R 1 1/8 W

C14 EC 470 F/10 V R18 R 0 1/8 W

C15 CC 100 pF/50 V R19 R 100 1/8 W

C16 C 1 nF/50 V R20 R 1 K 1/8 W

C17 C 470 pF/50 V R21 R 4.7 K 1/8 W

C18 EC 47 F/50 V R22 R 7.5 K 1/8 W

C19 C 0.01 F/50 V R23 R 120 K 1/8 W

C20 C 0.1 F/50 V R24 R 15 K 1/8 W

D1 FYP1010 R26 R 10 K 1/8 W

D2 1N4148 R28 R 0.43 2 W

D3 FR107 TX1 800 H(ERL-28)

D4 FR103 U1 IC FAN6755W

D5 FYP1010 U2 IC PC817

ZD1 P6KE150A U3 IC TL431

F1 FUSE 4A/250V

M1 VZ 9G

L1 13 mH

L2 Inductor (2 H)

L3 Inductor (2 H)

2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6755W / FAN6755UW Rev. 1.0.7 16

F

A

N

6

7

5

5

W

/

F

A

N

6

7

5

5

U

W

m

W

S

a

v

e

r

C

o

n

t

r

o

l

l

e

r

Physical Dimensions

PIN #1

FRONT VIEW

TOP VIEW

8

0

SEE DETAIL A

LAND PATTERN RECOMMENDATION

SEATING PLANE

C

GAGE PLANE

x 45

DETAIL A

SCALE: 2:1

4

7

1

B

5

A

3.85

0.65TYP

1.75TYP

1.27

6.20

5.80

3.81

4.00

3.80

5.00

4.80

(0.33)

1.27

0.51

0.33

0.25

0.10

1.75 MAX

0.25

0.19

0.36

0.50

0.25

R0.10

R0.10

0.90

0.406 (1.04)

OPTION A - BEVEL EDGE

OPTION B - NO BEVEL EDGE

7.35

3.81

NOTES:

A) THIS PACKAGE DOES NOT FULLY CONFORMS

TO JEDEC MS-012, VARIATION AA, ISSUE C,

DATED MAY 1990.

B) ALL DIMENSIONS ARE IN MILLIMETERS.

C) DIMENSIONS DO NOT INCLUDE MOLD

FLASH OR BURRS.

D) STANDARD LEAD FINISH:

200 MICROINCHES / 5.08 MICRONS MIN.

LEAD/TIN (SOLDER) ON COPPER.

E) DRAWING FILENAME : M07Arev3

2 3

6

0.25 C B A

0.10 C

Figure 24. 7-Lead, Small Outline Package (SOP)

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner

without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify

or obtain the most recent revision. Package specifications do not expand the terms of Fairchilds worldwide terms and conditi ons,

specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductors online packaging area for the most recent package drawings:

http://www.fairchildsemi.com/packaging/.

7

2009 Fairchild Semiconductor Corporation www.fairchildsemi.com

FAN6755W / FAN6755UW Rev. 1.0.7 17

F

A

N

6

7

5

5

W

/

F

A

N

6

7

5

5

U

W

m

W

S

a

v

e

r

C

o

n

t

r

o

l

l

e

r

You might also like

- Necrological ServiceDocument5 pagesNecrological Servicesir jj89% (28)

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- EGS002 Manual en PDFDocument6 pagesEGS002 Manual en PDFValerică Hizanu67% (6)

- EGS002 Manual en PDFDocument6 pagesEGS002 Manual en PDFValerică Hizanu67% (6)

- Sony - APS-252 - KLV-32BX300 AZ1-A - CXA3809MDocument1 pageSony - APS-252 - KLV-32BX300 AZ1-A - CXA3809MAndres Alegria100% (2)

- KDI49QT542LNT Main Board P75-628VX V6.0 Circuit DiagramDocument13 pagesKDI49QT542LNT Main Board P75-628VX V6.0 Circuit DiagramAndres AlegriaNo ratings yet

- Unit 2 - Compass CorrectionDocument81 pagesUnit 2 - Compass CorrectionUtpal Kant100% (2)

- Fan 6755 TEOT 6755Document17 pagesFan 6755 TEOT 6755Jorge HonzNo ratings yet

- DNP015 Fairchild SemiconductorDocument13 pagesDNP015 Fairchild SemiconductorIvan InqognitoNo ratings yet

- FAN7602B Green Current-Mode PWM Controller: Features DescriptionDocument17 pagesFAN7602B Green Current-Mode PWM Controller: Features DescriptionNichole RollinsNo ratings yet

- Aajfk Sg6859aDocument13 pagesAajfk Sg6859azarevgNo ratings yet

- OB2269Document12 pagesOB2269Juan Ballon100% (1)

- ACPI Regulator/Controller For Dual Channel DDR Memory Systems FeaturesDocument15 pagesACPI Regulator/Controller For Dual Channel DDR Memory Systems FeaturesnakameiyoNo ratings yet

- Design Guideline To Replace FAN6753 With FAN6755: Table 1. Comparison of FAN6753 and FAN6755Document9 pagesDesign Guideline To Replace FAN6753 With FAN6755: Table 1. Comparison of FAN6753 and FAN6755Ántico le RoixNo ratings yet

- Fan6755W / Fan6755Uw Mwsaver PWM Controller: Features DescriptionDocument17 pagesFan6755W / Fan6755Uw Mwsaver PWM Controller: Features DescriptionJorge MateusNo ratings yet

- LD7750-DS Fuente TCL GermanDocument20 pagesLD7750-DS Fuente TCL GermanAndres Alegria100% (1)

- R7731Document11 pagesR7731Malay K GhoshNo ratings yet

- FAN73832 (Half-Bridge Dead Time Control)Document16 pagesFAN73832 (Half-Bridge Dead Time Control)Ismael StarkNo ratings yet

- Fan 7316Document21 pagesFan 7316sontuyet82No ratings yet

- FSQ0565R, FSQ0765R Green-Mode Fairchild Power Switch (FPS™) For Quasi-Resonant OperationDocument0 pagesFSQ0565R, FSQ0765R Green-Mode Fairchild Power Switch (FPS™) For Quasi-Resonant Operationsontuyet82No ratings yet

- ADVR 12 Manual enDocument6 pagesADVR 12 Manual enSyed Mohammad Naveed0% (1)

- FSQ110 Green Mode Fairchild Power Switch (FPS™) : Features DescriptionDocument12 pagesFSQ110 Green Mode Fairchild Power Switch (FPS™) : Features DescriptionJohan BeckersNo ratings yet

- Viper 100Document8 pagesViper 100SeanNo ratings yet

- EN5322QI: 2 A Voltage Mode Synchronous Buck PWM DC-DC Converter With Integrated InductorDocument16 pagesEN5322QI: 2 A Voltage Mode Synchronous Buck PWM DC-DC Converter With Integrated Inductorcatsoithahuong84No ratings yet

- WPMDL950003 - WPMDL950005Document12 pagesWPMDL950003 - WPMDL950005Lullaby summerNo ratings yet

- FAN7602 - Green Current Mode PWM Controller - Fairchild SemiconductorDocument17 pagesFAN7602 - Green Current Mode PWM Controller - Fairchild SemiconductorVijay MistryNo ratings yet

- Fan 7530Document20 pagesFan 7530aldo_suviNo ratings yet

- ADocument17 pagesAWillian CristianoNo ratings yet

- NCP 2171Document19 pagesNCP 2171mari_casuNo ratings yet

- SM7530 LinkageDocument6 pagesSM7530 Linkagedecaedron decaedrumNo ratings yet

- Fan 7711Document21 pagesFan 7711uumpNo ratings yet

- SG 6841 TDocument14 pagesSG 6841 TBayron Salazar SaborioNo ratings yet

- Mip 2 C 2Document3 pagesMip 2 C 2Shubham AdkeNo ratings yet

- 4096 Circuito IntegradoDocument7 pages4096 Circuito IntegradoalexmanriqueNo ratings yet

- DM0565Document21 pagesDM0565Tammy WashingtonNo ratings yet

- ADP3180Document20 pagesADP3180chrizzcloNo ratings yet

- CAR1248TNDocument8 pagesCAR1248TNpatopickNo ratings yet

- NCP1337 D PDFDocument15 pagesNCP1337 D PDFBoKi PoKiNo ratings yet

- FAN7535 PFC & Ballast Control IC: Features DescriptionDocument12 pagesFAN7535 PFC & Ballast Control IC: Features Descriptionashish_rewaNo ratings yet

- Fan 7392NDocument18 pagesFan 7392NKhaleel MohammadNo ratings yet

- High Efficiency Low-Side N-Channel Controller For Switching RegulatorsDocument33 pagesHigh Efficiency Low-Side N-Channel Controller For Switching Regulatorssoft4gsmNo ratings yet

- Dap011 DDocument24 pagesDap011 Dsontuyet82No ratings yet

- Surge Protection Made Simple™ For Telecom Applications: BSPM1A48D60LV (R) BSPM1A75D100LV (R) BSPM1A150D200LV (R)Document2 pagesSurge Protection Made Simple™ For Telecom Applications: BSPM1A48D60LV (R) BSPM1A75D100LV (R) BSPM1A150D200LV (R)Rajasekaran RNo ratings yet

- A6251m PDFDocument7 pagesA6251m PDFYudi ElektroNo ratings yet

- NCP 43080Document36 pagesNCP 43080TestronicpartsNo ratings yet

- Fod8316 108263Document30 pagesFod8316 108263hieuhuech1No ratings yet

- 450W Single Output Medical Type: SeriesDocument3 pages450W Single Output Medical Type: SeriesshubhraenergyNo ratings yet

- DM0265Document19 pagesDM0265liberthNo ratings yet

- RT9193 Maybe VA Communication CardDocument14 pagesRT9193 Maybe VA Communication Cardrazali1982No ratings yet

- Description: Green-Power PWM Controller With Freq. JigglingDocument8 pagesDescription: Green-Power PWM Controller With Freq. JigglingLuis GuevaraNo ratings yet

- ELECTRONICDocument13 pagesELECTRONICMahmoued YasinNo ratings yet

- Viper 100 ADocument31 pagesViper 100 AvasilesicoeNo ratings yet

- Bd9397efv e PDFDocument30 pagesBd9397efv e PDFshafiuddin7326No ratings yet

- IC-ON-LINE - CN dm0465r 44841Document20 pagesIC-ON-LINE - CN dm0465r 44841ubhagavanNo ratings yet

- Data SheetDocument7 pagesData SheetOvi PanteaNo ratings yet

- Ir1161lpbf - Infineon Solutions For Transportation 24V To 60VDocument25 pagesIr1161lpbf - Infineon Solutions For Transportation 24V To 60VAnonymous R0s4q9X8No ratings yet

- NME 5V & 12V Series: Isolated 1W Single Output DC/DC ConvertersDocument6 pagesNME 5V & 12V Series: Isolated 1W Single Output DC/DC ConvertersMarcos SantosNo ratings yet

- LM5007 High Voltage (80V) Step Down Switching Regulator: FeaturesDocument17 pagesLM5007 High Voltage (80V) Step Down Switching Regulator: FeaturesbhushanchittaragiNo ratings yet

- LCD Bias Power Integrated With WLED Backlight Drivers: FeaturesDocument31 pagesLCD Bias Power Integrated With WLED Backlight Drivers: FeaturesJoseph BernardNo ratings yet

- Analog Dialogue Volume 46, Number 1: Analog Dialogue, #5From EverandAnalog Dialogue Volume 46, Number 1: Analog Dialogue, #5Rating: 5 out of 5 stars5/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- On-Chip Electro-Static Discharge (ESD) Protection for Radio-Frequency Integrated CircuitsFrom EverandOn-Chip Electro-Static Discharge (ESD) Protection for Radio-Frequency Integrated CircuitsNo ratings yet

- FGPF 4633Document9 pagesFGPF 4633Andres AlegriaNo ratings yet

- Radio FM Con RDS Un Proyecto HAT Superior para Raspberry Pi PDFDocument8 pagesRadio FM Con RDS Un Proyecto HAT Superior para Raspberry Pi PDFAndres AlegriaNo ratings yet

- Haier: Service ManualDocument52 pagesHaier: Service ManualAndres AlegriaNo ratings yet

- FAN73711 High-Current, High-Side Gate Drive IC: Features DescriptionDocument12 pagesFAN73711 High-Current, High-Side Gate Drive IC: Features DescriptionAndres AlegriaNo ratings yet

- Telefunken+TF LED50S10T2+K PL L01Document4 pagesTelefunken+TF LED50S10T2+K PL L01Andres AlegriaNo ratings yet

- 12.09.27 Selectionguide AC-DCandPFCDocument47 pages12.09.27 Selectionguide AC-DCandPFCGabriel TorresNo ratings yet

- Aoc Le39a0321 OvidioDocument68 pagesAoc Le39a0321 OvidioAndres AlegriaNo ratings yet

- LG 60LB5800 Chassis LJ46BDocument64 pagesLG 60LB5800 Chassis LJ46BAndres AlegriaNo ratings yet

- LGP32-14PL1 Rev3.1 PCB Eax65391401 Eax65693102Document29 pagesLGP32-14PL1 Rev3.1 PCB Eax65391401 Eax65693102Andres AlegriaNo ratings yet

- AP3041 Ic Driver Placa Simply Syled37i Que Se QuemaDocument14 pagesAP3041 Ic Driver Placa Simply Syled37i Que Se QuemaAndres Alegria0% (1)

- MFL68606401 32LF550D-DD Da NewDocument74 pagesMFL68606401 32LF550D-DD Da NewAndres Alegria100% (2)

- (LJ46B) 32LB580B-SBDocument79 pages(LJ46B) 32LB580B-SBMárcio FerreiraNo ratings yet

- MHDV2262-04 Fuente Ob2273Document64 pagesMHDV2262-04 Fuente Ob2273Andres AlegriaNo ratings yet

- Yamaha P5000S FuenteDocument1 pageYamaha P5000S FuenteAndres Alegria0% (2)

- Data SheetDocument62 pagesData SheetToni Martin SebéNo ratings yet

- Green-Mode PWM Controller With Frequency Trembling and Integrated ProtectionsDocument18 pagesGreen-Mode PWM Controller With Frequency Trembling and Integrated ProtectionsAndres AlegriaNo ratings yet

- 2A20112 PFC Fuentes LG Audio PFC CRITICALDocument9 pages2A20112 PFC Fuentes LG Audio PFC CRITICALAndres AlegriaNo ratings yet

- MS08FPDocument1 pageMS08FPAndres AlegriaNo ratings yet

- DVD Home Theater System: Service ManualDocument61 pagesDVD Home Theater System: Service ManualAndres AlegriaNo ratings yet

- MS08FPDocument1 pageMS08FPAndres AlegriaNo ratings yet

- MP3398A - r1.05 Driver Les Board Flaco BellohorizonteDocument20 pagesMP3398A - r1.05 Driver Les Board Flaco BellohorizonteAndres AlegriaNo ratings yet

- Am 5888Document10 pagesAm 5888Andres AlegriaNo ratings yet

- Device Specification: I C-Bus Controlled PAL/NTSC/SECAM TV ProcessorsDocument69 pagesDevice Specification: I C-Bus Controlled PAL/NTSC/SECAM TV ProcessorsAdolfo LacerdaNo ratings yet

- P130-628VX V6.0 - Circuit DiagramDocument13 pagesP130-628VX V6.0 - Circuit DiagramAndres Alegria80% (15)

- NI Film Showing Guide Questions 1Document2 pagesNI Film Showing Guide Questions 1Lassie AbusadoNo ratings yet

- Dokumen - Tips Descriptive Comparative Historical LinguisticsDocument20 pagesDokumen - Tips Descriptive Comparative Historical LinguisticsSmt 355No ratings yet

- Christian Response To Conversion DebateDocument11 pagesChristian Response To Conversion DebateVivek SlpisaacNo ratings yet

- DOST Puts Up Free Online Reviewer For PSHS ExamsDocument2 pagesDOST Puts Up Free Online Reviewer For PSHS ExamsOlecram Luarez Jr.No ratings yet

- UltrasoundgelDocument5 pagesUltrasoundgelWitbaasNo ratings yet

- About Quickxpert Infotech: - Sap Modules, Java, Dot Net, Software Testing, WebDocument13 pagesAbout Quickxpert Infotech: - Sap Modules, Java, Dot Net, Software Testing, Webchitra moteNo ratings yet

- Test Description Result Flag Unit Ref. Range: 9.8 L 4.18 L 32.3 L 77.27 L 23.44 L 30.34 LDocument2 pagesTest Description Result Flag Unit Ref. Range: 9.8 L 4.18 L 32.3 L 77.27 L 23.44 L 30.34 Lnamrata3660No ratings yet

- Standard Protocol of Seminar or Project - Modified FinalDocument34 pagesStandard Protocol of Seminar or Project - Modified FinalAkhil AnilNo ratings yet

- Data Rate Limits: Dept. of Computer Engineering Faculty of EngineeringDocument31 pagesData Rate Limits: Dept. of Computer Engineering Faculty of Engineeringআসিফ রেজাNo ratings yet

- Metastock Guide PDFDocument20 pagesMetastock Guide PDFraviNo ratings yet

- Jibachha Veterinary Hospital Kathmandu, BranchDocument8 pagesJibachha Veterinary Hospital Kathmandu, BranchJibachha ShahNo ratings yet

- Interface Mass TraDocument26 pagesInterface Mass TraWahid AliNo ratings yet

- New Project List 1Document12 pagesNew Project List 1Sachin K GowdaNo ratings yet

- General Regulatory Statement For RCBDocument5 pagesGeneral Regulatory Statement For RCBRoshni PattanayakNo ratings yet

- Environmental Policy 2020Document1 pageEnvironmental Policy 2020bosemahatmaNo ratings yet

- Basic Operations in Stack:: Push OperationDocument3 pagesBasic Operations in Stack:: Push Operationذیشان چودھریNo ratings yet

- Revised Conceptual Framework: Rainiel C. Soriano, CPA, MBADocument60 pagesRevised Conceptual Framework: Rainiel C. Soriano, CPA, MBAMila VeranoNo ratings yet

- Power System Stability: Prof. M Venkateswara RaoDocument56 pagesPower System Stability: Prof. M Venkateswara RaochinnaNo ratings yet

- Bulkscan Manual PDFDocument102 pagesBulkscan Manual PDFarhivarrNo ratings yet

- Salaries - Rock Falls, East Coloma SD 12Document2 pagesSalaries - Rock Falls, East Coloma SD 12saukvalleynewsNo ratings yet

- DSE12P1E Set1Document21 pagesDSE12P1E Set1Hmt1167 HoNo ratings yet

- Reflection Paper 1Document1 pageReflection Paper 1elizabeth clare yabutNo ratings yet

- Final Paper- Advanced Methodology for Language TeachingDocument7 pagesFinal Paper- Advanced Methodology for Language TeachingNhật LệNo ratings yet

- ScriptDocument4 pagesScriptapi-294984935No ratings yet

- 3E-Fii - KICPAA Webinar On ToI - 4 Mar 2022Document21 pages3E-Fii - KICPAA Webinar On ToI - 4 Mar 2022Vuthy DaraNo ratings yet

- Dr. Dr. Tjokorda Gde, SP - PD KEMD-Thyroid NoduleDocument51 pagesDr. Dr. Tjokorda Gde, SP - PD KEMD-Thyroid NodulevinahandoyoNo ratings yet

- Mississippi River SymbolismDocument5 pagesMississippi River SymbolismNoody Noody100% (1)

- Unit-2 The RhinocerosDocument11 pagesUnit-2 The Rhinocerosbhawnaghoshofficial78No ratings yet