Detailed MOS Gate Capacitance Model: Chapter 2 MOS Transistor Theory

Detailed MOS Gate Capacitance Model: Chapter 2 MOS Transistor Theory

Uploaded by

Carlos SaavedraCopyright:

Available Formats

Detailed MOS Gate Capacitance Model: Chapter 2 MOS Transistor Theory

Detailed MOS Gate Capacitance Model: Chapter 2 MOS Transistor Theory

Uploaded by

Carlos SaavedraOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

Detailed MOS Gate Capacitance Model: Chapter 2 MOS Transistor Theory

Detailed MOS Gate Capacitance Model: Chapter 2 MOS Transistor Theory

Uploaded by

Carlos SaavedraCopyright:

Available Formats

70 Chapter 2 MOS Transistor Theory

2.8(a), each source and drain has its own isolated region of contacted diffusion. In Figure

2.8(b), the drain of the bottom transistor and source of the top transistor form a shared

contacted diffusion region. In Figure 2.8(c), the source and drain are merged into an

uncontacted region. The average capacitance of each of these types of regions can be cal-

culated or measured from simulation as a transistor switches between VDD and GND.

Table 8.5 also lists the capacitance for each scenario for a variety of processes.

For the purposes of hand estimation, you can observe that the diffusion capacitance

Csb and Cdb of contacted source and drain regions is comparable to the gate capacitance

(e.g., 1–2 f F /Rm of gate width). The diffusion capacitance of the uncontacted source or

drain is somewhat less because the area is smaller but the difference is usually unimportant

for hand calculations. These values of Cg = Csb = Cdb ~ 1f F /Rm will be used in examples

throughout the text, but you should obtain the appropriate data for your process using

methods to be discussed in Section 8.4.

2.3.2 Detailed MOS Gate Capacitance Model

The MOS gate sits above the channel and may partially overlap the source and drain dif-

fusion areas. Therefore, the gate capacitance has two components: the intrinsic capaci-

tance Cgc (over the channel) and the overlap capacitances Cgol (to the source and drain).

The intrinsic capacitance was approximated as a simple parallel plate in EQ (2.12)

with capacitance C0 = WLCox. However, the bottom plate of the capacitor depends on the

mode of operation of the transistor. The intrinsic capacitance has three components repre-

senting the different terminals connected to the bottom plate: Cgb (gate-to-body), Cgs

(gate-to-source), and Cgd (gate-to-drain). Figure 2.9(a) plots capacitance vs. Vgs in the cut-

off region and for small Vds, while 2.9(b) plots capacitance vs. Vds in the linear and satura-

tion regions [Dally98].

Cgc

C0 Cgb

1. Cutoff. When the transistor is OFF (Vgs < Vt), the channel is not inverted and charge

on the gate is matched with opposite charge from the body. This is called Cgb , the

C0

2 Cgs,

gate-to-body capacitance. For negative Vgs, the transistor is in accumulation and Cgb =

Cgd C0. As Vgs increases but remains below a threshold, a depletion region forms at the

0 Vgs surface. This effectively moves the bottom plate downward from the oxide, reducing

<1 0 Vt 1 the capacitance, as shown in Figure 2.9(a).

(a)

2. Linear. When Vgs > Vt, the channel inverts and again serves as a good conductive bot-

tom plate. However, the channel is connected to the source and drain, rather than the

C0 Cgc

body, so Cgb drops to 0. At low values of Vds, the channel charge is roughly shared

Cgs 2 between source and drain, so Cgs = Cgd = C0/2. As Vds increases, the region near the

C0 3 C0

2 drain becomes less inverted, so a greater fraction of the capacitance is attributed to the

Cgd source and a smaller fraction to the drain, as shown in Figure 2.9(b).

Vds

0

0 1

Vdsat 3. Saturation. At Vds > Vdsat, the transistor saturates and the channel pinches off. At this

(b)

point, all the intrinsic capacitance is to the source, as shown in Figure 2.9(b). Because

of pinchoff, the capacitance in saturation reduces to Cgs = 2/3 C0 for an ideal transis-

FIGURE 2.9 Intrinsic gate capac-

itance Cgc = Cgs + Cgd + Cgb as a

tor [Gray01].

function of (a) Vgs and (b) Vds The behavior in these three regions can be approximated as shown in Table 2.1.

You might also like

- Chap2 Lect06 RC ModelDocument11 pagesChap2 Lect06 RC ModeldkishoreNo ratings yet

- Lec03 AE MS14Document43 pagesLec03 AE MS14Mohsin Abbas ZafarNo ratings yet

- Mosfet CapacitancesDocument17 pagesMosfet Capacitancesbhvkch2n0389100% (1)

- L3 (Part A) - MOS Oxide CapDocument19 pagesL3 (Part A) - MOS Oxide CapSambhav GullaNo ratings yet

- Feedback AmlifiersDocument32 pagesFeedback AmlifiersNarayana Rao RevallaNo ratings yet

- IntroductionDocument31 pagesIntroductionWagner SilvaNo ratings yet

- Design Unit-II: Choose The Correct Option From Following A. Space RequirementDocument3 pagesDesign Unit-II: Choose The Correct Option From Following A. Space RequirementUrstruly SriNo ratings yet

- EC4068D-Analog MOS Integrated Circuits Dhanaraj K. J. Associate Professor ECED, NIT CalicutDocument12 pagesEC4068D-Analog MOS Integrated Circuits Dhanaraj K. J. Associate Professor ECED, NIT CalicutM KIRITI SAI KUMARNo ratings yet

- Mos CapacitancesDocument26 pagesMos CapacitancesAbhishek SinghNo ratings yet

- Charge PumpsDocument7 pagesCharge Pumpsjofinjv3194100% (1)

- Frequency Response of Mosfet The Expanded Hybrid Equivalent Circuit of The Bipolar Transistor High-Frequency ResponseDocument37 pagesFrequency Response of Mosfet The Expanded Hybrid Equivalent Circuit of The Bipolar Transistor High-Frequency ResponseMuthukrishnan Vijayan VijayanNo ratings yet

- Capacitive Sensing Technology: 2.1 OverviewDocument28 pagesCapacitive Sensing Technology: 2.1 Overviewsdgpass2585No ratings yet

- L1 - MOS Junction CapDocument28 pagesL1 - MOS Junction CapRaghu RamanNo ratings yet

- Lec08 Ae Ms14Document34 pagesLec08 Ae Ms14Mohsin Abbas ZafarNo ratings yet

- Self Biased Complementary Folded Cascode Op AmpDocument3 pagesSelf Biased Complementary Folded Cascode Op AmpCapitaneanu StefanNo ratings yet

- Comparator Kick Back Noise PaperDocument8 pagesComparator Kick Back Noise Papergr8minds4allNo ratings yet

- Lab Vi. Small Signal Models of PN Junction Diodes: 1. ObjectiveDocument10 pagesLab Vi. Small Signal Models of PN Junction Diodes: 1. ObjectiveGregory WilsonNo ratings yet

- Appendix B: Calculation of Line and Cable ConstantsDocument20 pagesAppendix B: Calculation of Line and Cable ConstantsGilang SamudraNo ratings yet

- 3450 1 PDFDocument20 pages3450 1 PDFKen WalkerNo ratings yet

- Fundamentals of Adiabatic Logic: 2.1 The Charging Process in Adiabatic Logic Compared To Static CMOSDocument19 pagesFundamentals of Adiabatic Logic: 2.1 The Charging Process in Adiabatic Logic Compared To Static CMOSRaja PosupoNo ratings yet

- BR Magzine3Document4 pagesBR Magzine3Chau Nguyen MinhNo ratings yet

- Test-2 - Capacitor + Work + CurrentDocument7 pagesTest-2 - Capacitor + Work + CurrentSombir AhlawatNo ratings yet

- MOSFET-Internal Capacitances PDFDocument11 pagesMOSFET-Internal Capacitances PDFJayanth Sriranga100% (2)

- Impact of Mosfet Parameters On Its Parasitic Capacitances: Presented byDocument27 pagesImpact of Mosfet Parameters On Its Parasitic Capacitances: Presented bysattuhappyNo ratings yet

- Dual Gate BucketDocument8 pagesDual Gate BucketVigneswaran VigneshNo ratings yet

- Charge Density in MOSDocument68 pagesCharge Density in MOSJay Chandra DharNo ratings yet

- 17-Article Text in MSWORD Format-249-2-10-20140210 PDFDocument5 pages17-Article Text in MSWORD Format-249-2-10-20140210 PDFOmarFaruqeNo ratings yet

- EE3032 Introduction To VLSI Design-Homework 2Document1 pageEE3032 Introduction To VLSI Design-Homework 2陳大立No ratings yet

- Questions 2Document1 pageQuestions 2megaag007No ratings yet

- CAPACITORSDocument4 pagesCAPACITORSphysicist sharmaNo ratings yet

- Today's Topic: Integrated Devices and Modeling (With Focus On MOS Transistor) (Chapter 1)Document52 pagesToday's Topic: Integrated Devices and Modeling (With Focus On MOS Transistor) (Chapter 1)Akhendra KumarNo ratings yet

- 3.3.3 CS Stage With Current-Source Load: V m1 m2 O1 O2Document2 pages3.3.3 CS Stage With Current-Source Load: V m1 m2 O1 O2Nguyễn HiếuNo ratings yet

- Introduction To Capacitors Inductors andDocument68 pagesIntroduction To Capacitors Inductors andIlavarasan Tamizh100% (1)

- Fund - Circuit Chap THREEDocument29 pagesFund - Circuit Chap THREEERMIAS AmanuelNo ratings yet

- 0.1 MOS Transistor at High Frequency: GS GDDocument2 pages0.1 MOS Transistor at High Frequency: GS GDSimone MolinaroNo ratings yet

- Apacitance: Section (A) : Definition of CapacitanceDocument7 pagesApacitance: Section (A) : Definition of CapacitanceSwayam JindalNo ratings yet

- c-2c DAC Architecture PDFDocument3 pagesc-2c DAC Architecture PDFshobhit960No ratings yet

- C R Robertson Fundamental Electrical and ElectroBookZZ - Org 11Document10 pagesC R Robertson Fundamental Electrical and ElectroBookZZ - Org 11Salmarianto AntoNo ratings yet

- High Accuracy CMOS Capacitance Multiplier: SalvatoreDocument4 pagesHigh Accuracy CMOS Capacitance Multiplier: SalvatoreJatinKumarNo ratings yet

- CDVDT SolutionDocument6 pagesCDVDT SolutionKiran KumarNo ratings yet

- 3 - CapacitorDocument15 pages3 - CapacitorRichie BobbyNo ratings yet

- Capacitors (EEE-1101)Document22 pagesCapacitors (EEE-1101)Mubashshir AminNo ratings yet

- Mosfet CapacidadesDocument8 pagesMosfet Capacidadesluis coriaNo ratings yet

- Lab 3Document28 pagesLab 32024eem1016No ratings yet

- The Ideal Mos CapacitorDocument33 pagesThe Ideal Mos Capacitortennisbat91No ratings yet

- Charge Scaling DACDocument7 pagesCharge Scaling DACmilostar6No ratings yet

- Review of Mosfet Capacitances: The Capacitances Usually Given in FF/ MDocument46 pagesReview of Mosfet Capacitances: The Capacitances Usually Given in FF/ MSalim SanNo ratings yet

- Module2 - Capacitor and Resistor ModelDocument37 pagesModule2 - Capacitor and Resistor Modeldilshan singhNo ratings yet

- MOS CapacitanceDocument19 pagesMOS CapacitanceSandeep LocharlaNo ratings yet

- Vaz 2017Document6 pagesVaz 2017Santhosh H ANo ratings yet

- Module 3-FTDocument14 pagesModule 3-FTayushNo ratings yet

- Ch-2 SlidesCapacitanceDocument22 pagesCh-2 SlidesCapacitanceMonaf Dheaa AlfalahiNo ratings yet

- C R Robertson Fundamental Electrical and ElectroBookZZ - Org 12Document10 pagesC R Robertson Fundamental Electrical and ElectroBookZZ - Org 12Salmarianto AntoNo ratings yet

- VPT (Cet) 03 PhysicsDocument9 pagesVPT (Cet) 03 Physicsaishwarya kadamNo ratings yet

- Transactions Briefs: Improved Switched Tuning of Differential Cmos VcosDocument4 pagesTransactions Briefs: Improved Switched Tuning of Differential Cmos VcoskurabyqldNo ratings yet

- MOSFET Small Signal Analysy and BiasingDocument6 pagesMOSFET Small Signal Analysy and BiasingECHAVEZ TRILLOS FRANCISCO JAVIERNo ratings yet

- Lec05 Ae Ms14Document27 pagesLec05 Ae Ms14Mohsin Abbas ZafarNo ratings yet

- Epc M2Document14 pagesEpc M2harshithmnaidu95No ratings yet

- Easy(er) Electrical Principles for General Class Ham License (2019-2023)From EverandEasy(er) Electrical Principles for General Class Ham License (2019-2023)No ratings yet

- Heterojunction Bipolar Transistors for Circuit Design: Microwave Modeling and Parameter ExtractionFrom EverandHeterojunction Bipolar Transistors for Circuit Design: Microwave Modeling and Parameter ExtractionNo ratings yet

- Pitfalls and Fallacies: Targeting A Bleeding-Edge ProcessDocument1 pagePitfalls and Fallacies: Targeting A Bleeding-Edge ProcessCarlos SaavedraNo ratings yet

- Cmos Vlsi Design 198Document1 pageCmos Vlsi Design 198Carlos SaavedraNo ratings yet

- CMOS VLSI Design 192Document1 pageCMOS VLSI Design 192Carlos SaavedraNo ratings yet

- Logical Effort of Paths: A and C Begin To Rise (Figure 4.28 (C) ) - at First, Both Nodes See ApproximatelyDocument1 pageLogical Effort of Paths: A and C Begin To Rise (Figure 4.28 (C) ) - at First, Both Nodes See ApproximatelyCarlos SaavedraNo ratings yet

- 3.4 CMOS Process Enhancements: 3.4.3.3 InductorsDocument1 page3.4 CMOS Process Enhancements: 3.4.3.3 InductorsCarlos SaavedraNo ratings yet

- Cmos Vlsi Design 149Document1 pageCmos Vlsi Design 149Carlos SaavedraNo ratings yet

- Layer Density Rules: Chapter 3 CMOS Processing TechnologyDocument1 pageLayer Density Rules: Chapter 3 CMOS Processing TechnologyCarlos SaavedraNo ratings yet

- 4.4.6.4 Voltage Dependence: Chapter 4 DelayDocument1 page4.4.6.4 Voltage Dependence: Chapter 4 DelayCarlos SaavedraNo ratings yet

- Circuit Extraction: CONNECT Layer1 Layer2Document1 pageCircuit Extraction: CONNECT Layer1 Layer2Carlos SaavedraNo ratings yet

- Circuit Elements: 3.4.3.1 CapacitorsDocument1 pageCircuit Elements: 3.4.3.1 CapacitorsCarlos SaavedraNo ratings yet

- Manufacturing Issues: Antenna RulesDocument1 pageManufacturing Issues: Antenna RulesCarlos SaavedraNo ratings yet

- CMOS Process Enhancements: Layer Rule Description 65 NM Rule (M) TABLE 3.1Document1 pageCMOS Process Enhancements: Layer Rule Description 65 NM Rule (M) TABLE 3.1Carlos SaavedraNo ratings yet

- Chapter 3 CMOS Processing Technology: 3.4.3.4 Transmission LinesDocument1 pageChapter 3 CMOS Processing Technology: 3.4.3.4 Transmission LinesCarlos SaavedraNo ratings yet

- CMOS VLSI Design 138Document1 pageCMOS VLSI Design 138Carlos SaavedraNo ratings yet

- 3.4.1.4 Higher Mobility: High-K Gate Stack TEM (© IEEE 2007.)Document1 page3.4.1.4 Higher Mobility: High-K Gate Stack TEM (© IEEE 2007.)Carlos SaavedraNo ratings yet

- Micron Design Rules: Chapter 3 CMOS Processing TechnologyDocument1 pageMicron Design Rules: Chapter 3 CMOS Processing TechnologyCarlos SaavedraNo ratings yet

- MOSIS Scalable CMOS Design RulesDocument1 pageMOSIS Scalable CMOS Design RulesCarlos SaavedraNo ratings yet

- CMOS VLSI Design 140Document1 pageCMOS VLSI Design 140Carlos SaavedraNo ratings yet

- Mask Summary: The Only Mask Involved With Contacts To Active or PolyDocument1 pageMask Summary: The Only Mask Involved With Contacts To Active or PolyCarlos SaavedraNo ratings yet

- Silicon Dioxide (Sio) : Well-Edge Proximity EffectDocument1 pageSilicon Dioxide (Sio) : Well-Edge Proximity EffectCarlos SaavedraNo ratings yet

- Mask Summary: The Masks Encountered For Well Specification May Include N-WellDocument1 pageMask Summary: The Masks Encountered For Well Specification May Include N-WellCarlos SaavedraNo ratings yet

- Gate and Source/Drain Formations: Chapter 3 CMOS Processing TechnologyDocument1 pageGate and Source/Drain Formations: Chapter 3 CMOS Processing TechnologyCarlos SaavedraNo ratings yet

- Gate Oxide: 3.2 CMOS TechnologiesDocument1 pageGate Oxide: 3.2 CMOS TechnologiesCarlos SaavedraNo ratings yet

- Chapter 3 CMOS Processing Technology: PassivationDocument1 pageChapter 3 CMOS Processing Technology: PassivationCarlos SaavedraNo ratings yet

- CMOS VLSI Design 128Document1 pageCMOS VLSI Design 128Carlos SaavedraNo ratings yet

- Isolation: Chapter 3 CMOS Processing TechnologyDocument1 pageIsolation: Chapter 3 CMOS Processing TechnologyCarlos SaavedraNo ratings yet

- CMOS Technologies: Chapter 3 CMOS Processing TechnologyDocument1 pageCMOS Technologies: Chapter 3 CMOS Processing TechnologyCarlos SaavedraNo ratings yet

- CMOS VLSI Design 126Document1 pageCMOS VLSI Design 126Carlos SaavedraNo ratings yet

- Cmos Vlsi Design 131Document1 pageCmos Vlsi Design 131Carlos SaavedraNo ratings yet

- SCT 50 N 120Document11 pagesSCT 50 N 120JaimeNo ratings yet

- IMET M880 GruEdili en Rev1 4Document7 pagesIMET M880 GruEdili en Rev1 4Enoch Allen AkeseNo ratings yet

- DVLSI ESA 2020 Solution (SSR) PDFDocument10 pagesDVLSI ESA 2020 Solution (SSR) PDFM Chandan ShankarNo ratings yet

- Ecd LR - 1Document21 pagesEcd LR - 1Faaran Ahmed Zaheer AhmedNo ratings yet

- Curriculumn & Syllabus B.tech. (ECE) 16 17Document46 pagesCurriculumn & Syllabus B.tech. (ECE) 16 17SRINIVASA RAONo ratings yet

- Transistor PDFDocument14 pagesTransistor PDFMuhammad JameelNo ratings yet

- Digital Logic FamiliesDocument28 pagesDigital Logic FamiliesRalphNo ratings yet

- Numerical Continuation Scheme For Tracing The Double Bounded Homotopy For Analysing Nonlinear CircuitsDocument5 pagesNumerical Continuation Scheme For Tracing The Double Bounded Homotopy For Analysing Nonlinear CircuitsCalavera BanderillaNo ratings yet

- AND9218/D 5 Key Steps To Designing A Compact, High Efficiency PFC Stage Using The NCP1602Document19 pagesAND9218/D 5 Key Steps To Designing A Compact, High Efficiency PFC Stage Using The NCP1602Jonatan LunaNo ratings yet

- MTP3055VDocument3 pagesMTP3055VJoel Batazar CruzNo ratings yet

- Mosfet: Device StructureDocument15 pagesMosfet: Device StructureNoorullah ShariffNo ratings yet

- Ee6301 DLLC Notes RejinpaulDocument104 pagesEe6301 DLLC Notes RejinpaulAnney RevathiNo ratings yet

- ARDUINO SOLAR CHARGE CONTROLLER Version 30Document79 pagesARDUINO SOLAR CHARGE CONTROLLER Version 30orli20041No ratings yet

- Vlsi QuestionsDocument36 pagesVlsi Questionshariprasada0No ratings yet

- A Study On Al2O3 Passivation in Gan Mos-Hemt by Pulsed StressDocument6 pagesA Study On Al2O3 Passivation in Gan Mos-Hemt by Pulsed Stressoğuz odabaşıNo ratings yet

- 8 Devendra Singh Kushwaha 1437 Review Article VSRDIJEEC March 2Document4 pages8 Devendra Singh Kushwaha 1437 Review Article VSRDIJEEC March 2satyasheels@gmail.comNo ratings yet

- 3 Vlsi Design (Elective III)Document1 page3 Vlsi Design (Elective III)Rohith Sai RohiNo ratings yet

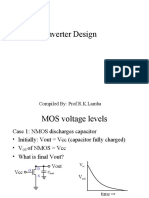

- Inverter Design: Compiled By: Prof.R.K.LambaDocument118 pagesInverter Design: Compiled By: Prof.R.K.LambaSamir TrivediNo ratings yet

- B7S65 DatasheetDocument7 pagesB7S65 Datasheetgumilao nelsonenclonar50% (2)

- FinfetDocument8 pagesFinfetRohith RajNo ratings yet

- Cmos Technology Scaling: Navakanta Bhat Associate Professor Ece Department, Iisc Ece Department, IiscDocument28 pagesCmos Technology Scaling: Navakanta Bhat Associate Professor Ece Department, Iisc Ece Department, Iiscabhijit_jamdadeNo ratings yet

- Power Solutions PDFDocument60 pagesPower Solutions PDFEngSampaio ManoelNo ratings yet

- Consonance: 4A, Standalone Li-Ion Battery Charger IC With Photovoltaic Cell MPPT Function CN3791Document11 pagesConsonance: 4A, Standalone Li-Ion Battery Charger IC With Photovoltaic Cell MPPT Function CN3791gpreviatoNo ratings yet

- P610 AOP610 É Um DUAL MOSFET CANAL N e P Com Diodos de Proteção-Driver de Inverter - LCD PDFDocument7 pagesP610 AOP610 É Um DUAL MOSFET CANAL N e P Com Diodos de Proteção-Driver de Inverter - LCD PDFKrista TranNo ratings yet

- Green-Mode PWM Controller With Frequency Swapping and Audio Noise PreventionDocument18 pagesGreen-Mode PWM Controller With Frequency Swapping and Audio Noise PreventionPaulo Roberto s freireNo ratings yet

- 20N50EDocument8 pages20N50EFernando SimãoNo ratings yet

- BP2866XJ: Non-Isolated Buck Offline LED Driver Description FeaturesDocument2 pagesBP2866XJ: Non-Isolated Buck Offline LED Driver Description FeaturesEo GpNo ratings yet

- History of SemiconductorsDocument14 pagesHistory of SemiconductorsSergio Andres Fajardo SaldarriagaNo ratings yet

- This Set of VLSI Multiple Choice QuestionsDocument20 pagesThis Set of VLSI Multiple Choice QuestionsSujith Mrinal100% (4)

- RD 15 HVF 1Document8 pagesRD 15 HVF 1zaxmavNo ratings yet