Gujarat Technological University

Gujarat Technological University

Uploaded by

prajapatidhnjCopyright:

Available Formats

Gujarat Technological University

Gujarat Technological University

Uploaded by

prajapatidhnjOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Gujarat Technological University

Gujarat Technological University

Uploaded by

prajapatidhnjCopyright:

Available Formats

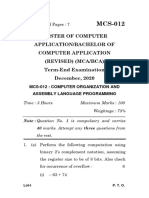

Seat No.: ________ Enrolment No.

___________

GUJARAT TECHNOLOGICAL UNIVERSITY

BE - SEMESTER– IV(NEW) EXAMINATION – SUMMER 2023

Subject Code:3140707 Date:13-07-2023

Subject Name:Computer Organization & Architecture

Time:10:30 AM TO 01:00 PM Total Marks:70

Instructions:

1. Attempt all questions.

2. Make suitable assumptions wherever necessary.

3. Figures to the right indicate full marks.

4. Simple and non-programmable scientific calculators are allowed.

Marks

Q.1 (a) Write the name of basic computer registers with their functionalities. 03

(b) Discuss 4-bit binary adder with neat diagram. 04

(c) Enlist various kinds of addressing modes. Explain any five of same and support 07

your answer by taking small example.

Q.2 (a) Write sequence of microoperations to execute the following instructions: 03

- AND

- STA

(b) Write assembly language program to subtract two numbers. 04

(c) Write two address, one address and zero address instructions program for the 07

following arithmetic expression:

X = (A + B) * (C – D / E) + F * G

OR

(c) Assume A = + 6 and B = + 7, apply Booth algorithm for multiplying A and B. 07

Make necessary assumptions if required.

Q.3 (a) Explain Flynn’s classification for computers in brief. 03

(b) Draw the flowchart for first pass of assembler and explain the same in brief. 04

(c) Elaborate CPU-IOP communication. 07

OR

Q.3 (a) Explain pipeline conflicts in brief. 03

(b) Discuss three state bus buffers with neat diagram. 04

(c) Write a detailed note on associative memory. 07

Q.4 (a) Explain DMA in brief. 03

(b) Write a note on SIMD array processor. 04

(c) A computer uses a memory unit with 256K words of 32 bits each. A binary 07

instruction code is stored in one word of memory. The instruction has four

parts: an indirect bit, an operation code, a register code part to specify one of 64

registers, and an address part.

1. How many bits are there in operation code, the register code part and the

address part?

2. Draw the instruction word format and indicate the number of bits in

each part.

3. How many bits are there in the data and address inputs of the memory?

OR

Q.4 (a) Write a brief note on memory hierarchy. 03

(b) In certain scientific computations it is necessary to perform the arithmetic 04

1

operation (Ai + Bi) * (Ci + Di) with a stream of numbers. Specify pipeline

configuration to carry out this task. List the contents of all registers in the

pipeline for i=1 through 4.

(c) Discuss microprogrammed control organization with neat diagram. 07

Q.5 (a) Perform A – B (subtract) operation for the following numbers using signed 03

magnitude number format. (Write necessary assumptions if required)

A = + 11 and B = - 6

(b) Explain status bit conditions with neat diagram. 04

(c) Discuss cache coherence problem in detail. 07

OR

Q.5 (a) Write the difference(s) between arithmetic shift left and logical shift left 03

instruction. Support your answer with proper illustration.

(b) State the differences between RISC and CISC. 04

(c) Explain any two types of mapping procedures when considering the 07

organization of cache memory.

*******************

You might also like

- Gujarat Technological UniversityDocument14 pagesGujarat Technological University220170107139No ratings yet

- S23 COA - MergedDocument7 pagesS23 COA - Mergedgojoo.saatoruNo ratings yet

- Syllabus 2paperDocument5 pagesSyllabus 2paperdev07panchalNo ratings yet

- Gtu 4th It Question PaperDocument38 pagesGtu 4th It Question Papercomputer myNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityOm Patel PatelNo ratings yet

- Be Summer 2021Document2 pagesBe Summer 2021Chandresh KanzariyaNo ratings yet

- Be Summer 2020Document2 pagesBe Summer 2020Chandresh KanzariyaNo ratings yet

- Gtu 4th It Question PaperDocument19 pagesGtu 4th It Question Papercomputer myNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityprajapatidhnjNo ratings yet

- Be Winter 2022Document2 pagesBe Winter 2022shah mananNo ratings yet

- Gujarat Technological UniversityDocument1 pageGujarat Technological UniversityPatel SarthakNo ratings yet

- 2170701Document2 pages2170701rinkalNo ratings yet

- GTU CO PaperDocument2 pagesGTU CO PaperVishal TailorNo ratings yet

- Gujarat Technological UniversityDocument3 pagesGujarat Technological UniversitypatelNo ratings yet

- DSD w20dsd GtuDocument1 pageDSD w20dsd GtuSandeep kumarNo ratings yet

- Computer Organization) 01CE0402: Enroll. No.Document4 pagesComputer Organization) 01CE0402: Enroll. No.nkrj34nNo ratings yet

- Q.1 Short Questions 14Document2 pagesQ.1 Short Questions 14gobinathNo ratings yet

- S2019-2140707-APY MaterialDocument1 pageS2019-2140707-APY MaterialRutvi MasalawalaNo ratings yet

- Compiler design-BE-WINTER-2020Document2 pagesCompiler design-BE-WINTER-2020Ankita AshalNo ratings yet

- PdfsDocument2 pagesPdfsßrijesh PatelNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological Universityprachi patelNo ratings yet

- Gujarat Technological UniversityDocument1 pageGujarat Technological Universityvifaket581No ratings yet

- C0-R4.B4 Page 1 of 2 January, 2019 (6+6+6)Document2 pagesC0-R4.B4 Page 1 of 2 January, 2019 (6+6+6)sanjay sheeNo ratings yet

- DE - S2023 (3131704) (GTURanker - Com)Document2 pagesDE - S2023 (3131704) (GTURanker - Com)pkrish0725No ratings yet

- MCS 012dec22Document4 pagesMCS 012dec22kk2760057No ratings yet

- Be Winter 2020Document2 pagesBe Winter 2020Chihaya FuruNo ratings yet

- OSW2022Document1 pageOSW2022Sarvaiya Digvijaysinh RameshsinhNo ratings yet

- 2020DECDocument7 pages2020DECAnupam GyawaliNo ratings yet

- New Microsoft Word DocumentDocument7 pagesNew Microsoft Word Documentpy2180333No ratings yet

- System Programming Question Paper GTUDocument2 pagesSystem Programming Question Paper GTUArpit SoniNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological Universityuttekarharshad85No ratings yet

- Amsum 2023Document1 pageAmsum 2023you.your.inspirationNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityKetan PatelNo ratings yet

- 1916eid 203Document2 pages1916eid 203Vamshidhar ReddyNo ratings yet

- Ce 419Document4 pagesCe 419all workNo ratings yet

- Be Summer 2022Document1 pageBe Summer 2022Drashti BabariyaNo ratings yet

- MCS 202Document6 pagesMCS 202pramod kumar yadavNo ratings yet

- DeDocument2 pagesDeUrvishNo ratings yet

- DS Question Papers (2009 To 2023)Document63 pagesDS Question Papers (2009 To 2023)Hiragar HarshilNo ratings yet

- Gtu Computer 3130704 Summer 2023Document2 pagesGtu Computer 3130704 Summer 2023madhavjani06No ratings yet

- Be Winter 2021Document2 pagesBe Winter 2021Raj SutharNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityJaineshNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityKetan PatelNo ratings yet

- Enroll. No. - : Marwadi UniversityDocument5 pagesEnroll. No. - : Marwadi Universitynkrj34nNo ratings yet

- B. C. A. (Fifth Semester) EXAMINATION, 2016-17: Note: All Questions Have To Be Attempted. Section-ADocument3 pagesB. C. A. (Fifth Semester) EXAMINATION, 2016-17: Note: All Questions Have To Be Attempted. Section-ARajeev GairolaNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversitymtbhoyeNo ratings yet

- Gujarat Technological UniversityDocument5 pagesGujarat Technological UniversitypatelNo ratings yet

- (NagpurStudents - Org) Computer Architecture and Organization 1Document4 pages(NagpurStudents - Org) Computer Architecture and Organization 1Saurabh GhuteNo ratings yet

- Mca 1 Sem Computer Organization and Architecture Rca104 2019Document2 pagesMca 1 Sem Computer Organization and Architecture Rca104 2019sandeepsm321No ratings yet

- Answer Any Two Full Questions, Each Carries 15 Marks: Reg No.: - NameDocument2 pagesAnswer Any Two Full Questions, Each Carries 15 Marks: Reg No.: - NameAmal Chandran MVNo ratings yet

- Be Summer 2020Document2 pagesBe Summer 2020surbhianiyaliya1108No ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological Universityypgcloud1No ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological Universityfeyayel988No ratings yet

- MCS 012Document4 pagesMCS 012trial versionNo ratings yet

- CT 801 / CSE802 - Compiler ConstructionDocument12 pagesCT 801 / CSE802 - Compiler ConstructionSumit PaulNo ratings yet

- PPS - W2022 (3110003) (GTURanker - Com)Document2 pagesPPS - W2022 (3110003) (GTURanker - Com)Faisal KhanNo ratings yet

- Computer Organization and Design (CSE-201) (Makeup)Document2 pagesComputer Organization and Design (CSE-201) (Makeup)damoy28211No ratings yet

- Summer 2023Document1 pageSummer 2023TusharNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityZack ThakorNo ratings yet

- Attainable Region Theory: An Introduction to Choosing an Optimal ReactorFrom EverandAttainable Region Theory: An Introduction to Choosing an Optimal ReactorNo ratings yet

- Ruggedcom RM1224 DatasheetDocument6 pagesRuggedcom RM1224 DatasheetAstrid Marin PalaciosNo ratings yet

- AI - ML AssignmentDocument2 pagesAI - ML AssignmentThomas ShelbyNo ratings yet

- Final Project Report of LabDocument7 pagesFinal Project Report of LabDuniya ANo ratings yet

- Get The Deal Here: NOW R16 999Document4 pagesGet The Deal Here: NOW R16 999Lincoln ColtmanNo ratings yet

- End-Term Exam - Quantitative Techniques IIDocument3 pagesEnd-Term Exam - Quantitative Techniques IIAshish TiwariNo ratings yet

- IGS NT Communication Guide 5Document157 pagesIGS NT Communication Guide 5Belghennou Hadj AliNo ratings yet

- An4938 Getting Started With Stm32h74xig and Stm32h75xig Hardware Development Stmicroelectronics PDFDocument47 pagesAn4938 Getting Started With Stm32h74xig and Stm32h75xig Hardware Development Stmicroelectronics PDFMax INo ratings yet

- Nikolai Ryskov: About The ArtistDocument2 pagesNikolai Ryskov: About The Artista.irin100% (1)

- Artificial Neural Network Part-2Document15 pagesArtificial Neural Network Part-2Zahid JavedNo ratings yet

- Python Day20Document17 pagesPython Day20ankur881120No ratings yet

- Buku Kenangan Pamilwa 922Document105 pagesBuku Kenangan Pamilwa 922Eddy MappaNo ratings yet

- Nutanix Study Notes (Part 3) - InfraPCSDocument9 pagesNutanix Study Notes (Part 3) - InfraPCSVijayenNNo ratings yet

- Telephone Directory FinalDocument38 pagesTelephone Directory FinalUdesh SiriwardhanaNo ratings yet

- 196 - Creating and Managing Users and GroupsDocument13 pages196 - Creating and Managing Users and GroupsPrem ChandNo ratings yet

- Communications Planning TemplateDocument7 pagesCommunications Planning TemplateInes Benvenutta KhoziNo ratings yet

- Quotation For 05 KW OFF GRID:: Quotation Date: 18 May, 2021 Unit Price (RS.) Quantity Total Cost (RS.)Document2 pagesQuotation For 05 KW OFF GRID:: Quotation Date: 18 May, 2021 Unit Price (RS.) Quantity Total Cost (RS.)ImranFazal100% (1)

- Predicting Autism Spectrum Disorder Using Machine Learning ClassifiersDocument4 pagesPredicting Autism Spectrum Disorder Using Machine Learning Classifiersahfn79No ratings yet

- 2017 Filipponi Et Al MultiTemp2017 WatermarkDocument9 pages2017 Filipponi Et Al MultiTemp2017 WatermarkDaniel Mateo Rangel ReséndezNo ratings yet

- Large Scale Apps With Svelte and TypeScript by DamDocument273 pagesLarge Scale Apps With Svelte and TypeScript by DamTran quoc Huy100% (1)

- SAP ABAP Central - RFC Gateway Security, Part 1 - Basic UnderstandingDocument5 pagesSAP ABAP Central - RFC Gateway Security, Part 1 - Basic UnderstandingFahri BaturNo ratings yet

- CWL Limit SwitchDocument3 pagesCWL Limit SwitchHandrêa SilvaNo ratings yet

- REPORTDocument5 pagesREPORTgomathi.shankarNo ratings yet

- 2015BCC Grade 7 - 8 (Solutions)Document37 pages2015BCC Grade 7 - 8 (Solutions)pjNo ratings yet

- 02 EPA EP72 GL 0052 Underwater Services Equipment SpecificationDocument94 pages02 EPA EP72 GL 0052 Underwater Services Equipment Specificationvijuindia1111No ratings yet

- DFMAPaper FullDocument13 pagesDFMAPaper FullahasimplemailNo ratings yet

- Eclipse Tutorial4Document11 pagesEclipse Tutorial4Cara BakerNo ratings yet

- Mix Uc3 & Uc8: Mix Boilers Sample Set-UpDocument3 pagesMix Uc3 & Uc8: Mix Boilers Sample Set-UpUmut GökdenizNo ratings yet

- DC Q BankDocument6 pagesDC Q BankSamarth UrankarNo ratings yet

- Research Methodology in Raid and TailorDocument12 pagesResearch Methodology in Raid and TailorShahzad SaifNo ratings yet

- Solar Electric Wheel ChairDocument4 pagesSolar Electric Wheel ChairInternational Journal of Innovative Science and Research TechnologyNo ratings yet