Principles of VLSI Tests

Uploaded by

Raghavan NagarajanPrinciples of VLSI Tests

Uploaded by

Raghavan NagarajanUmm Al-Qura University 1423/1424

Faculty of Engineering Subject: VLSI Design

Department of Computer Engineering 1

st

Midterm Exam

Answer the following questions: Time allowed: 1 (one) Hour

1. Aided with neat sketches, show the circuit of fabrication process of the twin-tub

shown in figure.

2. Illustrate the typical processing steps with the needed masks.

Best Wishes Prof. Dr. Kadry

Montasser

Umm Al-Qura University 1423/1424

Faculty of Engineering Subject: VLSI Design

Department of Computer Engineering 1

st

Midterm Exam

Answer the following questions: Time allowed: 1 (one) Hour

2. Aided with neat sketches, show the circuit of fabrication process of the twin-tub

shown in figure.

2. Illustrate the typical processing steps with the needed masks.

Best Wishes Prof. Dr.

Kadry Montasser

Umm Al-Qura University 1423/1424

Faculty of Engineering Subject: VLSI Design

Department of Computer Engineering 2

nd

Midterm Exam

Answer the following questions: Time allowed: 1 (one) Hour

1)a-Design an nMos enhancement transistor, as in Fig. (1); driving 1.8 mA in the drain

and a voltage difference between drain and source of 4.8 V. Assume R

D

= R

S

= 2kO,

R

1

= 100 kO, R

2

= 300 kO.

b- Deduce the new value of R

S

needed to maintain I

D

as in (a) if W/L become 6

and 1/6.

___________________________________________________________________________

2) An off chip capacitance load of 5 pF is to be driven from (a) CMOS and (b) nMOS

inverters. Set up suitable arrangements giving appropriate channel L:W ratios and

dimensions. Calculate the number of inverter stages required, and the delay exhibited

by the overall arrangement driving the 5 pF load.

___________________________________________________________________________

3) Calculate area capacitance values for the structure represented in Fig. (2).

Fig. (1)

Fig. (2)

Best Wishes Prof. Dr.

Kadry Montasser

Umm Al-Qura University 1423/1424 (2

nd

Term)

Faculty of Engineering Subject: VLSI Design

Department of Computer Engineering Final Exam

Answer the following questions: Time allowed: 2 (Two) Hours

1) Consider the circuit given in Fig. (1):

a- Draw a side view of the structure for the given circuit,

b- Illustrate the typical processing steps with the needed masks.

___________________________________________________________________________

2)a- Determine the pull-up to pull-down ratio (Z

p.u.

/Z

p.d.

) for an nMOS inverter driven by

another nMOS inverter.

b- Consider the complementary transistor pull-up (CMOS) given in Fig. (2):

i) draw and explain its transfer characteristic and inverter current versus

V

in

,

ii) prove that the width to length of the p-device is to be two to three times

that of the n-

device.

___________________________________________________________________________

3)a- Calculate Cin and Cout values for the structure represented in Fig. (3).

b-Two nMOS inverters are cascaded to drive a capatitive load C

L

= 12 C

g

, as shown in

Fig. (4). Calculate the pair delay (V

in

/V

out

) in terms of t for the inverter geometry

indicated in the given figure. What are the ratios of each inverter?

If strays and wiring are allowed for, it would be reasonable to increase the capacitance

to ground across the output of each inverter by 3 C

g

. What is the pair delay allowing

for strays?

Assume a suitable value for t and evaluate this pair delay.

___________________________________________________________________________

4) a- Discuss the salient features of GaAs technology.

b- Compare between CMOS, bipolar and GaAs technologies.

c- Give a brief description of MESFET transistor

Fig. (1) Fig. (2)

Fig. (3) Fig. (4)

Best Wishes Prof. Dr.

Kadry Montasser

.

Umm Al-Qura University 1424/1425

Faculty of Engineering Subject: VLSI

Department of Computer Engineering 2

nd

Midterm Exam

Answer the following questions: Time allowed: 1 (one) Hour

1) An off chip capacitance load of 5 pF is to be driven from (a) CMOS and (b) nMOS

inverters. Set up suitable arrangements giving appropriate channel L:W ratios and

dimensions. Calculate the number of inverter stages required, and the delay exhibited

by the overall arrangement driving the 5 pF load.

___________________________________________________________________________

2) Calculate area capacitance values for the structure represented in Fig. (1).

___________________________________________________________________________

3) Two nMOS inverters are cascaded to drive a capatitive load C

L

= 12 C

g

, as shown in

Fig. (2). Calculate the pair delay (V

in

/V

out

) in terms of t for the inverter geometry

indicated in the given figure. What are the ratios of each inverter?

If strays and wiring are allowed for, it would be reasonable to increase the capacitance

to ground across the output of each inverter by 3 C

g

. What is the pair delay allowing

for strays?

Assume a suitable value for t and evaluate this pair delay.

Fig. (1)

Fig. (2)

Best Wishes Prof. Dr.

Kadry Montasser

Umm Al-Qurah University 1424/1425 (2

nd

Term)

Faculty of Engineering Subject: Principles of VLSI Design

Department of Computer Engineering 1

st

Midterm Exam

Answer the following questions: Time allowed: 1 (one) Hour

1)a- Explain briefly, from a qualitative viewpoint; the processing steps of VLSI.

b- A resistor is constructed as shown in figure. If Rs= 45 O/ , determine the nominal value

of this resistor.

2)The nMOS transistor given in Figure has: k= 0.3 mA/V

2

, W=8 m, L= 4 m, V

T

= -2V,

c

in

= 4,

n

= 650 cm

2

/V sec, V

ds

= 4.8 V. The supply voltage is 12 V, R

D

=R

S

= 5 kO, R

1

= 150

kO, R

2

= 250 kO.

Find: a- The mode of operation of the transistor,

b- V

gs

and I

D

b- The transistor transconductance gm

c- The gate/ channel capacitance

d- The transistor figure of merit e

o

___________________________________________________________________________

3) a- Determine the pull-up to pull-down ratio (Z

p.u

/Z

p.d

) for an nMOS inverter driven

through one or more pass transistors.

b- Compare the relative merits of three different forms of pull-up for an inverter circuit.

What is the best choice for realization in (a) nMOS technology? (b) CMOS technology.

__________________________________________________________________________

Best Wishes Prof. Dr. Kadry Montasser

Umm Al-Qurah University 1424/1425 (2

nd

Term)

Faculty of Engineering Subject: Principles of VLSI

Design

Department of Computer Engineering 1

st

Midterm Exam

Answer the following questions: Time allowed: 1 (one) Hour

1)

2)The nMOS transistor given in Figure has: k= 0.3 mA/V

2

, W=8 m, L= 4 m, V

T

= -2V,

c

in

= 4,

n

= 650 cm

2

/V sec, V

ds

= 4.8 V. The supply voltage is 12 V, R

D

=R

S

= 5 kO, R

1

= 150

kO, R

2

= 250 kO.

Find: a- The mode of operation of the transistor,

b- V

gs

and I

D

b- The transistor transconductance gm

c- The gate/ channel capacitance

d- The transistor figure of merit e

o

___________________________________________________________________________

3) a- Determine the pull-up to pull-down ratio (Z

p.u

/Z

p.d

) for an nMOS inverter driven through

one or more pass transistors.

b- Compare the relative merits of three different forms of pull-up for an inverter circuit.

What is the best choice for realization in (a) nMOS technology? (b) CMOS technology.

__________________________________________________________________________

Best Wishes Prof. Dr. Kadry Montasser

Umm Al-Qurah University 1424/1425 (2

nd

Term)

Faculty of Engineering Subject: Principles of VLSI Design

Department of Computer Engineering 2

nd

Midterm Exam

Attempt the following questions: Time allowed: 1 Hours

1) An off chip capacitance load of 8 pF is to be driven from (a) CMOS and (b) nMOS

inverters. Set up suitable arrangements giving appropriate channel L:W ratios and

dimensions. Calculate the number of inverter stages required, and the delay exhibited

by the overall arrangement driving the 8 pF load.

___________________________________________________________________________

2) Calculate area capacitance values for the structure represented in Fig. (1).

___________________________________________________________________________

3) Assume that in Fig. (2) W = 5 , R

= 45 O/ for both poly layers, determine the

nominal value of resistance between nodes A and B.

___________________________________________________________________________

4) Two nMOS inverters are cascaded to drive a capatitive load C

L

= 12 C

g

, as shown in

Fig. (3). Calculate the pair delay (V

in

/V

out

) in terms of t for the inverter geometry

indicated in the given figure. What are the ratios of each inverter?

If strays and wiring are allowed for, it would be reasonable to increase the capacitance

to ground across the output of each inverter by 3 C

g

. What is the pair delay allowing

for strays? Assume a suitable value for t and evaluate this pair delay.

Fig. (1) Fig. (2)

Fig. (3)

_______________________________________________________________________

Best Wishes Prof. Dr. Kadry Montasser

Umm Al-Qura University 1424/1425 (2

nd

Term)

Faculty of Engineering Subject: VLSI Design

Department of Computer Engineering Final Exam

Answer the following questions: Time allowed: 2 (Two) Hours

1) A n-channel enhancement MOSFET having K = 100 A/V

2

and V

t

= +1 V is operating

with V

S

= 0 and V

G

= 3 V. For what range of voltages V

DS

, on the drain is operation in

the non-saturated region? What current flows for V

DS

= 4 V? 2 V? 1 V? 0.5 V? What is

the value of r

DS

for V

DS

relatively small?

___________________________________________________________________________

2)a- Compare between the deposition and etching as two processing steps in VLSI

technology.

b- Consider the complementary transistor pull-up (CMOS) given in Fig. (1):

i) draw and explain its transfer characteristic and inverter current versus V

in

,

ii) prove that the width to length of the p-device is to be two to three times that of the

n-device.

___________________________________________________________________________

3)a- Determine the pull-up to pull-down ratio (Z

p.u

/Z

p.d

) for an nMOS inverter driven

by another nMOS inverter .

b- Compare the relative merits of three different forms of pull-up for an inverter circuit.

What is the best choice for realization in (i) nMOS technology, (ii) CMOS technology.

___________________________________________________________________________

4)a- Calculate area capacitance values for the structure represented in Fig. (2).

b- Discuss the advantages of using BiCMOS drivers, concentrate on the delay estimation.

___________________________________________________________________________

Fig. (1) Fig. (2)

___________________________________________________________________________

Best Wishes Prof. Dr. Kadry Montasser

Umm Al-Qurah University 1425/1426 (2

nd

Term)

Faculty of Engineering Subject: Principles of VLSI Design

Department of Computer Engineering 1

st

Midterm Exam

Answer the following questions: Time allowed: 1 (one) Hour

1) A n-channel enhancement MOSFET having K = 100 A/V

2

and V

t

= +1 V is operating

with V

S

= 0 and V

G

= 3 V. For what range of voltages V

DS

, on the drain is operation in

the non-saturated region? What current flows for V

DS

= 4 V? 2 V? 1 V? 0.5 V? What is

the value of r

DS

for V

DS

relatively small?

2) Consider the complementary transistor pull-up (CMOS) given in Fig. (1):

i) draw and explain its transfer characteristic and inverter current versus V

in

,

ii) prove that the width to length of the p-device is to be two to three times that

of the n-device.

3) Design a complementary logic circuit for F(ABCD) = (0,2,4,5,6,7,8,10,13,15). Note

that this expression indicates the minterms of the logic function F.

________________________________________________________________________

4) Differentiate between the static loads that may be used for MOS inverters. Write your

opinion about the best to be used.

5) For the circuit given in Fig. (2):

a- Draw the equivalent complementary logic gate circuit,

b- Identify the funcion of the circuit by writing the function z.

Fig. (1)

Fig. (2)

Best Wishes Prof. Dr. Kadry Montasser

Umm Al-Qurah University 1425/1426 (2

nd

Term)

Faculty of Engineering Subject: Principles of VLSI Design

Department of Computer Engineering 2

nd

Midterm Exam

Answer the following questions: Time allowed: 1 Hours

1) a-Design an nMos enhancement transistor, as in Fig. (1); driving 1.8 mA in the drain

and a voltage difference between drain and source of 4.8 V. Assume R

D

= R

S

= 2kO,

R

1

= 100 kO, R

2

= 300 kO.

b- Deduce the new value of R

S

needed to maintain I

D

as in (a) if W/L become 6 and 1/6.

2) Design a complementary logic circuit for F(ABCD) = (0,3,4,,6,7,8,11,12,14). Note

that this expression indicates the minterms of the logic function F.

3) Two nMOS inverters are cascaded to drive a capatitive load C

L

= 12 C

g

, as shown in

Fig. (2). Calculate the pair delay (V

in

/V

out

) in terms of t for the inverter geometry

indicated in the given figure. What are the ratios of each inverter?

4) Assume that in Fig.(3): W = 5 , R

= 45 O/ for both poly layers, determine the nominal

value of resistance between nodes A and B.

5) In Fig. (4), two inputs X and Y are to enter in parallel. Calculate area capacitance value at

the output O/P.

Fig. (1) Fig. (2)

Fig.(3) Fig. (4)

Best Wishes Prof. Dr. Kadry Montasser

Umm Al-Qurah University 1425/1426 (2

nd

Term)

Faculty of Engineering Subject: Principles of VLSI Design

Department of Computer Engineering Final Exam

Answer the following questions: Time allowed: 2 Hours

1)The nMOS transistor given in Fig. (1) has: k= 0.3 mA/V

2

, W=8 m, L= 4 m, V

T

= -2V,

c

in

= 4,

n

= 650 cm

2

/V sec, V

ds

= 4.8 V. The supply voltage is 12 V, R

D

=R

S

= 5 kO, R

1

= 150

kO, R

2

= 250 kO.

Find: a- The mode of operation of the transistor,

b- V

gs

and I

D

c- The transistor transconductance gm

2) Design a complementary logic circuit for F(ABCD) = (0,3,4,,6,7,8,11,12,14). Note

that this expression indicates the minterms of the logic function F.

3) An off chip capacitance load of 5 pF is to be driven from (a) CMOS and (b) nMOS

inverters. Set up suitable arrangements giving appropriate channel L:W ratios and

dimensions. Calculate the number of inverter stages required, and the delay

exhibited by the overall arrangement driving the 5 pF load.

4) Assume that in Fig.(2): W = 5 , R

= 45 O/ for both poly layers, determine the

nominal value of this resistor.

5) In Fig. (3), two inputs X and Y are to enter in parallel. Calculate area capacitance

value at the output O/P.

Fig. (1) Fig. (2)

Fig.(3)

Best Wishes Prof. Dr. Kadry Montasser

Umm Al-Qurah University 1426/1427 (2

nd

Term)

Faculty of Computer& Information Systems Subject: Principles of VLSI Design

Department of Computer Engineering 1

st

Midterm Exam

Attempt the following questions: Time allowed: 1 Hours

1) A n-channel enhancement MOSFET having K = 100 A/V

2

and V

t

= +1 V is operating

with V

S

= 0 and V

G

= 3 V. For what range of voltages V

DS

, on the drain is operation in

the non-saturated region? What current flows for V

DS

= 4 V? 2 V? 1 V? 0.5 V? What is

the value of r

DS

for V

DS

relatively small?

2) Consider the complementary transistor pull-up (CMOS), given in figure:

i)draw and explain its transfer characteristic and inverter current versus V

in

,

ii)prove that the width to length of the p-device is to be two to three times that of

the n-device.

3) Design a complementary logic circuit for F(ABCD) = (0,2,4,5,6,7,8,10,13,15). Note

that this expression indicates the minterms of the logic function F.

________________________________________________________________________

4) Differentiate between the static loads that may be used for MOS inverters. Write your

opinion about the best to be used.

5)a-Aided with neat sketches, show the circuit of fabrication process of the twin-tub

shown in figure.

b- Illustrate the typical processing steps with the needed masks.

Best Wishes Prof. Dr. Kadry Montasser

Umm Al-Qura University 1426/1427 (2

nd

Term)

Faculty of Engineering Subject: VLSI Design

Department of Computer Engineering 2

nd

Midterm Exam

Answer the following questions: Time allowed: 1 (one) Hour

1) An off chip capacitance load of 12 pF is to be driven from (a) CMOS and (b) nMOS

inverters. Set up suitable arrangements giving appropriate channel L:W ratios and

dimensions. Calculate the number of inverter stages required, and the delay exhibited

by the overall arrangement driving the 8pF load.

2) Determine the pull-up to pull-down ratio (Z

p.u

/Z

p.d

) for an nMOS inverter driven through

one or more pass transistors

3) Two nMOS inverters are cascaded to drive a capatitive load C

L

= 12 C

g

, as shown in

Fig. (2). Calculate the pair delay (V

in

/V

out

) in terms of t for the inverter geometry

indicated in the given figure. What are the ratios of each inverter?

4) In Fig. (4), two inputs X and Y are to enter in parallel. Calculate the total delay at the

output O/P.

Best Wishes Prof. Dr. Kadry Montasser

Umm Al-Qurah University 1426/1427 (2

nd

Term)

Faculty of Computer& Information Systems Subject: Principles of VLSI Design

Department of Computer Engineering Final Exam

Attempt the following questions: Time allowed: 2 Hours

1) Consider the circuit given in Fig. (1).

a- Draw a side view of the structure for the given circuit,

b- Illustrate the typical processing steps with the needed masks.

___________________________________________________________________________

2)a- For a CMOS inverter, calculate the shift in the transfer characteristic when the |

n

/|

p

ratio is varied from 1/1 to 10/1.

b-The nMOS transistor given in Fig. (2) has: k= 0.3 mA/V

2

, W=8 m, L= 4 m, V

T

= -2V,

c

in

= 4,

n

= 650 cm

2

/V sec, V

ds

= 4.8 V. The supply voltage is 12 V, R

D

=R

S

= 5 kO, R

1

=

150 kO, R

2

= 250 kO.

Find: a- The mode of operation of the transistor,

b- V

gs

and I

D

c- The transistor transconductance gm

d- The gate/ channel capacitance

e- The transistor figure of merit e

o

Fig. (1) Fig. (2)

__________________________________________________________________________

3) a- Derive an expression for the pull-up to pull-down ratio (Z

p.u.

/Z

p.d.

) for an nMOS inverter

driven by another nMOS inverter.

b- Design a complementary logic circuit for F(ABCD) = (0,2,4,,7,8,9,11,12,15). Note

that this expression indicates the minterms of the logic function F.

___________________________________________________________________________

4) a- Derive an expression for the CMOS inverter delay by estimating both the rise and delay

times.

b- In Fig. (3), two inputs X and Y are to enter in parallel. Calculate the delay occurring on

a pulse entering:

i) at only input X;

ii) at only input Y.

.

Fig.(3)

Best Wishes Prof. Dr. Kadry Montasser

Umm Al-Qura University 1427/1428 (2

nd

Term)

Faculty of Engineering Subject: Priniples of VLSI Design

Department of Computer Engineering 1

st

MidTerm Exam

Answer the following questions: Time allowed: 1 (One) Hour

1) Consider the circuit given in Fig. (1):

a- Draw a side view of the structure for the given circuit,

b- Illustrate the typical processing steps with the needed masks.

___________________________________________________________________________

2)a- Determine the pull-up to pull-down ratio (Z

p.u

/Z

p.d

) for an nMOS inverter driven through

one or more pass transistors.

b- Design a complementary logic circuit for F(ABCD) = (0,2,4,,7,8,9,11,12,15). Note

that this expression indicates the minterms of the logic function F.

___________________________________________________________________________

3) The nMOS transistor given in Fig.(2) has: k= 0.3 mA/V

2

, W=8 m, L= 4 m, V

T

= -2V,

c

in

= 4,

n

= 650 cm

2

/V sec, V

ds

= 4.8 V. The supply voltage is 12 V, R

D

=R

S

= 5 kO, R

1

= 150

kO, R

2

= 250 kO.

Find: a- The mode of operation of the transistor,

b- V

gs

and I

D,

c- The transistor transconductance gm,

d- The gate/ channel capacitance,

e- The transistor figure of merit e

o

.

___________________________________________________________________________

Fig. (1) Fig. (2)

Best Wishes Prof. Dr.

Kadry Montasser

Umm Al-Qura University 1427/1428 (2

nd

Term)

Faculty of Engineering Subject: VLSI Design

Department of Computer Engineering 2

nd

Midterm Exam

Answer the following questions: Time allowed: 1 (one) Hour

1) Consider the complementary transistor pull-up (CMOS), given in Fig. 1:

i)draw and explain its transfer characteristic and inverter current versus V

in

,

ii)prove that the width to length of the p-device is to be two to three times that of

the n-device.

2) Differentiate between the static loads that may be used for MOS inverters. Write your

opinion about the best to be used.

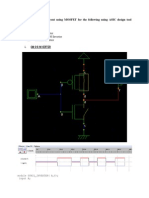

3) In Fig. 2, two inputs X and Y are to enter in parallel. Calculate the total delay at the

output O/P.

Fig. 1 Fig. 2

Best Wishes Prof. Dr. Kadry Montasser

Umm Al-Qura University 1427/1428 (2

nd

Term)

Faculty of Engineering Subject: VLSI Design

Department of Computer Engineering 2

nd

Midterm Exam

Answer the following questions: Time allowed: 1 (one) Hour

1) Consider the complementary transistor pull-up (CMOS), given in Fig. 1:

i)draw and explain its transfer characteristic and inverter current versus V

in

,

ii)prove that the width to length of the p-device is to be two to three times that of

the n-device.

2) Differentiate between the static loads that may be used for MOS inverters. Write your

opinion about the best to be used.

3) In Fig. 2, two inputs X and Y are to enter in parallel. Calculate the total delay at the

output O/P.

Fig. 1 Fig. 2

Best Wishes Prof. Dr. Kadry Montasser

Umm Al-Qurah University 1427/1428 (2

nd

Term)

Faculty of Computer& Information Systems Subject: Principles of VLSI Design

Department of Computer Engineering Final Exam

Answer only 4 (four) questions: Time allowed: 2 Hours

1) For the circuit given in Fig. (1), draw the corresponding side view.

___________________________________________________________________________

2) a- Derive expressions for MOS transistor transconductance g

m

and output conductance g

ds

.

b- A n-channel enhancement MOSFET having K = 200 A/V

2

and V

t

= +2 V is

operating with V

S

= 0 and V

G

= 4 V. For what range of voltages V

DS

, on the drain is

operation in the non-saturated region? What current flows for V

DS

= 6 V? 4 V? 2 V?

1 V? What is the value of r

DS

for V

DS

relatively small?

___________________________________________________________________________

_______________

3) a- Derive an expression for the pull-up to pull-down ratio (Z

p.u.

/Z

p.d.

) for an nMOS inverter

driven through one or more pass transistors.

b- Design a complementary logic circuit for F(ABCD) = (0,2,3,4,5,8,10,11,12,13). Note

that this expression indicates the minterms of the logic function F.

___________________________________________________________________________

4)a- Derive an expression for the CMOS inverter total delay by estimating both the rise and

delay times.

b- An off chip capacitance load of 10 pF is to be driven from (a) CMOS and (b) nMOS

inverters. Set up suitable arrangements giving appropriate channel L:W ratios and

dimensions. Calculate the number of inverter stages required, and the delay exhibited

by the overall arrangement driving the 10 pF load. Consider 2- technology.

___________________________________________________________________________

5) Calculate the total delay occurring on a pulse entering the input for Fig. (2).

.

Page 220

Fig. (1) Fig. (2)

Best Wishes Prof. Dr. Kadry Montasser

Umm Al-Qura University 1428/1429 (1

st

Term)

Faculty of Engineering Subject: Principles of VLSI Design

Department of Computer Engineering 1

st

MidTerm Exam

Answer the following questions: Time allowed: 1 (one) Hour

1) Consider the circuit given in Fig. (1):

a- Draw a side view of the structure for the given circuit,

b- Illustrate the typical processing steps with the needed masks.

___________________________________________________________________________

2) a- Derive an expression for the pull-up to pull-down ratio (Z

p.u.

/Z

p.d.

) for an nMOS inverter

driven through one or more pass transistors.

b- Consider the complementary transistor pull-up (CMOS) given in Fig. (2):

i- draw and explain its transfer characteristic and inverter current versus V

in

,

ii- prove that the width to length of the p-device is to be two to three times that of the

n-device.

___________________________________________________________________________

3) The nMOS transistor given in Fig. (3) has: k= 0.3 mA/V

2

, W=8 m, L= 4 m, V

T

= -2V,

c

in

= 4,

n

= 650 cm

2

/V sec, V

ds

= 3.6 V. The supply voltage is 12 V, R

D

=R

S

= 6 kO, R

1

= 200

kO, R

2

= 300 kO.

Find: a- The mode of operation of the transistor,

b- V

gs

and I

D,

c- The transistor transconductance gm,

d- The gate/ channel capacitance,

e- The transistor figure of merit e

o

.

Fig. (1) Fig. (2) Fig. (3)

___________________________________________________________________________

Best Wishes Prof. Dr. Kadry Montasser

Umm Al-Qurah University 1428/1429 (1st Term)

Faculty of Computer& Information Systems Subject: Principles of VLSI Design

Department of Computer Engineering Final Exam

Answer ONLY 4(four) questions: Time allowed: 2 Hours

1) Consider the circuit given in Fig. (1):

c- Draw a side view of the structure for the given circuit,

b- Illustrate the typical processing steps with the needed masks.

___________________________________________________________________________

2)a- Compare between CMOS and bipolar technologies.

b-The nMOS transistor given in Fig.(2) has: k= 0.3 mA/V

2

, W=8 m, L= 4 m, V

T

= -2V,

c

in

= 4,

n

= 650 cm

2

/V sec, V

ds

= 4.8 V. The supply voltage is 12 V, R

D

=R

S

= 5 kO, R

1

=

150 kO, R

2

= 250 kO.

Find: a- The mode of operation of the transistor,

b- V

gs

and I

D,

c- The transistor transconductance gm,

d- The gate/ channel capacitance,

e- The transistor figure of merit e

o

.

_________________________________________________________________________

3) a- Derive expressions for MOS transistor transconductance g

m

and output conductance g

ds

.

b- Design a complementary logic circuit for F(ABCD) = (0,2,4,5,6,7,8,10,13,15). Note

that this expression indicates the minterms of the logic function F.

___________________________________________________________________________

4) a- Derive an expression for the CMOS inverter delay by estimating both the rise and delay

Times.

b- An off chip capacitance load of 15 pF is to be driven from (a) CMOS and (b) nMOS

inverters. Set up suitable arrangements giving appropriate channel L:W ratios and

dimensions. Calculate the number of inverter stages required, and the delay exhibited by

the overall arrangement driving the 15 pF load. Consider 1.2- technology.

___________________________________________________________________________

5) In Fig. 3, two inputs X and Y are to enter in parallel. Calculate the total delay at the output.

Fig. 1 Fig. 2 Fig. 3

Best Wishes Prof. Dr. Kadry Montasser

Umm Al-Qura University 1429/1430 (1

st

Term)

Faculty of Engineering Subject: Principles of VLSI Design

Department of Computer Engineering 1

st

MidTerm Exam

___________________________________________________________________________

Answer the following questions: Time allowed: 1 Hours

1) Consider the circuit given in Fig. (1):

c- Draw a side view of the structure for the given circuit,

d- Illustrate the typical processing steps with the needed masks.

___________________________________________________________________________

2) a- Derive an expression for the pull-up to pull-down ratio (Z

p.u.

/Z

p.d.

) for an nMOS inverter

driven by another inverter.

b- Compare the relative merits of three different forms of pull-up for an inverter circuit.

What is the best choice for realization in (a) nMOS technology? (b) CMOS

technology.

___________________________________________________________________________

3) Design a complementary logic circuit for F(ABCD) = (0,2,4,5,6,7,8,10,13,15). Note

that this expression indicates the minterms of the logic function F.

4) The nMOS transistor given in Fig. (2) has: k= 0.2 mA/V

2

, W=8 m, L= 4 m, V

T

= -3V,

c

in

= 4,

n

= 650 cm

2

/V sec, V

ds

= 5.6 V. The supply voltage is 12 V, R

D

=R

S

= 6 kO, R

1

= 200

kO, R

2

= 300 kO.

Find: a- The mode of operation of the transistor,

b- V

gs

and I

D,

c- The transistor transconductance gm,

d- The gate/ channel capacitance,

e- The transistor figure of merit e

o

.

Fig. (1) Fig. (2)

___________________________________________________________________________

Best Wishes Prof. Dr. Kadry Montasser

Umm Al-Qura University 1429/1430 (2

nd

Term)

Faculty of Engineering Subject: Principles of VLSI Design

Department of Computer Engineering 2

nd

Midterm Exam

Answer the following questions: Time allowed: 1 (one) Hour

1) Consider the complementary transistor pull-up (CMOS), given in Fig. 1:

i)draw and explain its transfer characteristic and inverter current versus V

in

,

ii)prove that the width to length of the p-device is to be two to three times that of

the n-device.

2) a- Derive an expression for the CMOS inverter delay by estimating both the rise and delay

Times.

b- An off chip capacitance load of 15 pF is to be driven from (a) CMOS and (b) nMOS

inverters. Set up suitable arrangements giving appropriate channel L:W ratios and

dimensions. Calculate the number of inverter stages required, and the delay exhibited by

the overall arrangement driving the 15 pF load. Consider 1.2- technology.

___________________________________________________________________________

3) a- Derive expressions for MOS transistor transconductance g

m

and output conductance g

ds

.

b-In Fig. 2, two inputs X and Y are to enter in parallel. Calculate the total delay at the

output.

3) In Fig. 2, two inputs X and Y are to enter in parallel. Calculate the total delay at the

output O/P.

Fig. 1

Fig. 2

__________________________________________________________________________

Best Wishes Prof. Dr. Kadry Montasser

Umm Al-Qurah University 1429/1430 (1st Term)

Faculty of Computer& Information Systems Subject: Principles of VLSI Design

Department of Computer Engineering Final Exam

Answer ONLY 4(four) questions: Time allowed: 2 Hours

1)a-Aided with neat sketches, show the circuit of fabrication process of the twin-tub shown

in Fig. 1.

b- Illustrate the typical processing steps with the needed masks.

Fig. 1

___________________________________________________________________________

2)a- Compare between CMOS and bipolar technologies.

b-The nMOS transistor given in Fig.(2) has: k= 0.3 mA/V

2

, W=8 m, L= 4 m, V

T

= 2V,

c

in

= 4,

n

= 650 cm

2

/V sec, V

ds

=3.6 V. The supply voltage is 12 V, R

D

=R

S

= 10 kO, R

1

=

200 kO, R

2

= 250 kO.

Find: a- The mode of operation of the transistor,

b- V

gs

and I

D,

c- The transistor transconductance gm,

d- The gate/ channel capacitance,

e- The transistor figure of merit e

o

.

___________________________________________________________________________

3) a- Compare the relative merits of three different forms of pull-up for an inverter circuit.

Explain why of them is the best choice for realization in (i) nMOS technology? (ii)

CMOS technology.

b- Design a complementary logic circuit for F(ABCD) = (3,5,7,11,12,13,14,15). Note

that this expression indicates the minterms of the logic function F.

___________________________________________________________________________

4) a- Determine the pull-up to pull-down ratio (Z

p.u

/Z

p.d

) for an nMOS inverter driven

by another nMOS inverter .

b- An off chip capacitance load of 15 pF is to be driven from (a) CMOS and (b) nMOS

inverters. Set up suitable arrangements giving appropriate channel L:W ratios and

dimensions. Calculate the number of inverter stages required, and the delay exhibited by

the overall arrangement driving the 15 pF load. Consider 1.2- technology.

___________________________________________________________________________

5) In Fig. 3, two inputs X and Y are to enter in parallel. Calculate the total delay at the output.

1/2

Fig. 2 Fig. 3

___________________________________________________________________________

Best Wishes Prof. Dr. Kadry Montasser

2/2

Umm Al-Qura University 1430/1431 (1

st

Term)

Faculty of Engineering Subject: Principles of VLSI Design

Department of Computer Engineering 1

st

MidTerm Exam

___________________________________________________________________________

Answer the following questions: Time allowed: 1 (one) Hour

1) Consider the circuit given in Fig. (1):

e- Draw a side view of the structure for the given circuit,

f- Illustrate the typical processing steps with the needed masks.

___________________________________________________________________________

2) a- Derive an expression for the pull-up to pull-down ratio (Z

p.u.

/Z

p.d.

) for an nMOS inverter

driven through one or more pass transistors.

b- Consider the complementary transistor pull-up (CMOS) given in Fig. (2):

j- draw and explain its transfer characteristic and inverter current versus V

in

,

ii- prove that the width to length of the p-device is to be two to three times that of the

n-device.

___________________________________________________________________________

3)a- Differentiate between the static loads that may be used for MOS inverters. Write your

opinion about the best to be used.

b- The nMOS transistor given in Figure has: k= 0.3 mA/V

2

, W=8 m, L= 4 m, V

T

= -2V,

c

in

= 4,

n

= 650 cm

2

/V sec, V

ds

= 4.8 V. The supply voltage is 12 V, R

D

=R

S

= 5 kO, R

1

=

150 kO, R

2

= 250 kO.

Find: a- The mode of operation of the transistor,

i- V

gs

and I

D

ii- The transistor transconductance gm

iii- The gate/ channel capacitance

iv- The transistor figure of merit e

o

Fig. (1) Fig. (2) Fig. (3)

___________________________________________________________________________

Best Wishes Prof. Dr. Kadry Montasser

You might also like

- Two-Stage Operational Amplifier Design Using Gm/Id MethodNo ratings yetTwo-Stage Operational Amplifier Design Using Gm/Id Method7 pages

- Introduction To CMOS VLSI Design: Credits: David HarrisNo ratings yetIntroduction To CMOS VLSI Design: Credits: David Harris62 pages

- Scaling of MOSFETs and Short Channel Effects0% (1)Scaling of MOSFETs and Short Channel Effects35 pages

- Digital Integrated Circuits: A Design PerspectiveNo ratings yetDigital Integrated Circuits: A Design Perspective29 pages

- Design and Performance Analysis of The Cmos InverterNo ratings yetDesign and Performance Analysis of The Cmos Inverter14 pages

- Laboratory 3 - Resistor Design Manual Part 1 (NWell)No ratings yetLaboratory 3 - Resistor Design Manual Part 1 (NWell)89 pages

- Partially Depleted and Fully Depleted Silicon On Insulator: A Comparative Study Using TCADNo ratings yetPartially Depleted and Fully Depleted Silicon On Insulator: A Comparative Study Using TCAD3 pages

- Ece-V-fundamentals of Cmos Vlsi (10ec56) - Notes0% (1)Ece-V-fundamentals of Cmos Vlsi (10ec56) - Notes214 pages

- Effects of Opamp Finite Gain and Bandwidth On The Performance of Switched Capacitor Filters - KMartin - Sedra - IEEENo ratings yetEffects of Opamp Finite Gain and Bandwidth On The Performance of Switched Capacitor Filters - KMartin - Sedra - IEEE8 pages

- Immediate download CMOS VLSI Design A Circuits and Systems Perspective (4th Edition) ebooks 2024100% (7)Immediate download CMOS VLSI Design A Circuits and Systems Perspective (4th Edition) ebooks 202446 pages

- Low Power High Speed Cmos Comparator DesignNo ratings yetLow Power High Speed Cmos Comparator Design5 pages

- Maloberti F. - Layout of Analog and Mixed Analog-Digital Circuits PDFNo ratings yetMaloberti F. - Layout of Analog and Mixed Analog-Digital Circuits PDF27 pages

- CMOS Inverter: © Digital Integrated Circuits InverterNo ratings yetCMOS Inverter: © Digital Integrated Circuits Inverter77 pages

- An Inverter I. CMOS Inverter Ii. Pseudo nMOS Inverter Iii. Tristate InverterNo ratings yetAn Inverter I. CMOS Inverter Ii. Pseudo nMOS Inverter Iii. Tristate Inverter53 pages

- Logic Families: Designed By: Asadullah JamalovNo ratings yetLogic Families: Designed By: Asadullah Jamalov6 pages

- Vlsi Design Instruction Manual With SolutionNo ratings yetVlsi Design Instruction Manual With Solution65 pages

- Vlsi Lab Manual: Department of Information TechnologyNo ratings yetVlsi Lab Manual: Department of Information Technology135 pages

- CAD For VLSI Lecture Notes - Aravinda Koithyar100% (3)CAD For VLSI Lecture Notes - Aravinda Koithyar116 pages

- Classification of CMOS Digital Logic Circuit (Part - I)No ratings yetClassification of CMOS Digital Logic Circuit (Part - I)35 pages

- A Physically Transient Form of Silicon ElectronicsNo ratings yetA Physically Transient Form of Silicon Electronics6 pages

- Zen of Analog Circuit Design - Anand Udupa100% (5)Zen of Analog Circuit Design - Anand Udupa78 pages

- Cadence Layout Tutorial With Post Layout SimulationNo ratings yetCadence Layout Tutorial With Post Layout Simulation27 pages

- Download (Ebook) Principles of Verilog Digital Design by Wen-Long Chin ISBN 9781032034126, 1032034122 ebook All Chapters PDF100% (8)Download (Ebook) Principles of Verilog Digital Design by Wen-Long Chin ISBN 9781032034126, 1032034122 ebook All Chapters PDF71 pages

- Adamson University College of Engineering Computer Engineering Department Microelectronics LaboratoryNo ratings yetAdamson University College of Engineering Computer Engineering Department Microelectronics Laboratory9 pages

- Dynamic CMOS Circuits: Chapter 4a: Draft - NOT TO BE REPRODUCEDNo ratings yetDynamic CMOS Circuits: Chapter 4a: Draft - NOT TO BE REPRODUCED7 pages

- Chapter 1-8086-16 Bit Microprocessor: by Mr. Shinde G. B. M.Tech. (Electronics Engineering)No ratings yetChapter 1-8086-16 Bit Microprocessor: by Mr. Shinde G. B. M.Tech. (Electronics Engineering)329 pages

- Ec3552 Vlsi Book-muralibabureg2021_compressedNo ratings yetEc3552 Vlsi Book-muralibabureg2021_compressed474 pages

- Two-Stage Operational Amplifier Design Using Gm/Id MethodTwo-Stage Operational Amplifier Design Using Gm/Id Method

- Introduction To CMOS VLSI Design: Credits: David HarrisIntroduction To CMOS VLSI Design: Credits: David Harris

- Design and Performance Analysis of The Cmos InverterDesign and Performance Analysis of The Cmos Inverter

- Laboratory 3 - Resistor Design Manual Part 1 (NWell)Laboratory 3 - Resistor Design Manual Part 1 (NWell)

- Partially Depleted and Fully Depleted Silicon On Insulator: A Comparative Study Using TCADPartially Depleted and Fully Depleted Silicon On Insulator: A Comparative Study Using TCAD

- Effects of Opamp Finite Gain and Bandwidth On The Performance of Switched Capacitor Filters - KMartin - Sedra - IEEEEffects of Opamp Finite Gain and Bandwidth On The Performance of Switched Capacitor Filters - KMartin - Sedra - IEEE

- Immediate download CMOS VLSI Design A Circuits and Systems Perspective (4th Edition) ebooks 2024Immediate download CMOS VLSI Design A Circuits and Systems Perspective (4th Edition) ebooks 2024

- Maloberti F. - Layout of Analog and Mixed Analog-Digital Circuits PDFMaloberti F. - Layout of Analog and Mixed Analog-Digital Circuits PDF

- CMOS Inverter: © Digital Integrated Circuits InverterCMOS Inverter: © Digital Integrated Circuits Inverter

- An Inverter I. CMOS Inverter Ii. Pseudo nMOS Inverter Iii. Tristate InverterAn Inverter I. CMOS Inverter Ii. Pseudo nMOS Inverter Iii. Tristate Inverter

- Vlsi Lab Manual: Department of Information TechnologyVlsi Lab Manual: Department of Information Technology

- Classification of CMOS Digital Logic Circuit (Part - I)Classification of CMOS Digital Logic Circuit (Part - I)

- A Physically Transient Form of Silicon ElectronicsA Physically Transient Form of Silicon Electronics

- Cadence Layout Tutorial With Post Layout SimulationCadence Layout Tutorial With Post Layout Simulation

- Download (Ebook) Principles of Verilog Digital Design by Wen-Long Chin ISBN 9781032034126, 1032034122 ebook All Chapters PDFDownload (Ebook) Principles of Verilog Digital Design by Wen-Long Chin ISBN 9781032034126, 1032034122 ebook All Chapters PDF

- Adamson University College of Engineering Computer Engineering Department Microelectronics LaboratoryAdamson University College of Engineering Computer Engineering Department Microelectronics Laboratory

- Dynamic CMOS Circuits: Chapter 4a: Draft - NOT TO BE REPRODUCEDDynamic CMOS Circuits: Chapter 4a: Draft - NOT TO BE REPRODUCED

- Chapter 1-8086-16 Bit Microprocessor: by Mr. Shinde G. B. M.Tech. (Electronics Engineering)Chapter 1-8086-16 Bit Microprocessor: by Mr. Shinde G. B. M.Tech. (Electronics Engineering)