CA5260, CA5260A: Features

CA5260, CA5260A: Features

Uploaded by

Charbel TadrosOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CA5260, CA5260A: Features

CA5260, CA5260A: Features

Uploaded by

Charbel TadrosCopyright:

Available Formats

DATASHEET

CA5260, CA5260A FN1929

3MHz, BiMOS Microprocessor Operational Amplifiers with MOSFET Input/CMOS Rev 8.00

Output August 3, 2010

The CA5260A and CA5260 are integrated-circuit operational Features

amplifiers that combine the advantage of both CMOS and

bipolar transistors on a monolithic chip. The CA5260 series • MOSFET Input Stage provides

circuits are dual versions of the popular CA5160 series. - Very High ZI . . . . . . . . . . . . . 1.5T (1.5 x 1012) (Typ)

They are designed and guaranteed to operate in - Very Low II . . . . . . . . . . . . . 5pA (Typ) at 15V Operation

microprocessor or logic systems that use +5V supplies. 2pA (Typ) at 5V Operation

• Ideal for Single Supply Applications

Gate-protected P-Channel MOSFET (PMOS) transistors are

• Common Mode Input Voltage Range Includes

used in the input circuit to provide very-high-input

Negative Supply Rail; Input Terminals Can be

impedance, very-low-input current, and exceptional speed

Swung 0.5V Below Negative Supply Rail

performance. The use of PMOS field-effect transistors in the

input stage results in common-mode input-voltage capability • CMOS Output Stage Permits Signal Swing to Either (or

down to 0.5V below the negative-supply terminal, an Both) Supply Rails

important attribute in single-supply applications. • CA5260A, CA5260 Have Full Military Temperature Range

Guaranteed Specifications for V+ = 5V

A complementary-symmetry MOS (CMOS) transistor-pair,

capable of swinging the output voltage to within 10mV of • CA5260A, CA5260 are Guaranteed to Operate Down to

either supply-voltage terminal (at very high values of load 4.5V for AOL

impedance), is employed as the output circuit. • Fully Guaranteed to Operate from -55°C to +125°C at

The CA5260 Series circuits operate at supply voltages V+ = 5V, V- = GND

ranging from 4.5V to 16V, or ±2.25V to ±8V when using split • Pb-Free Available (RoHS Compliant)

supplies.

The CA5260, CA5260A have guaranteed specifications for

Applications

5V operation over the full military temperature range of • Ground Referenced Single Supply Amplifiers

-55°C to +125°C.

• Fast Sample-Hold Amplifiers

Pinout • Long Duration Timers/Monostables

CA5260, CA5260A • Ideal Interface with Digital CMOS

(8 LD SOIC)

TOP VIEW • High Input Impedance Wideband Amplifiers

• Voltage Followers (e.g., Follower for Single Supply D/A

OUTPUT (A) 1 8 V+ Converter)

A

• Voltage Regulators (Permits Control of Output Voltage

INV. INPUT (A) 2 7 OUTPUT (B)

- + Down to 0V)

B

NON INV. INPUT (A) 3

+ -

6 INV. INPUT (B) • Wien Bridge Oscillators

V- 4 5 NON INV. INPUT (B) • Voltage Controlled Oscillators

• Photo Diode Sensor Amplifiers

• 5V Logic Systems

• Microprocessor Interface

FN1929 Rev 8.00 Page 1 of 7

August 3, 2010

CA5260, CA5260A

Ordering Information

PART NUMBER PART TEMP. RANGE PACKAGE PKG.

(Note 3) MARKING (°C) (Pb-Free) DWG. #

CA5260AM96 (Note 1) 5260A -55 to +125 8 Ld SOIC (Tape and Reel) M8.15

CA5260MZ96 (Note 2) CA5260 MZ -55 to +125 8 Ld SOIC M8.15

CA5260M (Notes 1) 5260 -55 to +125 8 Ld SOIC (Tape and Reel) M8.15

CA5260MZ (Note 2) CA5260 MZ -55 to +125 8 Ld SOIC M8.15

NOTES:

1. Please refer to TB347 for details on reel specifications.

2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin

plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free

products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

3. For Moisture Sensitivity Level (MSL), please see device information page for CA5260, CA5260A. For more information on MSL please see

techbrief TB363.

FN1929 Rev 8.00 Page 2 of 7

August 3, 2010

CA5260, CA5260A

Absolute Maximum Ratings Thermal Information

Supply Voltage (Between V+ and V- Terminals) . . . . . . . . . . . . 16V Thermal Resistance (Typical, Note 5) JA (°C/W)

Differential Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8V SOIC Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

Input Voltage . . . . . . . . . . . . . . . . . . . . . . . . (V+ +8V) to (V- -0.5V) Maximum Junction Temperature (Die) . . . . . . . . . . . . . . . . . . . 175°C

Input Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1mA Maximum Junction Temperature (Plastic Package) . . . . . . +150°C

Output Short Circuit Duration (Note 4). . . . . . . . . . . . . . . . Indefinite Maximum Storage Temperature Range . . . . . . . . . -65°C to +150°C

Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . -55°C to +125°C Pb-Free Reflow Profile. . . . . . . . . . . . . . . . . . . . . . . . .see link below

http://www.intersil.com/pbfree/Pb-FreeReflow.asp

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact

product reliability and result in failures not covered by warranty.

NOTES:

4. Short circuit may be applied to ground or to either supply.

5. JA is measured with the component mounted on an evaluation PC board in free air.

Electrical Specifications Typical Values Intended Only for Design Guidance, V+ = 5V, V- = 0V, TA = +25°C, Unless Otherwise Specified

TYPICAL VALUES

PARAMETER SYMBOL TEST CONDITIONS CA5260 CA5260A UNITS

Input Resistance RI 1.5 1.5 T

Input Capacitance CI f = 1MHz 4.3 4.3 pF

Unity Gain Crossover Frequency fT 3 3 MHz

Slew Rate SR VOUT = 2.5VP-P 5 5 V/µs

Transient Response CL = 25pF, RL = 2k

Rise Time tr (Voltage Follower) 0.09 0.09 µs

Overshoot OS 10 10 %

Settling Time (To <0.1%, VIN = 4VP-P) tS CL = 25pF, RL = 2k 1.8 1.8 µs

(Voltage Follower)

Electrical Specifications TA = +25°C, V+ = 5V, V- = 0V

CA5260 CA5260A

TEST

PARAMETER SYMBOL CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

Input Offset Voltage VIO VO = 2.5V - 2 15 - 1.5 4 mV

Input Offset Current IIO VO = 2.5V - 1 10 - 1 10 pA

Input Current II VO = 2.5V - 2 15 - 2 15 pA

Common Mode Rejection CMRR VCM = 0V to 1V 70 85 - 74 85 - dB

Ratio

VCM = 0V to 2.5V 50 55 - 50 55 - dB

Common Mode Input VlCR+ 2.5 3 - 2.5 3 - V

Voltage Range

VlCR- - -0.5 0 - -0.5 0 V

Power Supply Rejection PSRR V+ = 1V; V- = 1V 70 84 - 75 84 - dB

Ratio

Large Signal Voltage Gain AOL RL = , VO = 0.5V to 4V - 111 - - 113 - dB

(Note 6)

RL = 10k, 80 86 - 83 86 - dB

VO = 0.5V to 3.6V

Source Current ISOURCE VO = 0V 1.75 2.2 - 1.75 2.2 - mA

Sink Current ISINK VO = 5V 1.70 2 - 1.70 2 - mA

FN1929 Rev 8.00 Page 3 of 7

August 3, 2010

CA5260, CA5260A

Electrical Specifications TA = +25°C, V+ = 5V, V- = 0V (Continued)

CA5260 CA5260A

TEST

PARAMETER SYMBOL CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

Output Voltage VOM+ RL = 4.99 5 - 4.99 5 - V

VOM- - 0 0.01 - 0 0.01 V

VOM+ RL = 10k 4.4 4.7 - 4.4 4.7 - V

VOM- - 0 0.01 - 0 0.01 V

VOM+ RL = 2k 3 3.4 - 3 3.4 - V

VOM- - 0 0.01 - 0 0.01 V

Supply Current ISUPPLY VO = 0V - 1.60 2.0 - 1.60 2.0 mA

VO = 2.5V - 1.80 2.25 - 1.80 2.25 mA

NOTE:

6. For V+ = 4.5V and V- = GND; VOUT = 0.5V to 3.2V at RL = 10k

Electrical Specifications TA = -55°C to +125°C, V+ = 5V, V- = 0V

CA5260 CA5260A

TEST MIN MAX MIN MAX

PARAMETER SYMBOL CONDITIONS (Note 8) TYP (Note 8) (Note 8) TYP (Note 8) UNITS

Input Offset Voltage VIO VO = 2.5V - 3 20 - 2 15 mV

Input Offset Current IIO VO = 2.5V - 1 10 - 1 10 nA

Input Current II VO = 2.5V - 2 15 - 2 15 nA

Common Mode Rejection Ratio CMRR VCM = 0 to 1V 60 78 - 65 78 - dB

VCM = 0 to 2.5V 50 60 - 50 60 - dB

Common Mode Input Voltage VlCR+ 2.5 3 - 2.5 3 - V

Range

VlCR- - -0.5 0 - -0.5 0 V

Power Supply Rejection Ratio PSRR V+ = 1V; 60 65 - 62 65 - dB

V- = 1V

Large Signal Voltage Gain (Note 7) AOL RL = , 70 78 - 70 78 - dB

VO = 0.5 to 4V

RL = 10k, 60 65 - 60 65 - dB

VO = 0.5 to 3.6V

Source Current ISOURCE VO = 0V 1.3 1.6 - 1.3 1.6 - mA

Sink Current ISINK VO = 5V 1.2 1.4 - 1.2 1.4 - mA

Output Voltage VOM+ RL = 4.99 5 - 4.99 5 - V

VOM- - 0 0.01 - 0 0.01 V

VOM+ RL = 10k 4.2 4.4 - 4.2 4.4 - V

VOM- - 0 0.01 - 0 0.01 V

VOM+ RL = 2k 2.5 2.7 - 2.5 2.7 - V

VOM- - 0 0.01 - 0 0.01 V

Supply Current ISUPPLY VO = 0V - 1.65 2.2 - 1.65 2.2 mA

VO = 2.5V - 1.95 2.35 - 1.95 2.35 mA

NOTES:

7. For V+ = 4.5V and V- = GND; VOUT = 0.5V to 3.2V at RL = 10k

8. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization

and are not production tested.

FN1929 Rev 8.00 Page 4 of 7

August 3, 2010

CA5260, CA5260A

Electrical Specifications Each Amplifier at TA = +25°C, V+ = 15V, V- = 0V, Unless Otherwise Specified

CA5260 CA5260A

TEST

PARAMETER SYMBOL CONDITIONS MIN TYP MAX MIN TYP MAX UNITS

Input Offset Voltage VIO VS = 7.5 - 6 15 - 2 5 mV

Input Offset Current IIO VS = 7.5 - 0.5 30 - 0.5 20 pA

Input Current II VS = 7.5 - 5 50 - 5 30 pA

Large Signal Voltage Gain AOL VO = 10VP-P, 40 320 - 40 320 - kV/V

RL = 10k

92 110 - 92 110 - dB

Common Mode Rejection Ratio CMRR 70 90 - 80 95 - dB

Common Mode Input Voltage VlCR 10 -0.5 to 12 0 10 -0.5 to 12 0 V

Range

Power Supply Rejection Ratio, PSRR VS = 7.5 - 32 320 - 32 150 µV/V

VIO/ V

Maximum Output Voltage VOM+ RL = 10k 11 13.3 - 11 13.3 - V

VOM- - 0.002 0.01 - 0.002 0.01 V

VOM+ RL = 14.99 15 - 14.99 15 - V

VOM- - 0 0.01 - 0 0.01 V

Maximum Output Current IOM+ VO = 7.5V 12 22 45 12 22 45 mA

(Source)

IOM- (Sink) 12 20 45 12 20 45 mA

Total Supply Current, RL = I+ VO (Amp A) = 7.5V - 9 16.5 - 9 16.5 mA

VO (Amp B) = 7.5V

VO (Amp A) = 0V - 1.2 4 - 1.2 4 mA

VO (Amp B) = 0V

VO (Amp A) = 0V VO - 5 9.5 - 5 9.5 mA

(Amp B) = 7.5V

Input Offset Voltage VIO/T - 8 - - 6 - µV/oC

Temperature Drift

Crosstalk f = 1kHz - 120 - - 120 - dB

FN1929 Rev 8.00 Page 5 of 7

August 3, 2010

CA5260, CA5260A

Schematic Diagram

V+

8

AMPLIFIER A AMPLIFIER B

Q6 Q7 Q21 Q20

Q11 Q10 Q9 Q23 Q25

D2 D3 D6 D7 Q24

D1 D4 D5 D8

R5 R12

2k 2k

Q1 Q2 Q8 Q22 Q16

Q12 C1 C2 Q15 Q26

R4 30pF 30pF R11

Q14 Q13 R3 1k 1k R10 Q27 Q28

1k Q5 Q19 1k C4 R13

R6

200k C3 200k

R7 Q3 Q4 Q18 Q17 R14

300k 300

R1 R2 R9 R8

1k 1k 1k 1k

3 2 1 7 6 5 4

+IN -IN OUT -IN +IN V-

FN1929 Rev 8.00 Page 6 of 7

August 3, 2010

CA5260, CA5260A

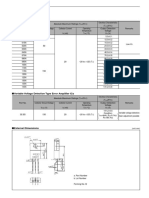

Small Outline Plastic Packages (SOIC)

N

M8.15 (JEDEC MS-012-AA ISSUE C)

8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

INDEX

AREA H 0.25(0.010) M B M

INCHES MILLIMETERS

E

SYMBOL MIN MAX MIN MAX NOTES

-B-

A 0.0532 0.0688 1.35 1.75 -

1 2 3 A1 0.0040 0.0098 0.10 0.25 -

L

B 0.013 0.020 0.33 0.51 9

SEATING PLANE C 0.0075 0.0098 0.19 0.25 -

-A-

A h x 45°

D 0.1890 0.1968 4.80 5.00 3

D

E 0.1497 0.1574 3.80 4.00 4

-C- e 0.050 BSC 1.27 BSC -

H 0.2284 0.2440 5.80 6.20 -

e A1

C h 0.0099 0.0196 0.25 0.50 5

B 0.10(0.004)

L 0.016 0.050 0.40 1.27 6

0.25(0.010) M C A M B S

N 8 8 7

NOTES: 0° 8° 0° 8° -

1. Symbols are defined in the “MO Series Symbol List” in Section 2.2 of Rev. 1 6/05

Publication Number 95.

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimension “D” does not include mold flash, protrusions or gate burrs.

Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006

inch) per side.

4. Dimension “E” does not include interlead flash or protrusions. Inter-

lead flash and protrusions shall not exceed 0.25mm (0.010 inch) per

side.

5. The chamfer on the body is optional. If it is not present, a visual index

feature must be located within the crosshatched area.

6. “L” is the length of terminal for soldering to a substrate.

7. “N” is the number of terminal positions.

8. Terminal numbers are shown for reference only.

9. The lead width “B”, as measured 0.36mm (0.014 inch) or greater

above the seating plane, shall not exceed a maximum value of

0.61mm (0.024 inch).

10. Controlling dimension: MILLIMETER. Converted inch dimensions

are not necessarily exact.

© Copyright Intersil Americas LLC 2003-2010. All Rights Reserved.

All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted

in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such

modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are

current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its

subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN1929 Rev 8.00 Page 7 of 7

August 3, 2010

You might also like

- A Brief Tutorial On Mixers PDFDocument12 pagesA Brief Tutorial On Mixers PDFSage SwayneNo ratings yet

- Ca 3260Document4 pagesCa 3260Carlos TibussiNo ratings yet

- LMC 662Document26 pagesLMC 662gabriel taberneroNo ratings yet

- LMC 662Document26 pagesLMC 662Remy MendozaNo ratings yet

- Ca3260, Ca3260A: 4Mhz, Bimos Operational Amplifier With Mosfet Input/Cmos Output FeaturesDocument4 pagesCa3260, Ca3260A: 4Mhz, Bimos Operational Amplifier With Mosfet Input/Cmos Output FeaturesPaulo Cesar SimonettiNo ratings yet

- HCPL 7601 AvagoDocument13 pagesHCPL 7601 AvagoSyed Khawar MukhtarNo ratings yet

- Features: CMOS Voltage ConvertersDocument12 pagesFeatures: CMOS Voltage ConvertersAlexNo ratings yet

- Ca3130, Ca3130aDocument17 pagesCa3130, Ca3130aproctepNo ratings yet

- Ca3140 ADocument23 pagesCa3140 AvjchandrarNo ratings yet

- 25AA160A/B, 25LC160A/B: 16K SPI Bus Serial EEPROMDocument26 pages25AA160A/B, 25LC160A/B: 16K SPI Bus Serial EEPROMmuglanNo ratings yet

- Item 13 Lmc660ainDocument22 pagesItem 13 Lmc660aindifa20061168No ratings yet

- Datasheet 3Document25 pagesDatasheet 3Rhyan Roberto Ferreira SantosNo ratings yet

- Features: High Supply Voltage 220Mhz Unity-Gain Stable Operational AmplifierDocument13 pagesFeatures: High Supply Voltage 220Mhz Unity-Gain Stable Operational AmplifiersdasfaNo ratings yet

- LM 2904Document7 pagesLM 2904rmlarangNo ratings yet

- Data SheetDocument21 pagesData SheetVíctor GómezNo ratings yet

- Features: 0.5Mhz, Low Supply Voltage, Low Input Current Bimos Operational AmplifierDocument5 pagesFeatures: 0.5Mhz, Low Supply Voltage, Low Input Current Bimos Operational AmplifierAlexandre Correa100% (1)

- CA3140Document19 pagesCA3140samNo ratings yet

- CA3140Document20 pagesCA3140Brzata PticaNo ratings yet

- Isocom H11L1 DatasheetDocument12 pagesIsocom H11L1 DatasheetsolNo ratings yet

- ADC0804 DatasheetDocument48 pagesADC0804 DatasheetSaurabh AnmadwarNo ratings yet

- LMC662 CMOS Dual Operational Amplifier: General Description FeaturesDocument16 pagesLMC662 CMOS Dual Operational Amplifier: General Description FeaturesAnonymous nQ4z7PNo ratings yet

- Amplificador Operacional Usado en Paneles Samsung AS34-GDocument9 pagesAmplificador Operacional Usado en Paneles Samsung AS34-GAntonio ChavezNo ratings yet

- Vishay Siliconix: Features DescriptionDocument2 pagesVishay Siliconix: Features DescriptionEjaz AhmadNo ratings yet

- 6 N 139Document15 pages6 N 1391867468No ratings yet

- Ipm650 PDFDocument5 pagesIpm650 PDFJAHDLNo ratings yet

- Ca3130, Ca3130A: 15Mhz, Bimos Operational Amplifier With Mosfet Input/Cmos Output FeaturesDocument18 pagesCa3130, Ca3130A: 15Mhz, Bimos Operational Amplifier With Mosfet Input/Cmos Output FeaturesJosé Moisés Nuñez SilvaNo ratings yet

- 5 Amps PSDocument10 pages5 Amps PSAmtNo ratings yet

- Charge Pump DC-to-DC Voltage Converter: Features Package TypesDocument20 pagesCharge Pump DC-to-DC Voltage Converter: Features Package TypesTomás CuetoNo ratings yet

- Single-Channel: 6N138, 6N139 Dual-Channel: HCPL-2730, HCPL-2731 Low Input Current High Gain Split Darlington OptocouplersDocument15 pagesSingle-Channel: 6N138, 6N139 Dual-Channel: HCPL-2730, HCPL-2731 Low Input Current High Gain Split Darlington Optocouplersdevrim.kosalNo ratings yet

- SA5888Document8 pagesSA5888albinicue1No ratings yet

- 364 19327 0 Tda3654Document14 pages364 19327 0 Tda3654lidahrahasia07No ratings yet

- 3peak: LM2903/LM2901Document12 pages3peak: LM2903/LM2901alexandre donizetiNo ratings yet

- Low Power Dual Operational Amplifiers Az358/358CDocument13 pagesLow Power Dual Operational Amplifiers Az358/358CMarissa ValdezNo ratings yet

- ADC08831 /ADC08832 8-Bit Serial I/O CMOS A/D Converters With Multiplexer and Sample/Hold FunctionDocument32 pagesADC08831 /ADC08832 8-Bit Serial I/O CMOS A/D Converters With Multiplexer and Sample/Hold FunctionJuan HernándezNo ratings yet

- ICL7611-1.4MHz, Low Power CMOS Operational AmplifiersDocument13 pagesICL7611-1.4MHz, Low Power CMOS Operational Amplifiersy0956880No ratings yet

- Single-Phase Power Supply Unit, Primary Switched For Universal Use QUINT-PS-100-240AC/48DC/20Document10 pagesSingle-Phase Power Supply Unit, Primary Switched For Universal Use QUINT-PS-100-240AC/48DC/20toseruNo ratings yet

- DS ptb78560cDocument27 pagesDS ptb78560cRajesh VenkateshNo ratings yet

- U708Document28 pagesU708Sol De GabrielNo ratings yet

- Ca3140, Ca3140A: 4.5Mhz, Bimos Operational Amplifier With Mosfet Input/Bipolar Output FeaturesDocument19 pagesCa3140, Ca3140A: 4.5Mhz, Bimos Operational Amplifier With Mosfet Input/Bipolar Output FeaturesRicardo Teixeira de AbreuNo ratings yet

- 1558 6n137 PDFDocument21 pages1558 6n137 PDFСергей ЖивиловNo ratings yet

- High Speed, Monolithic D/A Converter With Reference FeaturesDocument10 pagesHigh Speed, Monolithic D/A Converter With Reference FeaturessohcahtoaNo ratings yet

- Data Sheet Gp1 Can 3xm8 CDocument2 pagesData Sheet Gp1 Can 3xm8 Cpk.wil.idkNo ratings yet

- Modulo DVP 04DA SL DatasheetDocument20 pagesModulo DVP 04DA SL DatasheetjoaoNo ratings yet

- Irs2003 (S) PBF: Half-Bridge DriverDocument14 pagesIrs2003 (S) PBF: Half-Bridge DriverSundar RajanNo ratings yet

- HCPL 2200Document12 pagesHCPL 2200Hachimi ZerroukiNo ratings yet

- AIVR1004Document8 pagesAIVR1004SubhashChandraNo ratings yet

- CA3102Document11 pagesCA3102bonaparteCWBNo ratings yet

- Data Sheet: HCPL-3120/J312 HCNW3120Document26 pagesData Sheet: HCPL-3120/J312 HCNW3120Nae CarNo ratings yet

- Ir2301 (S) & (PBF) : High and Low Side DriverDocument18 pagesIr2301 (S) & (PBF) : High and Low Side DriverDr Zeljko DespotovicNo ratings yet

- Features: Dual, Low Power CMOS Operational AmplifiersDocument9 pagesFeatures: Dual, Low Power CMOS Operational AmplifiersDibya DeyNo ratings yet

- +2.7 V To +5.5 V, 350 KSPS, 10-Bit 4-/8-Channel Sampling AdcsDocument20 pages+2.7 V To +5.5 V, 350 KSPS, 10-Bit 4-/8-Channel Sampling AdcsAbhishek ChaudharyNo ratings yet

- CA3161EDocument4 pagesCA3161EAlejandro Borrego DominguezNo ratings yet

- Icl7660 PDFDocument11 pagesIcl7660 PDFfran01334No ratings yet

- SN74CBTS16211 24-Bit Fet Bus Switch With Schottky Diode ClampingDocument11 pagesSN74CBTS16211 24-Bit Fet Bus Switch With Schottky Diode ClampingBa DuyNo ratings yet

- Ca3140, Ca3140A: 4.5Mhz, Bimos Operational Amplifier With Mosfet Input/Bipolar Output FeaturesDocument22 pagesCa3140, Ca3140A: 4.5Mhz, Bimos Operational Amplifier With Mosfet Input/Bipolar Output FeaturesfcabreraibanezNo ratings yet

- 600 Na, Rail-to-Rail Input/Output Op Amps: Features DescriptionDocument40 pages600 Na, Rail-to-Rail Input/Output Op Amps: Features DescriptionNguyen Danh HuyNo ratings yet

- Icl 7673Document7 pagesIcl 7673Luis AlfredoNo ratings yet

- Voltage-Controlled Oscillator: ... The Analog Plus CompanyDocument24 pagesVoltage-Controlled Oscillator: ... The Analog Plus CompanyMoltrevNo ratings yet

- AD694-Circuito Transmisor de 4-20ma, 0-10VDocument17 pagesAD694-Circuito Transmisor de 4-20ma, 0-10VNolan Alexis Rosales SanchezNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Technical Publications: Insite Kit Installation For System Without Isc AssyDocument22 pagesTechnical Publications: Insite Kit Installation For System Without Isc AssyCharbel TadrosNo ratings yet

- 321 CJDocument4 pages321 CJCharbel TadrosNo ratings yet

- Technical Publications: CT Pace/Pace Plus DiagnosticsDocument260 pagesTechnical Publications: CT Pace/Pace Plus DiagnosticsCharbel TadrosNo ratings yet

- Tle 2021Document80 pagesTle 2021Charbel TadrosNo ratings yet

- Technical Publications: Direction 2358897-100 Revision 1Document17 pagesTechnical Publications: Direction 2358897-100 Revision 1Charbel TadrosNo ratings yet

- Step 6 - Auto CalibrationDocument27 pagesStep 6 - Auto CalibrationCharbel TadrosNo ratings yet

- LD130CJDocument8 pagesLD130CJCharbel TadrosNo ratings yet

- The AppendicesDocument58 pagesThe AppendicesCharbel TadrosNo ratings yet

- MC1747Document4 pagesMC1747Charbel TadrosNo ratings yet

- TDA8444Document16 pagesTDA8444Charbel TadrosNo ratings yet

- TMC1175ADocument19 pagesTMC1175ACharbel TadrosNo ratings yet

- Pin Connections: Order This Document by MC34181/DDocument12 pagesPin Connections: Order This Document by MC34181/DCharbel TadrosNo ratings yet

- ADD8702Document8 pagesADD8702Charbel TadrosNo ratings yet

- AD7869Document16 pagesAD7869Charbel TadrosNo ratings yet

- 5-Terminal, Multi-Function, Full-Mold, Low Dropout Voltage Dropper TypeDocument6 pages5-Terminal, Multi-Function, Full-Mold, Low Dropout Voltage Dropper TypeCharbel TadrosNo ratings yet

- VHDL Cookbook 6Document4 pagesVHDL Cookbook 6Charbel TadrosNo ratings yet

- VHDL Cookbook 2Document18 pagesVHDL Cookbook 2Charbel TadrosNo ratings yet

- VHDL Cookbook 7Document58 pagesVHDL Cookbook 7Charbel TadrosNo ratings yet

- VHDL Cookbook 5Document7 pagesVHDL Cookbook 5Charbel TadrosNo ratings yet

- VHDL Cookbook 3Document6 pagesVHDL Cookbook 3Charbel TadrosNo ratings yet

- Video ControllerDocument57 pagesVideo ControllerCharbel TadrosNo ratings yet

- AD96685/AD96687 Ultrafast ComparatorsDocument8 pagesAD96685/AD96687 Ultrafast ComparatorsCharbel TadrosNo ratings yet

- VHDL Cookbook 1Document5 pagesVHDL Cookbook 1Charbel TadrosNo ratings yet

- Siemens NEW Matrix ManualDocument1 pageSiemens NEW Matrix ManualCharbel TadrosNo ratings yet

- Ta1360Afg: Ycbcr/Ypbpr Signal and Sync Processor For Digital TV, Progressive Scan TV and Double Scan TVDocument110 pagesTa1360Afg: Ycbcr/Ypbpr Signal and Sync Processor For Digital TV, Progressive Scan TV and Double Scan TVCharbel TadrosNo ratings yet

- Obsolete Product(s) - Obsolete Product(s) : Switch-Mode Solenoid DriverDocument8 pagesObsolete Product(s) - Obsolete Product(s) : Switch-Mode Solenoid DriverCharbel TadrosNo ratings yet

- Error Amplifier Ics (Se Series)Document1 pageError Amplifier Ics (Se Series)Charbel TadrosNo ratings yet

- Precision Power Analyzer Communication Interface: WT3000 Manual, Vol 2/3Document151 pagesPrecision Power Analyzer Communication Interface: WT3000 Manual, Vol 2/3Hữu DuyệtNo ratings yet

- ANT-ATR451703-0604 DatasheetDocument2 pagesANT-ATR451703-0604 DatasheetDris AkliNo ratings yet

- Product Specifications Product Specifications: MR918 MR918Document2 pagesProduct Specifications Product Specifications: MR918 MR918TC Cemal GüntürkünNo ratings yet

- Difference Between Curves v1.2: How To Find The Frequency Response in A MicrophoneDocument12 pagesDifference Between Curves v1.2: How To Find The Frequency Response in A MicrophoneNicola AttimonelliNo ratings yet

- Traffic Light Controller Using 8051 Microcontroller: Mini Project Report OnDocument1 pageTraffic Light Controller Using 8051 Microcontroller: Mini Project Report OnNithin JohnNo ratings yet

- Tle Ict Grade 8Document3 pagesTle Ict Grade 8cid ladjamatliNo ratings yet

- Introduction To Massive MIMODocument33 pagesIntroduction To Massive MIMOturi313No ratings yet

- Conformity Cert 200400vdc 3Document1 pageConformity Cert 200400vdc 3Mohammed HamedNo ratings yet

- Service Manual: SpecificationsDocument50 pagesService Manual: SpecificationsSimon PapukyanNo ratings yet

- Cce TV HPS-2906 PDFDocument1 pageCce TV HPS-2906 PDFeduscribd18No ratings yet

- Ammonit Meteo-40 Data Logger: Accurate. Reliable. Effi CientDocument6 pagesAmmonit Meteo-40 Data Logger: Accurate. Reliable. Effi CientdiCoutiNo ratings yet

- DSPDocument51 pagesDSPIman_Mukherjee_5260No ratings yet

- F4 Worksheet (Network) 5 (With Answer)Document2 pagesF4 Worksheet (Network) 5 (With Answer)Mr. Jack 1106No ratings yet

- Sctx6Arx6A: Remote Controller With Secen FunctionsDocument7 pagesSctx6Arx6A: Remote Controller With Secen FunctionsGebert TorresNo ratings yet

- Axis11 Beep Call SolutionDocument13 pagesAxis11 Beep Call Solutionpoppy tooNo ratings yet

- For Nos (1) 8THDocument14 pagesFor Nos (1) 8THBalu PrasadNo ratings yet

- Ericsson MSS Kpi-FormulaeDocument13 pagesEricsson MSS Kpi-Formulaekaijage kishekyaNo ratings yet

- User's Manual For Android 4.4.4 Head Unit GPS Navigation SystemDocument30 pagesUser's Manual For Android 4.4.4 Head Unit GPS Navigation SystemALJASMI78No ratings yet

- Huawei 5g Cpe Pro h112 370 372 Datasheet PDFDocument3 pagesHuawei 5g Cpe Pro h112 370 372 Datasheet PDFKunjali KummalilNo ratings yet

- Lowpower Vlsi Design.Document5 pagesLowpower Vlsi Design.NareshNo ratings yet

- ST-IIIB User ManualDocument46 pagesST-IIIB User ManualderbalijalelNo ratings yet

- Sailor Rt5022 VHF DSC Sailor Rt5020 VHF DSC Duplex: Operation ManualDocument68 pagesSailor Rt5022 VHF DSC Sailor Rt5020 VHF DSC Duplex: Operation ManualAleksey BuzulukovNo ratings yet

- Technote-Aci-Snmp - v3 - Good Debug Commands PDFDocument115 pagesTechnote-Aci-Snmp - v3 - Good Debug Commands PDFflyingccie datacenterNo ratings yet

- TC-L32E6H: 32 Inch Class 1080p LCD HDTVDocument30 pagesTC-L32E6H: 32 Inch Class 1080p LCD HDTVJosé Ivan Bonillas GranadosNo ratings yet

- Data Sheet 6ES7214-1AG40-0XB0: General InformationDocument9 pagesData Sheet 6ES7214-1AG40-0XB0: General InformationMuh Talib HRNo ratings yet

- Unit IVDocument53 pagesUnit IVRiya KateNo ratings yet

- Digital Literacy Skills: Info-Savvy Media-Fluent Tech-TunedDocument11 pagesDigital Literacy Skills: Info-Savvy Media-Fluent Tech-TunedBrendajc JcNo ratings yet

- Audio Delivery Specifications Around The WorldDocument2 pagesAudio Delivery Specifications Around The Worldmailmanager8946No ratings yet

- VGA/LCD Core Specifications: Author: Richard HerveilleDocument29 pagesVGA/LCD Core Specifications: Author: Richard HerveilleVasista AtiNo ratings yet