100N50F FDL Mosfet N PDF

100N50F FDL Mosfet N PDF

Uploaded by

Hưng HQCopyright:

Available Formats

100N50F FDL Mosfet N PDF

100N50F FDL Mosfet N PDF

Uploaded by

Hưng HQOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Copyright:

Available Formats

100N50F FDL Mosfet N PDF

100N50F FDL Mosfet N PDF

Uploaded by

Hưng HQCopyright:

Available Formats

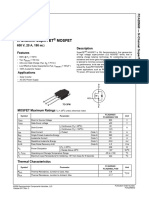

FDL100N50F N-Channel MOSFET

May 2009

UniFETTM

FDL100N50F

N-Channel MOSFET,FRFET

500V, 100A, 0.055

Features Description

RDS(on) = 0.043 ( Typ.)@ VGS = 10V, ID = 50A These N-Channel enhancement mode power field effect

transistors are produced using Fairchilds proprietary, planar

Low gate charge ( Typ. 238nC) stripe, DMOS technology.

Low Crss ( Typ. 64pF) This advanced technology has been especially tailored to

Fast switching minimize on-state resistance, provide superior switching

performance, and withstand high energy pulse in the avalanche

100% avalanche tested and commutation mode. These devices are well suited for high

efficient switched mode power supplies and active power factor

Improved dv/dt capability

correction.

RoHS Compliant

TO-264

G D S FDL Series

S

MOSFET Maximum Ratings TC = 25 C unless otherwise noted o

Symbol Parameter FDL100N50F Units

VDSS Drain to Source Voltage 500 V

VGSS Gate to Source Voltage 30 V

-Continuous (TC = 25oC) 100

ID Drain Current A

-Continuous (TC = 100oC) 60

IDM Drain Current - Pulsed (Note 1) 400 A

EAS Single Pulsed Avalanche Energy (Note 2) 5000 mJ

IAR Avalanche Current (Note 1) 100 A

EAR Repetitive Avalanche Energy (Note 1) 73.5 mJ

dv/dt Peak Diode Recovery dv/dt (Note 3) 20 V/ns

(TC = 25oC) 2500 W

PD Power Dissipation

- Derate above 25oC 20 W/oC

o

TJ, TSTG Operating and Storage Temperature Range -55 to +150 C

Maximum Lead Temperature for Soldering Purpose, o

TL 300 C

1/8 from Case for 5 Seconds

*Drain current limited by maximum junction temperature

Thermal Characteristics

Symbol Parameter Min. Max. Units

RJC Thermal Resistance, Junction to Case - 0.05

o

RCS Thermal Resistance, Case to Sink Typ. 0.1 - C/W

RJA Thermal Resistance, Junction to Ambient - 30

2009 Fairchild Semiconductor Corporation 1 www.fairchildsemi.com

FDL100N50F Rev. A

FDL100N50F N-Channel MOSFET

Package Marking and Ordering Information

Device Marking Device Package Reel Size Tape Width Quantity

FDL100N50F FDL100N50F TO-264 - - 30

Electrical Characteristics TC = 25oC unless otherwise noted

Symbol Parameter Test Conditions Min. Typ. Max. Units

Off Characteristics

BVDSS Drain to Source Breakdown Voltage ID = 250A, VGS = 0V, TC = 25oC 500 - - V

BVDSS Breakdown Voltage Temperature

ID = 250A, Referenced to 25oC - 0.5 - V/oC

TJ Coefficient

VDS = 500V, VGS = 0V - - 10

IDSS Zero Gate Voltage Drain Current A

VDS = 400V, TC = 125oC - - 100

IGSS Gate to Body Leakage Current VGS = 30V, VDS = 0V - - 100 nA

On Characteristics

VGS(th) Gate Threshold Voltage VGS = VDS, ID = 250A 3.0 - 5.0 V

RDS(on) Static Drain to Source On Resistance VGS = 10V, ID = 50A - 0.043 0.055

gFS Forward Transconductance VDS = 20V, ID = 50A (Note 4) - 95 - S

Dynamic Characteristics

Ciss Input Capacitance - 12000 - pF

VDS = 25V, VGS = 0V

Coss Output Capacitance - 1700 - pF

f = 1MHz

Crss Reverse Transfer Capacitance - 64 - pF

Qg(tot) Total Gate Charge at 10V - 238 - nC

VDD = 400V, ID = 50A

Qgs Gate to Source Gate Charge - 74 - nC

VGS = 10V

Qgd Gate to Drain Miller Charge - 95 - nC

Switching Characteristics

td(on) Turn-On Delay Time - 63 - ns

tr Turn-On Rise Time VDD = 250V, ID = 50A - 186 - ns

RG = 4.7

td(off) Turn-Off Delay Time - 202 - ns

tf Turn-Off Fall Time - 105 - ns

Drain-Source Diode Characteristics

IS Maximum Continuous Drain to Source Diode Forward Current - - 100 A

ISM Maximum Pulsed Drain to Source Diode Forward Current - - 400 A

VSD Drain to Source Diode Forward Voltage VGS = 0V, ISD = 100A - - 1.5 V

trr Reverse Recovery Time VGS = 0V, ISD = 100A - 250 - ns

Qrr Reverse Recovery Charge dIF/dt = 100A/s - 1.5 - nC

Notes:

1. Repetitive Rating: Pulse width limited by maximum junction temperature

2. L = 1mH, IAS = 100A, VDD = 50V, RG = 25, Starting TJ = 25C

3. ISD 100A, di/dt 200A/s, VDD BVDSS, Starting TJ = 25C

4. Pulse Test: Pulse width 300s, Duty Cycle 2%

5. Essentially Independent of Operating Temperature Typical Characteristics

FDL100N50F Rev. A 2 www.fairchildsemi.com

FDL100N50F N-Channel MOSFET

Typical Performance Characteristics

Figure 1. On-Region Characteristics Figure 2. Transfer Characteristics

300 400

VGS = 15.0 V

10.0 V

100 8.0 V

7.0 V 100

6.5 V

ID, Drain Current[A]

ID, Drain Current[A]

6.0 V

o

150 C

o

25 C

10

10

o

-55 C

*Notes: *Notes:

1. 250s Pulse Test 1. VDS = 20V

1 o

2. TC = 25 C 2. 250s Pulse Test

0.5 1

0.1 1 10 4 6 8 10

VDS, Drain-Source Voltage[V] VGS, Gate-Source Voltage[V]

Figure 3. On-Resistance Variation vs. Figure 4. Body Diode Forward Voltage

Drain Current and Gate Voltage Variation vs. Source Current

and Temperature

0.07 300

100

Drain-Source On-Resistance

IS, Reverse Drain Current [A]

0.06 o

150 C

RDS(ON) [],

VGS = 10V

0.05

o

25 C

VGS = 20V 10

0.04

*Notes:

1. VGS = 0V

o

*Note: TC = 25 C 2. 250s Pulse Test

0.03 1

0 50 100 150 200 250 0.0 0.5 1.0 1.5

ID, Drain Current [A] VSD, Body Diode Forward Voltage [V]

Figure 5. Capacitance Characteristics Figure 6. Gate Charge Characteristics

30000 10

Ciss = Cgs + Cgd (Cds = shorted)

Coss = Cds + Cgd VDS = 100V

VGS, Gate-Source Voltage [V]

25000 Crss = Cgd VDS = 250V

Coss 8 VDS = 400V

20000 *Note:

Capacitances [pF]

1. VGS = 0V 6

2. f = 1MHz

15000 Ciss

4

10000

Crss

2

5000

*Note: ID = 50A

0 0

10

-1

1 10 30 0 50 100 150 200 250

VDS, Drain-Source Voltage [V] Qg, Total Gate Charge [nC]

FDL100N50F Rev. A 3 www.fairchildsemi.com

FDL100N50F N-Channel MOSFET

Typical Performance Characteristics (Continued)

Figure 7. Breakdown Voltage Variation Figure 8. On-Resistance Variation

vs. Temperature vs. Temperature

1.2 3.0

Drain-Source Breakdown Voltage

2.5

Drain-Source On-Resistance

1.1

BVDSS, [Normalized]

RDS(on), [Normalized]

2.0

1.0 1.5

1.0

0.9

*Notes: *Notes:

0.5

1. VGS = 0V 1. VGS = 10V

2. ID = 1mA 2. ID = 50A

0.8 0.0

-100 -50 0 50 100 150 200 -100 -50 0 50 100 150 200

o o

TJ, Junction Temperature [ C] TJ, Junction Temperature [ C]

Figure 9. Maximum Safe Operating Area Figure 10. Maximum Drain Current

vs. Case Temperature

1000 120

30s

100s

100

100 1ms

ID, Drain Current [A]

10ms

DC

ID, Drain Current [A]

80

10

60

Operation in This Area

1 is Limited by R DS(on)

40

*Notes:

o

0.1 1. TC = 25 C

20

o

2. TJ = 150 C

3. Single Pulse

0.01 0

1 10 100 1000 25 50 75 100 125 150

o

VDS, Drain-Source Voltage [V] TC, Case Temperature [ C]

Figure 11. Transient Thermal Response Curve

0.1

Thermal Response [ZJC]

0.5

0.01 0.2

0.1

PDM

0.05

t1

0.02 t2

0.001 0.01 *Notes:

Single pulse o

1. ZJC(t) = 0.05 C/W Max.

2. Duty Factor, D= t1/t2

3. TJM - TC = PDM * ZJC(t)

0.0001

-5 -4 -3 -2 -1

10 10 10 10 10 1

Rectangular Pulse Duration [sec]

FDL100N50F Rev. A 4 www.fairchildsemi.com

FDL100N50F N-Channel MOSFET

Gate Charge Test Circuit & Waveform

Resistive Switching Test Circuit & Waveforms

Unclamped Inductive Switching Test Circuit & Waveforms

FDL100N50F Rev. A 5 www.fairchildsemi.com

FDL100N50F N-Channel MOSFET

Peak Diode Recovery dv/dt Test Circuit & Waveforms

DUT +

V DS

I SD

L

D r iv e r

R G

S am e T ype

as DUT V DD

V GS d v / d t c o n t r o lle d b y R G

I S D c o n t r o lle d b y p u ls e p e r io d

G a t e P u ls e W id t h

V GS D = --------------------------

G a t e P u ls e P e r io d 10V

( D r iv e r )

I F M , B o d y D io d e F o r w a r d C u r r e n t

I SD

( DUT ) d i/d t

IR M

B o d y D io d e R e v e r s e C u r r e n t

V DS

( DUT ) B o d y D io d e R e c o v e r y d v / d t

V SD V DD

B o d y D io d e

F o r w a r d V o lta g e D r o p

FDL100N50F Rev. A 6 www.fairchildsemi.com

FDL100N50F N-Channel MOSFET

Mechanical Dimensions

Dimensions in Millimeters

FDL100N50F Rev. A 7 www.fairchildsemi.com

FDL100N50F MOSFET

TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not

intended to be an exhaustive list of all such trademarks.

Auto-SPM F-PFS PowerTrench The Power Franchise

Build it Now FRFET PowerXS

CorePLUS Global Power ResourceSM Programmable Active Droop

CorePOWER Green FPS QFET

tm

CROSSVOLT Green FPS e-Series QS TinyBoost

CTL Gmax Quiet Series TinyBuck

Current Transfer Logic GTO RapidConfigure TinyLogic

EcoSPARK IntelliMAX TINYOPTO

EfficentMax ISOPLANAR TinyPower

EZSWITCH * MegaBuck Saving our world, 1mW /W /kW at a time TinyPWM

* MICROCOUPLER SmartMax TinyWire

MicroFET SMART START TriFault Detect

MicroPak SPM TRUECURRENT*

tm MillerDrive STEALTH SerDes

Fairchild MotionMax SuperFET

Fairchild Semiconductor Motion-SPM SuperSOT-3

FACT Quiet Series OPTOLOGIC SuperSOT-6 UHC

FACT OPTOPLANAR SuperSOT-8 Ultra FRFET

FAST SupreMOS UniFET

FastvCore SyncFET VCX

FETBench

tm

Sync-Lock VisualMax

FlashWriter * PDP SPM

* XS

FPS Power-SPM

*Trademarks of System General Corporation, used under license by Fairchild Semiconductor.

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE

RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY

PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILDS WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY

THEREIN, WHICH COVERS THESE PRODUCTS.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE

EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

As used herein:

1. Life support devices or systems are devices or systems which, (a) are 2. A critical component in any component of a life support, device, or

intended for surgical implant into the body or (b) support or sustain life, system whose failure to perform can be reasonably expected to cause

and (c) whose failure to perform when properly used in accordance with the failure of the life support device or system, or to affect its safety or

instructions for use provided in the labeling, can be reasonably effectiveness.

expected to result in a significant injury of the user.

ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporations Anti-Counterfeiting Policy. Fairchilds Anti-Counterfeiting Policy is also stated on our external website,

www.Fairchildsemi.com, under Sales Support.

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufactures of semiconductor products are experiencing counterfeiting of their

parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed

application, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the

proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild

Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild

Distributors are genuine parts, have full traceability, meet Fairchilds quality standards for handing and storage and provide access to Fairchilds full range of

up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address and

warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is

committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

PRODUCT STATUS DEFINITIONS

Definition of Terms

Datasheet Identification Product Status Definition

Datasheet contains the design specifications for product development. Specifications

Advance Information Formative / In Design

may change in any manner without notice.

Datasheet contains preliminary data; supplementary data will be published at a later

Preliminary First Production date. Fairchild Semiconductor reserves the right to make changes at any time without

notice to improve design.

Datasheet contains final specifications. Fairchild Semiconductor reserves the right to

No Identification Needed Full Production

make changes at any time without notice to improve the design.

Datasheet contains specifications on a product that is discontinued by Fairchild

Obsolete Not In Production

Semiconductor. The datasheet is for reference information only.

Rev. I40

FDL100N50F Rev. A 8 www.fairchildsemi.com

You might also like

- BOP Failure Mode Effect Analysis PDFDocument725 pagesBOP Failure Mode Effect Analysis PDFAbd EnnacerNo ratings yet

- DatasheetDocument8 pagesDatasheetRegisk8 OliveiraNo ratings yet

- FDL100N50F DDocument9 pagesFDL100N50F DrajayoganandNo ratings yet

- FCA20N60_F109_D-2311741Document8 pagesFCA20N60_F109_D-2311741Antonio FilhoNo ratings yet

- Fch25N60N: N-Channel Supremos MosfetDocument8 pagesFch25N60N: N-Channel Supremos MosfetKUMAR ABHINAVNo ratings yet

- Fcb20N60: N-Channel Superfet MosfetDocument9 pagesFcb20N60: N-Channel Superfet MosfetEo GpNo ratings yet

- Fqa 24 N 50Document8 pagesFqa 24 N 50CristhianNo ratings yet

- FDP20N50 184794Document11 pagesFDP20N50 184794Paulo NogueiraNo ratings yet

- FCH25N60NDocument8 pagesFCH25N60Ngustavo gonzalezNo ratings yet

- Mosfet FDPDocument8 pagesMosfet FDPIrvin OrtegaNo ratings yet

- FDD5N50Document8 pagesFDD5N50primero marnezNo ratings yet

- FQPF8N60C-tv Mosfet OriginalDocument9 pagesFQPF8N60C-tv Mosfet OriginalFerhat QweNo ratings yet

- FQA10N80-darasheetDocument9 pagesFQA10N80-darasheetnasiriNo ratings yet

- FDP20N50FDocument10 pagesFDP20N50Ftplink.gtzrojasNo ratings yet

- Fda 69 N 25Document8 pagesFda 69 N 25Jose Altamiranda GarcesNo ratings yet

- Irf 634 BDocument8 pagesIrf 634 BAhmed ShagidullinNo ratings yet

- FDP 150 N 10Document8 pagesFDP 150 N 10Luka BaracNo ratings yet

- fdp33n25 fdpf33n25tDocument10 pagesfdp33n25 fdpf33n25tNovri AndiNo ratings yet

- FCH067N65S3 FairchildSemiconductorDocument9 pagesFCH067N65S3 FairchildSemiconductorJoaquim FernandesNo ratings yet

- Fdp8N50Nz / Fdpf8N50Nz: N-Channel Unifet Ii MosfetDocument10 pagesFdp8N50Nz / Fdpf8N50Nz: N-Channel Unifet Ii MosfetsrasicNo ratings yet

- 16N60 Fairchild SemiconductorDocument10 pages16N60 Fairchild SemiconductorPop-Coman SimionNo ratings yet

- FQPF 8 N 60 CFDocument8 pagesFQPF 8 N 60 CFBhadreshkumar SharmaNo ratings yet

- Superfet Ii Fcp260N60E / Fcpf260N60E: 600V N-Channel MosfetDocument10 pagesSuperfet Ii Fcp260N60E / Fcpf260N60E: 600V N-Channel MosfetAlexandros BobNo ratings yet

- MDF13N50: N-Channel MOSFET 500V, 13.0 A, 0.5Document6 pagesMDF13N50: N-Channel MOSFET 500V, 13.0 A, 0.5Moroșan CristiNo ratings yet

- B 812 Cfa 38Document8 pagesB 812 Cfa 38Sajid AliNo ratings yet

- STF 13 NM 60 NDDocument12 pagesSTF 13 NM 60 NDlejojoel321No ratings yet

- FQP8N60C: N-Channel QFET MosfetDocument8 pagesFQP8N60C: N-Channel QFET MosfetVuksanov ZarkoNo ratings yet

- fdp054n10 PDFDocument8 pagesfdp054n10 PDFAldi DwprstwnNo ratings yet

- FDP025N06Document9 pagesFDP025N06bravo.bravoNo ratings yet

- Datasheet FDP7N50Document10 pagesDatasheet FDP7N50Anonymous fAL3CNtUiNo ratings yet

- Datasheet PDFDocument10 pagesDatasheet PDFShikamaru MendozaNo ratings yet

- Fqa9n90c F109-96052 PDFDocument9 pagesFqa9n90c F109-96052 PDFKhoa DangNo ratings yet

- MDF7N60BDocument8 pagesMDF7N60BFreddyNo ratings yet

- MDP2N60/MDF2N60: N-Channel MOSFET 600V, 2.0A, 4.5Document8 pagesMDP2N60/MDF2N60: N-Channel MOSFET 600V, 2.0A, 4.5Erroz RosadiNo ratings yet

- MDF11N65BDocument6 pagesMDF11N65BElec FoNo ratings yet

- fqp30n06 1192362Document9 pagesfqp30n06 1192362channyein.paypalNo ratings yet

- MDF10N60G 1Document6 pagesMDF10N60G 1samvick103No ratings yet

- FQP10N60C DatasheetzDocument10 pagesFQP10N60C DatasheetzagesoporteNo ratings yet

- Fdp52N20 / Fdpf52N20T: UnifetDocument10 pagesFdp52N20 / Fdpf52N20T: UnifetJoão de barroNo ratings yet

- Fcp190N60 / Fcpf190N60: N-Channel Superfet Ii MosfetDocument10 pagesFcp190N60 / Fcpf190N60: N-Channel Superfet Ii Mosfetarness22No ratings yet

- FQB55N10: N-Channel QFET MosfetDocument8 pagesFQB55N10: N-Channel QFET MosfetcurzNo ratings yet

- FQPF12N60C FairchildSemiconductorDocument9 pagesFQPF12N60C FairchildSemiconductorAkhmad Isnaeni RamdaniNo ratings yet

- FQP12N60C FairchildSemiconductorDocument9 pagesFQP12N60C FairchildSemiconductoroskr.bstNo ratings yet

- WFF13N50 WinsemisemiconductorDocument8 pagesWFF13N50 WinsemisemiconductorHamilton Jorge SilvaNo ratings yet

- OSP5N60C-OSF5N60CDocument7 pagesOSP5N60C-OSF5N60Cbewareofthedark8No ratings yet

- Fca47n60 FetDocument10 pagesFca47n60 FetRuslanNo ratings yet

- FQPF13N50CFDocument8 pagesFQPF13N50CFPiotr vvNo ratings yet

- Frfet: FQA24N50FDocument8 pagesFrfet: FQA24N50FqaisersgsNo ratings yet

- STF 13 NM 60 NDocument12 pagesSTF 13 NM 60 Nrafaelmattos2015No ratings yet

- 4N60BDocument11 pages4N60BAirton SousaNo ratings yet

- MDF11N60: N-Channel MOSFET 600V, 11A, 0.55Document6 pagesMDF11N60: N-Channel MOSFET 600V, 11A, 0.55Ariel MercochaNo ratings yet

- FCH47N60F 37104 214932Document11 pagesFCH47N60F 37104 214932Crazy electroNo ratings yet

- FQP10N20C / FQPF10N20C: N-Channel QFET MosfetDocument10 pagesFQP10N20C / FQPF10N20C: N-Channel QFET MosfethenriquegonferNo ratings yet

- fqpf5n50cf Fqpf5n50cftu PDFDocument8 pagesfqpf5n50cf Fqpf5n50cftu PDFALFREDO BARREZUETANo ratings yet

- FQPF7N80C FQPF7N80CDocument12 pagesFQPF7N80C FQPF7N80Cmadeline cruzata downerNo ratings yet

- 18N80T DatasheetDocument10 pages18N80T DatasheetVịnh DemoNo ratings yet

- IRF630BDocument12 pagesIRF630BIon CretuNo ratings yet

- Fda59N30: N-Channel Unifet MosfetDocument8 pagesFda59N30: N-Channel Unifet Mosfettecson.engNo ratings yet

- A Guide to Vintage Audio Equipment for the Hobbyist and AudiophileFrom EverandA Guide to Vintage Audio Equipment for the Hobbyist and AudiophileNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- BDX33C Transistor PDFDocument4 pagesBDX33C Transistor PDFHưng HQNo ratings yet

- 100N50P IXFB Power Mosfet PDFDocument5 pages100N50P IXFB Power Mosfet PDFHưng HQNo ratings yet

- Bat54 Series Typical Characteristics Bat54 Series: Sot23 Silicon Epitaxial Schottky Barrier DiodesDocument2 pagesBat54 Series Typical Characteristics Bat54 Series: Sot23 Silicon Epitaxial Schottky Barrier DiodesHưng HQNo ratings yet

- 47N60C3 Mos N PDFDocument14 pages47N60C3 Mos N PDFHưng HQNo ratings yet

- Po3 PDFDocument7 pagesPo3 PDFHưng HQNo ratings yet

- 47N60 FCA MOSFET N-Channel PDFDocument9 pages47N60 FCA MOSFET N-Channel PDFHưng HQNo ratings yet

- 32N50C3 Mos PDFDocument11 pages32N50C3 Mos PDFHưng HQNo ratings yet

- Infineon IPP075N15N3 DS v02 06 enDocument11 pagesInfineon IPP075N15N3 DS v02 06 enRiss CalmaNo ratings yet

- Fqa19n60 PDFDocument8 pagesFqa19n60 PDFHưng HQNo ratings yet

- 43NM60ND Mos PDFDocument13 pages43NM60ND Mos PDFHưng HQNo ratings yet

- 6R190C6 Mos PDFDocument19 pages6R190C6 Mos PDFHưng HQNo ratings yet

- 6N90C Mosfet N PDFDocument10 pages6N90C Mosfet N PDFHưng HQNo ratings yet

- RHRG1560C Diode PDFDocument5 pagesRHRG1560C Diode PDFHưng HQNo ratings yet

- 317mbg PDFDocument13 pages317mbg PDFHưng HQNo ratings yet

- Features Description: Ltc1799 1Khz To 33Mhz Resistor Set Sot-23 OscillatorDocument14 pagesFeatures Description: Ltc1799 1Khz To 33Mhz Resistor Set Sot-23 OscillatorHưng HQNo ratings yet

- 317mbg PDFDocument13 pages317mbg PDFHưng HQNo ratings yet

- Hef40106b PDFDocument15 pagesHef40106b PDFHưng HQNo ratings yet

- lm5110 1 PDFDocument13 pageslm5110 1 PDFHưng HQNo ratings yet

- Features Description: Ltc1799 1Khz To 33Mhz Resistor Set Sot-23 OscillatorDocument14 pagesFeatures Description: Ltc1799 1Khz To 33Mhz Resistor Set Sot-23 OscillatorHưng HQNo ratings yet

- STPS80L60CY-ST Diode Kep PDFDocument3 pagesSTPS80L60CY-ST Diode Kep PDFHưng HQNo ratings yet

- DSSK30-018A-476304 Diode Kep PDFDocument3 pagesDSSK30-018A-476304 Diode Kep PDFHưng HQNo ratings yet

- F60SA60DS K36 Diode Kep PDFDocument3 pagesF60SA60DS K36 Diode Kep PDFHưng HQNo ratings yet

- DSSK 30-018A Diode Kep PDFDocument2 pagesDSSK 30-018A Diode Kep PDFHưng HQNo ratings yet

- STPS40170C High Voltage Power Schottky Rectifier Diode PDFDocument8 pagesSTPS40170C High Voltage Power Schottky Rectifier Diode PDFHưng HQNo ratings yet

- The Devil Never Sleeps''.FalicovDocument21 pagesThe Devil Never Sleeps''.FalicovQuisocNo ratings yet

- Azamar - CompanionDocument60 pagesAzamar - Companionteam_mo100% (1)

- Minister Asked To Probe PM Criticism in Nottingham School LessonDocument1 pageMinister Asked To Probe PM Criticism in Nottingham School LessonCraig Siewai PerkintonNo ratings yet

- Income Tax Verification: Reminder To Submit Supporting DocumentsDocument1 pageIncome Tax Verification: Reminder To Submit Supporting Documentsbra9tee9tiniNo ratings yet

- Gen 001 TG 23Document9 pagesGen 001 TG 23marryluvvieNo ratings yet

- TN, TT, ItDocument14 pagesTN, TT, ItTuan Anh Le CongNo ratings yet

- 610 Final ProjectDocument8 pages610 Final Projectapi-309677775No ratings yet

- Janssen 2nd D0se 8-5-2021 Updated DianeDocument64 pagesJanssen 2nd D0se 8-5-2021 Updated DianeGanie Mar BiasonNo ratings yet

- A Guide To Seed FundraisingDocument15 pagesA Guide To Seed FundraisingMridul UpadhyayNo ratings yet

- CultureAndImperialism 1 PDFDocument66 pagesCultureAndImperialism 1 PDFMà Ř YãmNo ratings yet

- MIDTERM EXAM. Grade 7Document2 pagesMIDTERM EXAM. Grade 7WINDA BOIMAUNo ratings yet

- Top Oil Temperature Modelling by Calibrating Oil Time Constant For An ONAN Distribution TransformerDocument9 pagesTop Oil Temperature Modelling by Calibrating Oil Time Constant For An ONAN Distribution TransformermohamedNo ratings yet

- Heirs of Lorenzo Buensuceso Vs PerezDocument13 pagesHeirs of Lorenzo Buensuceso Vs PerezJuan Luis LusongNo ratings yet

- M CommerceDocument35 pagesM Commerceapi-1993758450% (4)

- TERMS OF REFERENCE. Development of Integrated Financial Management System (IFMS)Document5 pagesTERMS OF REFERENCE. Development of Integrated Financial Management System (IFMS)Derek KahongoNo ratings yet

- JavaScript & CSS Code ExplanationDocument10 pagesJavaScript & CSS Code ExplanationsmjavailableNo ratings yet

- Ebook of PoemsDocument24 pagesEbook of Poemsapi-519442608No ratings yet

- Strategic MGMT Ch01Document250 pagesStrategic MGMT Ch01Phuong NguyenNo ratings yet

- Structural Estimates of Supply and Demand Elasticities For Houses in SydneyDocument27 pagesStructural Estimates of Supply and Demand Elasticities For Houses in SydneySteven WangNo ratings yet

- Brecon ConnectionDocument8 pagesBrecon ConnectionJack DavisNo ratings yet

- Conversation Cards MojeDocument4 pagesConversation Cards MojeMonika JNo ratings yet

- Bicycle Powered Water Filtration System: 25% Senior Design ReportDocument28 pagesBicycle Powered Water Filtration System: 25% Senior Design ReportGajanan MaliNo ratings yet

- Padmanabhapuram Palace & Unit - 5Document26 pagesPadmanabhapuram Palace & Unit - 5Priya Priya100% (1)

- GPH ScreentimeDocument6 pagesGPH ScreentimeVicta Ryza CatartikaNo ratings yet

- Application Form For Manager / Assistant Manager From Among Tata Steel Employee Ward - 2017Document1 pageApplication Form For Manager / Assistant Manager From Among Tata Steel Employee Ward - 2017shamb2020No ratings yet

- Safer Smarter Better: Riders, Ridercoaches & TrainingDocument6 pagesSafer Smarter Better: Riders, Ridercoaches & TrainingLovejoy Bermudez QuiambaoNo ratings yet

- Us Deloitte Global Treasury Survey 2022Document22 pagesUs Deloitte Global Treasury Survey 2022kirill.barkhatovNo ratings yet

- Akips Installation GuideDocument14 pagesAkips Installation GuideHanan AbbasNo ratings yet

- Aldehydes, Ketones and Carboxylic Acids Question Bank (Subjective)Document16 pagesAldehydes, Ketones and Carboxylic Acids Question Bank (Subjective)helixvector45411No ratings yet